Discrete Semiconductor Circuit Examples

# Discrete Semiconductor Circuit Examples

© 1973 International Telephone and Telegraph Corporation

Reprinting is generally permitted, indicating the source. However, our consent must be obtained in all cases.

Information furnished by ITT is believed to be accurate and reliable. However, no responsibility is assumed by ITT for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of ITT.

The information and suggestions are given without obligation and cannot give rise to any liability; they do not indicate the availability of the components mentioned.

Printed in W.-Germany · Imprimé dans la République Fédérale d'Allemagne by Druckerei Karl Schillinger · Freiburg im Breisgau · Wallstraße 14

Edition 1973/3

Order No. 6200-99-1 E

Subject to modifications

#### **Preface**

This book is a revised version of an earlier collection of circuit examples to which new ones, devised in the INTERMETALL application laboratory, have been added. It does not contain any RF circuits or circuits with thyristors, four-layer diodes or integrated devices. Simple circuits, which allow basic principles and their elaborations to be recognized, have been chosen rather than complex ones. For the sake of clarity, power supplies have been omitted on most of the diagrams.

The explanatory text represents a compromise in that it had to be written so as to provide a coherent book as well as a reference manual divided into self-contained sections. Whilst there are frequent references to other circuits in the book, this does not mean that lengthly passages have to be read in order to understand a particular circuit. The descriptions of circuits with which familiarity can be assumed are kept brief (unless they are of special importance), whilst those of lesser known and novel ones are treated in greater depth. Most circuit diagrams contain detailed component information; design procedures are given only for very simple circuits.

As far as the lay-out of the circuit diagrams is concerned, an attempt has been made to adhere to the following: The top and bottom limits of each diagram are formed by the two supply lines; the component networks are then drawn between these lines so that physical position in the diagram is indicative of potential. For example, if a circuit employs mainly NPN transistors, then the positive line is near the top of the page and the top terminals of any components drawn in a vertical position would be more positive than the bottom ones; the opposite applies to circuits incorporating PNP transistors. However, this rule is not always strictly observed for the sake of even component distribution and space utilization.

Circuits designed for NPN transistors will, in general, also function with PNP devices, provided the polarity of the supply and that of any electrolytics and diodes is reversed.

|      |                                                              | Page     |

|------|--------------------------------------------------------------|----------|

| l.   | Voltage and Current Stabilizers                              | 9        |

| 1.   | Basic Zener Diode Shunt Stabilizer                           | 12       |

| 2.   | Zener Diode Bridge Stabilizers                               | 14       |

| 3.   | Rectifier Bridge Stabilizer                                  | 16       |

| 4.   | Half-Wave Rectifier Stabilizer                               | 18       |

|      | AC Stabilizer                                                | 20       |

|      | High-Symmetry AC Stabilizer                                  | 22       |

|      | Simple Series Stabilizers                                    | 24       |

|      | Simple Shunt Stabilizers                                     | 26       |

|      | Combined Series-Shunt Stabilizer                             | 28       |

|      | Simple Current Stabilizer                                    | 30       |

|      | Two-Terminal Constant Current Circuit                        | 32<br>34 |

|      | Wide Range Constant Current Source                           | 36       |

|      | Series Stabilizer Short-Circuit Protected Complementary      | 30       |

| 14.  | Transistor Series Stabilizer                                 | 38       |

| 15   | Series Stabilizer with Variable Output Voltage               | 40       |

|      | Series Stabilizer with Low Voltage Drop                      | 42       |

|      | Series Stabilizer with Electronic Cut-Out                    | 44       |

|      | Stabilizer for Low Battery Voltages                          | 46       |

|      |                                                              | 40       |

| II.  | Amplifiers                                                   | 49       |

|      | General-Purpose AF Amplifier                                 | 52       |

| 2.   | Recording Response Equalizer with Rumble and Noise Filter    | 54       |

| 3.   | AF Preamplifier with Tone and Volume Controls                | 58       |

|      | Presence Filter                                              | 60       |

|      | Low-Power Complementary Series Push-Pull Output Stage        | 62       |

|      | Single-Ended 1.5 W Class A Amplifier                         | 64       |

|      | Series Push-Pull 2 W Class B Amplifier                       | 66       |

|      | 2 x 6 W Amplifier Conforming to DIN 45 500 (HiFi)            | 68       |

|      | 60 W Amplifier with Output Power Switching Facilities        | 70<br>74 |

|      | Transformer-Coupled 8 W Push-Pull Class B Amplifier          | 74<br>76 |

|      | Telephone Pick-Up Amplifier  Flootropic Coin Control Circuit | 78       |

| 12.  | Electronic Gain Control Circuit                              | 70       |

| 111. | Oscillators                                                  | 81       |

|      |                                                              | •        |

|      | RC Oscillators                                               | 84       |

|      | RC Oscillators for Very Low Frequencies                      | 86       |

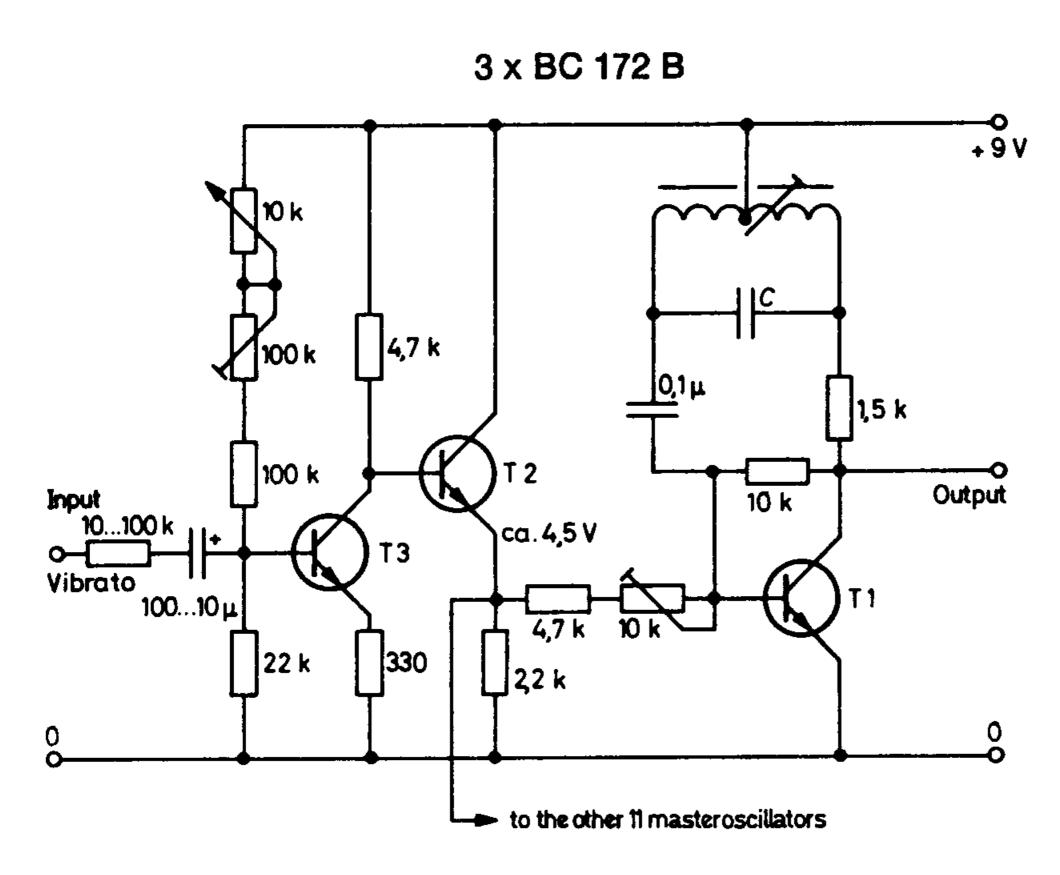

| 3.   | LC Oscillator for Electronic Organs                          | 88       |

| 5.          | RC Oscillator for Simple Electronic Musical Instruments Two-Terminal Oscillator Circuits Flasher Circuits | <b>Page</b><br>90<br>92<br>94 |

|-------------|-----------------------------------------------------------------------------------------------------------|-------------------------------|

| IV.         | Digital and Pulse Circuits                                                                                | 97                            |

| 1.          | Schmitt Trigger                                                                                           | 100                           |

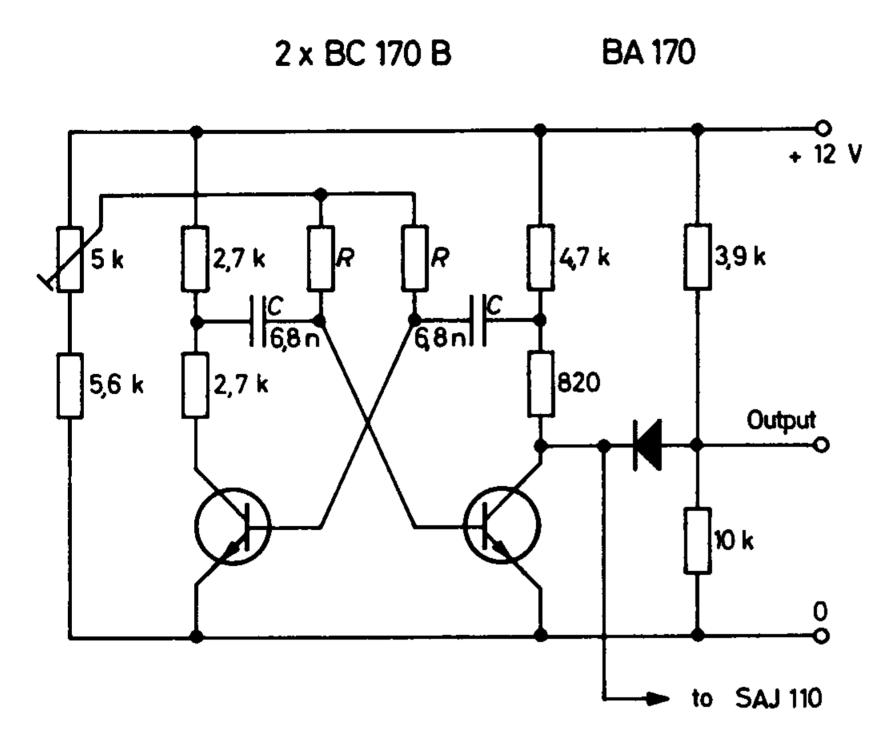

| 2.          | Bistable Flip-Flop                                                                                        | 102                           |

| 3.          | Monostable Flip-Flop                                                                                      | 104                           |

|             | Astable Flip-Flop                                                                                         | 106                           |

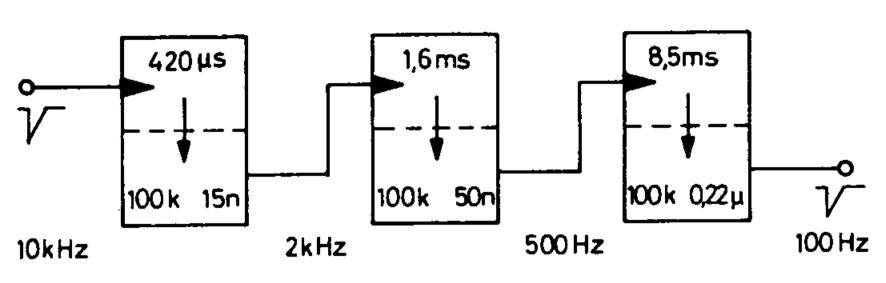

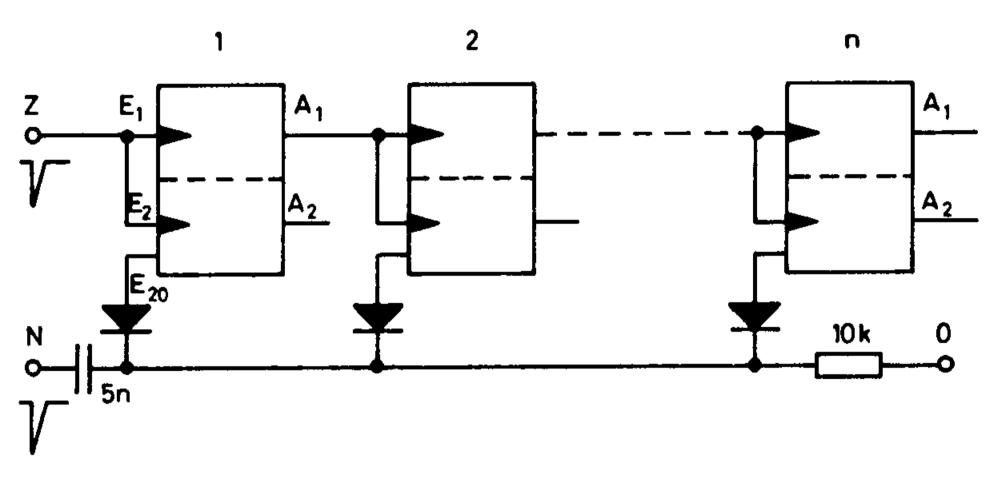

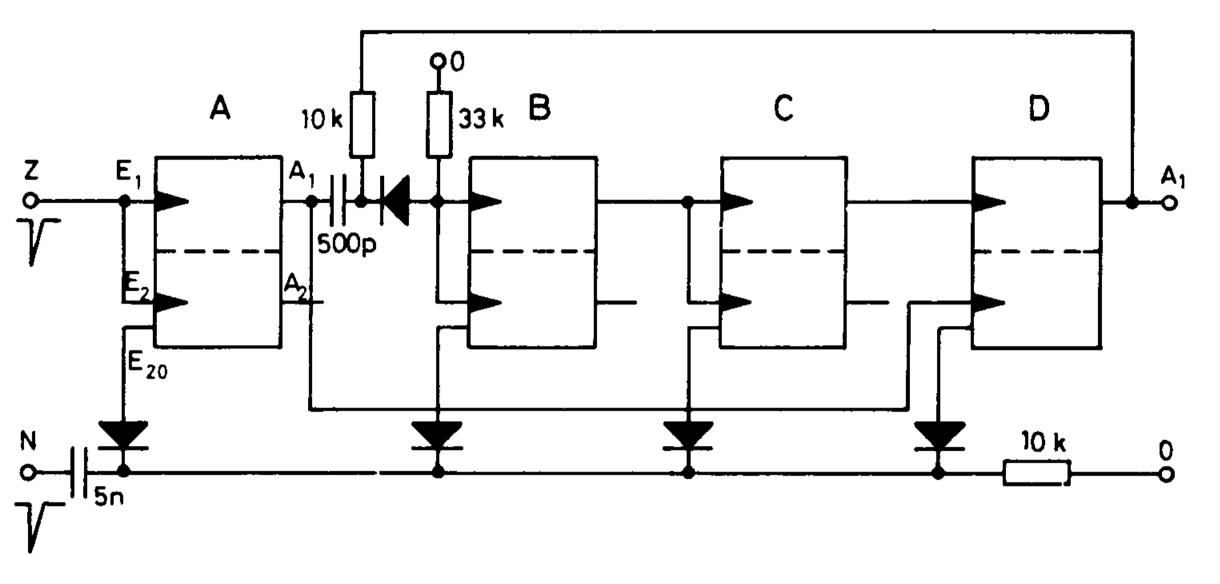

|             | Monostable Frequency Divider Chain                                                                        | 108                           |

|             | Binary Counter                                                                                            | 110                           |

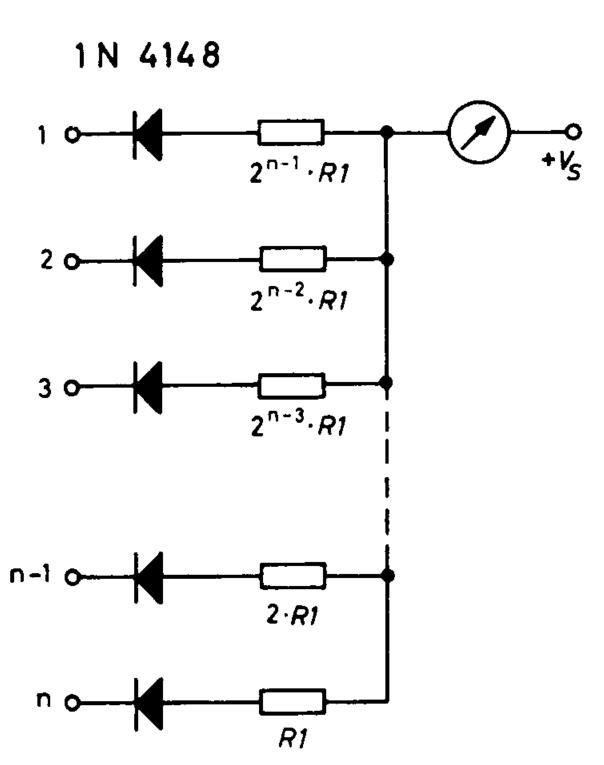

|             | Digital-Analog Converter for Binary Counters                                                              | 112                           |

|             | Decade Counter with Binary Stages                                                                         | 114                           |

|             | Shift Register                                                                                            | 116                           |

| 70.         | Shift Register with Polarized Relays Providing                                                            | 118                           |

| 44          | Information Storage on Supply Failure                                                                     | 120                           |

|             | Blocking Oscillator Blocking Oscillator Frequency Divider                                                 | 122                           |

|             | Numerical Indicator for BCD Counters                                                                      | 124                           |

| v.          | Timer and Relay Circuits                                                                                  | 127                           |

| 4           | Polov Bull-On Dolov Circuit                                                                               | 130                           |

|             | Relay Pull-On Delay Circuit Relay Drop-Out Delay Circuit                                                  | 132                           |

|             | Relay Pull-On and Drop-Out Delay Circuit                                                                  | 134                           |

|             | Cyclic Relay Timer                                                                                        | 136                           |

|             | Cyclic Astable Multivibrator Timer                                                                        | 138                           |

|             | Timer Incorporating Monostable Circuit                                                                    | 140                           |

|             | Miller Integrator Timer                                                                                   | 142                           |

|             | Timer (Relay Energized During Timing Interval)                                                            | 144                           |

|             | Relay Pull-On Delay Circuit Utilizing Superimposed Pulses                                                 | 146                           |

|             | Flick Pulse Relay                                                                                         | 148                           |

| <b>V</b> 1. | Control Circuits                                                                                          | 151                           |

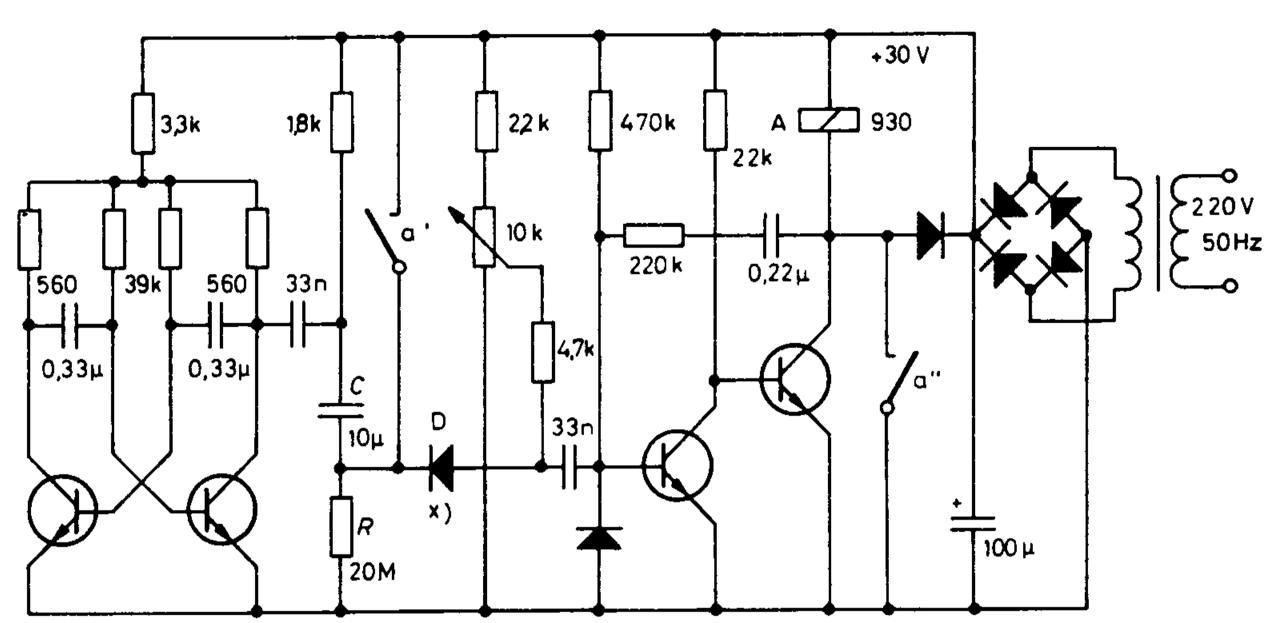

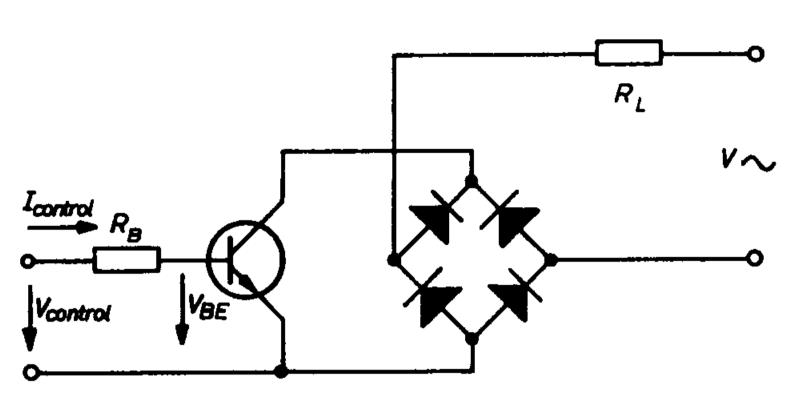

| 1           | AC Transistor Switch                                                                                      | 154                           |

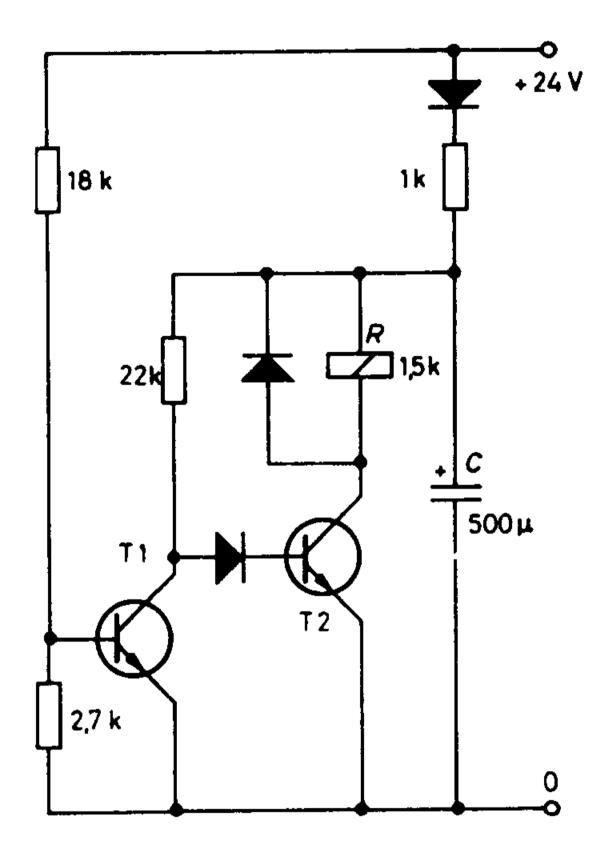

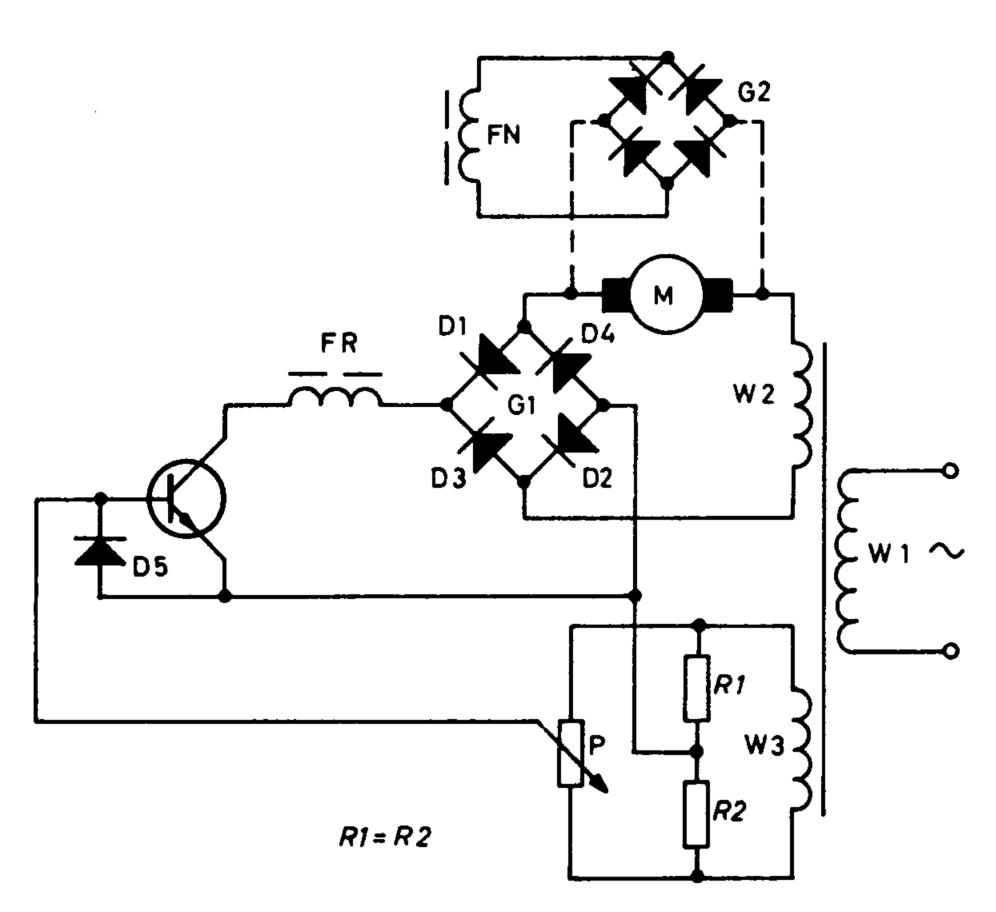

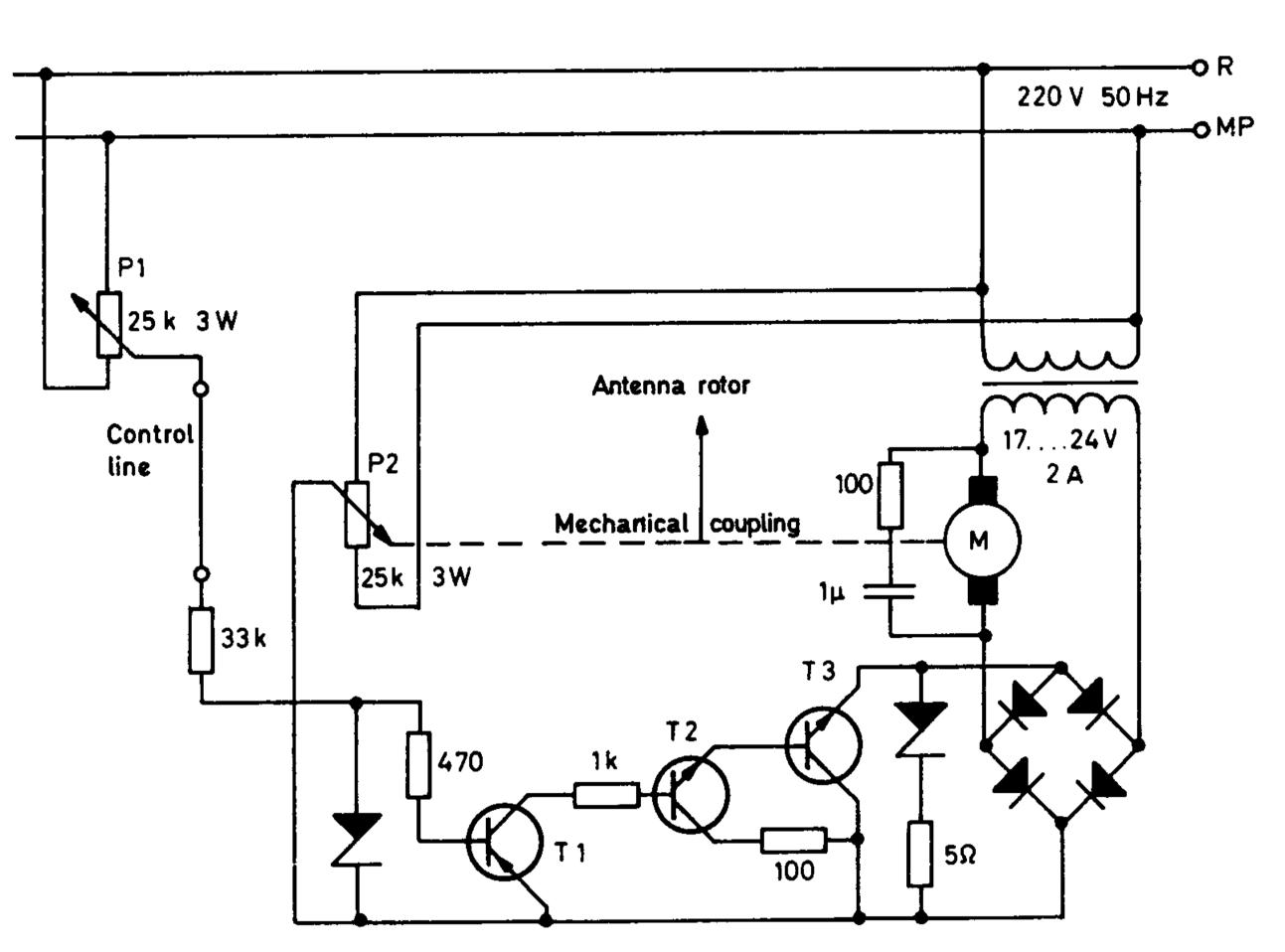

|             | DC Motor Control Circuit                                                                                  | 156                           |

|             | Servo Control System                                                                                      | 158                           |

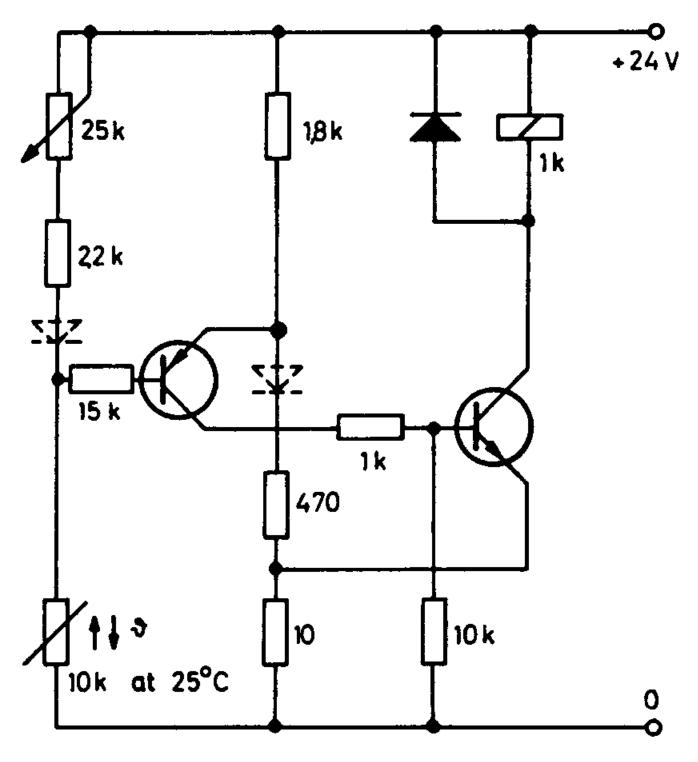

|             | On-off Temperature Controller                                                                             | 160                           |

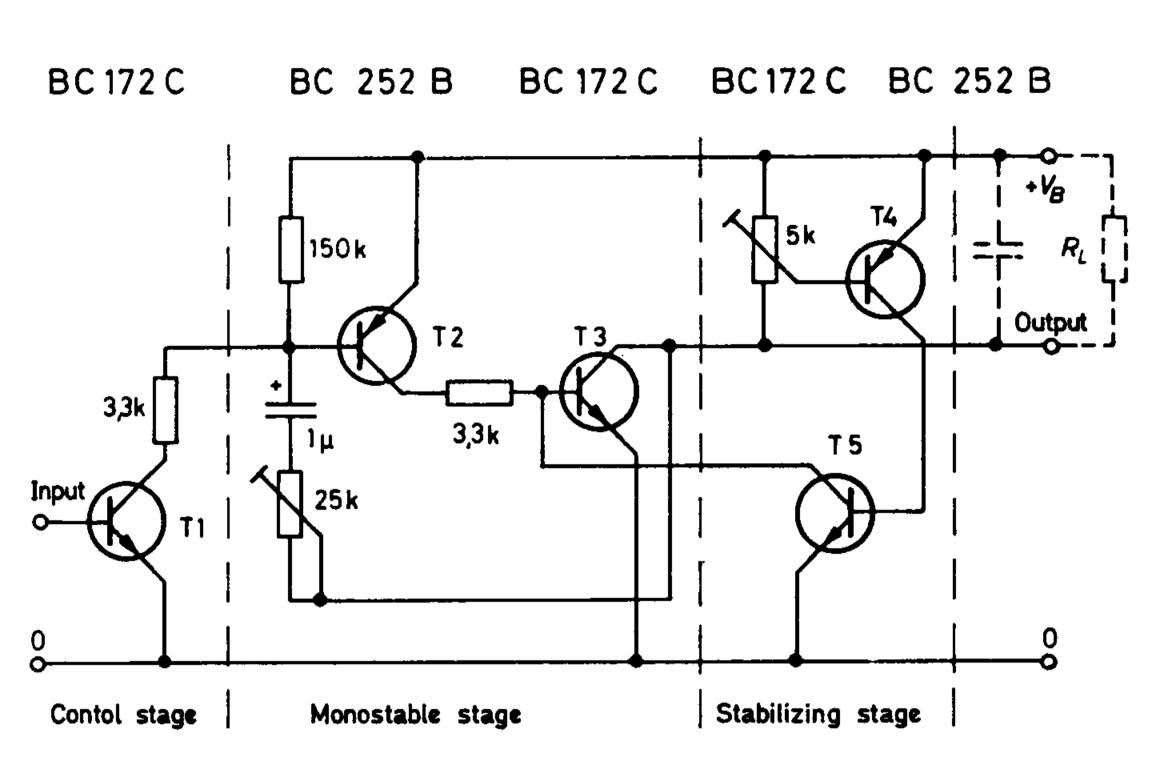

|             | Stabilized Stepping Pulse Generator                                                                       | 162                           |

|             |                                                                                                           |                               |

|                                                | Page |

|------------------------------------------------|------|

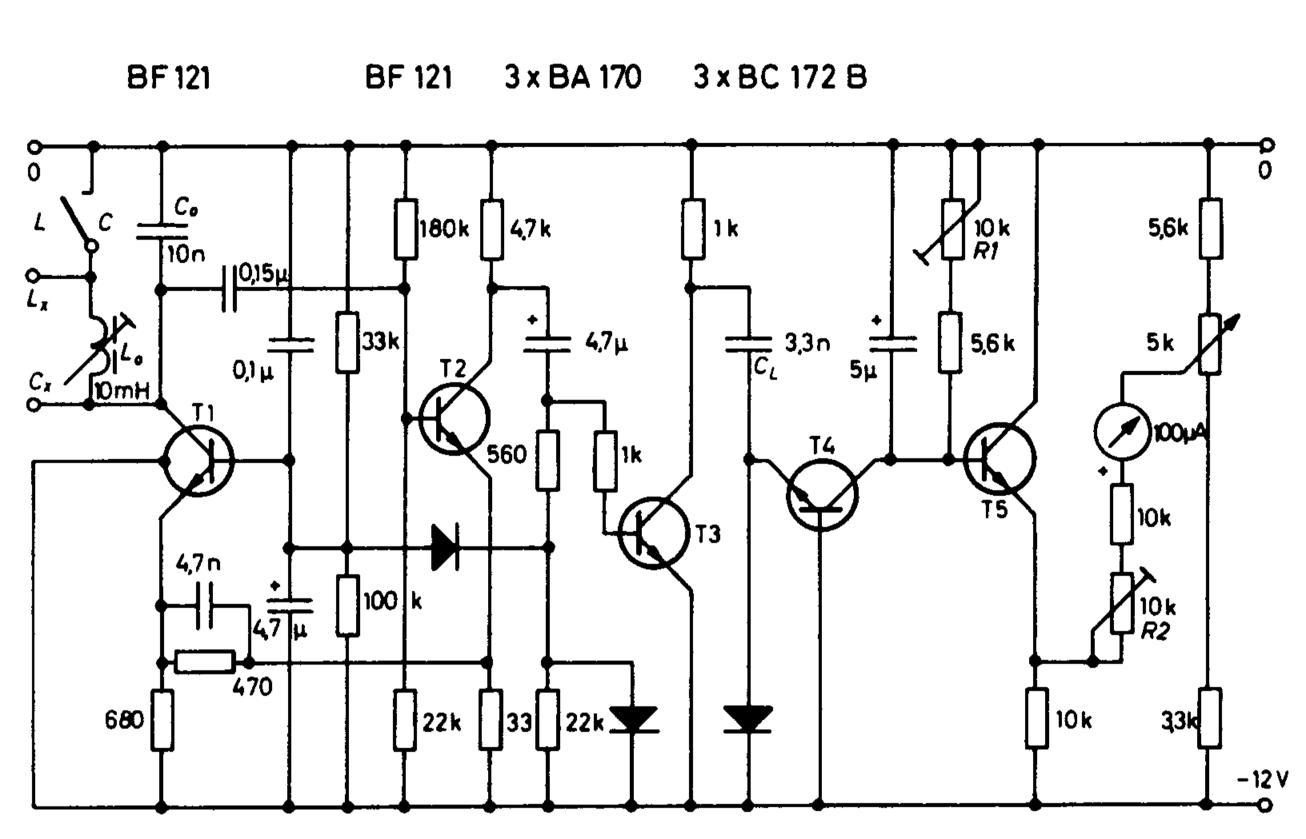

| . Metering and Monitor Circuits                | 165  |

| 1. Revolution Counter for Motor Vehicles       | 168  |

| 2. Frequency Meter                             | 172  |

| 3. Direct-Reading LC-Meter                     | 174  |

| 4. Direct-Reading Transistor $\beta$ -Meter    | 176  |

| 5. Event Timer                                 | 178  |

| 6. Energizing Circuit for Standby Warning Lamp | 180  |

| 7 Inductive Limit Switch                       | 182  |

# I. Voltage and Current Stabilizers

|     |                                                                    | <b>D</b> |

|-----|--------------------------------------------------------------------|----------|

|     |                                                                    | Page     |

| 1.  | Basic Zener Diode Shunt Stabilizer                                 | 12       |

| 2.  | Zener Diode Bridge Stabilizers                                     | 14       |

| 3.  | Rectifier Bridge Stabilizer                                        | 16       |

| 4.  | Half-Wave Rectifier Stabilizer                                     | 18       |

| 5.  | AC Stabilizer                                                      | 20       |

| 6.  | High-Symmetry AC Stabilizer                                        | 22       |

| 7.  | Simple Series Stabilizers                                          | 24       |

| 8.  | Simple Shunt Stabilizers                                           | 26       |

| 9.  | Combined Series-Shunt Stabilizer                                   | 28       |

| 10. | Simple Current Stabilizer                                          | 30       |

| 11. | Two-Terminal Constant Current Circuit                              | 32       |

| 12. | Wide Range Constant Current Source                                 | 34       |

| 13. | Series Stabilizer                                                  | 36       |

| 14. | Short-Circuit Protected Complementary Transistor Series Stabilizer | 38       |

| 15. | Series Stabilizer with Variable Output Voltage                     | 40       |

| 16. | Series Stabilizer with Low Voltage Drop                            | 42       |

| 17. | Series Stabilizer with Electronic Cut-Out                          | 44       |

| 18. | Stabilizer for Low Battery Voltages                                | 46       |

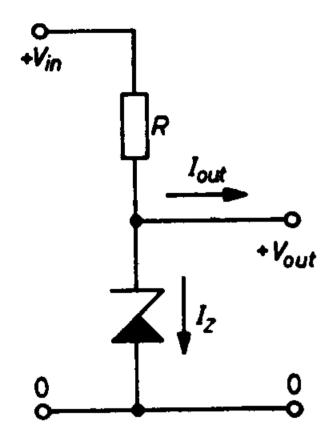

### **Basic Zener Diode Shunt Stabilizer**

A stabilizer, in its simplest form, consists of a resistor R in series with a zener diode, this network being connected to the unstabilized input voltage  $V_{in}$ . The stabilized output voltage  $V_{out}$  is taken from across the zener diode. If the output current  $I_{out}$  decreases, then  $I_Z$ , the operating current through the diode, increases by nearly the same amount, with the result that the output voltage is held approximately constant. If, on the other hand, the input voltage increases, then  $I_Z$ , and hence the voltage drop across R, increase sufficiently to compensate for the increase in input voltage.

The stabilizing factor S is the ratio of relative input voltage change to relative output voltage change:

$$S = \frac{dV_{in}/V_{in}}{dV_{out}/V_{out}}$$

or, for high values of R,

$$S \approx \frac{R}{r_z} \cdot \frac{V_{out}}{V_{in}}$$

The differential output resistance of the stabilizer is approximately the same as  $r_z$ , the differential resistance of the zener diode.

The value of resistor R is governed by two factors, namely on the one hand by the maximum current which the diode can handle without suffering damage, and on the other by the lowest diode reverse current necessary to ensure reliable breakdown conditions.

The following rules apply:

$$R > \frac{V_{in \max} - V_{out}}{I_{Z \max} + I_{out \min}}$$

$$R < \frac{V_{in \max} - V_{out}}{I_{Z \min} + I_{out \max}}$$

where  $I_{Z max}$  is the maximum permissible operating current quoted in the relevant data sheet, and  $I_{Z min}$  is the minimum current which can be tolerated without increasing the differential resistance above an acceptable limit.  $I_Z$  should be approximately 5 to 10 % of  $I_{Z max}$ .

1. Basic zener diode shunt stabilizer

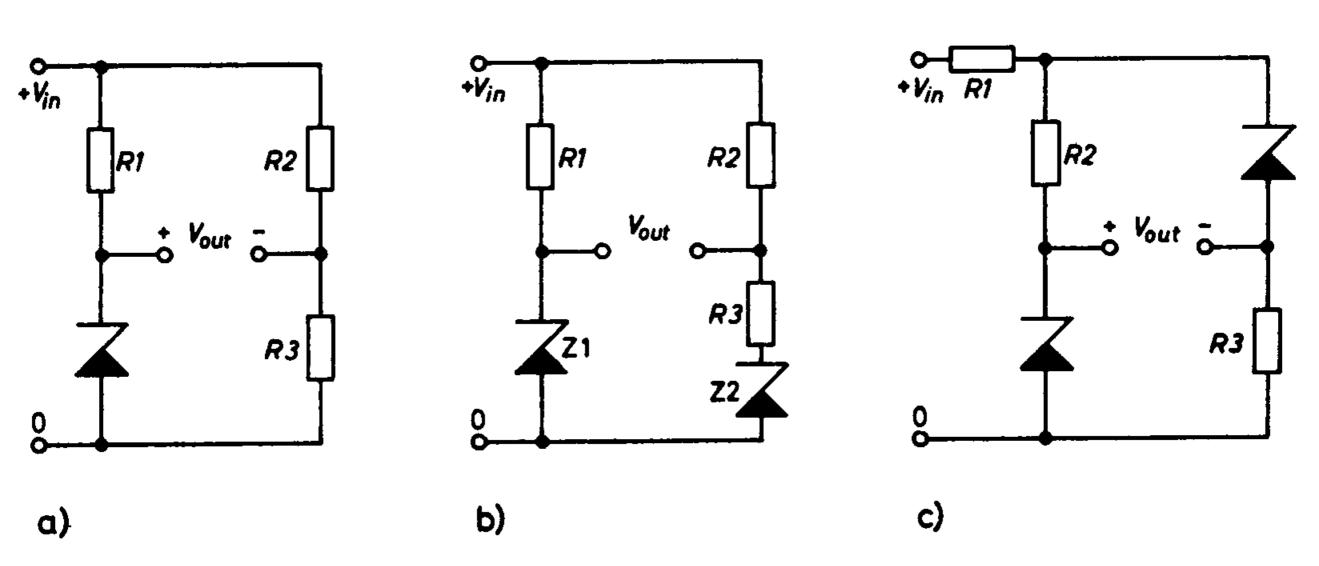

## Zener Diode Bridge Stabilizers

Considerably better stabilization factors than those attainable with the basic zener diode circuit of Fig. I. 1. can be obtained with bridge circuits. In fact, if  $r_z$ , the differential zener diode resistance, were constant and the bridge accurately balanced, then the stabilization factor would be infinite. Unfortunately the differential resistance is not constant. It becomes smaller as the diode current is increased. Hence the bridge is usually adjusted so that balance conditions obtain only in the centre of the desired operating range. Under these conditions an increase in voltage causes the output to increase initially, and then, beyond the balance point, to decrease. If the stabilization factor is measured for a small input voltage swing about a mean input voltage, it will be found that, as the mean input voltage is varied from low to high values, S is initially positive and increases until the balance point is reached when it becomes  $+\infty$ ; S then changes sign and slowly decreases in magnitude from  $-\infty$  downwards.

If the stabilization factor is measured by determining the ratio of maximum input change to maximum output change and the signs are disregarded, then, for the usual  $\pm$  10% input variation, a stabilization factor of the order of several hundred can be expected.

To balance the bridge, an AC voltage should be superimposed on the DC supply and the resistive bridge arms adjusted for minimum AC output.

A better balancing method, which also takes the thermal part of the differential zener diode resistance into account, is to switch the DC bridge input between two levels. In this case bridge output readings should be taken only after the circuit has reached thermal equilibrium.

- a) The bridge comprises one zener diode and three resistors, the load being connected to the "detector" points. The resistance values should be chosen so that, with the bridge operating in the centre of the desired stabilization range, the condition  $R1/r_z = R2/R3$  is fulfilled. The differential output resistance of this circuit is approximately  $r_z + R3$ ; the output voltage is equal to the diode zener voltage minus the voltage dropped across R3.

- b) This circuit is particularly suitable for use as a low voltage stabilizer, the output being approximately equal to  $V_{Z1} V_{Z2}$ , where  $V_{Z1}$  and  $V_{Z2}$  are the operating voltages of the zener diodes Z1 and Z2 respectively. The differential output resistance is  $r_{z1} + r_{z2} + R3$ . The bridge should be balanced in the centre of the desired stabilization range so that  $R1/r_{z1} = R2/(R3 + r_{z2})$ . R3 can be omitted if a slight difference in the currents passed by the two bridge arms is acceptable, or if the differential resistance values of the two diodes are approximately equal.

- 2. Zener diode bridge stabilizers

- c) This circuit is recommended when the difference between input and output voltage is only small. The operating voltages of the zener diodes should be closely matched; the same applies to the values of the resistors R2 and R3, which should be chosen so that with the bridge operating in the centre of the stabilization range, they have the same value as the differential resistance of the zener diodes. The value of resistor R1 should be low enough to ensure sufficient current flow through the diode at low input voltages, but not so low that at maximum input the zener diodes are overloaded.

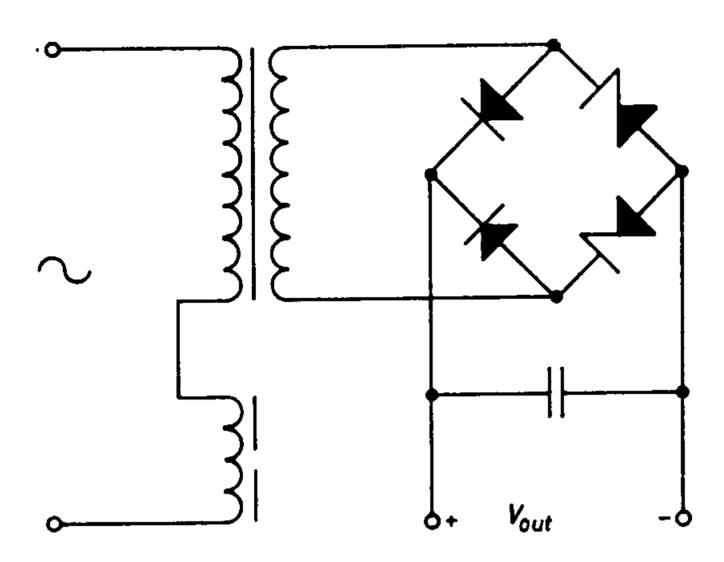

# Rectifier Bridge Stabilizer

It is possible to replace the two of the four rectifiers in an AC rectifier bridge by zener diodes in order to obtain a stabilized output. Such a circuit requires a "dropper" in the AC path; this could be either a capacitive or inductive reactance, in which case the dissipated power would be particularly low.

The stabilizing effect of this circuit is based on the fact that the voltage to which the reservoir capacitor is charged is limited to a value determined by the operating voltage of the zener diode. The voltage decays during the discharge intervals. The amount of ripple present depends on the capacitance of the reservoir capacitor, the supply frequency and the load current. The circuit is, therefore, only suitable for use as a prestabilizer or semi-stabilized supply.

The voltage across the reservoir capacitor is limited to a peak value equal to the difference between the operating voltage of the zener diode and the forward voltage of the conventional diode. The operating voltages of the two zener diodes should be matched as closely as possible, otherwise the ripple content (at fundamental supply frequency) would be increased.

In the circuit shown in Fig. 3 a choke is used as an AC input dropper. Alternatively the supply transformer could be designed as a leakage-reactance transformer, in which case the choke could be omitted because the input current is then limited by the leakage reactance of the transformer.

3. Rectifier bridge stabilizer

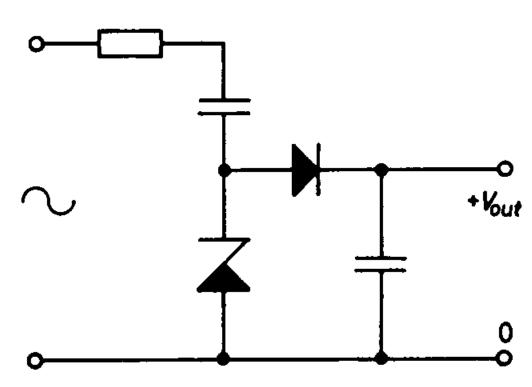

#### Half-Wave Rectifier Stabilizer

In the half-wave rectifier circuit shown in Fig. 4 a capacitor is used as a series "dropper" for the zener diode. During the negative half-cycles of the input voltage the zener diode conducts in the forward direction, and the lower terminal of the series capacitor is connected to the 0 V line. During the positive half-cycles the diode operates under reverse breakdown conditions and limits the voltage developed across the reservoir capacitor. The output of this circuit has a higher ripple content than that of a full-wave circuit.

The circuit is suitable for supplying semiconductor circuits with low current requirements directly from the AC line. The resistor is included to limit the capacitor inrush current to a value which the diode can handle safely.

It should be noted that the absence of an AC line transformer calls for special safety precautions.

.

4. Half-wave rectifier stabilizer

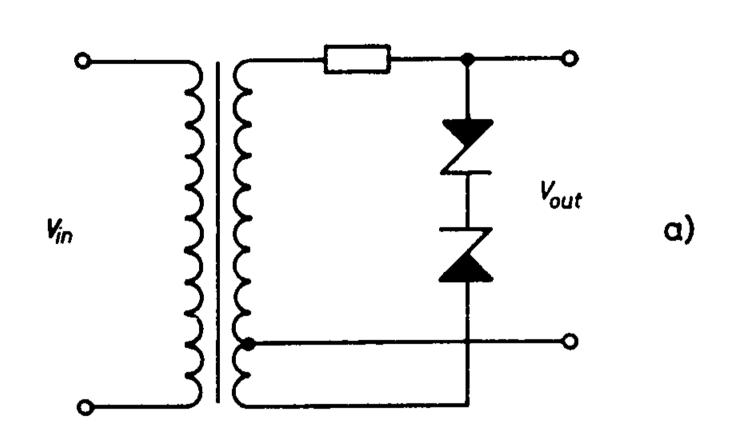

#### **AC Stabilizer**

If a network, comprising two identical zener diodes, connected back-to-back and in series with a resistor (this resistor could be a capacitive or inductive reactance), is connected to an AC supply, then the output waveform will be a symmetrical trapezoid with a stabilized peak value equal to the sum of the forward and the operating voltage of the diode. Note, however, that any input level variations, whilst having no effect on the peak value, will affect the sloping edges of the trapezoid and consequently the form factor and RMS value of the output voltage. The circuit is, therefore, only suitable for applications where the RMS value is unimportant (e. g. as a voltage calibrator in oscilloscopes).

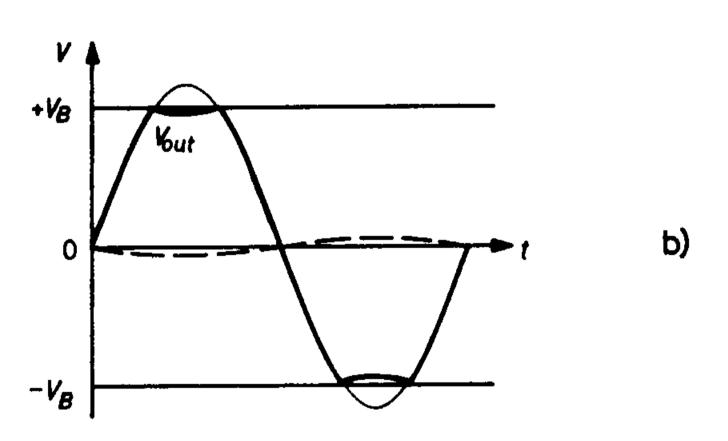

The circuit can be modified to form a bridge by providing the transformer secondary with a tap (Fig. 5 a). At low input voltages the output then has the near-trapezoidal shape shown in Fig. 5 b, the input sine wave being clipped to  $V_B$  (the sum of forward and operating voltage); the effect of the "bucking" voltage presented across the lower part of the secondary winding is negligible in these circumstances.

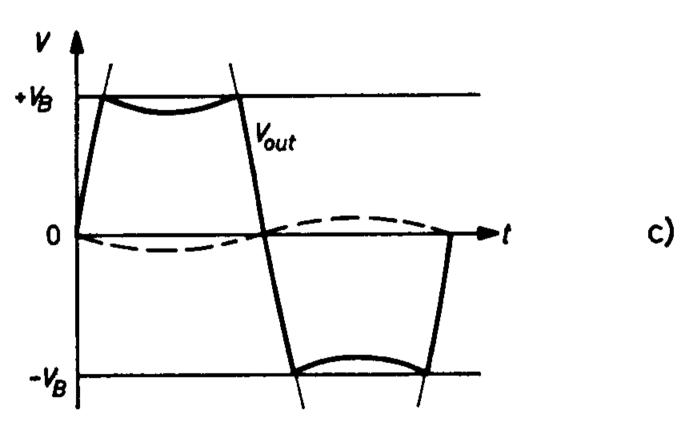

Without the bucking voltage any large increase in input would result in what is virtually a square wave with a peak value of  $V_B$ . The RMS value of such a waveform would be considerably higher than that of the trapezoidal voltage shown in Fig. 5 b (which also has a peak value of  $V_B$ ). However, the bucking winding now produces an opposing voltage (dotted line in Fig. 5 c) which, if the number of turns is correct, tends to keep the RMS value of the output voltage (thick lines) nearly constant.

One application for such a circuit would be as a filament voltage stabilizer for vacuum tubes used in precision measurement equipment.

- 5. RMS Stabilizer for AC

- a) Circuit diagram

- b) Output waveform a low input voltages

- c) Output waveform at high input voltages

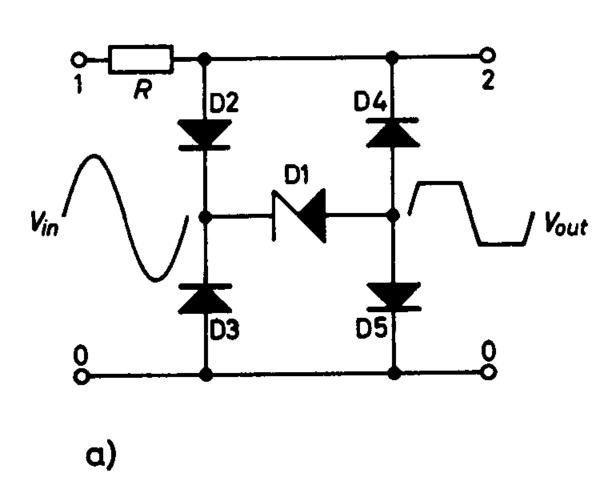

## **High-Symmetry AC Stabilizer**

The conventional AC clipper circuit incorporating back-to-back zener diodes has the disadvantage that in order to obtain a good symmetry, the diodes must be quite closely matched. Such diodes are, however, virtually unobtainable in large quantities. Nevertheless a square or trapezoidal waveform of good symmetry is often required for calibration purposes (in oscilloscopes, for example).

In the circuit shown in Fig. 6a the problem has been solved by shunting a zener diode across the DC terminals of a bridge rectifier. When the input goes positive with respect to the zero line, current passes from terminal 1, via series resistor R and the diodes D2, D1, and D5, to the zero line, and when it goes negative it passes from terminal 0, via diodes D3, D1, D4, and resistor R, back to terminal 1; diode D1 consequently always carries a reverse current. This has the effect of clipping both the positive and negative half waves of the input  $V_{in}$  to a level which depends on the forward voltages of the two conventional diodes and the operating voltage of the zener diode, i. e.

$$+ V_{out} = V_{FD2} + V_Z + V_{FD5}$$

$- V_{out} = V_{FD3} + V_Z + V_{FD4}.$

By choice of a correct operating point and operating voltage for the zener diode it is possible to attain a certain degree of temperature compensation of the output.

Fig. 6b shows a clipper circuit for higher currents. When the input voltage goes positive with respect to the zero line, current passes from terminal 1, via R, the collector-base diode of T1, diode D1, the base-emitter diode of T2 and diode D3, to terminal 0; at the same time the base current turns on transistor T2. Similarly when the input voltage goes negative with respect to the zero line, current passes from terminal 0, via diode D2, the base-emitter diode of T1, zener diode D1, the base-collector diode of T2, and R, back to terminal 1, while transistor T2 is now turned on.

As can be seen, the zener diode need only pass the base current of either T1 or T2, which is considerably lower than the associated collector current,  $I_B$  being equal to  $I_C/h_{FE}$ , where  $h_{FE}$  is the DC current gain. In this way it is possible to use high-power transistors capable of passing a high shunt current and yet employ a low-power zener diode. Diodes D2 and D3 must be able to carry the full shunt current but are only necessary when the operating voltage of zener diode D1 exceeds the maximum permissible transistor emitter-base voltage  $V_{EB0}$  (approximately 5...7 V for diffused silicon transistors).

and

- 6. High-symmetry AC stabilizer

- a) Low-current circuit

- b) Heavy-current circuit

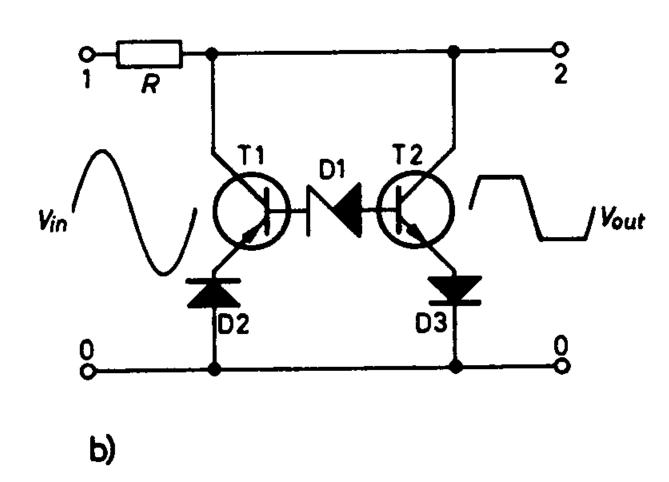

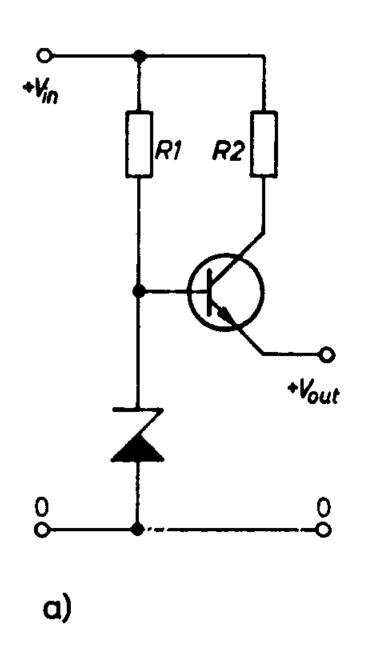

# Simple Series Stabilizers

The output power obtainable from the simple zener diode shunt stabilizer discussed in I. 1. can be increased by applying the stabilized zener diode output voltage to the base of a power transistor and taking the final output from the emitter of this transistor (Fig. 7a). The stabilization factor of this circuit (like that of circuit I. 1.) is governed by the ratio  $R1/r_z$ . Resistor R2 is merely included to reduce the transistor dissipation. The output voltage is equal to the operating voltage of the zener diode minus the transistor base-emitter voltage; the differential output resistance is approximately  $(r_z + h_{ie})/h_{FE}$ .

A further reduction in output resistance can be obtained by employing a so-called Lin-circuit, of which the circuit shown in Fig. 7b is a design example. Here a PNP transistor T1 and an NPN transistor T2 are connected in such a way that the circuit performs very much like a single transistor stage with a current gain of  $h_{FE\ 1} \cdot h_{FE\ 2}$ , which, however, has an input impedance  $h_{ie}$  equal to that of T1 only. Connecting the transistors in this way reduces the output resistance of the stage well below that of circuit 7a. The resistor R3 is added to provide overload protection for T1; the capacitor prevents unwanted oscillation. The measured mean output resistance was found to be as follows:

```

2 \Omega in the range I_L = 0...50 mA, 0.1 \Omega in the range I_L = 50...500 mA, 0.02 \Omega in the range I_L = 0.5...1 A

```

As can be seen, the output resistance is current-dependent. At  $I_L = 500$  mA the stabilization factor S is > 50.

The power transistor must be mounted on a heat sink with a thermal resistance not exceeding  $15\,^{\circ}\text{C/W}$ . In supplies designed to give a positive output with respect to chassis, the transistor case (which is directly connected to the collector) need not be insulated from the chassis. If the load current is less than 0.6 A, then the circuit can be short-circuit protected simply by increasing the value of R2 to  $8.2\,^{\circ}\Omega$ , in which case R2 must be capable of dissipating 40 W under short-circuit conditions.

- 7. Simple series stabilizers

- a) Incorporating series transistor

- b) Incorporating two-transistor Lin-circuit

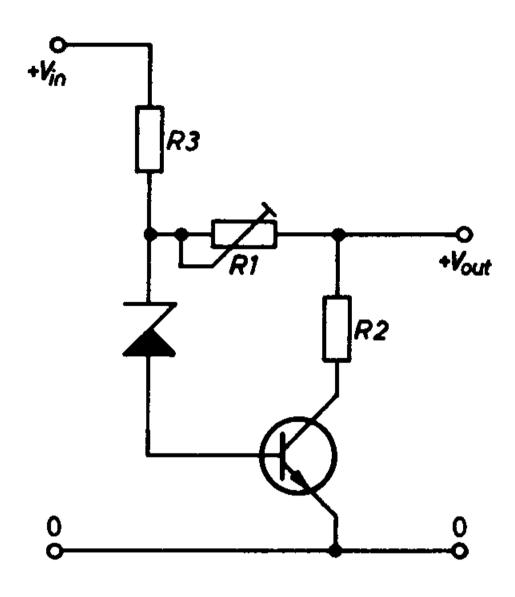

# Simple Shunt Stabilizers

Each of the circuits 8a and 8b incorporates a variable resistor R1 which allows the stabilization factor to be set to infinity for one particular operating point (similar to the bridge circuit described in I. 2.).

The circuit shown in Fig. 8a provides a fixed output voltage of approximately the same value as the operating voltage of the zener diode, which merely passes the base current of the transistor. The whole circuit, comprising a transistor, a zener diode, and the resistors R1 and R2, performs in the same way as a single high-power zener diode, with the additional advantage that the differential resistance can be varied between positive and negative values. The differential resistance is zero when

$$R1 = (r_z + h_{ie})/h_{fe}$$

If the input voltage is increased, then the current through the zener diode and hence the base and collector current of the transistor increase also. This causes the voltage dropped across R3 and preset control R1 to increase, with the result that the original rise in input voltage is compensated for and  $V_{out}$  is kept constant.

Circuit 8b is an improvement on circuit 8a in that it permits the output to be adjusted by variation of the R3/R4 ratio; it has the disadvantage that the zener diode must be capable of carrying the full emitter current of the transistor. The balance equation for this circuit is

$$R1 = (r_z + h_{ie}/h_{fe}) \cdot (R3 + R4)/R4.$$

At balance the output resistance of either circuit is approximately equal to R1.

8 a. Shunt stabilizer for fixed output voltage

8 b. Shunt stabilizer giving variable output voltage

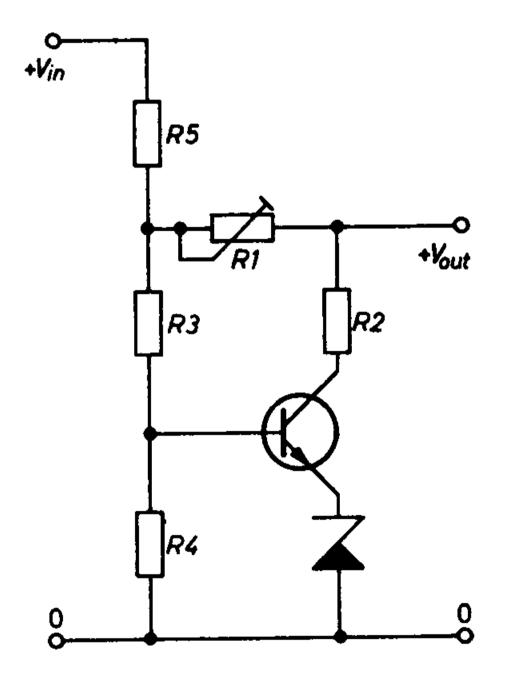

#### Combined Series-Shunt Stabilizer

Conventional series stabilizers are unable to cope with an appreciable back-EMF or reverse current produced by the load. If the emitter of the series transistors used in the stabilizer is directly connected to the output (see I. 7.), then this transistor is likely to be damaged whenever the back EMF exceeds the output voltage by more than the maximum permissible emitter-base voltage of the series transistor (usually 5...7 V). Such a supply presents a very high resistance to reverse currents. Shunt stabilizers, on the other hand, whilst not suffering from the same disadvantages, pass a continuous quiescent shunt current of the same order of magnitude as the output current.

The combined circuit shown in Fig. 9 largely overcomes both these disadvantages. In principle it is very similar to a transformerless output stage familiar from audio engineering, and consists, in the main, of a Darlington pair formed by transistors T1 and T2. A stabilized voltage derived from zener diode D3 is applied to the base of T1. Two diodes, D1 and D2, are connected in series with D3 to compensate for any loss in voltage caused by the base-emitter threshold voltages of T1 and T2. The output voltage  $V_{out}$  is consequently largely the same as that across zener diode D3 and is reasonably unaffected by temperature variations.

NPN transistor T2 and PNP transistor T3 form a complementary output stage. The operating point of both these transistors is determined by the voltage dropped across preset control P and diode D4, control P being adjusted so that the quiescent current through transistors T2 and T3 is approximately 10 mA, i. e. so that the voltage drop across emitter resistor R3 is approximately 50 mV.

Under normal conditions the circuit functions like any conventional series regulator, and passes a quiescent current of 10 mA. If, however, a back EMF is applied to the output, then the emitter potential of transistor T3 becomes more positive. Transistor T3 is now turned on harder, and the reverse current passes, via T3 and R3, to the zero terminal. Capacitor C1 provides additional filtering for the reference voltage, whilst C2 prevents instability. Each of the output transistors T2 and T3 should be fitted with a heat dissipator, p. ex. KS 1.

ZW 5,6 3x BA 170 BC 172 B

9. Combined series-shunt stabilizer

# **Performance Specifications**

Required thermal resistance

of the sink

| Input voltage             | $V_{in} = 12 \text{ V} \pm 20 \%$         |

|---------------------------|-------------------------------------------|

| Output voltage            | $V_{out} pprox 5.6  V  (V_{out} pprox 1)$ |

| Max. load current         | I <sub>out</sub> = 200 mA                 |

| Stabilization factor      | s > 50                                    |

| Output resistance         | $r_{\rm out} \approx 20~{ m m}\Omega$     |

| Max. reverse current      | $I_{rev} = 200 \mathrm{mA}$               |

| Output reverse resistance | $r_{\rm rev} \approx 1  \Omega$           |

29

Vz)

$R_{th S} < 50 \, {\rm ^{\circ}C/W}$

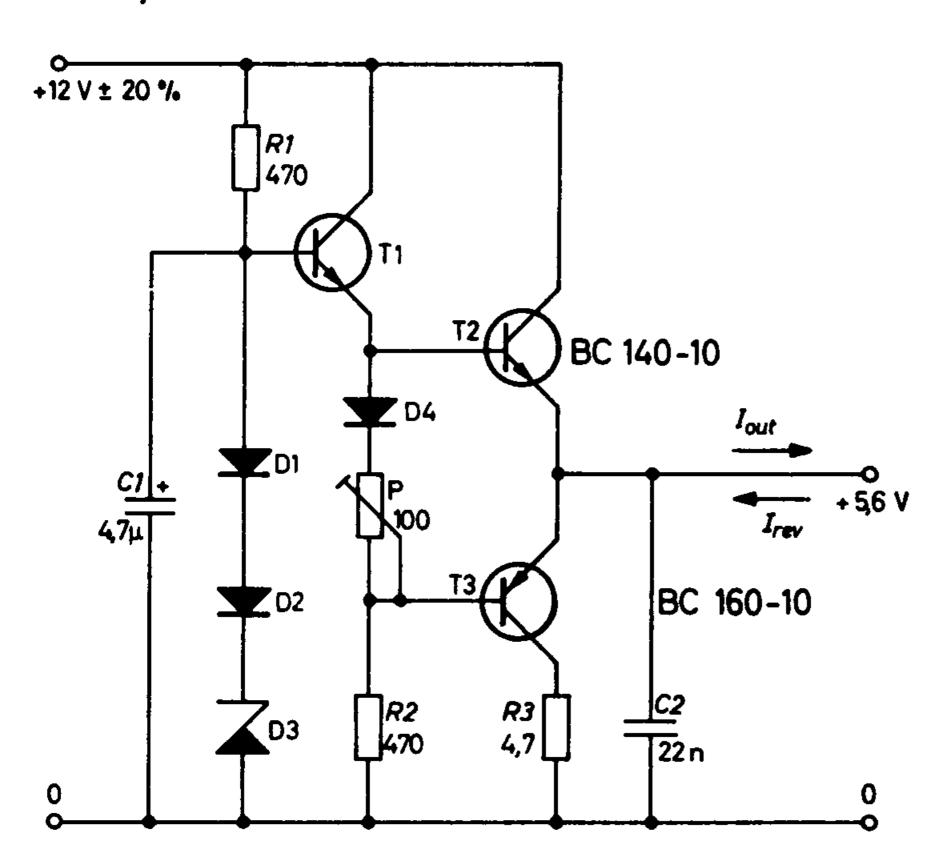

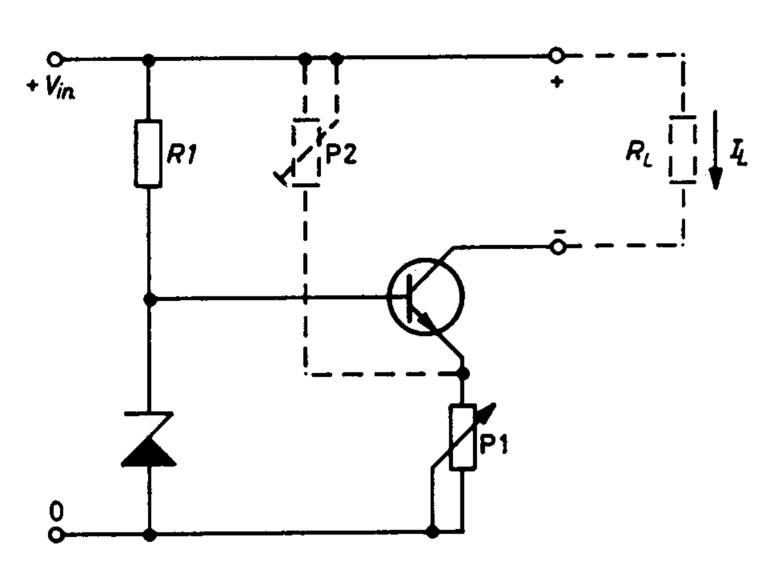

# Simple Current Stabilizer (Constant Current Source)

The output current of this stabilizer is largely unaffected by input voltage or load resistance variations. The voltage drop across P1 due to the load current,  $I_L$ , is compared with the operating voltage of the zener diode. The transistor has the dual role of error signal amplifier and control element.

Potentiometer P1 permits the output current to be set to the desired value. The stabilization factor of this circuit is approximately

$$S_{I} = \frac{dV_{in}}{dI_{L}} \cdot \frac{I_{L}}{V_{in}} = \frac{P1 \cdot R1}{r_{z}}$$

where  $r_z$  is the differential resistance of the zener diode. Use of a second potentiometer P2 enables the stabilization factor to be made infinite; P2 would then have to be adjusted to a value of P1  $\cdot$  R1/ $r_z$ .

The current stabilizer shown employs NPN transistors, the load being connected to the positive supply line. If the load is to be connected to the negative supply line, then an identical circuit incorporating PNP transistors should be used.

10. Simple current stabilizer (constant current source)

# **Two-Terminal Constant Current Circuit**

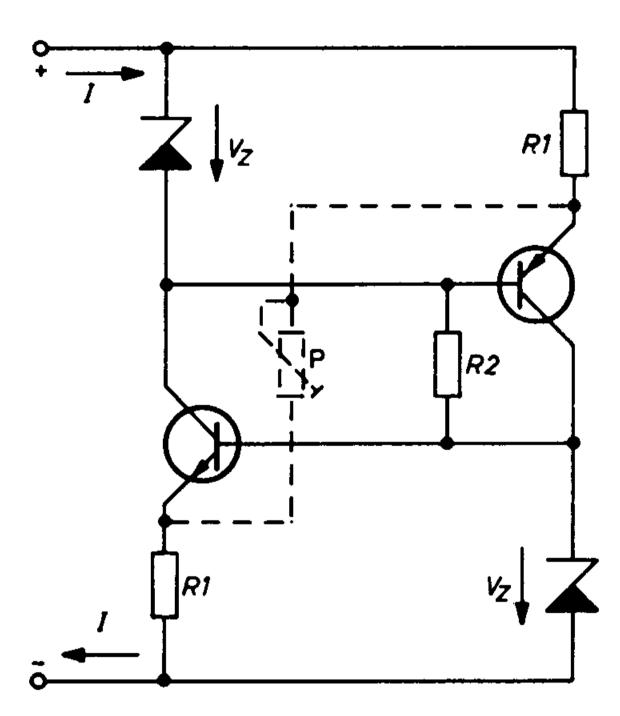

If two constant current sources of the type shown in Fig. 10 are connected in parallel, one incorporating a PNP and the other one an NPN transistor, then a two-terminal circuit with current-stabilizing properties is formed. Such a circuit will stabilize a current within narrow limits irrespective of any input voltage variations or voltage drops across other loads.

Resistors P and R2 could be omitted, but in this case the two-terminal device would have to be triggered into conduction by application of a current pulse to one of the bases. This is because the collector current of one transistor is the base current of the other and vice versa — a state which must be artifically induced by application of an external signal. The presence of resistor R2 (approx. 1  $M\Omega$ ) ensures that this happens automatically.

Whether R2 is used or not, the preset control P is important; without it an increase in terminal voltage would result in a slight current rise, which this control allows to be compensated for.

If P is reduced below the optimum value giving maximum current stabilization, then the two-terminal device exhibits a resistance characteristic which, under certain conditions, is negative.

The voltage dropped across either of the two resistors R1, and hence the current through them is virtually constant, the voltage being approximately equal to  $V_Z$ . The collector current of both transistors is equal to this constant current minus the current passing through variable resistor P (base-currents are disregarded). Whilst any voltage increase across the two-terminal network causes the current through this resistor to increase, this is offset by an equal reduction of the current through the two transistors; therefore the total current through the two-terminal device falls by the same amount as that by which the current through P is increased. The two-terminal device consequently has a negative differential resistance of -P, provided the resistance of R2 is very much higher than that of P.

The usable negative resistance range is limited by the terminal voltages  $2 V_Z$  and  $(P/R1 + 2) \cdot V_Z$ . If the terminal voltage is too low, then the diodes carry hardly any current, and if it is too high, then the transistors are cut off.

This easily adjustable device, because of its ability to maintain a constant negative resistance over a wide range of operating conditions, could be used, for example, to nullify the effect of a positive resistance in a circuit in which a constant current is to be maintained.

11. Two-terminal constant current circuit

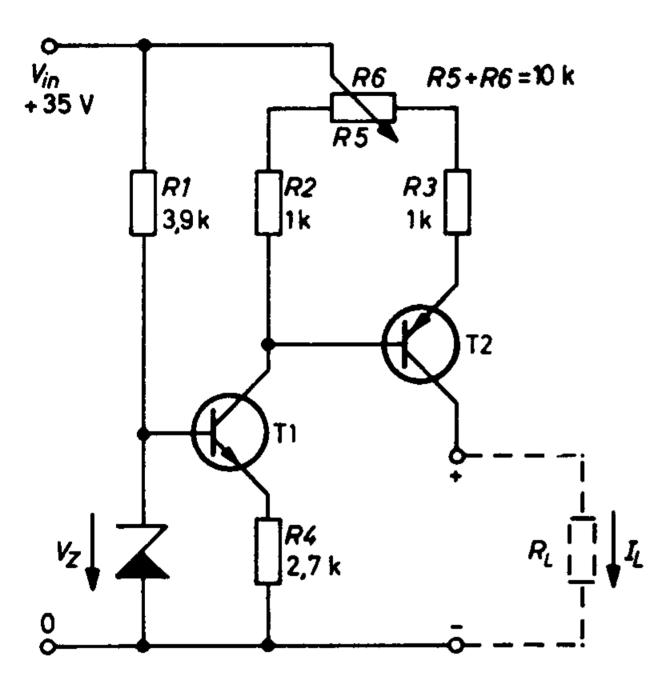

# Wide Range Constant Current Source

In this circuit the voltage dropped across a load, supplied from the current stabilizer discussed in I. 10., is used as base-bias for an identical but complementary constant current source. Since the collector current of transistor T2 is proportional to the ratio of T1 collector load (NPN transistor) to T2 emitter resistor (PNP transistor), a linear potentiometer is incorporated which permits this ratio to be continuously varied.

Assuming a base emitter voltage of 0.6 V for silicon transistors, the output current works out to

$$I_{L} = \frac{\frac{V_{Z}-0.6 \text{ V}}{R4} \cdot (R2+R5) -0.6 \text{ V}}{R3+R6}$$

and is

approximately 0.15 mA for the minimum collector load setting (R5=0), approximately 2.2 mA with the wiper in the centre (R5=R6), and approximately 24.5 mA for the minimum emitter resistance setting (R6=0) of the potentiometer.

The variation range is consequently 24.5:0.15=163:1. The reduction in output current due to the finite current gain of transistors T1 and T2 is negligible. The circuit is designed to give an output voltage of between 0 and 5 V.

When the circuit is to be designed for different output currents and voltages, is should be borne in mind that the voltage difference  $V_{in}-V_Z$  must exceed the maximum possible voltage drop across R2+R5. This voltage drop also sets a limit to the maximum possible voltage that can be developed across the load  $R_L$ . If very low currents are to be stabilized and the circuit is consequently designed as a high-impedance device, then the load current should not be reduced to below 1  $\mu A$  as otherwise difficulties due to the leakage current of transistor T2 may be experienced.

The circuit could have applications in wide range timers and function generators, to provide a constant charging current for the timing capacitor (in a Miller integrator, for example). The device replaces in this case the conventional charge or discharge resistor but has the advantage that the value of any capacitors used in long time constant circuits can be drastically reduced.

ZPD 6,8 BC 171 B BC 251 B

12. Wide range constant current source

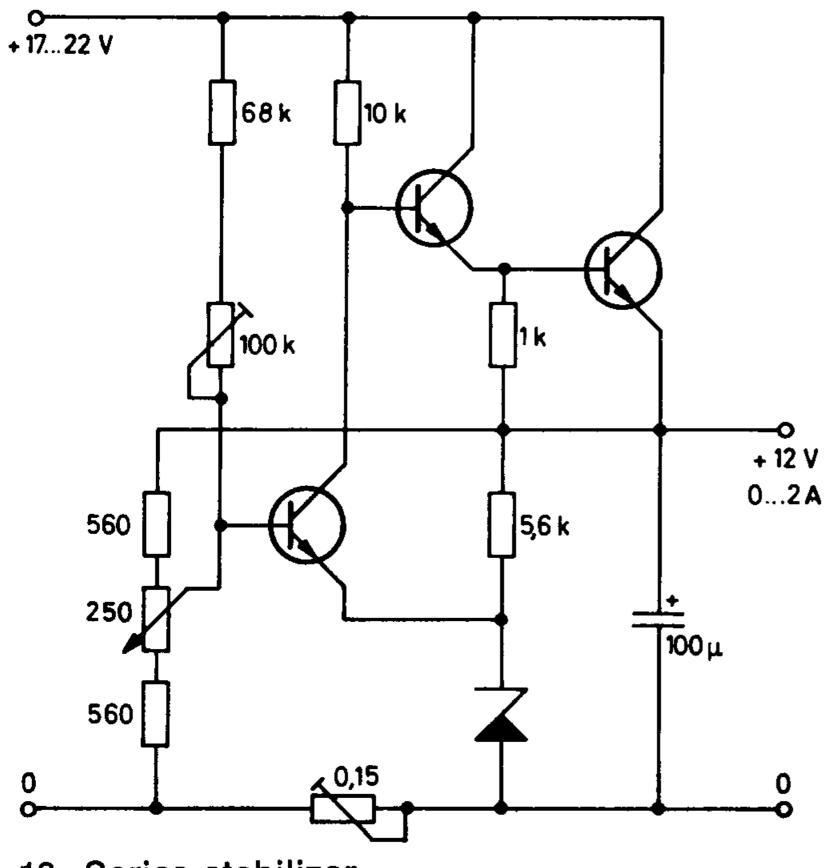

#### **Series Stabilizer**

This circuit, unlike that of the very simple series stabilizer discussed in I.7., incorporates an error signal amplifier, which amplifies a signal proportional to the difference between the actual and the reference value; the amplified signal then controls the series regulator. The stabilization factor attainable in this way is much higher, and the output resistance much lower than that of the simple circuit.

Transistor BC 170 functions as an error amplifier; its base is connected to a voltage divider across the output line, and its emitter is connected to a zener diode ZPD 6.2 which serves as a reference voltage source. The amplified error signal at the collector of the control transistor is applied to the base of the first transistor of a Darlington pair, formed by transistors BC 140-6 and 2 N 3055. The pair can be considered a single series transistor of high current gain and high input impedance which forms part of the main circuit, i. e. is connected in series with the load. The Darlington pair functions in common collector configuration.

If the output voltage rises, then the base of control transistor BC 170 becomes more positive. This causes the collector current and hence the voltage dropped across the 10  $k\Omega$  collector load to increase, with the result that the BC 140-6 base voltage and hence the output voltage is reduced, and the original voltage rise is largely corrected.

The residual output variations of such a proportional control system, whether these are due to input voltage or load current variations, can be eliminated by feedforward of the disturbance variable, the 100 k $\Omega$  potentiometer being provided for this purpose. This should be adjusted so that the output voltage is not affected by any input voltage changes. Stabilization factors of approximately 100 can be attained in this way. The 250  $\Omega$  potentiometer is an incremental output control; the variable 150 m $\Omega$  resistor permits the output resistance of the stabilizer to be reduced to zero.

The 2 N 3055 transistor must be mounted on a heat sink with a thermal resistance not exceeding 5  $^{\circ}$ C/W; the BC 140 should be fitted with a push-on heat dissipator (e. g. KS 1). The circuit may then be operated at ambient temperatures up to +45  $^{\circ}$ C. Note that the output must not be short-circuited.

BC 170 B BC 140-6 ZPD 6,2 2N 3055

13. Series stabilizer

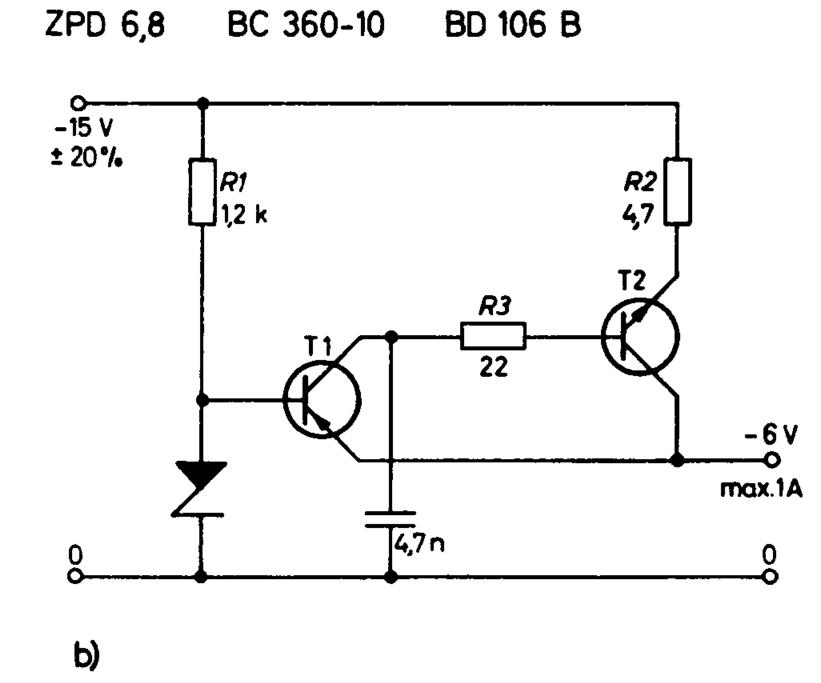

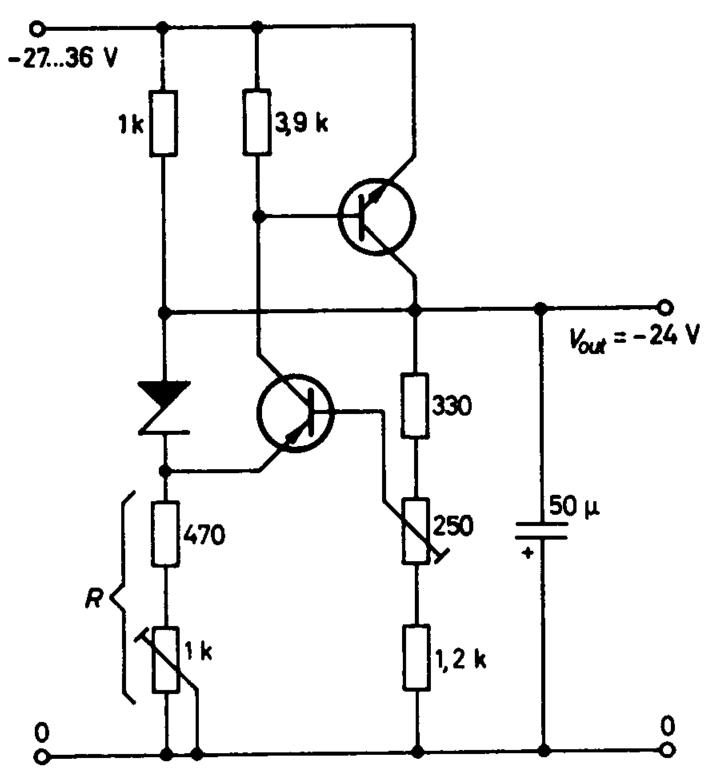

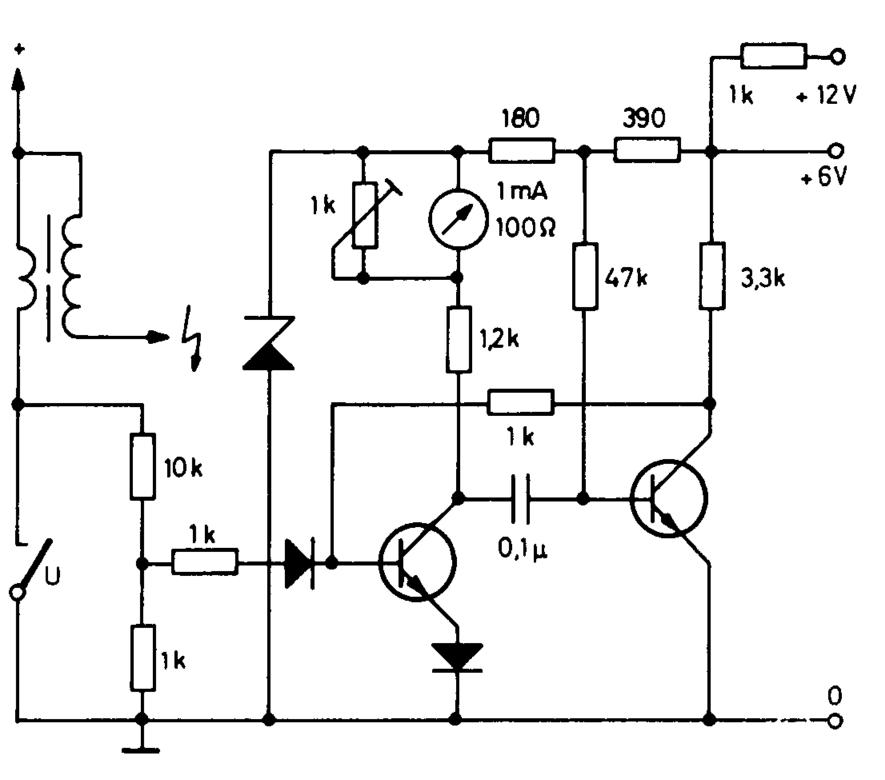

# Short-Circuit Protected Complementary Transistor Series Stabilizer

Use of two complementary transistors permits the principle on which circuit I. 13. is based to be modified so as to gain two advantages, namely better stabilization with less circuitry, and an automatic cut-out action on application of an overload.

The current passing through the series resistor R of the zener diode is composed of the current through the zener diode and the emitter current of the transistor forming the error amplifier (this is virtually the same as the base current of the output transistor); it produces a voltage drop of approximately 17 V across R. If the load current is increased, then the emitter current of the PNP transistor must, by necessity, increase correspondingly, whilst the current through the zener diode decreases by the same amount. The output voltage is held constant until the current through the zener diode is reduced to zero, whereupon any further increase in load current causes the output voltage to fall. This has the effect of reducing the base current of the control transistor and also that of the output transistor, with the result that the output current and the output voltage decrease still further, the whole action being cumulative until finally the output transistor is cut off and the output voltage is zero.

The approximate value of the cut-off current can be calculated by use of the formula

$$I_{max} = (V_{out} - V_Z)h_{FE}/R$$

where  $h_{FE}$  is the current gain of the output transistor (taking into account the current passing through the 3.9 k $\Omega$  base-emitter resistor) and  $V_Z$  is the operating voltage of the zener diode.

Because of the 1  $k\Omega$  resistor the circuit still produces a small quiescent output voltage decrease still further, the whole action being cumulative necessary to permit the circuit to reset itself to normal after the short circuit or the cause of the overload has been removed. To achieve this the load must be reduced until the voltage drop across it due to the quiescent current exceeds the base-emitter turn-on voltage of the PNP transistor.

The 250  $\Omega$  preset control permits the output voltage to be set to the exact required value. The 1 k $\Omega$  potentiometer is a cut-out current control which permits several stabilizers to be set so that they cut out at the same current regardless of the spread in current gain of the output transistors.

ZY 6,8 BC 360-6 2 N 3055

14. Short-circuit protected complementary transistor series stabilizer

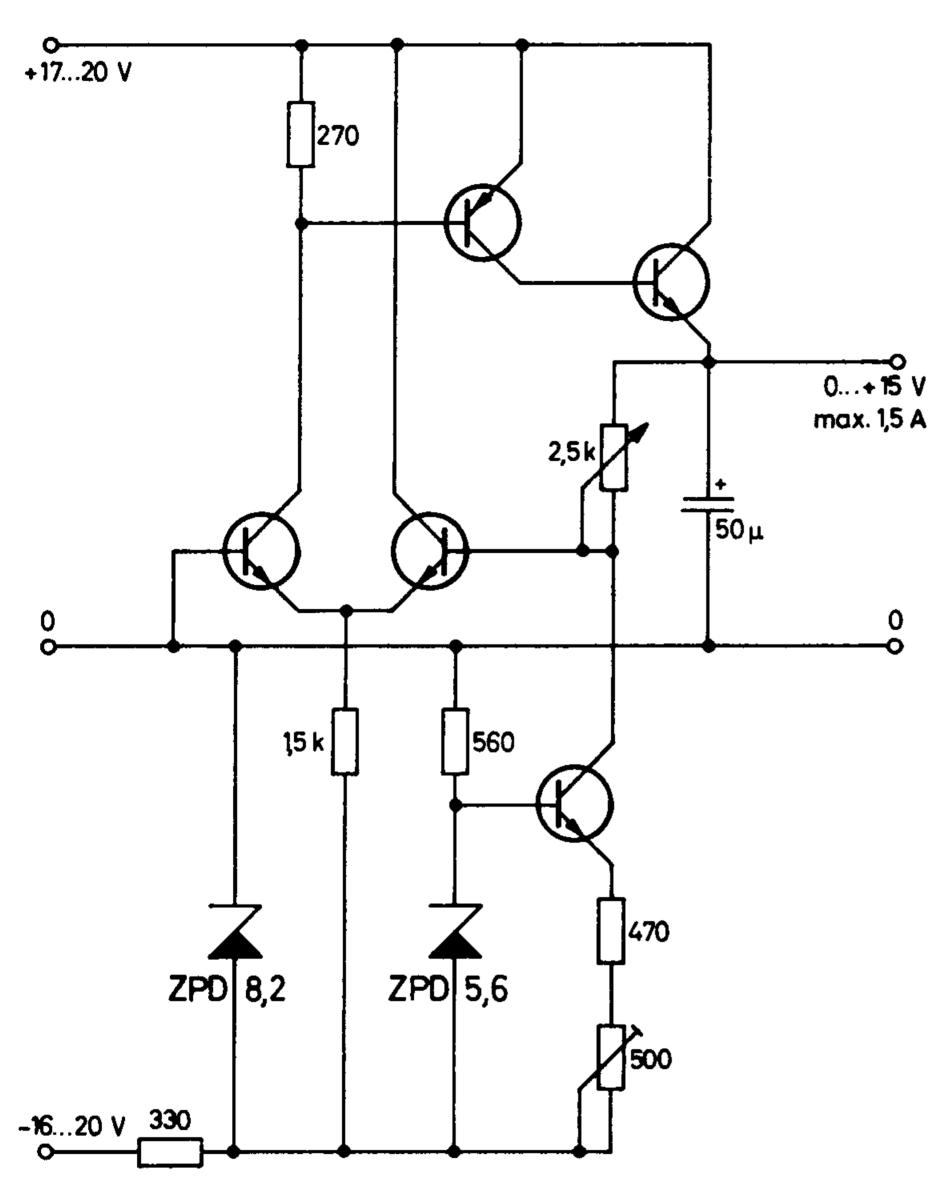

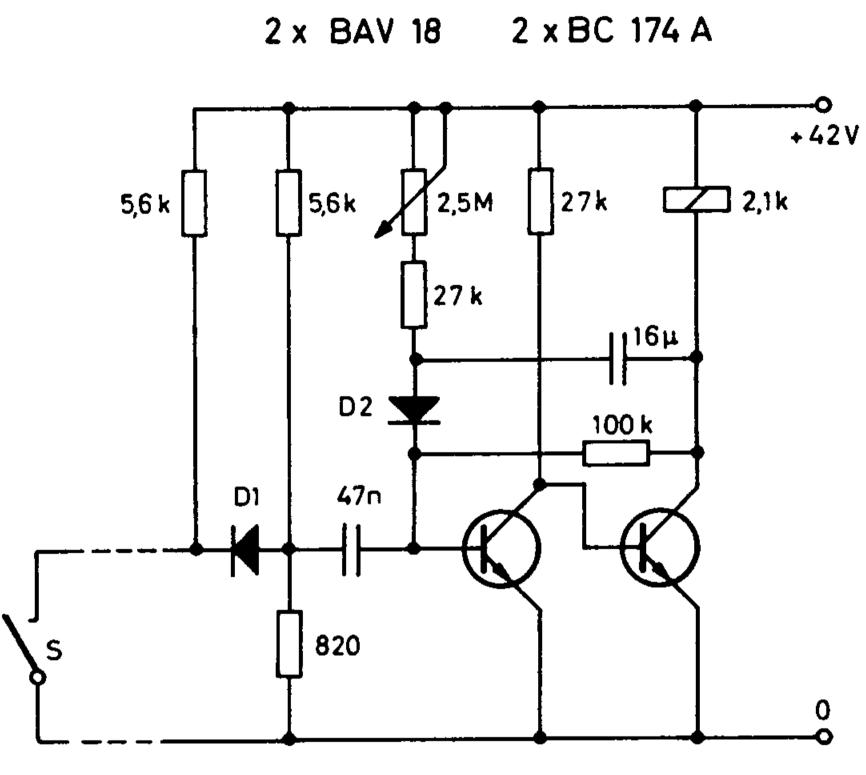

### Series Stabilizer with Variable Output Voltage

If the output voltage of a stabilizer is to be continuously variable between 0 and a maximum value, then the use of a constant current as a reference value has certain advantages. In the circuit shown in Fig. 15 the reference current is derived from a constant current source furnished by an ancillary supply. The reference current can be varied by adjustment of the 500  $\Omega$  preset control and should be set to approximately 7 mA. It passes through a variable 2.5 k $\Omega$  resistor to produce a voltage drop that can be varied between 0 and the value of the maximum output voltage, the control action of the circuit being such that the output voltage is always the same as this voltage drop. A balanced differential control amplifier drives the series regulator, which, in this circuit, comprises a PNP driver and an NPN power transistor connected in Lin configuration.

To remove the heat generated at the rated output currents and voltages, the 2 N 3055 power transistor must be mounted on a heat sink with a thermal resistance of less than 3.5  $^{\circ}$ C/W, and it is also recommended that the driver transistor BC 360 be fitted with a heat dissipator. The circuit can then be operated at ambient temperatures up to  $\pm 45$   $^{\circ}$ C.

The circuit has a stabilization factor of approximately 100 and an output resistance of approximately 30 . . . 40 m $\Omega$ .

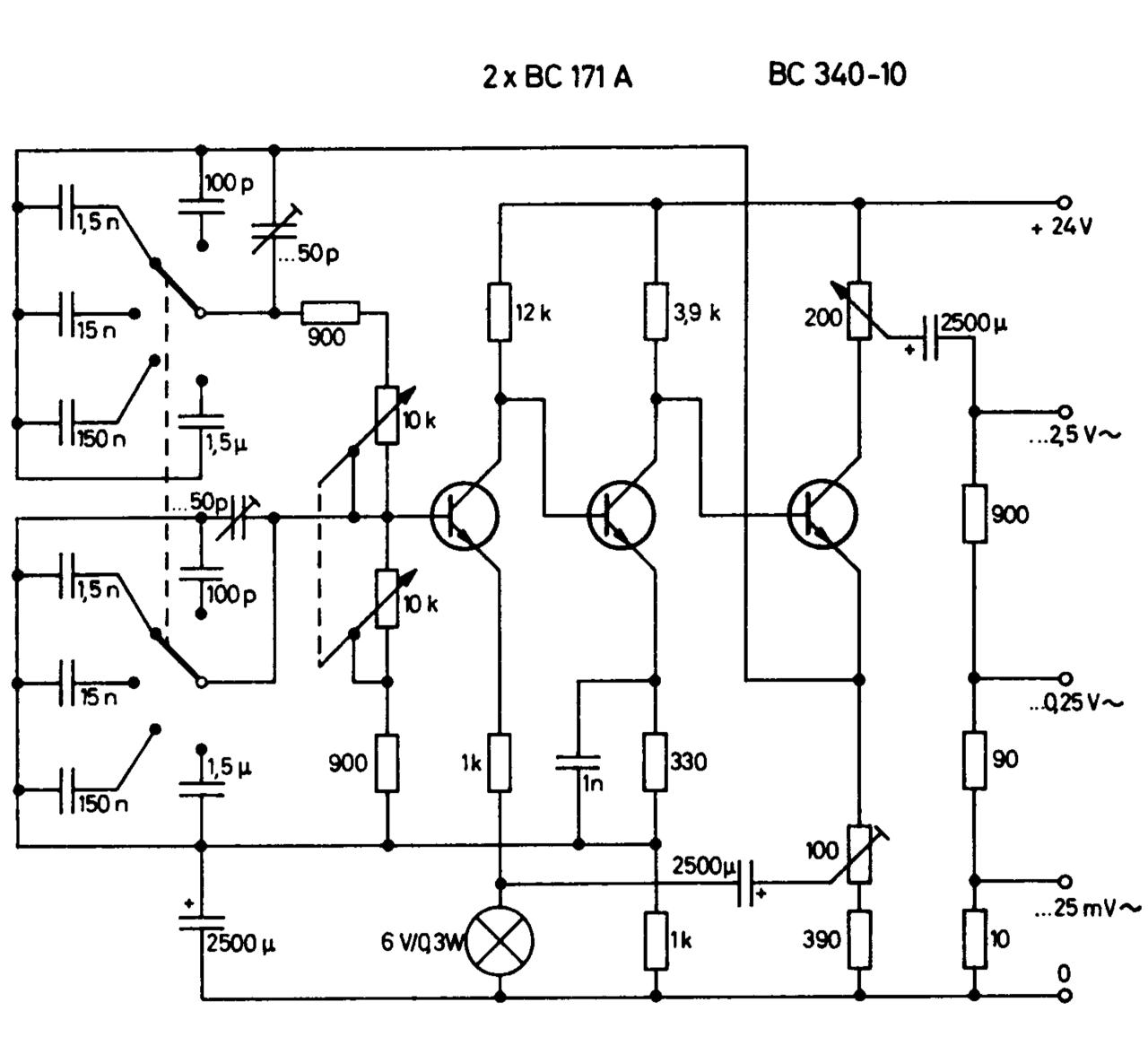

3 x BC 171 B BC 360-10 2 N 3055

15. Series stabilizer with variable output voltage

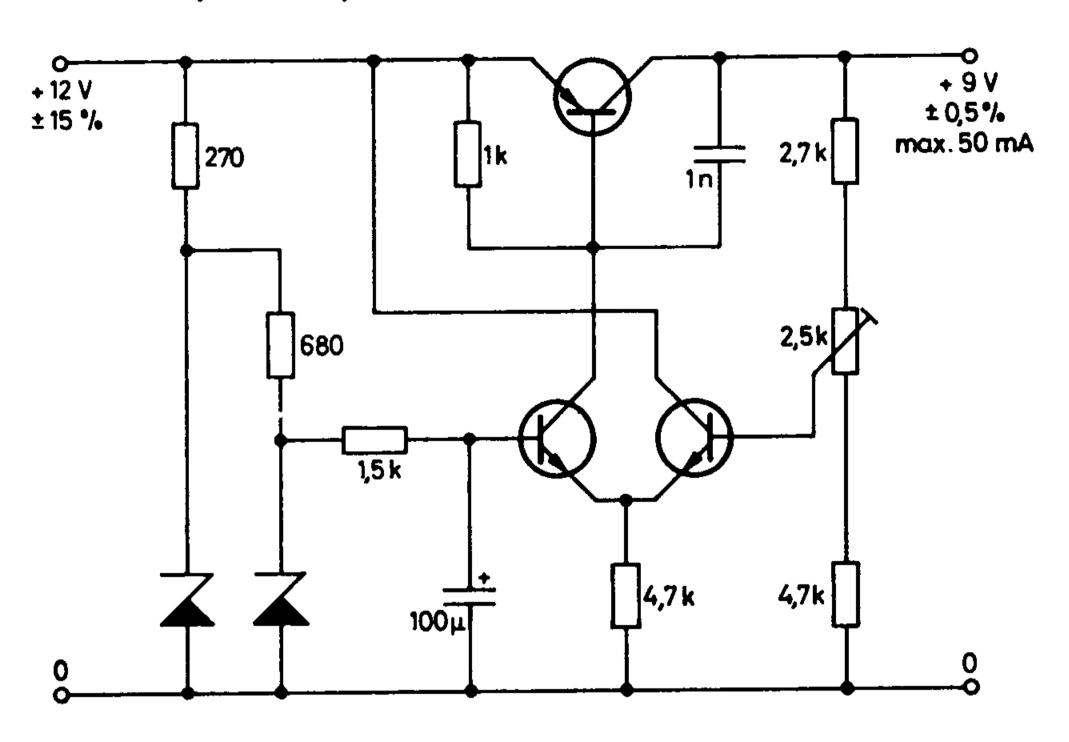

## Series Stabilizer with Low Voltage Drop

The main feature of this complementary transistor circuit (the collector of the series transistor is connected to the output terminal) is that the difference between the lowest supply voltage and the stabilized output voltage can be extremely small (approximately 1.2 V). Circuits incorporating transistors of the same polarity, such as the one discussed in I. 13. for example, are unsuitable for this purpose.

The PNP series transistor BC 360-10 is driven from a balanced differential amplifier (2 x BC 172 C), which amplifies an error signal proportional to the difference between the actual output voltage (derived from a 2.5 k $\Omega$  potentiometer) and a 5.6 V stabilized reference voltage (derived from two cascaded zener diodes).

Two zener diodes are necessary because the first diode, a ZPD 8.2, whilst exhibiting a relatively low inherent differential resistance, has an operating voltage with a relatively large temperature coefficient, whereas the second diode, the ZPD 5.6, has opposite characteristics, namely a low temperature coefficient and a relatively large inherent differential resistance. Operating the two diodes in cascade ensures that the output voltage is highly stable.

The 2.5  $k\Omega$  potentiometer is used to set the output to the required value. The 1 nF capacitor suppresses any tendency towards RF oscillation.

ZPD 8,2 ZPD 5,6 BC 360-10 2xBC 172 C

16. Series stabilizer with low voltage drop

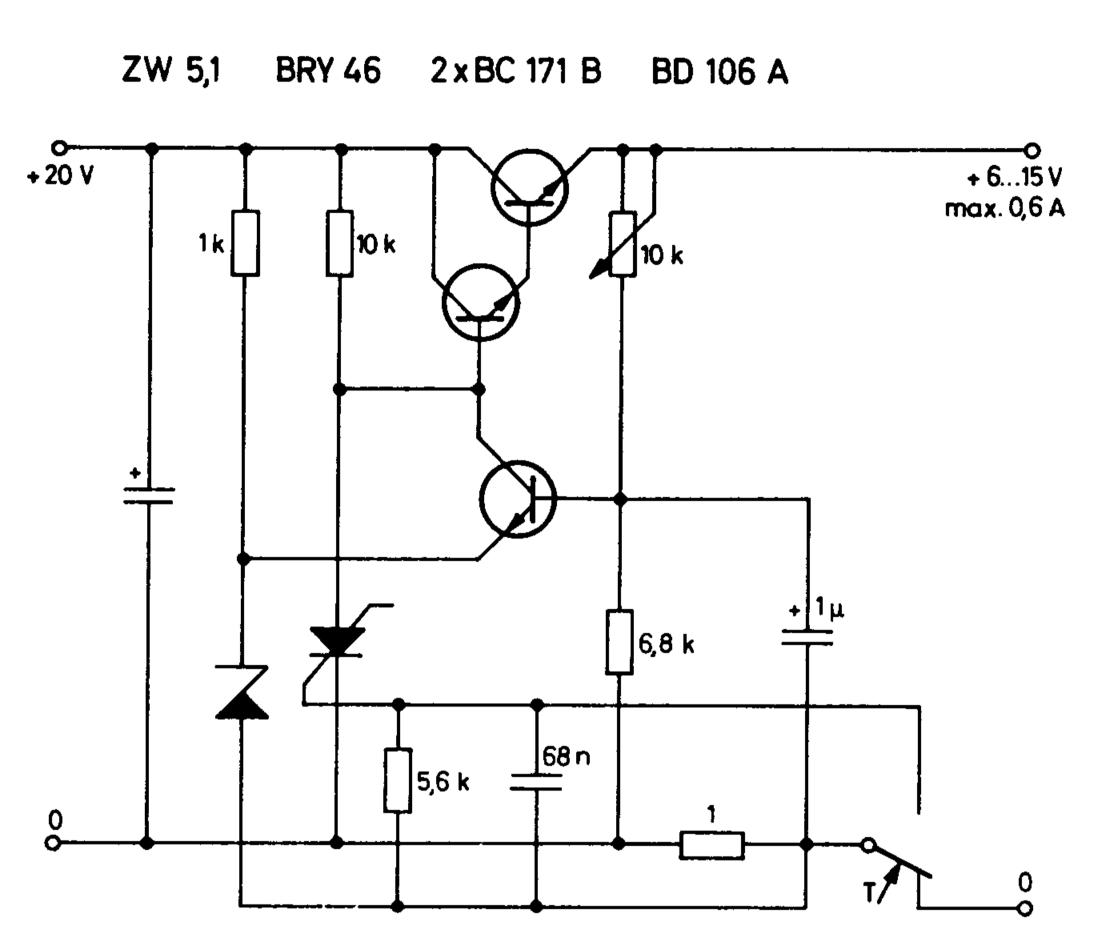

#### Series Stabilizer with Electronic Cut-Out

Series stabilizer circuits are not usually intrinsically short-circuit proof. Any overload, or short-circuit across the output terminals, endangers the series transistor or could even result in its destruction. Therefore a cut-out specifically designed to protect the series transistor would have to operate extremely quickly. Such a device would then not only protect the series transistor but also the load itself against the effect of any overload.

The circuit (Fig. 17) shows how a thyristor tetrode type BRY 46 can be used to provide overload protection for a series stabilizer. The load current passes through a 1  $\Omega$  resistor where it produces a voltage drop which is applied to the gate nearest to the cathode of the thyristor. The thyristor fires when this voltage exceeds approximately 1 V and thereby virtually short-circuits the input to the Darlington stage driving the series transistor. The series transistor, and hence the output current, are now cut off. The circuit can be returned to normal by pressing button 'T', thereby causing the load circuit to be temporarily open-circuited and the thyristor to be turned off again.

The 10  $k\Omega$  potentiometer permits the output voltage to be continuously varied between 6 and 15 V. The 1  $\Omega$  resistor, as well as providing the thyristor with a trigger signal, also introduces a feedforward signal proportional to the disturbance variable (refer to circuit I. 13.), an arrangement which considerably reduces the output resistance of the stabilizer.

17. Series stabilizer with electronic cut-out

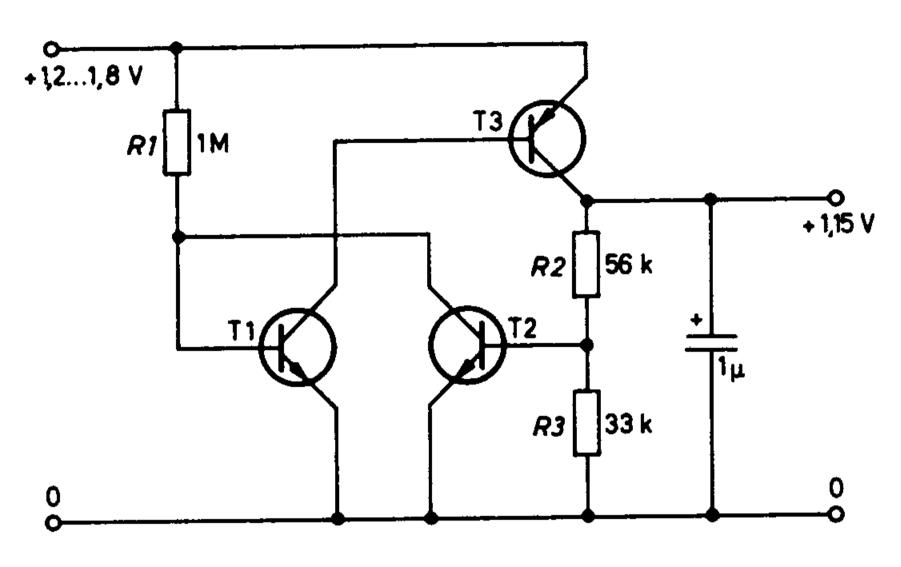

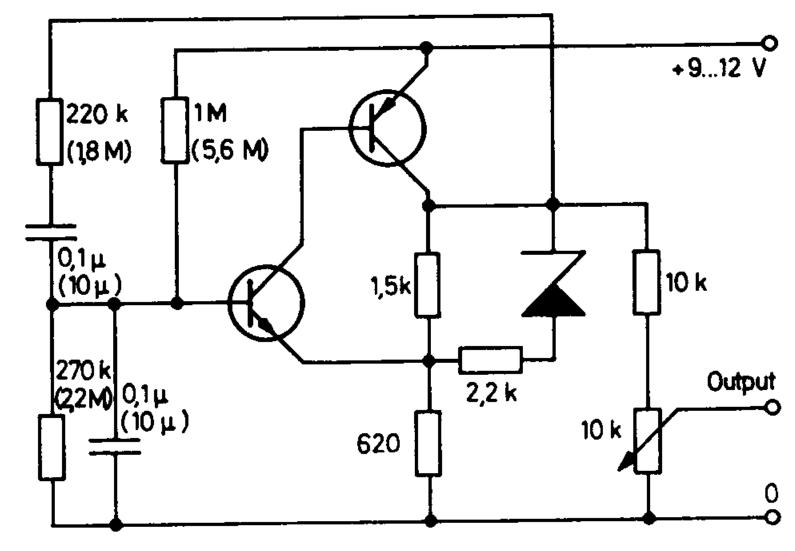

## Stabilizer for Low Battery Voltages

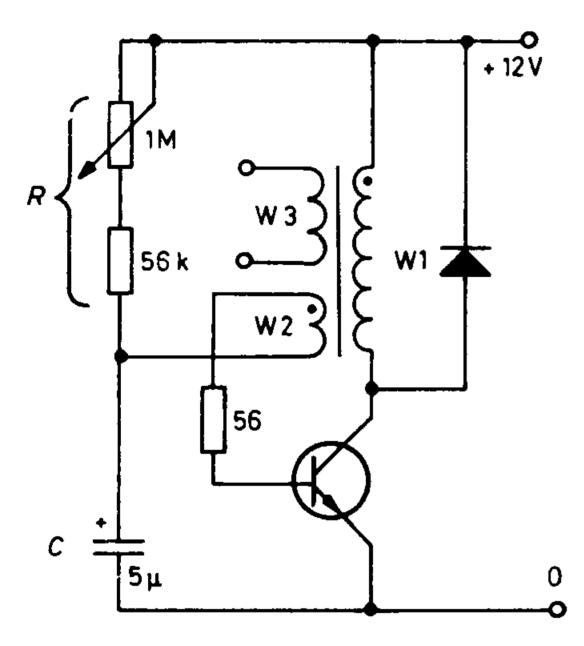

The terminal voltage of a monocell can vary between 1.7 and 1.2 V, depending on the state of discharge. The stabilizer described below will be of use when the supply voltage of a battery-powered circuit is to be held reasonably constant during the life of the battery.

The value of the base resistor (1 M $\Omega$ ) for transistor T1 is governed by the product of the current gains of T1 and T3, and must be chosen so that the series transistor T3 is fully driven when T2, the control amplifier transistor, is cut off. Under normal operating conditions the collector current of T2 has just the right value to reduce the base current of T1 sufficiently to stabilize the output at 1.15 V.

The reference voltage of this circuit is the base-emitter voltage of transistor T2 (approximately 420 mV at 1  $\mu$ A collector current). The output voltage depends on the ratio of R2 to R3 and is

$$V_{out} = V_{BE} \cdot \frac{R2 + R3}{R3} \approx 1.15 \text{ V}.$$

The output voltage remains stabilized for load currents up to approximately 5 mA, but higher load currents can be drawn if R1 is reduced. The output resistance is approximately  $1\dots 2\ \Omega$ . An input voltage variation from 1.2 to 1.8 V causes the output voltage to vary by not more than approximately 70 mV.

18. Stabilizer for low battery voltages

.

#### **Contents**

|     |                                                           | Page |

|-----|-----------------------------------------------------------|------|

| 1.  | General-Purpose AF Amplifier                              | 52   |

| 2.  | Recording Response Equalizer with Rumble and Noise Filter | 54   |

| 3.  | AF Preamplifier with Tone and Volume Controls             | 58   |

| 4.  | Presence Filter                                           | 60   |

| 5.  | Low-Power Complementary Series Push-Pull Output Stage     | 62   |

| 6.  | Single-Ended 1.5 W Class A Amplifier                      | 64   |

| 7.  | Series Push-Pull 2 W Class B Amplifier                    | 66   |

| 8.  | 2 x 6 W Amplifier Conforming to DIN 45 500 (HiFi)         | 68   |

| 9.  | 60 W Amplifier with Output Power Switching Facilities     | 70   |

| 10. | Transformer-Coupled 8 W Push-Pull Class B Amplifier       | 74   |

| 11. | Telephone Pick-Up Amplifier                               | 76   |

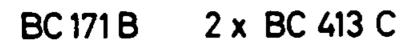

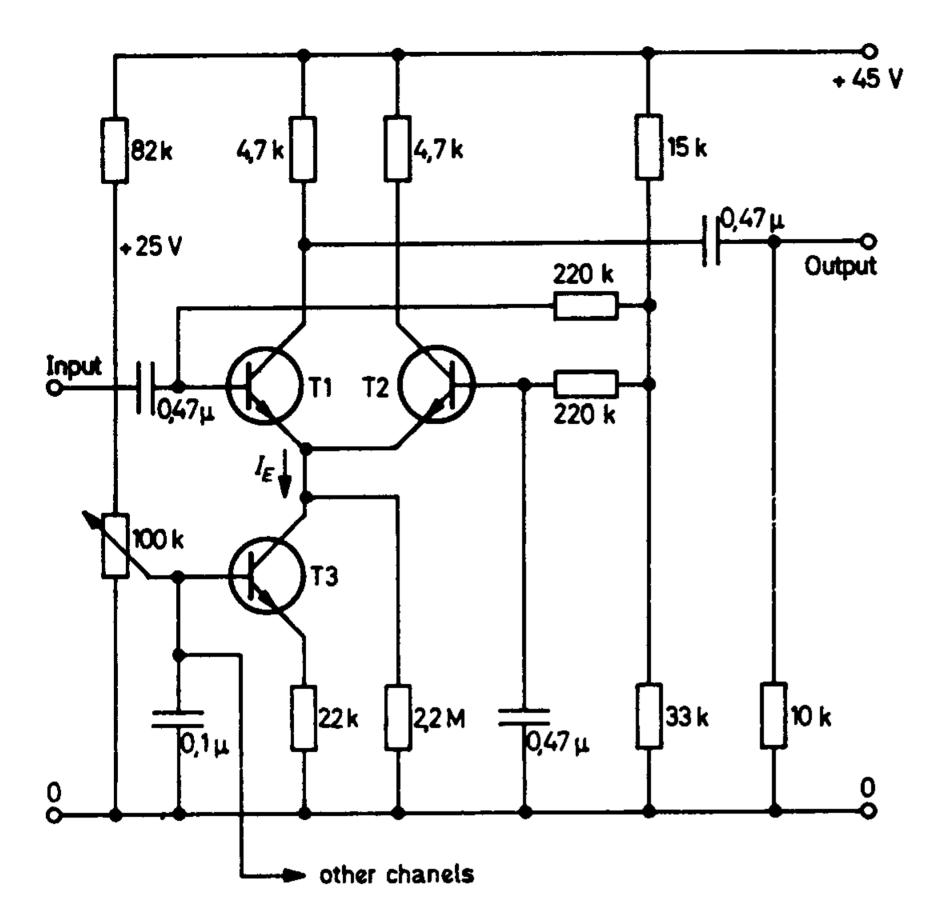

| 12  | Electronic Gain Control Circuit                           | 78   |

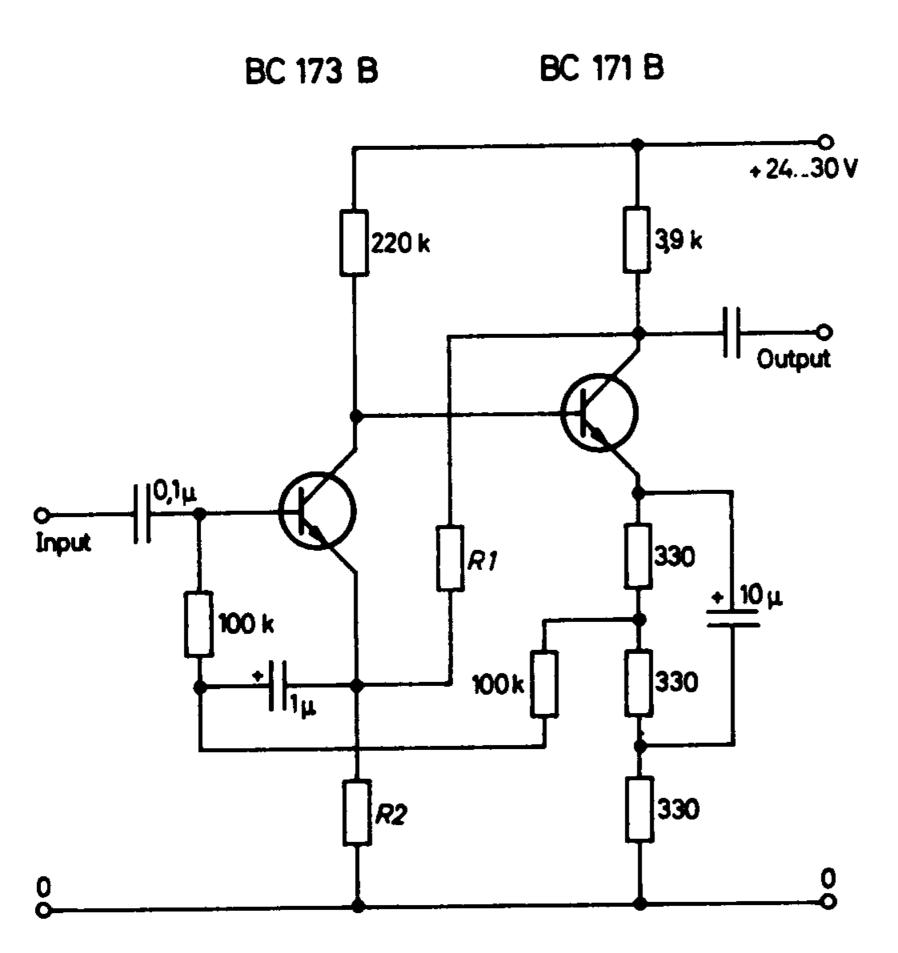

#### General-Purpose AF Amplifier

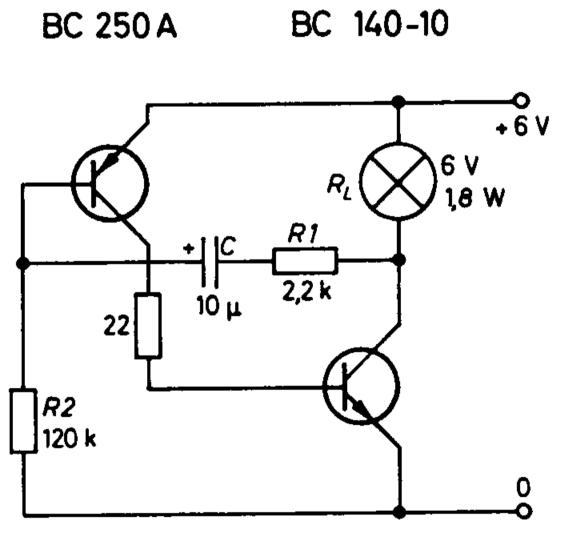

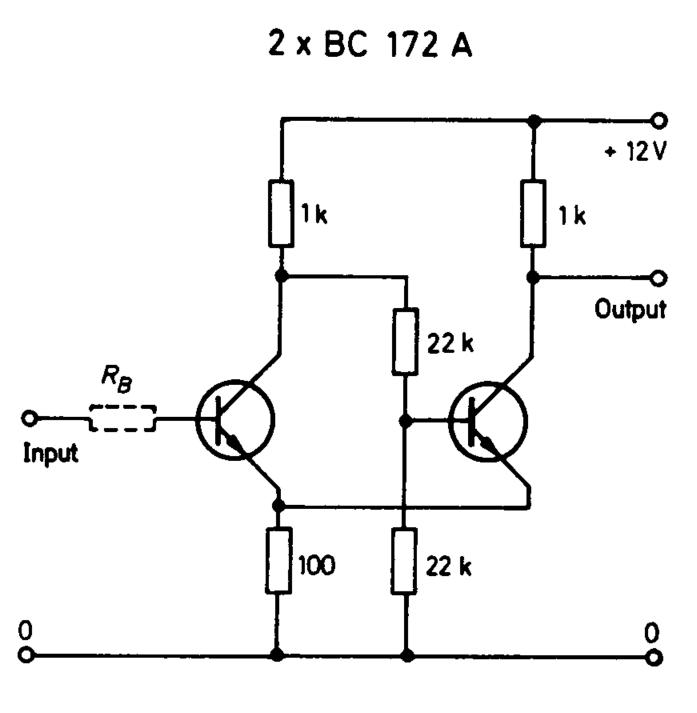

The circuit shown in Fig. II. 1. is that of a general-purpose two-stage AF amplifier which is directly coupled, to save components. Use of two DC negative feedback loops — one from the emitter of the second transistor to the base of the first, and the other one from the collector of the second transistor to the emitter of the first — stabilizes the operating point of the amplifier to such an extent that it is largely independent of voltage and temperature changes as well as transistor parameter spreads.

The voltage gain of the amplifier depends almost entirely on the attenuation of the negative feedback voltage divider interposed between the collector of the second transistor and the emitter of the first, and is, therefore, also very stable and quite unaffected by the factors mentioned above. The table below lists various gain and input impedance figures and the associated component values.

| Voltage Gain<br>Factor | Voltage Gain<br>in dB | R1<br>kΩ | R2<br>kΩ | Input<br>Impedance<br>MΩ |

|------------------------|-----------------------|----------|----------|--------------------------|

| 10                     | 20                    | 39       | 3.9      | 2                        |

| 20                     | 26                    | 47       | 2.2      | 1                        |

| 50                     | 34                    | 100      | 1.8      | 0.35                     |

| 100                    | 40                    | 100      | 0.91     | 0.2                      |

Practically any frequency response can be attained if the resistive feed-back network is replaced by a reactive one, such as an RC network. This principle is used, for example, in the recording response equalizer described further on. Another feature of this amplifier is that any unwanted open loop gain is reduced by application of negative feedback, with a consequent reduction in distortion.

The amplifier described will perform just as well with NPN transistors, such as the types BC 253 and BC 251, but in this case the polarity of the supply and that of the electrolytics must be reversed.

The current consumption of the amplifier is approximately 3 mA, and the output impedance is approximately 1  $k\Omega$ . The value of the output coupling capacitor depends on the input impedance and LF response requirements of the following amplifier.

1. General-purpose AF amplifier

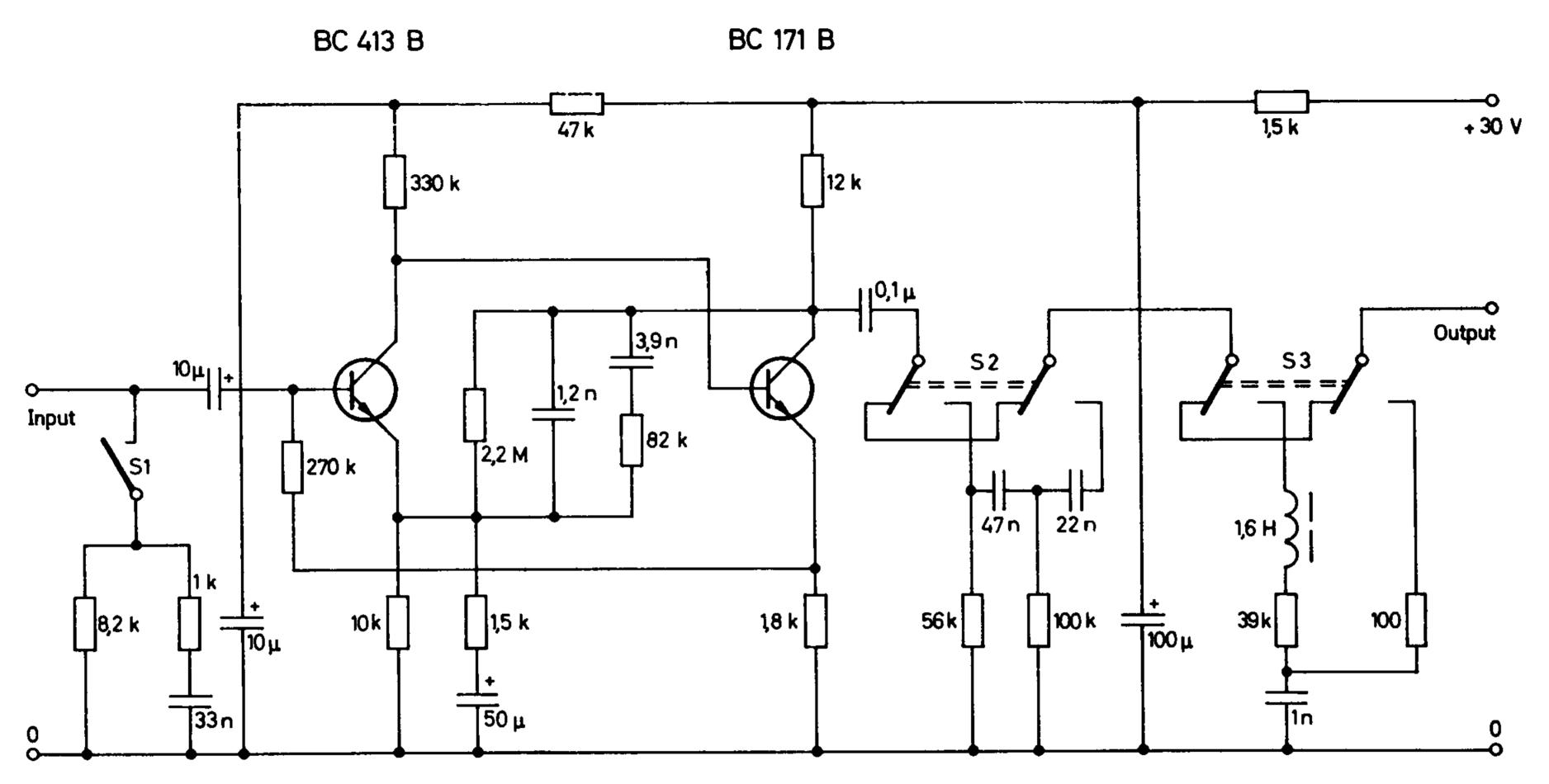

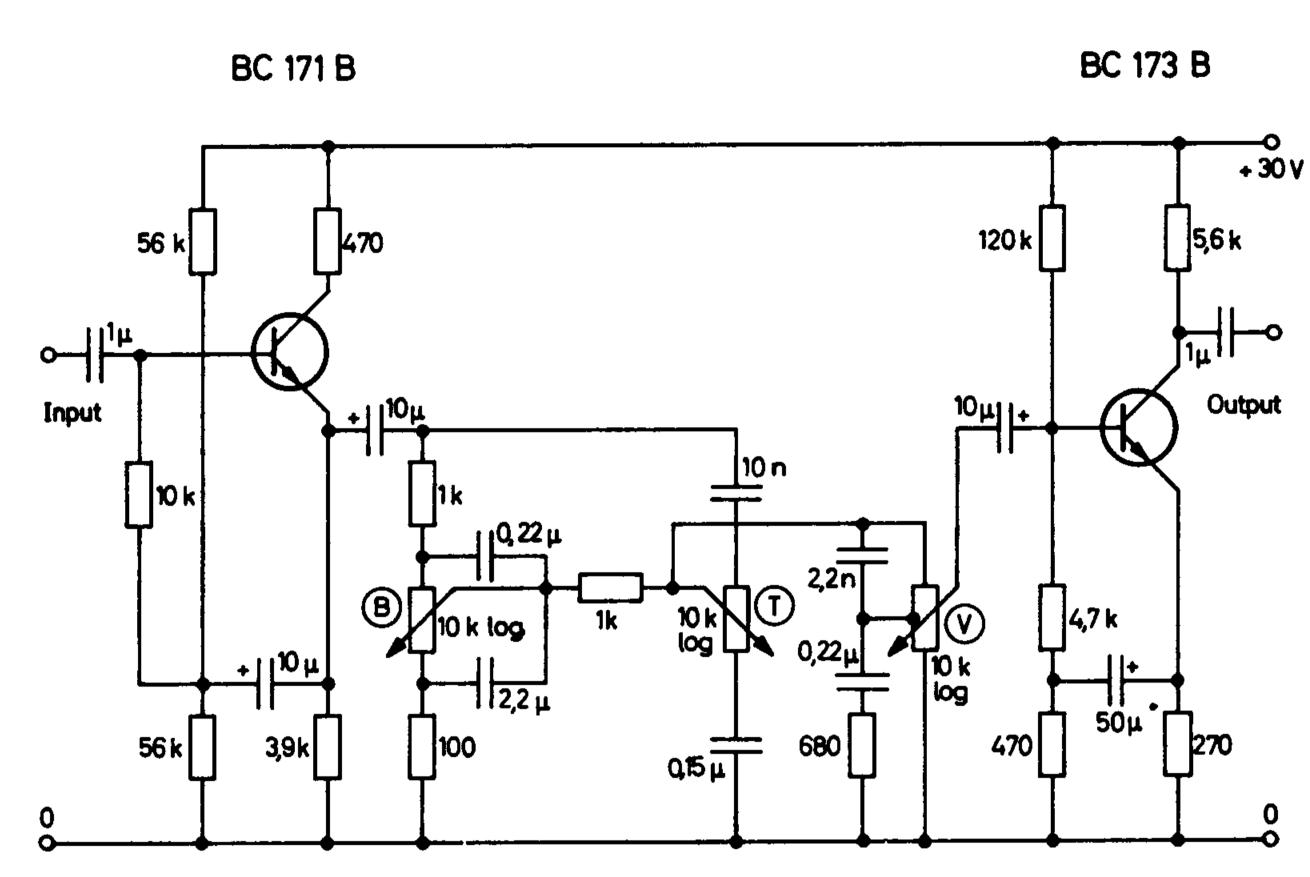

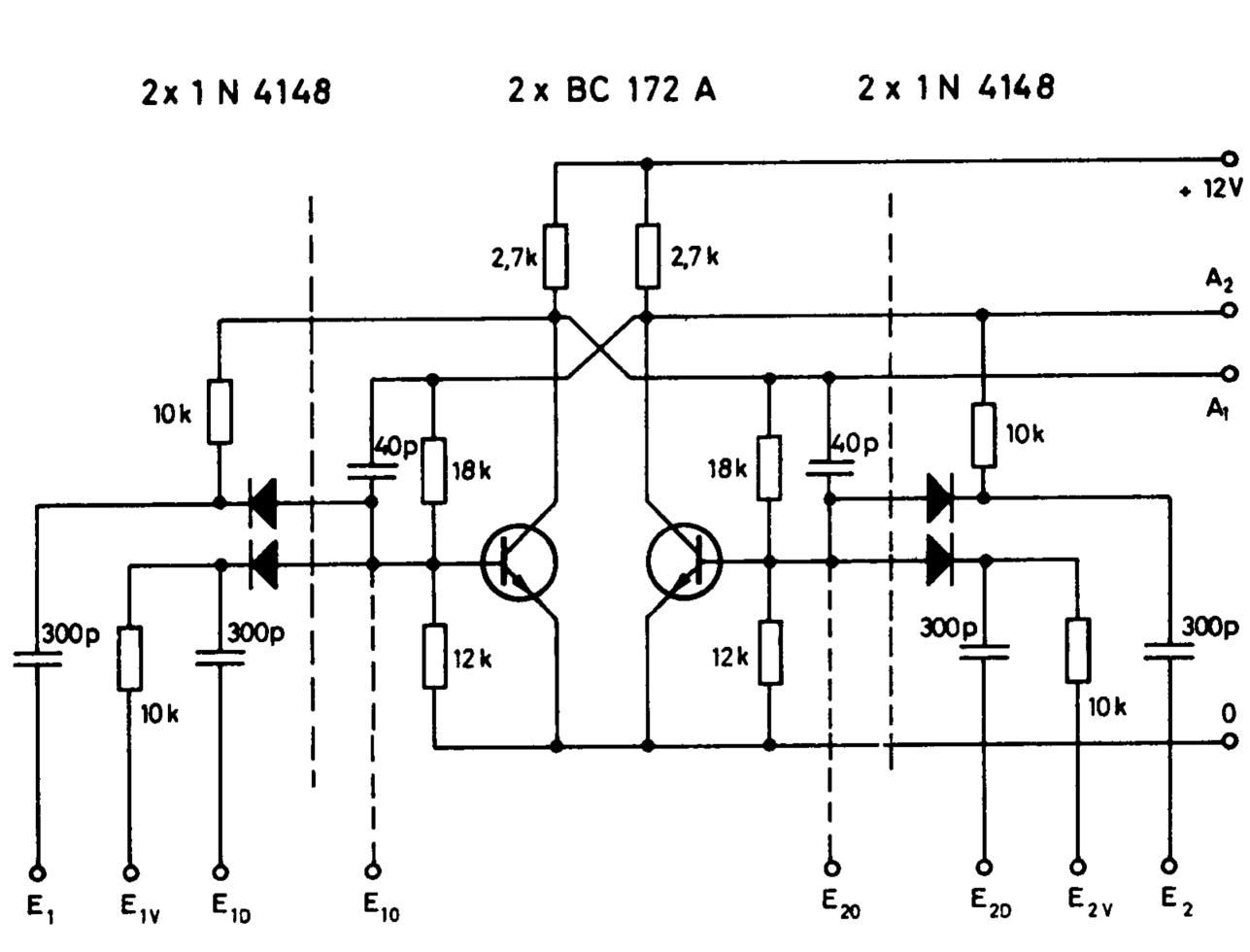

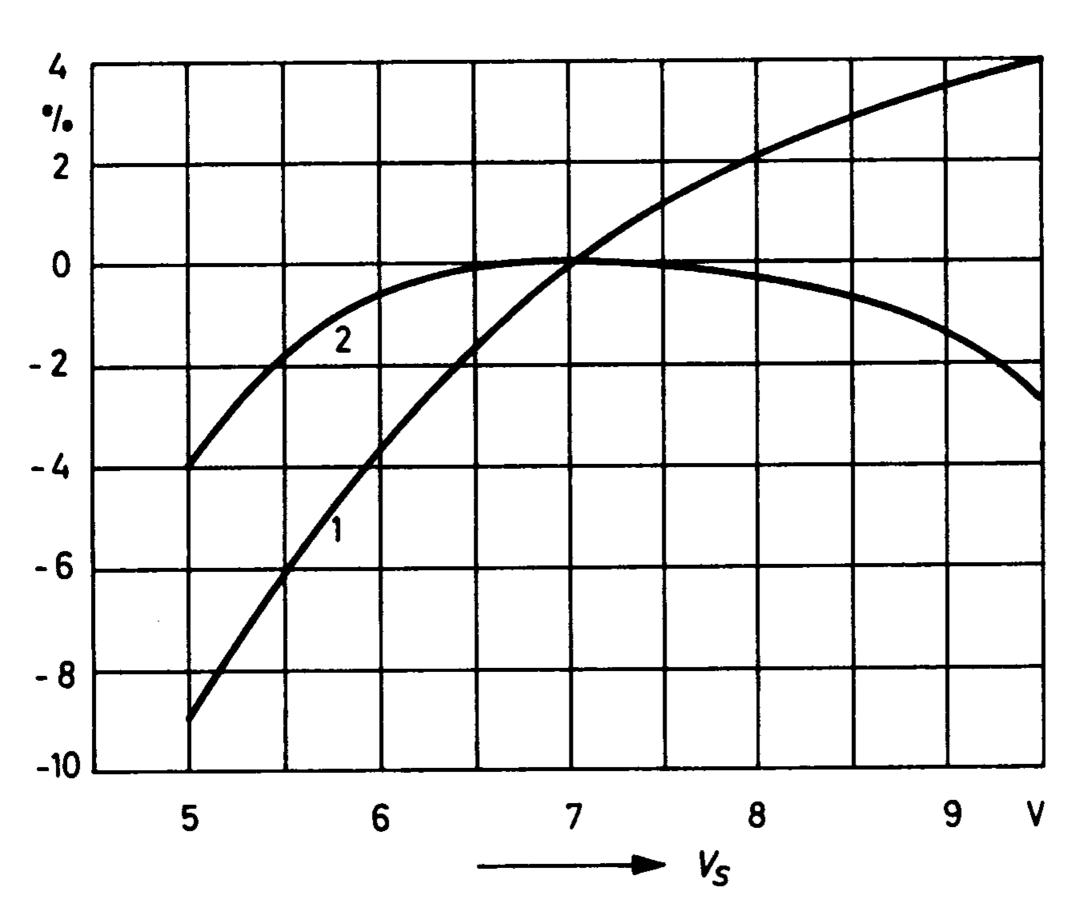

## Recording Response Equalizer with Rumble and Noise Filter

A non-linear frequency response in AF amplifiers is often desirable, or even necessary. The lifting and cutting of certain frequency bands is effected by the use or RC or LC networks, the methods by which this can be achieved being demonstrated in this and the two following circuits.

In disk recording, to save space on the disk, the low frequencies are recorded at a lower amplitude than the high ones, in accordance with a standardized recording response (DIN 45 546, DIN 45 547). If such a recording is to be reproduced via a magnetic pickup, then the playback amplifier must have a response which is the inverse of the recording response.

The equalizer/amplifier, which is basically that described in II. 1. incorporates two directly coupled common emitter stages. There is no special base bias network for the input transistor, base bias being derived from the emitter of the following transistor.

Two negative feedback loops, one from the collector of the second transistor to the emitter of the first, and the other one from the emitter of the second transistor to the base of the first, as well as local negative current feedback, ensure that the operating points of both stages are well stabilized. The design of the network is such that more feedback is applied at the higher than at the lower frequencies, thus providing the required bass lift.

Magnetic pickups produce a velocity-proportional EMF (deflection velocity of the needle), while crystal pickups produce an amplitude-proportional EMF. The equalizer/amplifier, which, in the described form, is suitable for the connection of a magnetic pickup, can be modified for use with a crystal pickup simply by providing a switch S1 which connects an RC network across the input.

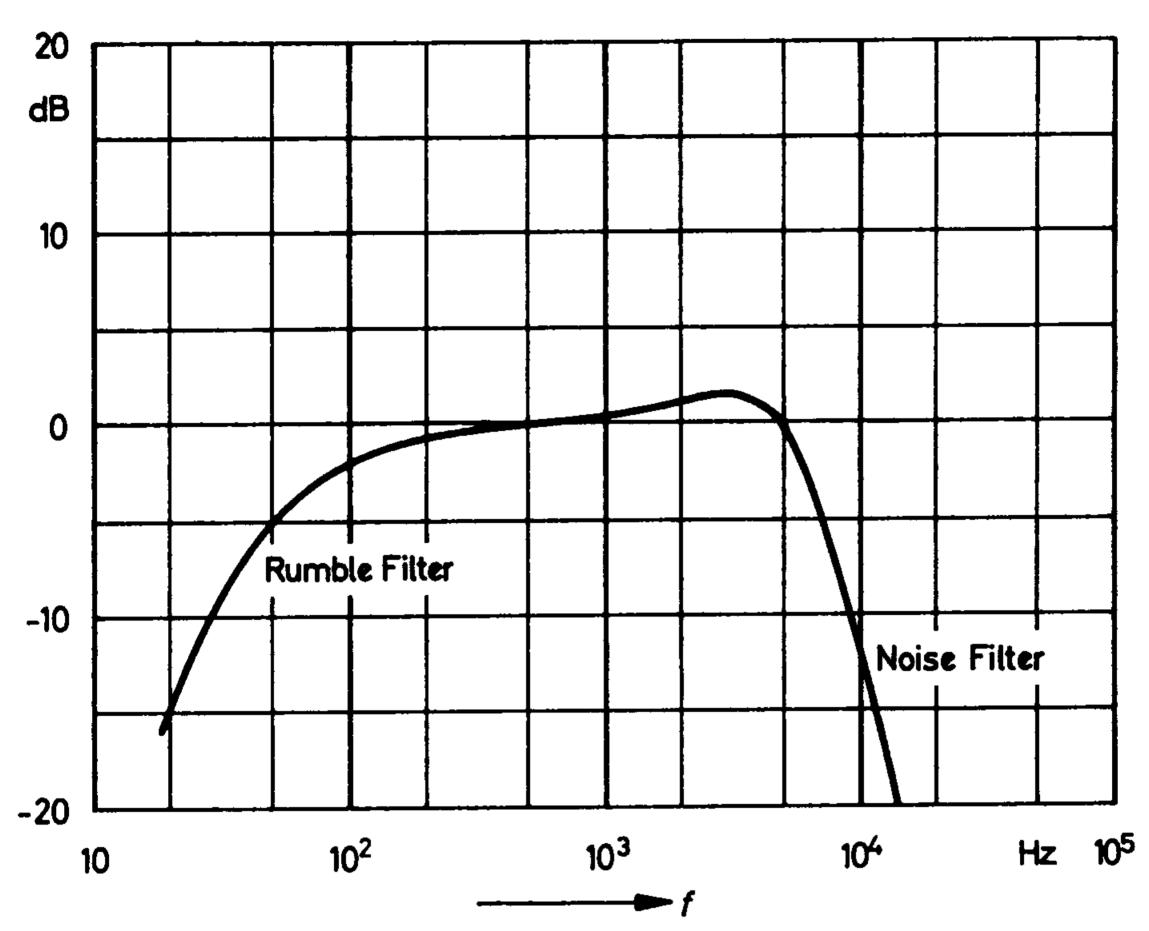

Another switch S2 brings into circuit a rumble filter which attenuates all frequencies below 30 Hz and is an example of how the frequency response of an amplifier can be modified by use of an RC highpass filter.

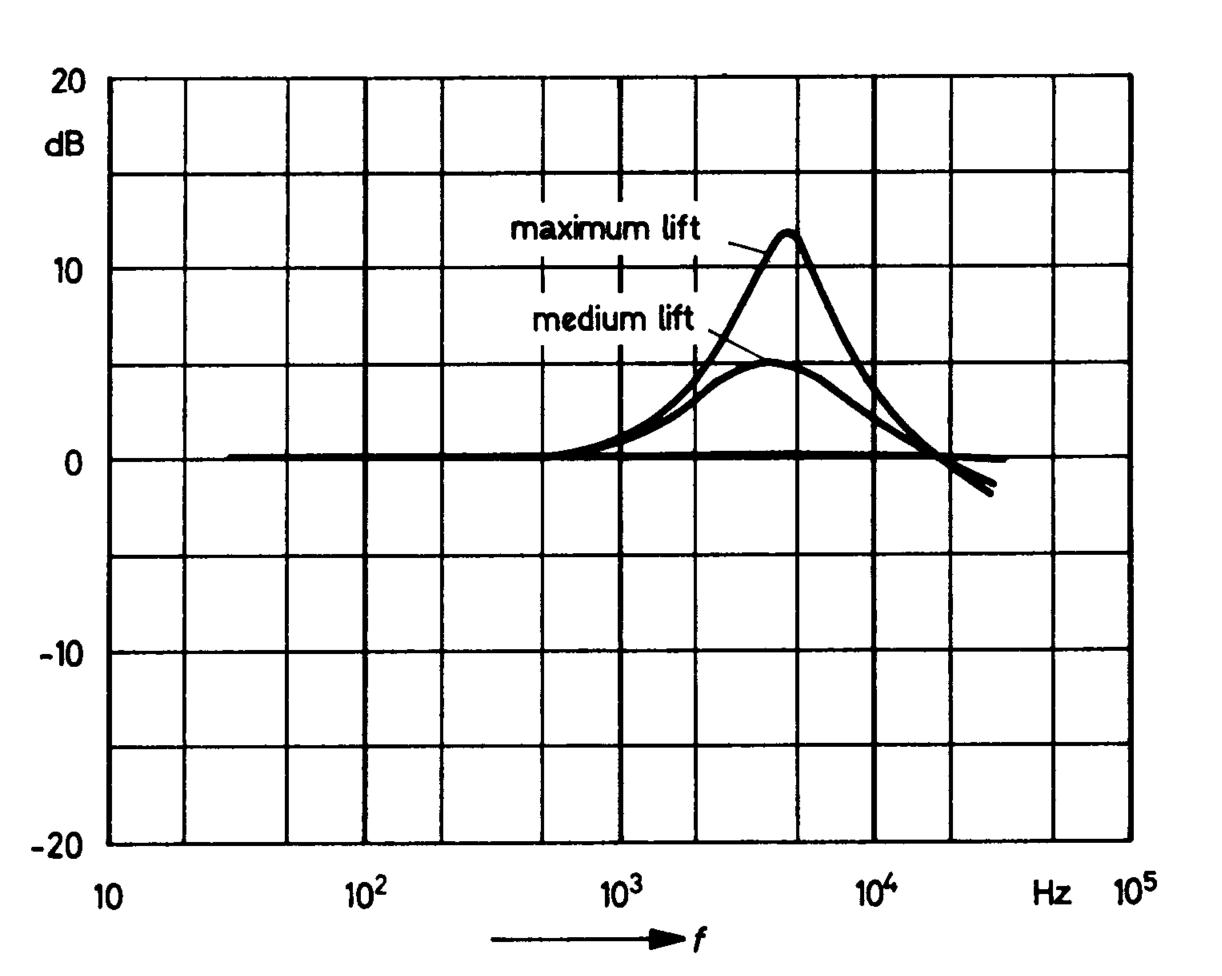

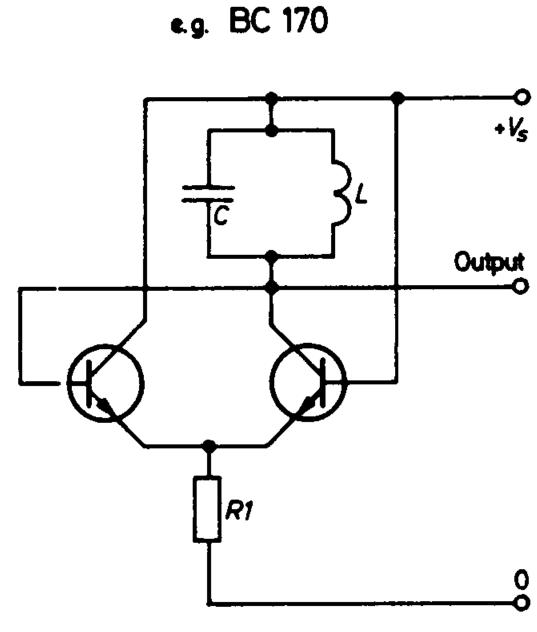

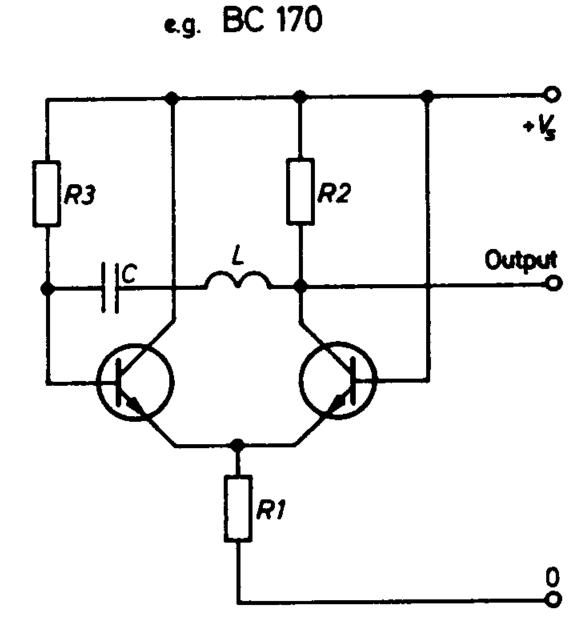

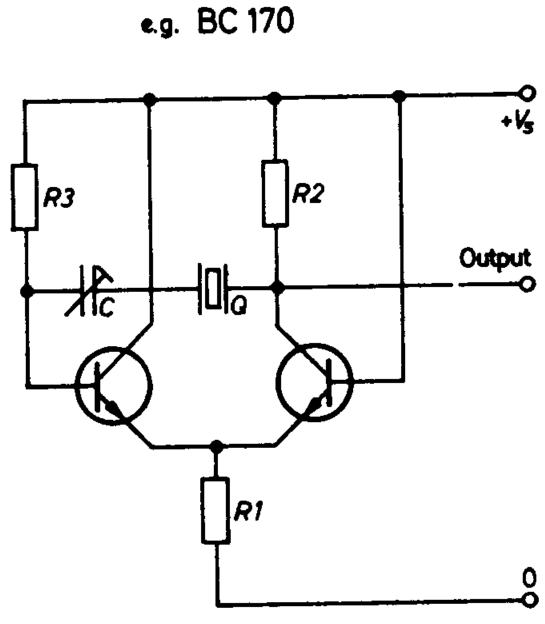

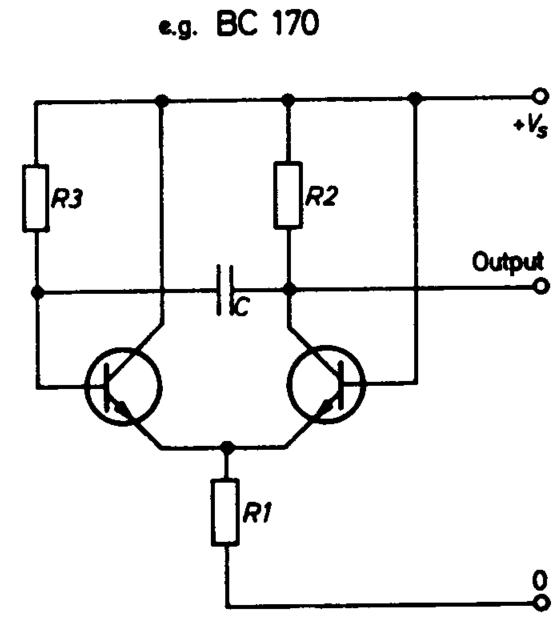

Switch S3 connects into circuit an LC noise filter, comprising a series-resonant circuit tuned to approximately 4 kHz; this circuit is heavily damped so as to produce only a slight lift in response about the resonant frequency, whilst signals above resonance are rapidly attenuated.

The amplifier, which has a current consumption of approximately 1 mA, provides a gain of approximately 50 ( $\triangleq$  34 dB) at 1 kHz, so that an input of 10 mV (magnetic pickup) produces an output of 500 mV. However, the amplifier can be driven up to an output level of 4 V to comply with the

2 a. Recording response equalizer with rumble and noise filter

12 dB overload reserve requirement laid down in DIN 45 500. The distortion factor is less than 0.5 %, and the output resistance is of the order of several  $k\Omega$ , which means that the input impedance of any following amplifier should be not less than 50  $k\Omega$ .

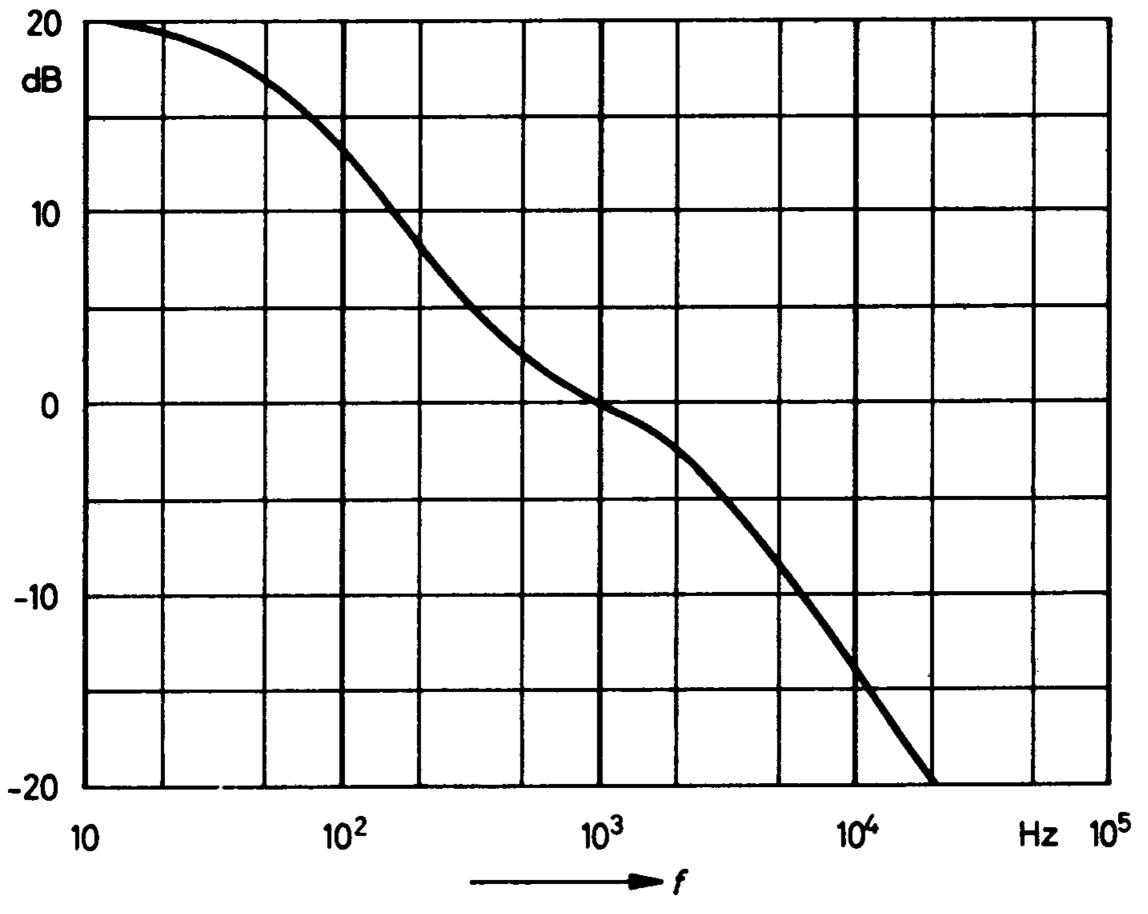

2b. Equalizer response

2 c. Response of rumble and noise filter without amplifier

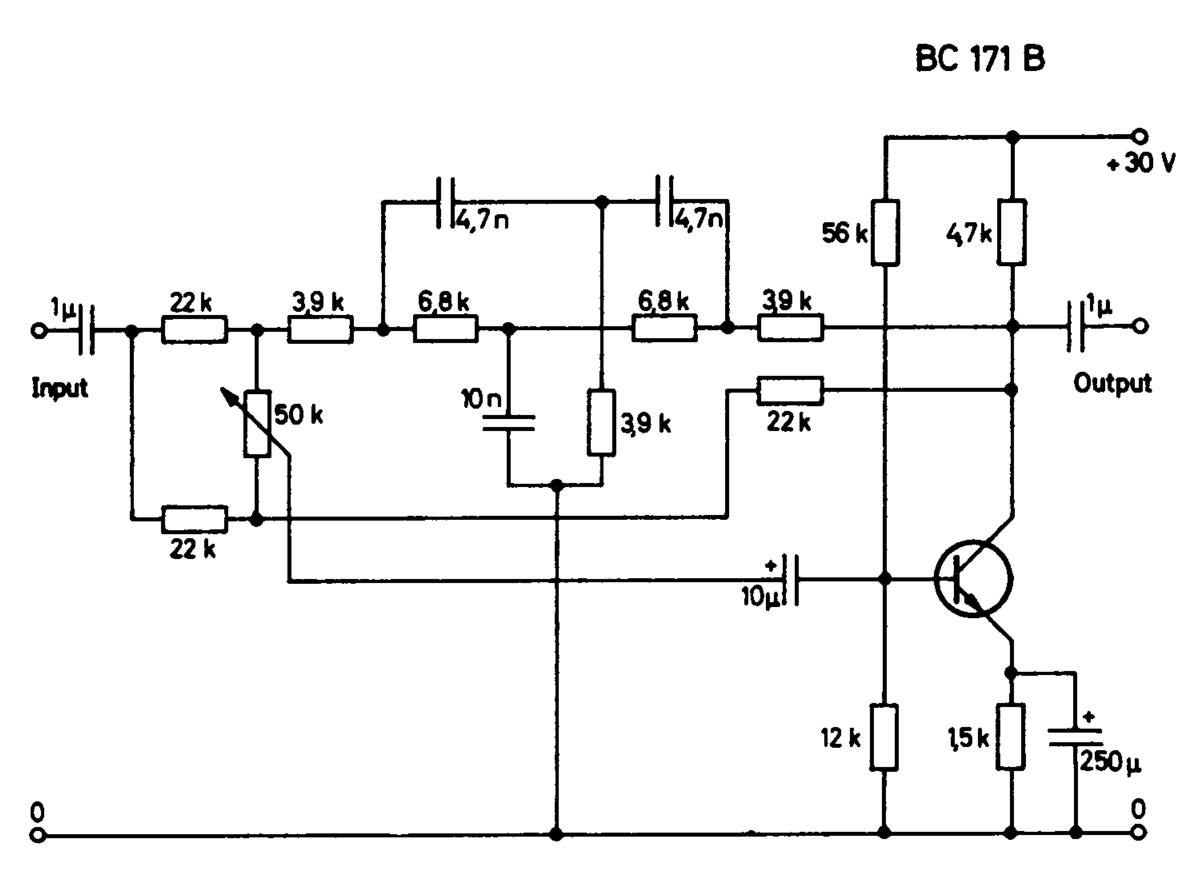

#### AF Preamplifier with Tone and Volume Controls

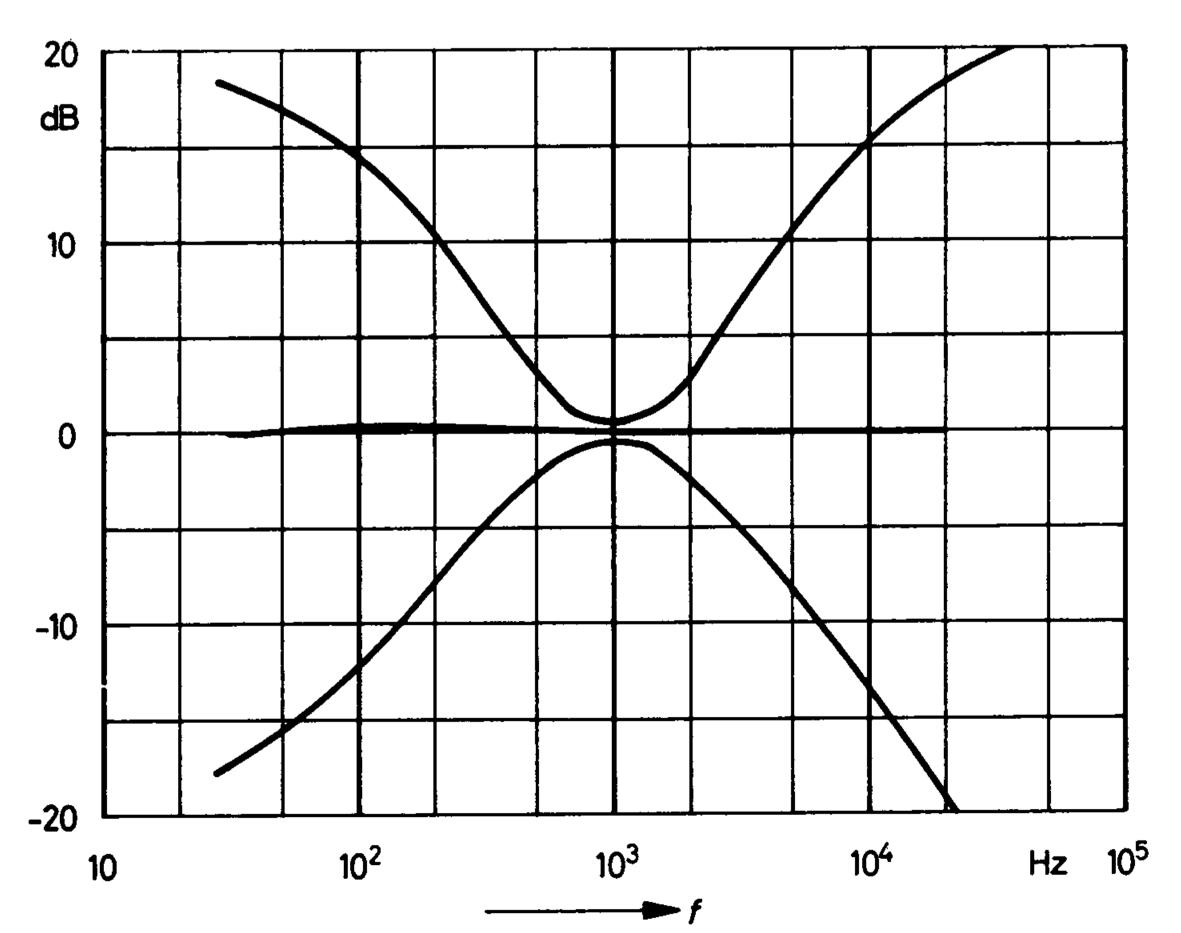

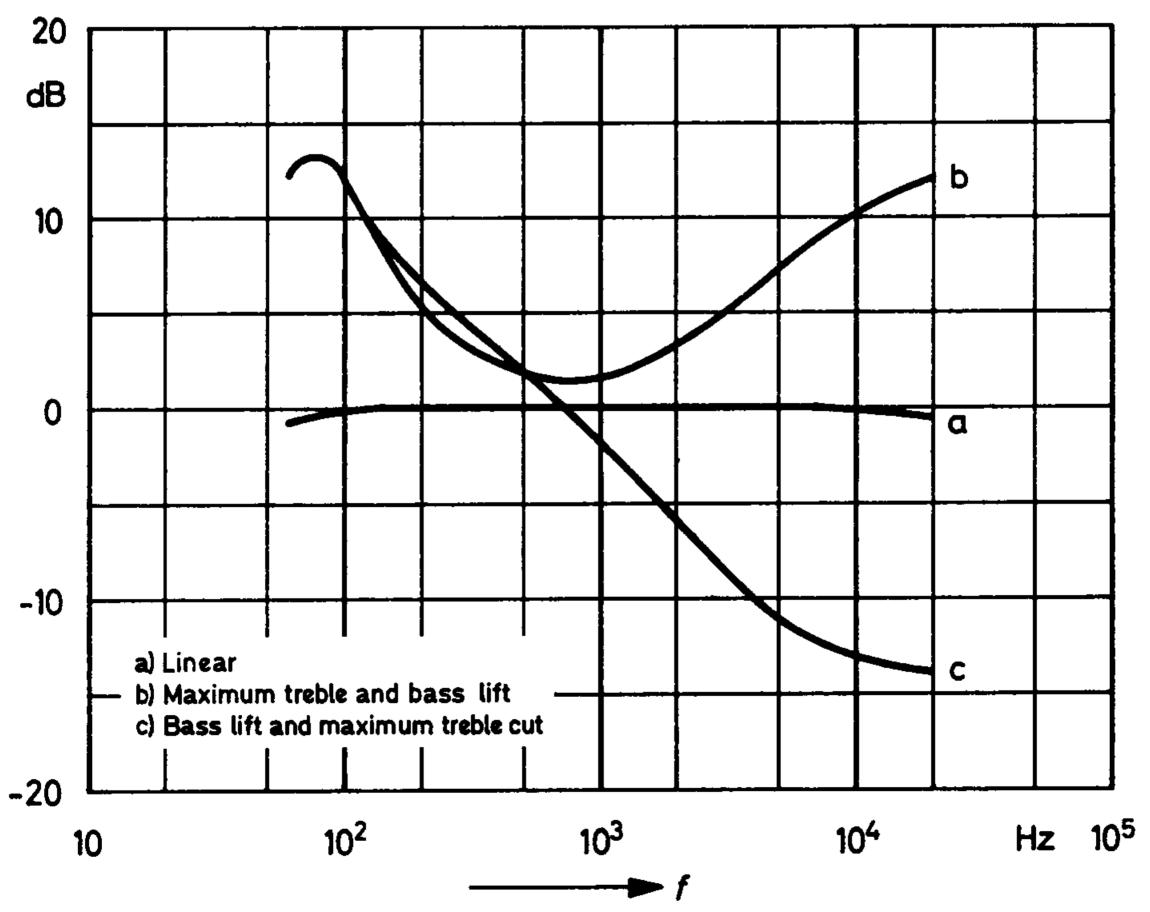

This circuit incorporates an impedance converter to match the relatively low impedance of the tone control network to the output impedance of the preceding stage (circuit II. 2. for example). The network, to which a signal derived from the emitter of the input transistor is applied, incorporates two potentiometers to provide separate treble and bass adjustment facilities. A third potentiometer acts as a physiologically correct volume control.

Because the networks affect the signal amplitude (i. e. the volume) as well as the frequency response, a voltage amplifier stage is provided to restore the signal to the original level. The emitter resistor of this stage is not bypassed, so that local AC as well as DC negative feedback is applied, thereby reducing any distortion and increasing the input impedance of the stage (this is further increased by "bootstrapping" the base-bias divider to the emitter via a 50  $\mu$ F capacitor — see circuit II. 1.).

A voltage gain of approximately 20 is provided by the second stage, so that if the 20 dB loss introduced by the tone control network is taken into consideration, the overall gain, with the volume control at maximum, is 2. The input impedance is greater than 100 k $\Omega$ , and the output impedance is approximately 5 k $\Omega$ . The amplifier draws a current of approximately 7 mA.

If circuit II. 3. is driven by the output of circuit II. 2. then the input coupling capacitor can be omitted.

3 a. AF Preamplifier with tone and volume controls

3b. Tone control network response curves

#### Presence Filter

The tone control network of circuit II. 3. incorporates separate bass and treble controls. In the reproduction of speech, however, it may be desirable to emphasize the centre frequencies and attenuate those in the treble and bass ranges. This can be achieved by use of the network described below which incorporates only a single potentiometer. The filter employs a common emitter transistor stage. As in circuit II. 2. negative feedback is applied (this time from collector to base) via a frequency-selective network, which gives the circuit its bandpass characteristic. The network is designed to pass the high and low-frequency signals and to attenuate the mid-frequency signals, resulting in a response in which the high and low frequencies are attenuated relative to the midband frequencies. When the wiper of the 50 k $\Omega$  potentiometer is near the bottom end, the frequency response of the amplifier is almost flat; when it is at the top end, however, the centre frequency band from  $4\dots 5$  kHz is lifted by approximately 12 dB.

The circuit presents an input impedance of approximately  $10 \text{ k}\Omega$  and an output impedance of approximately  $5 \text{ k}\Omega$ . Negative feedback reduces the basic gain to approximately 1, but this is increased to approximately 4 ( $\triangleq$  12 dB) in the middle of the band, when the control is set for maximum lift. The circuit has approximately 3 mA current consumption. The coupling capacitor can be omitted when circuit II. 4. is driven by the output of circuit II. 3.

4 a. Presence filter

4b. Presence filter response

## Low-Power Complementary Series Push-Pull Output Stage

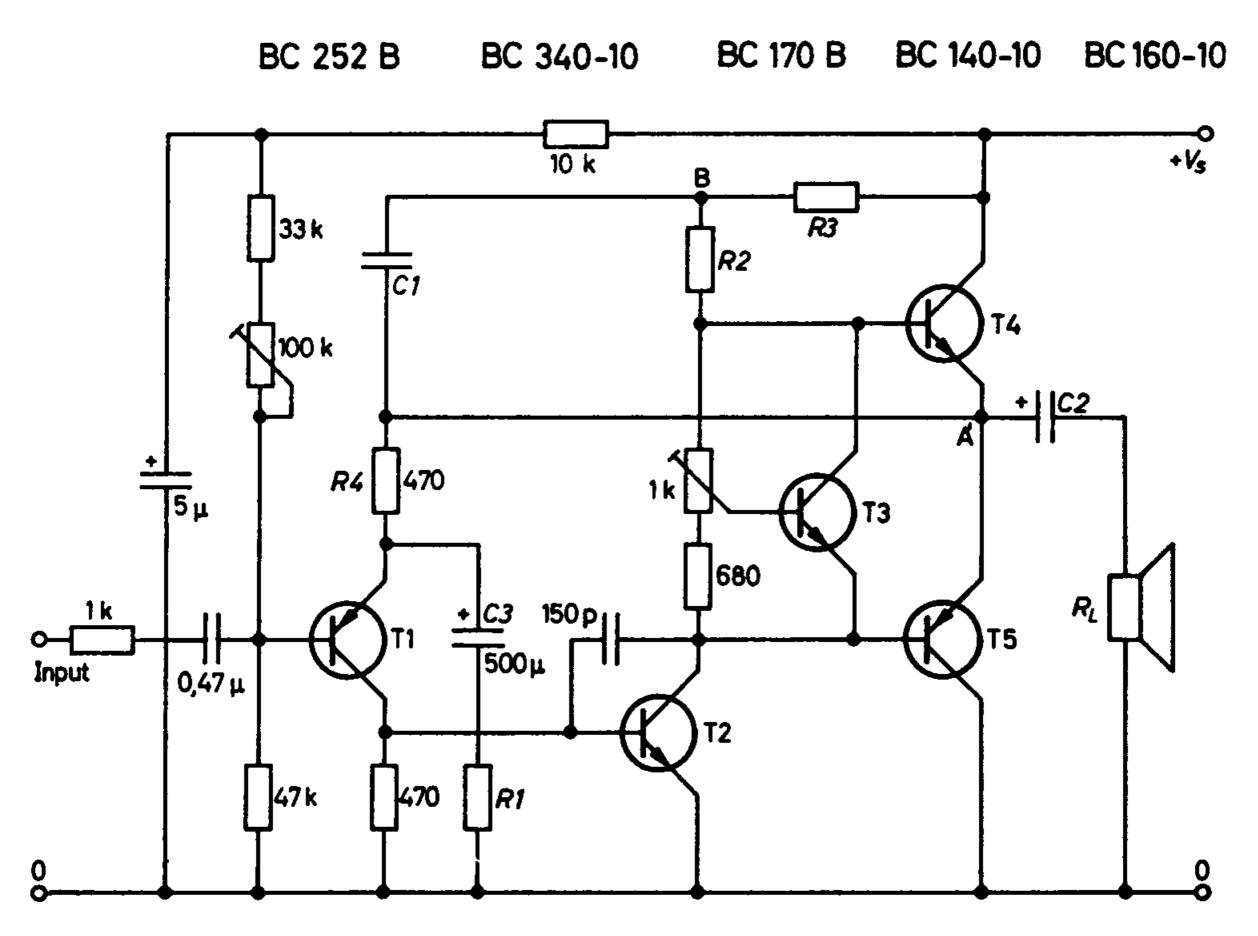

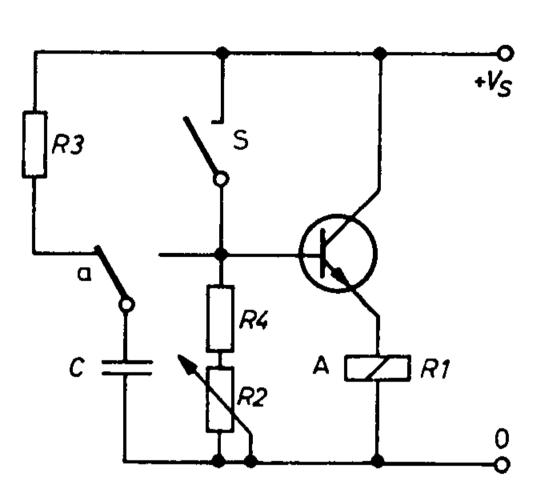

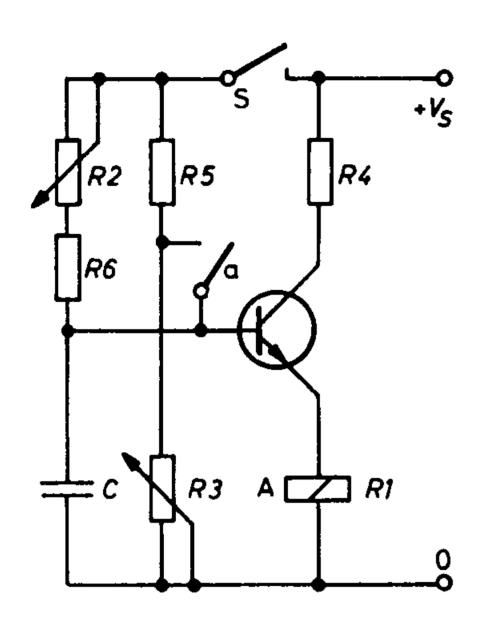

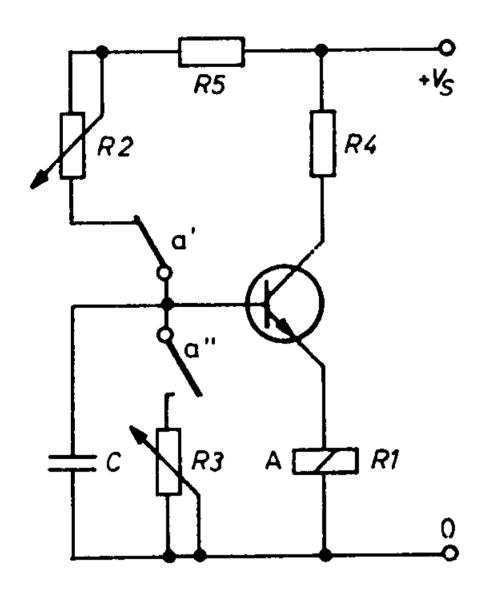

The circuit shown is that of a simple low-power series push-pull output stage. The operating point of the amplifier, which employs direct coupling throughout, is stabilized by application of negative DC feedback from the output, via R4, to the emitter of the first transistor. Capacitor C3 and resistor R1 reduce the amount of negative AC feedback to the required value.

A "bootstrap" arrangement (capacitor C1 connected between point 'A' and the R2/R3 junction) ensures that the limit of maximum positive signal swing is solely dependent on the saturation voltage of transistor T4. Transistor T3, in conjunction with the setting of the 1 kΩ potentiometer, determine the magnitude of the quiescent current through the output stage. To adjust this current, connect a meter in the collector lead of T4 and initially set the  $1\,k\Omega$  potentiometer for minimum resistance between the wiper and T3 collector. Now increase this setting until a quiescent current of 15...20 mA is attained. T3 also effectively stabilizes the quiescent current against ambient temperature and supply voltage variations. Adjustment of the 100 kΩ potentiometer affects the operating point of the output stage; the potentiometer should be set so that when the amplifier is over-driven with a sinusoidal signal, the positive and negative signal peaks are clipped by the same amount (this occurs when the DC voltage measured at point 'A' is equal to the supply voltage divided by 2).

The 150 pF capacitor and the 1  $k\Omega$  resistor in series with the input suppress any RF instability.

For a given load resistor  $R_L$  and an assumed output transistor saturation voltage of 0.7 V, the attainable output power depends above all on the supply voltage:

$$P_{out} = \frac{(V_S - 1.4 \text{ V})}{8 R_L}$$

On the other hand, the maximum permissible collector peak current should not be exceeded, so that

$$P_{out} = 0.5 \cdot I_{Cmax}^2 \cdot R_L$$

The lower of these two values is the output power that can be attained in practice. It should be noted, however, that an output transistor collector current of  $I_{CM} = 0.6$  to  $0.8 I_{Cmax}$  should not be exceeded, otherwise the output stage would require too much drive power.

The values of the components used in the negative feedback voltage divider are chosen so that the amplifier is fully driven with an input of 0.1 V. The input impedance is  $20 \text{ k}\Omega$ , and the signal distortion at full rated output power is less than 1%. Table 1 lists the component values necessary to attain this performance, whilst table 2 gives the maximum attainable output levels.

## 5. Complementary series push-pull output stage

Table 1: Amplifier component values

| Component        | $R_L \Omega$ | $V_S = 6 V$ | $V_S = 9 V$ | $V_S = 12 V$ |

|------------------|--------------|-------------|-------------|--------------|

|                  | 4            | 27          | 15          | _            |

| R1 Ω             | 8            | 27          | 15          | 10           |

|                  | 16           | -           | 15          | 10           |

| <del></del>      | 4            | 47          | 47          | _            |

| $R2 = R3 \Omega$ | 8            | 100         | 100         | 100          |

|                  | 16           |             | 220         | 220          |

|                  | 4            | 100         | 100         |              |

| C1 μF            | 8            | 50          | 50          | 50           |

| •                | 16           | _           | 25          | 25           |

|                  | 4            | 1000        | 1000        |              |

| C2 μF            | 8            | 500         | 500         | 500          |

| •                | 16           | -           | _           | 250          |

Table 2: Attainable output power Pout

| $R_L \Omega$ | $V_S = 6 V$ | $V_s = 9 V$ | $V_S = 12 V$ |  |

|--------------|-------------|-------------|--------------|--|

| 4            | 0.6 W       | 1.5 W       |              |  |

| 8            | 0.36 W      | 0.95 W      | 1.7 W        |  |

| 16           | -           | 0.48 W      | 0.87 W       |  |

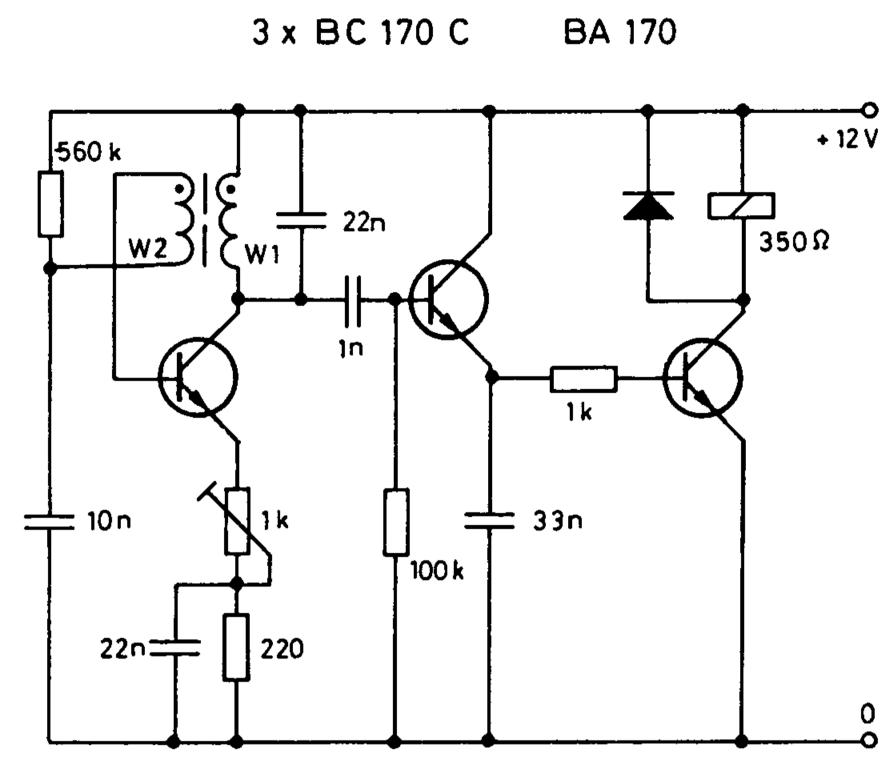

# Single-Ended 1.5 W Class A Amplifier

The circuit of this amplifier is basically that described in II.1. Two directly coupled stages are employed in which the base current of the first stage is derived from the emitter of the second. The large amount of negative feedback introduced in this way ensures that the operating points of both stages are very stable.

Matching the loudspeaker impedance to that of the output transistor by means of an autotransformer has the advantage that a small core can be employed without degrading the frequency response. A negative feedback signal derived from a secondary winding on this transformer is applied to a frequency-selective network, whose transfer characteristic determines the overall gain as well as the frequency response of the amplifier — as discussed in II. 1. A speech-music switch and a treble control permit the tone character of the output to be adjusted as required.

The output transistor passes a quiescent current of approximately 350 mA and dissipates approximately 5 W. If the amplifier is to be operated at ambient temperatures up to +60 °C, then a heat sink with a thermal resistance not exceeding 10 °C/W should be used, e.g. a 100 cm² aluminium sheet 1 mm thick.

The amplifier has a current consumption of 400 mA; in the 100 Hz...20 kHz frequency range the distortion at 1.5 W output power is less than 3 %. An input of 250 mV is required for full output; the input impedance is approximately 10 k $\Omega$ .

#### **Transformer Data**

Core: El 38/14; type IV lamination, 2 x 0.2 mm air gap

Windings: W1 = 230 + 95 turns 0.4 mm dia. en. copper wire

W2 = 325 turns 0.1 mm dia. en. copper wire

Both windings bifilar wound.

6a. Single-ended 1.5 W class A amplifier

6b. Amplifier response curves

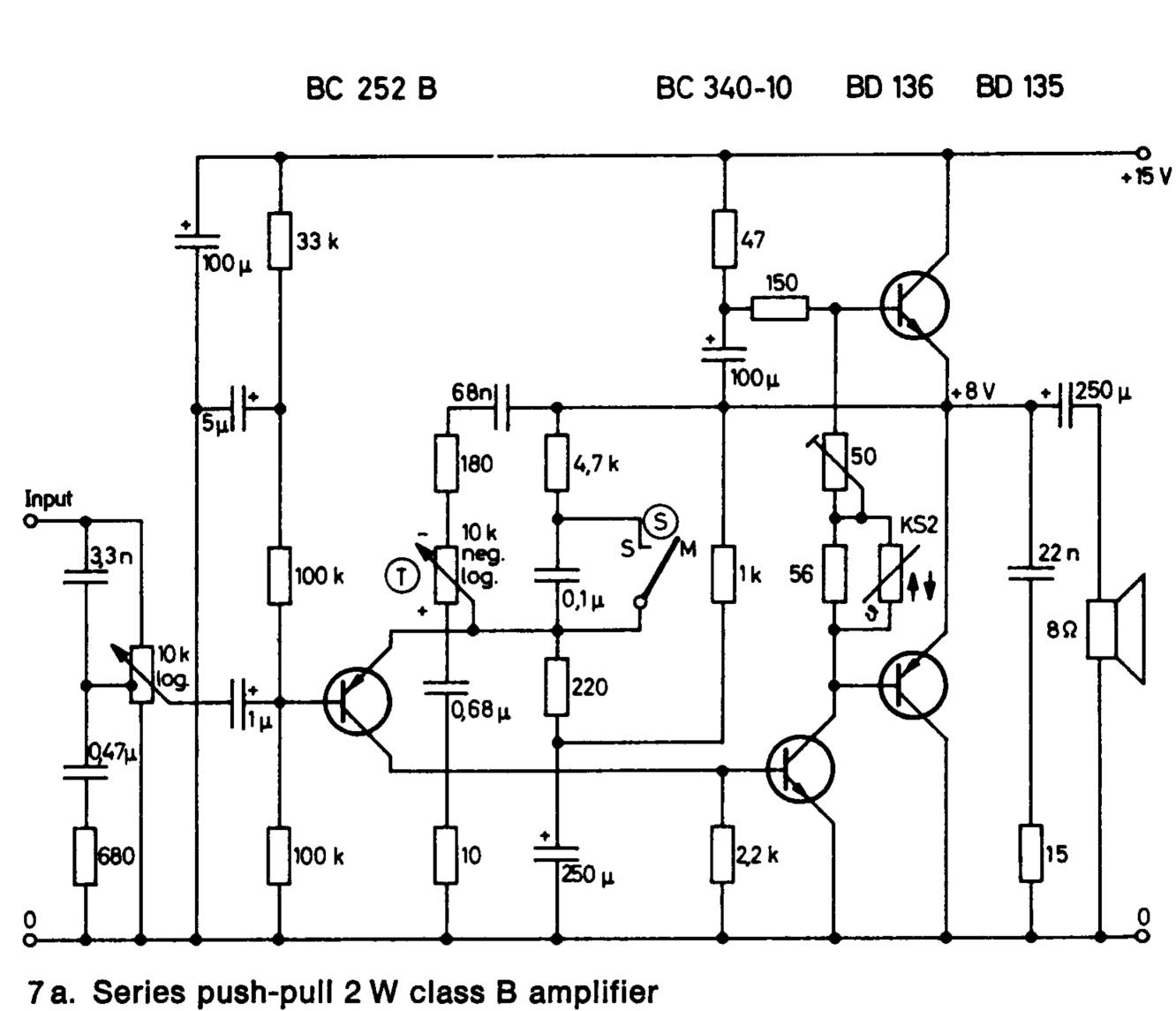

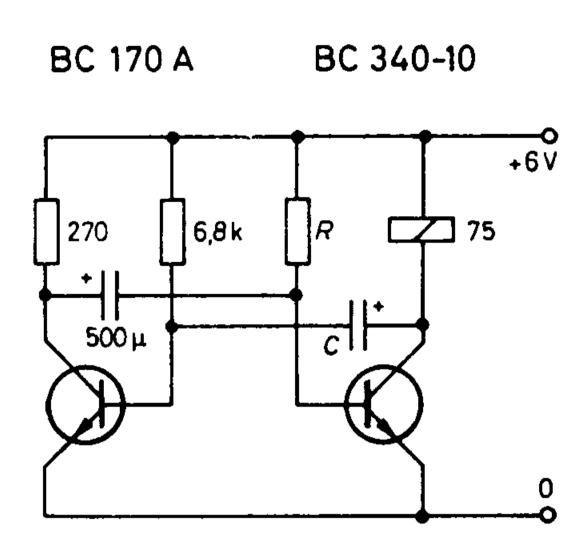

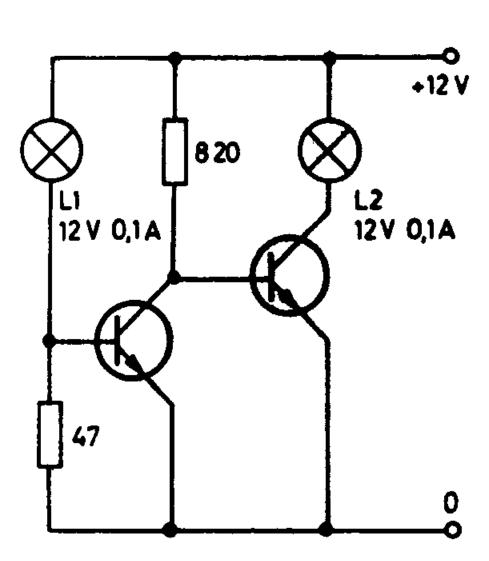

#### Series Push-Puil 2 W Class B Amplifier

This amplifier has the same performance as that described in II. 6. It employs two more transistors, but requires no output transformer and draws considerably less current. Also, the size of the heat sink (necessary for operation at ambient temperatures up to  $+60\,^{\circ}$ C) is considerably smaller, only a 25 cm² aluminium sheet of 1 mm thickness with a thermal resistance of 25 °C/W being required. Both transistors are mounted on the same heat sink.

The amplifier employs directly coupled negative feedback, which is effective over all three stages. A PNP transistor input stage is followed by an NPN transistor driver stage, which drives a series push-pull complementary symmetry output stage. A large amount of negative feedback from the amplifier output to the emitter of the input transistor ensures that the operating point is well stabilized. A 50  $\Omega$  potentiometer permits the quiescent current of the output stage to be set to 10 mA. The total quiescent current consumption of the amplifier is approximately  $40\ldots50$  mA, this current rising to approximately 300 mA under full drive conditions.

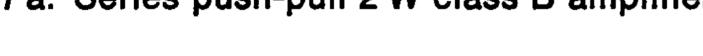

As in circuit II.6. a frequency selective negative feedback network is interposed between the amplifier output and the emitter of the input transistor. Also, as in the previous amplifier, a speech-music switch S and a treble control T are incorporated to permit the tone to be adjusted to individual taste.

In the frequency range 70 Hz ... 20 kHz and at 2 W output, the amplifier has less than 2 % distortion; it requires an input level of 200 mV for full output. The input impedance is approximately 10 k $\Omega$ .

7 b. Amplifier response curves

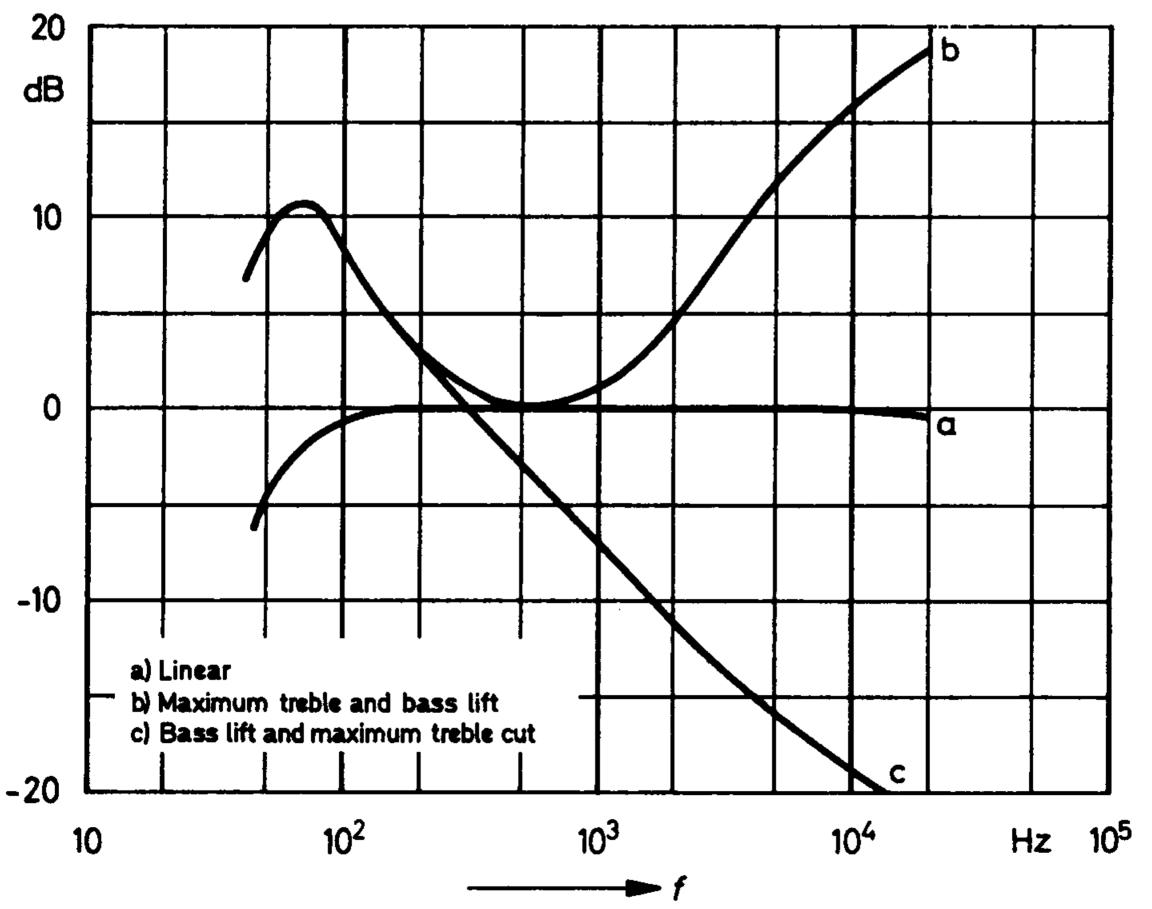

# 2 x 6 W Amplifier Conforming to DIN 45 500 (HiFi)

The circuit of this amplifier is very similar to that of II. 7. with the exception of the output stage which employs NPN transistors. Here the complementary-symmetry output stage of circuit II. 6. is utilized as a complementary-symmetry phase inverter to drive the NPN output stage (quasi-complementary circuit). This type of amplifier is used mainly for medium and high power applications.

Connected in a similar way as in circuits II. 6. and II. 7. the tone control network incorporates two potentiometers, one for continuous treble and one for continuous bass adjustment. They form part of a network in the negative feedback path from the amplifier output to the emitter of the input transistor, and give approximately  $\pm$  12 dB treble and bass level variation (at 10 kHz and 100 Hz respectively) with reference to the 1 kHz level.

The operating point is stabilized by use of negative DC feedback applied via the same path. Careful circuit design has made it possible to dispense with a stabilized power supply (usually required for class B amplifiers) and to employ no more smoothing than that provided by a single reservoir capacitor. The quiescent current of the output stage is stabilized against supply and ambient temperature variations by diodes. Each output transistor requires a heat sink with less than 15 °C/W thermal resistance. Alternatively all four output transistors can be mounted on a common heat sink, in which case the thermal resistance of the sink should be less than 3.5 °C/W.

The volume and balance controls are connected right at the amplifier input. Three volume control versions are suggested: an untapped logarithmic potentiometer, a logarithmic potentiometer tapped so as to provide physiologically correct volume control, and finally a linear potentiometer with three taps. In the last case a good approximation to a logarithmic law and physiologically correct modification of the frequency response is attained by the connection of RC networks to the taps. Use of the RC values shown in brackets results in a higher bass boost (in accordance with the Fletcher Munson curves) than the boost attained with the values outside the brackets, which are based on I. S. O. Recommendation R. 226.

In the frequency range 50 Hz...20 kHz, with the tone controls set for a flat response, the amplifier has less than 0.5 % distortion at 2 x 6 W output; it requires 350 mV input across 1 M $\Omega$  to attain full output.

8. 2 x 6 W Amplifier

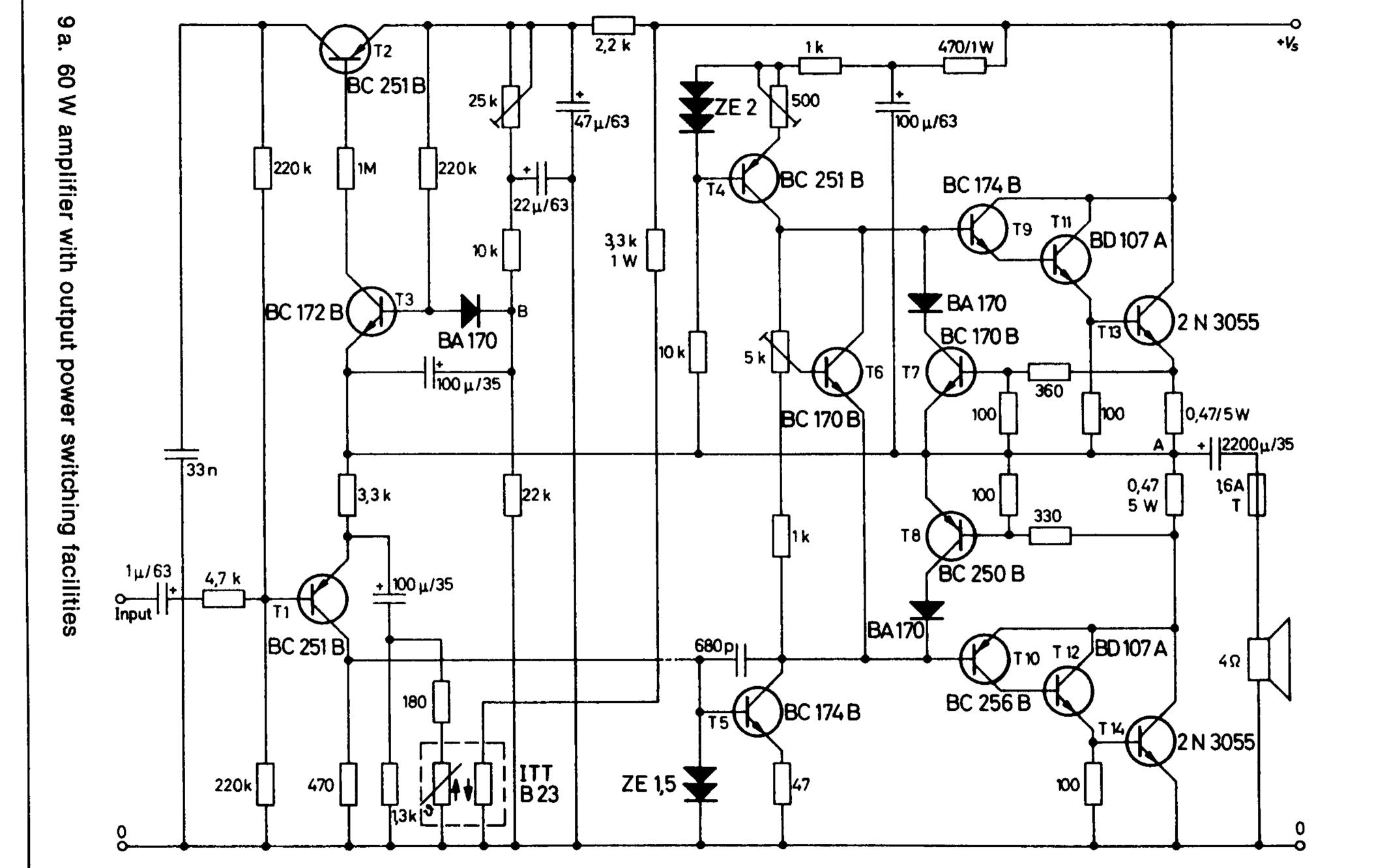

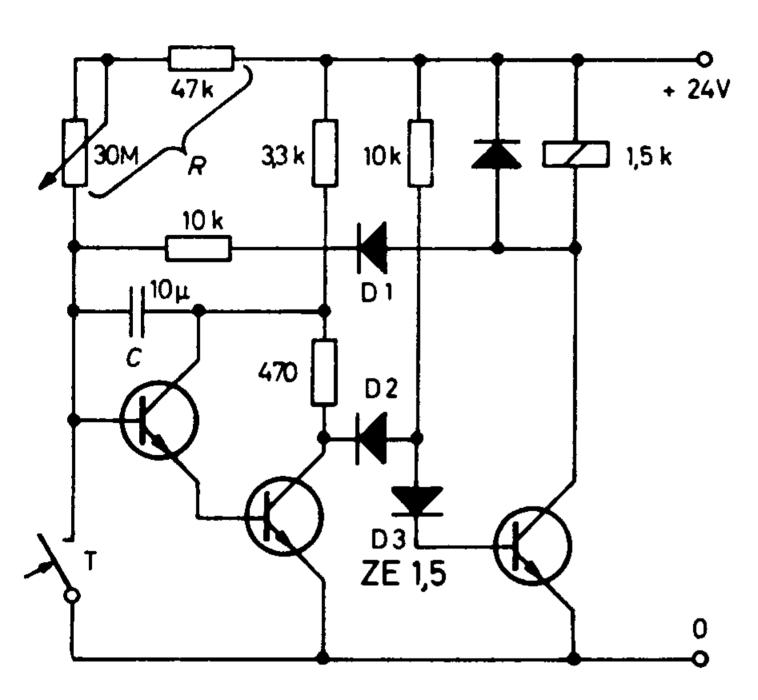

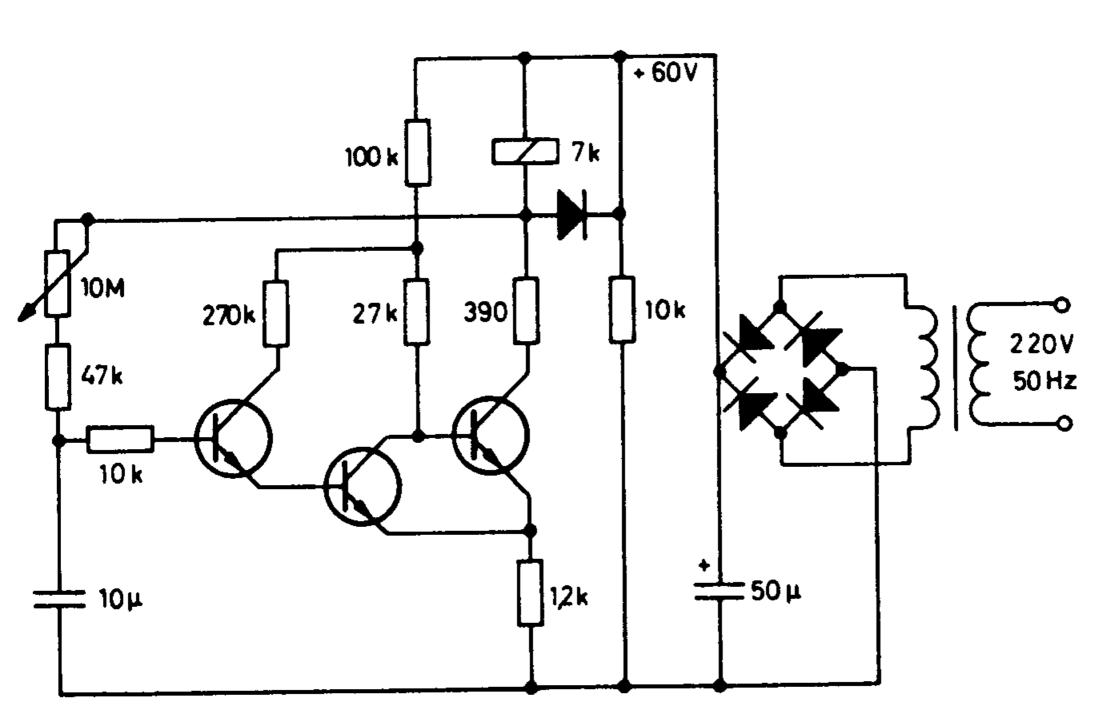

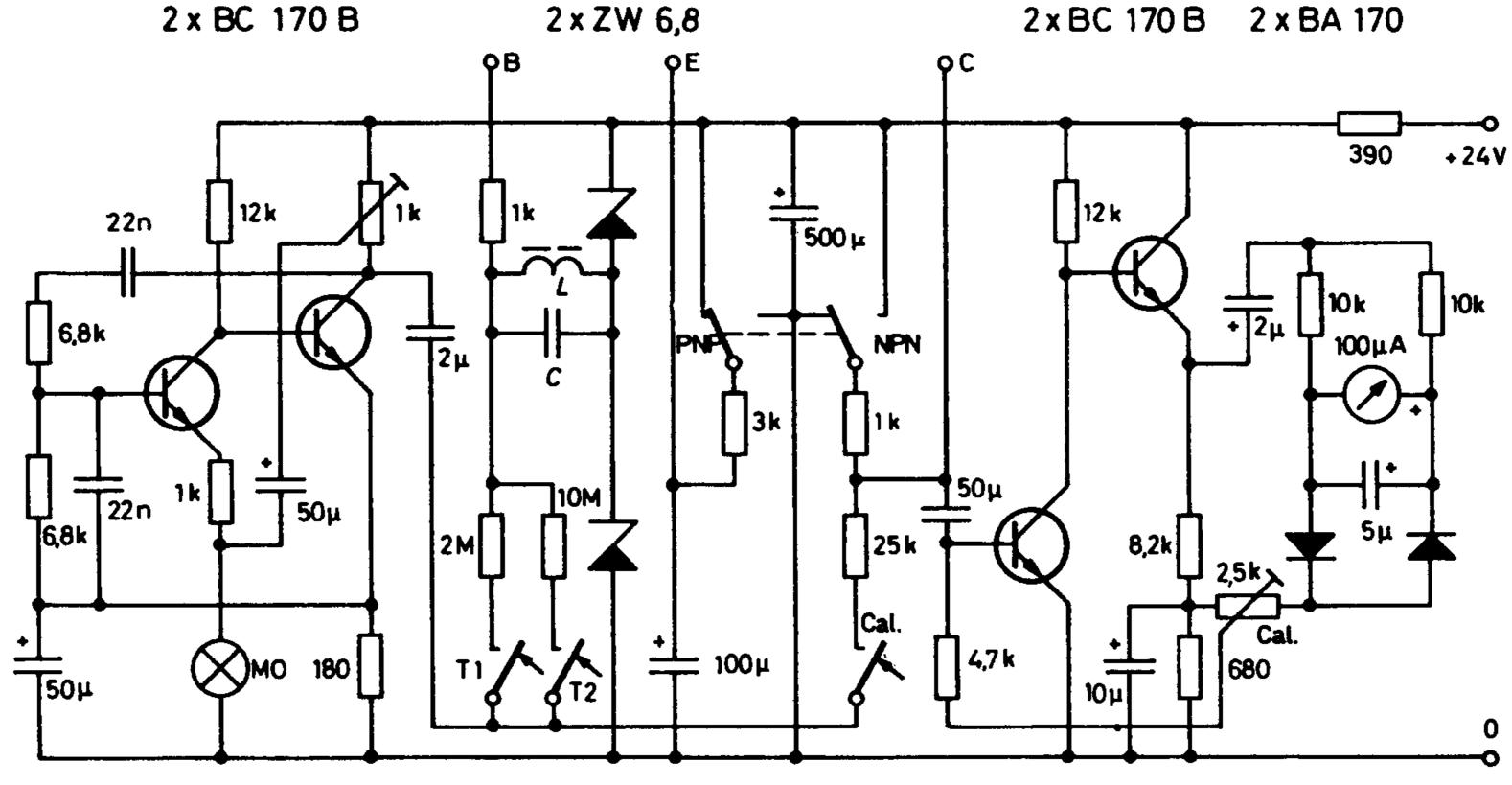

#### 60 W Amplifier with Output Power Switching Facilities

This circuit is similar in design to those discussed in II. 7. and II. 8., a quasi complementary transformerless series push pull output stage and direct interstage coupling being employed. What is new in circuit II. 9. is the high output power of 60 W and the facilities provided which permit the output power to be reduced by supply voltage reduction (selection of taps on the AC power transformer) without increasing the distortion. To achieve this the amplifier incorporates circuits which automatically stabilize the operating point and the sensitivity against supply voltage changes.

As can be deduced from the equation

$$P_{out} = \frac{(V_S - V_{R1} - V_{R2})}{8 R_L}$$

if  $R_L$ , the value of the load, remains unchanged, then the maximum attainable output power depends primarily on the supply voltage  $V_S$ . The terms  $V_{R1}$  and  $V_{R2}$  are the voltages dropped across the output transistors and the 0.47  $\Omega$  emitter or collector resistors during the positive and negative half-cycles respectively.

A change in supply voltage has the effect of:

- 1. shifting two operating point (i. e. the DC level at point 'A' is no longer  $V_S/2$ );

- 2. producing a pronounced change in the quiescent current of the output stage;

- 3. changing the amplifier sensitivity.

To overcome this the following steps are taken:

- 1. The DC level at point 'A' is compared, in transistor T3, with the voltage at point 'B', derived from a variable voltage divider, this being half the supply voltage. Error signal amplifier T3 in conjunction with series transistor T2 form a series regulator (similar to that discussed in I. 3.), which controls the base potential of input transistor T1 so that  $V_A$  is always equal to  $V_S/2$ .

- 2. Transistor T4 and stabilizer diode ZE 2 in the collector circuit of transistor T5 act as a constant current source, which largely stabilizes the collector current of T5, and hence the quiescent current of the output stage, against supply voltage variations.

- 3. The bottom arm of the gain determining negative feedback voltage divider connected to the emitter of input transistor T1 incorporates an indirectly heated thermistor (NTC resistor ITT B 23). The heater of this thermistor is connected to the supply line via a 3.3 k $\Omega$  resistor, so that the heater current, and consequently the negative feedback divider ratio,

**E.** 9.

ユ

changes with the supply voltage in such a manner that the input sensitivity (approximately 1 V for full output) is maintained constant for any supply voltage between 20 and 60 V.

The circuit incorporating transistor T6 stabilizes in the usual way the quiescent current of the output stage against ambient temperature changes. Transistors T7 and T8 are driven by the voltages dropped across the 0.47  $\Omega$  resistors; these voltages are proportional to the amplifier output current. The transistors limit the peak current passed by the output transistors to approximately 7 A, and thus provide overload protection. Additional protection is provided by the fuse which, in the event of a short circuit, completely disconnects the load. Diode ZE 1.5 and the 47  $\Omega$  emitter resistor protect transistor T5 in the event of a short circuit.

To operate the amplifier at ambient temperatures up to  $\pm 45$  °C, each of the two output transistors 2 N 3055 must be mounted on a heat sink with a thermal resistance  $R_{thS} < 6$  °C/W; this must be reduced to 3 °C/W if a common heat sink is used. The BD 107 driver transistors require a heat sink of only a few cm², or they can even be mounted on the output transistor heat sink.

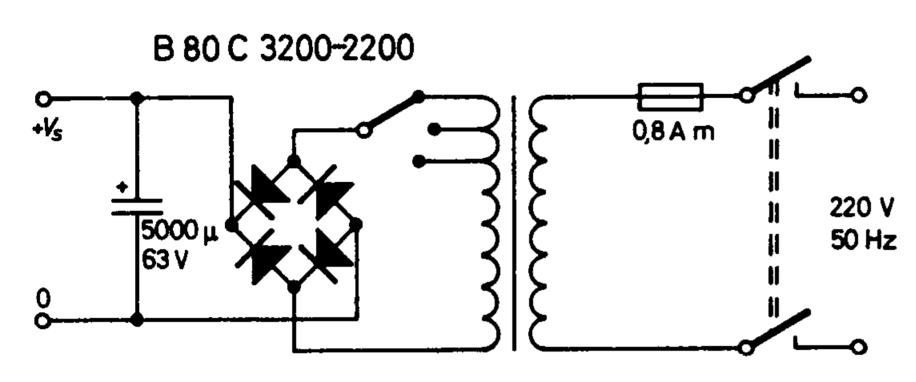

As the diagram on page 73 shows, the power supply is very simple. Because the amplifier is largely self-stabilizing, any power supply stabilization is unnecessary, and a simple bridge rectifier followed by a reservoir capacitor is all that is required. The switch permits the maximum amplifier output power to be reduced, as already described.

#### **Transformer Data**

Core: M 102a type III laminations, alternately stacked Windings: Primary 735 turns 0.35 mm dia. en. copper wire

secondary 77 + 28 + 42 turns 1.2 mm dia. en. copper wire

When the amplifier is switched on for the first time ensure that the 500  $\Omega$  potentiometer is set to maximum resistance and that the slider of the 5  $k\Omega$  potentiometer is set so that it is at the same potential as the collector of T6. Use the 25  $k\Omega$  potentiometer to set the voltage at point 'B' to half the supply voltage and confirm that the voltage at point 'A' is the same. Next adjust the 500  $\Omega$  potentiometer for a T5 collector current of 5 mA corresponding to a voltage drop of 230 mV across the T5 emitter resistor. Only now should the 5  $k\Omega$  potentiometer be adjusted for 20 mA quiescent current through the output stage corresponding to a voltage drop of approximately 10 mV across one of the 0.47  $\Omega$  resistors in this stage. The amplifier is now ready for operation.

9b. Power supply for 60 W amplifier

#### **Amplifier Data**

| Output power | at | Supply voltage |

|--------------|----|----------------|

| 15 W         |    | 29 V           |

| 30 W         |    | 40 V           |

| 60 W         |    | 50 V           |

Adjustment of the supply voltage between 20 and 60 V permits any output level to be selected.

Frequency response ± 1 dB in the 25 Hz... 20 kHz range

Required input for full output 1 V

Distortion at full output < 0.2 % at 100 Hz

< 0.1 % at 1 kHz

< 0.25 % at 10 kHz

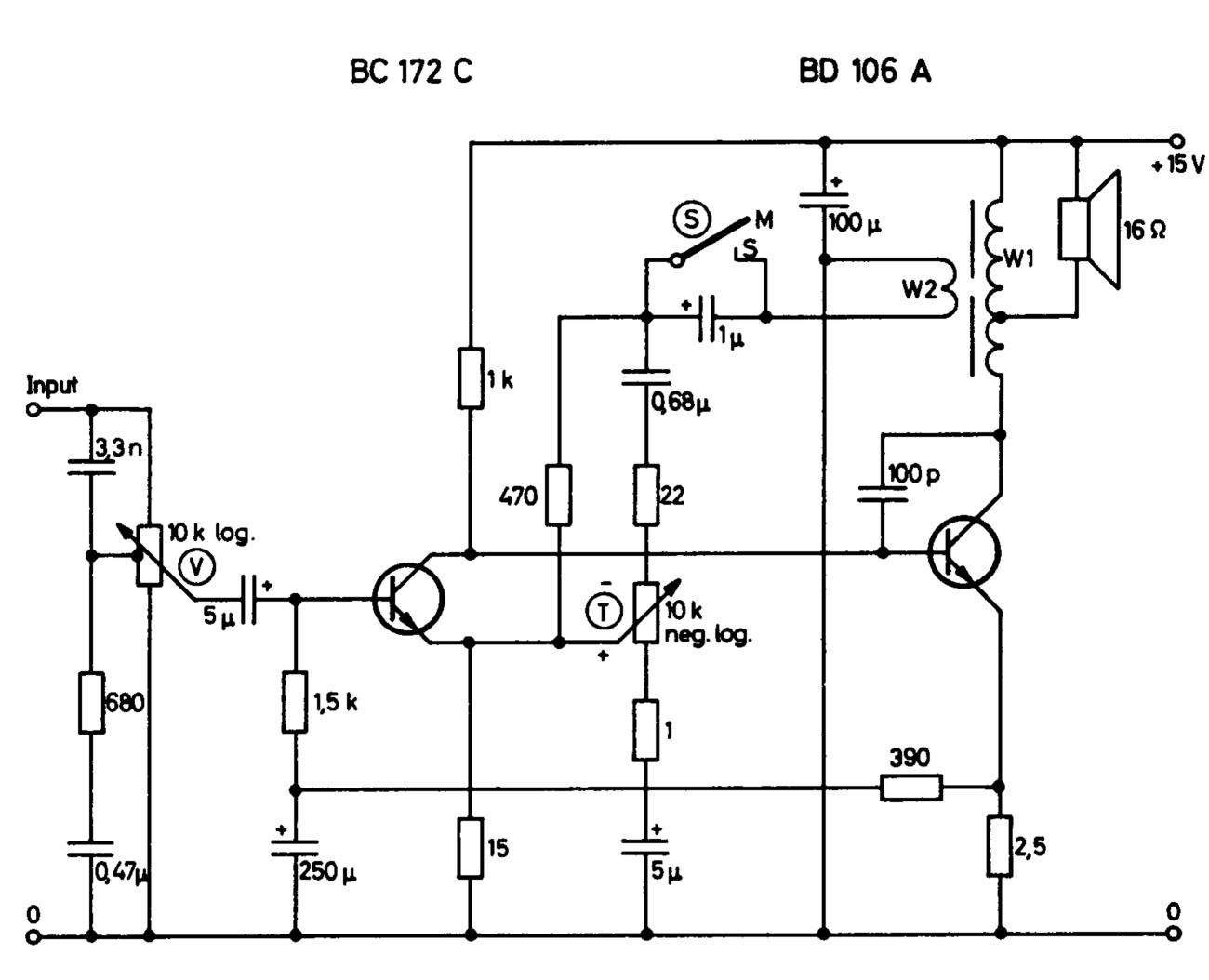

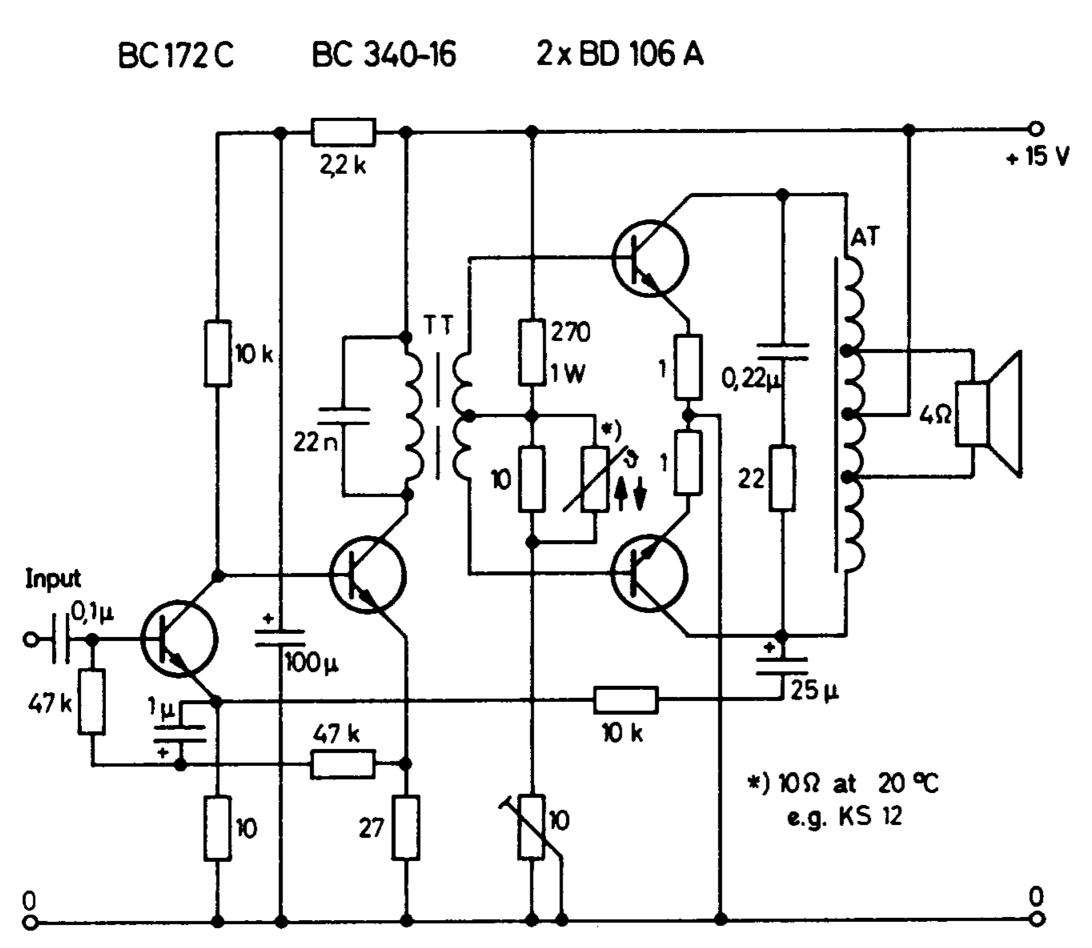

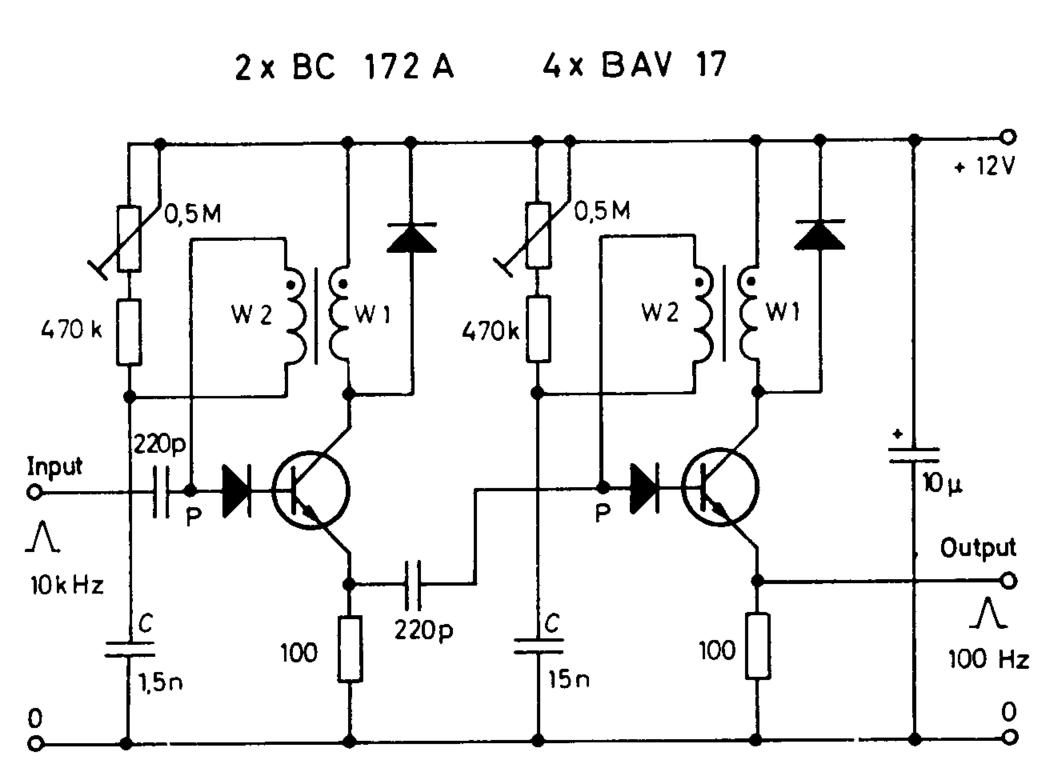

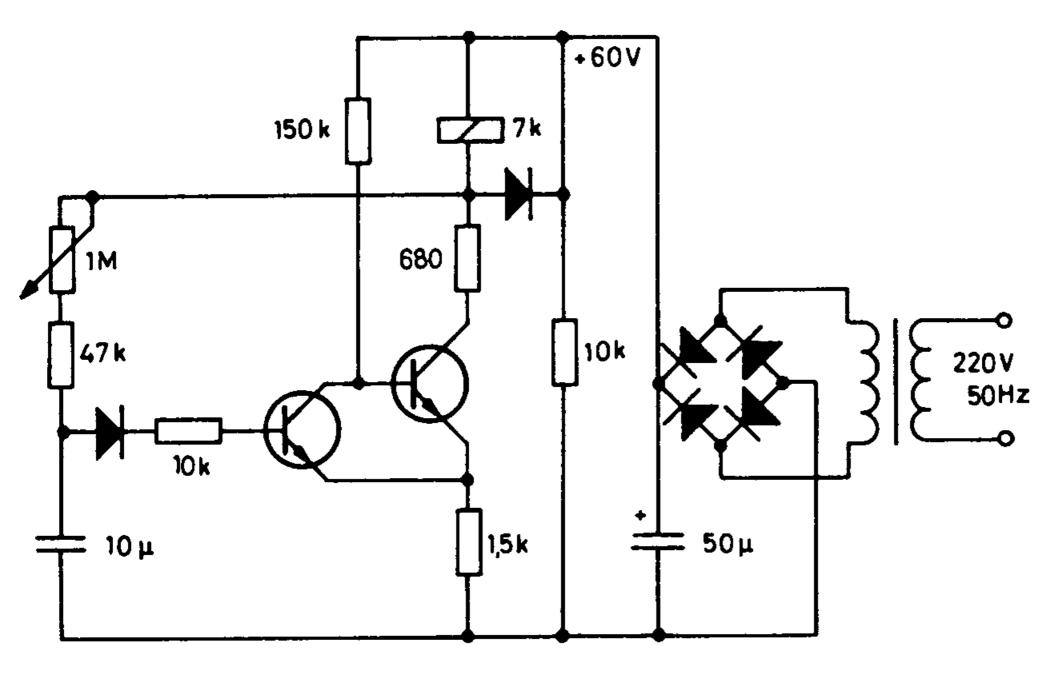

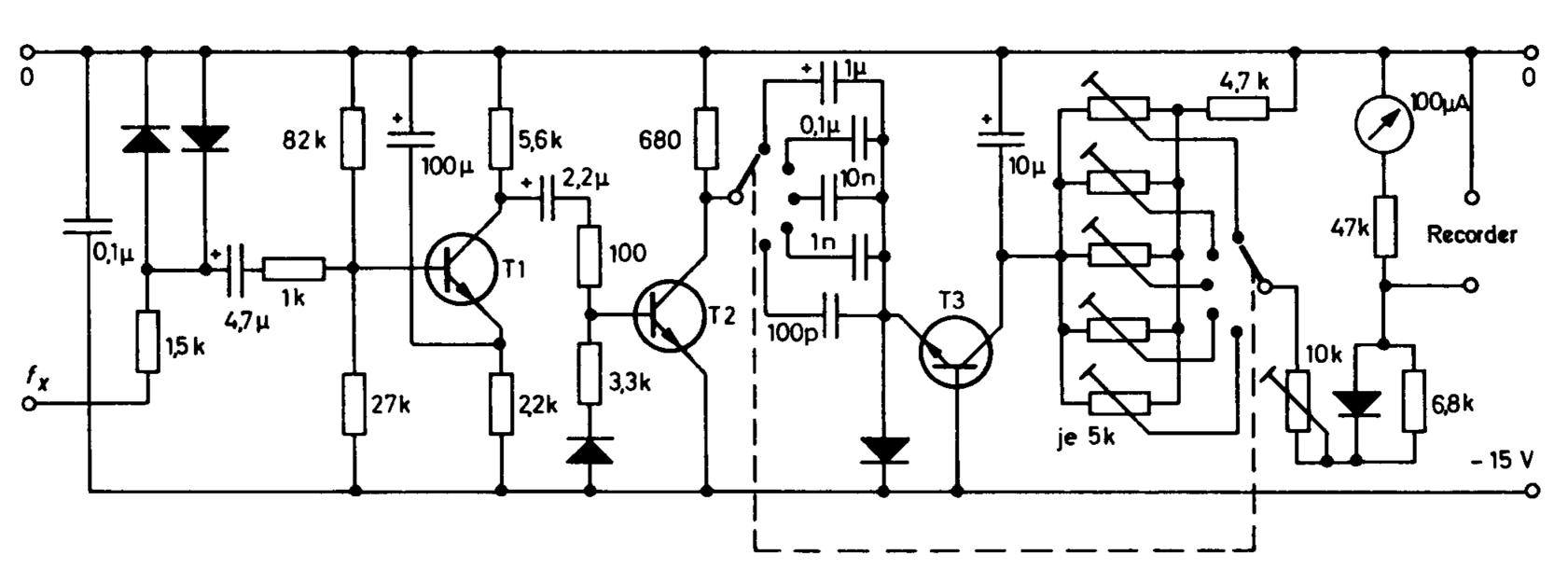

## Transformer-Coupled 8 W Push-Pull Class B Amplifier

There are not many applications now for transformer-coupled push-pull amplifiers, these having been replaced by transformerless series push-pull amplifiers of the type described previously, which usually give a better performance. However, they are still required for some special applications. For example, a designer would have to fall back on a transformer-coupled amplifier design when there are supply voltage restrictions, and when a specified power level has to be supplied to a specified load. Use of an output transformer permits the amplifier to be matched to virtually any load, whereas in a series push-pull amplifier supply voltage, output power and load must be compatible.

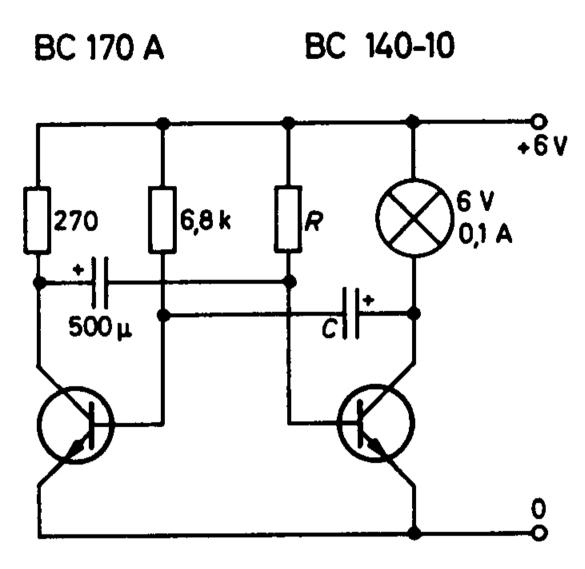

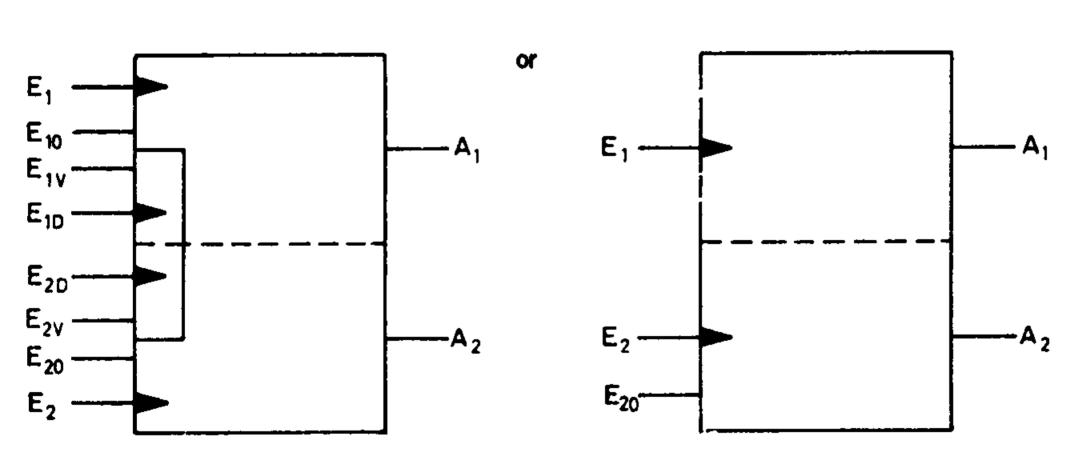

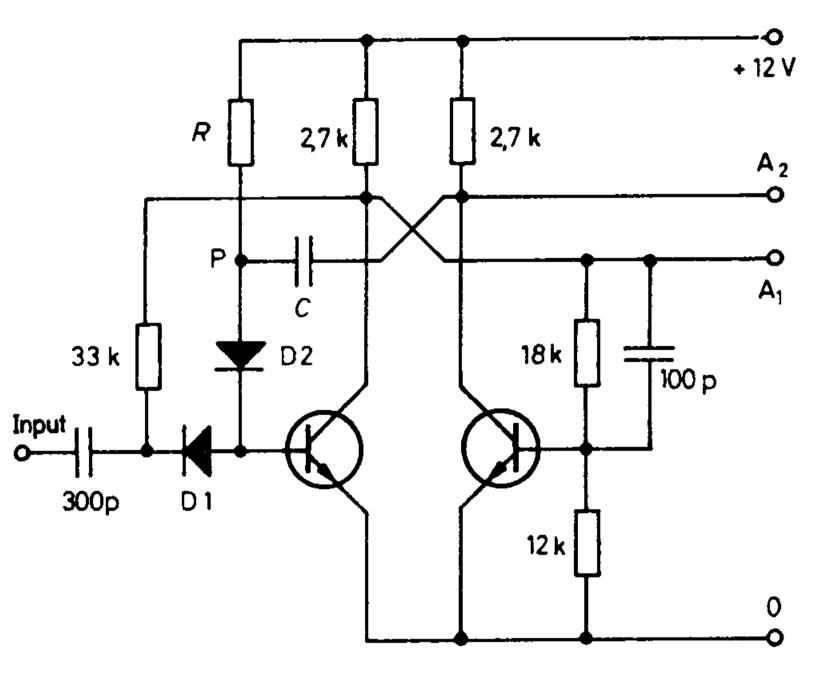

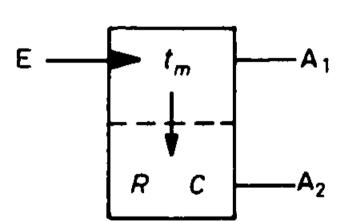

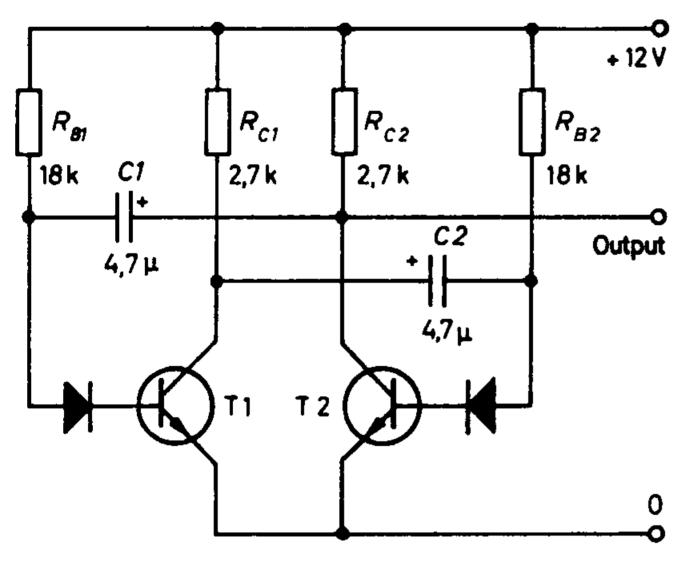

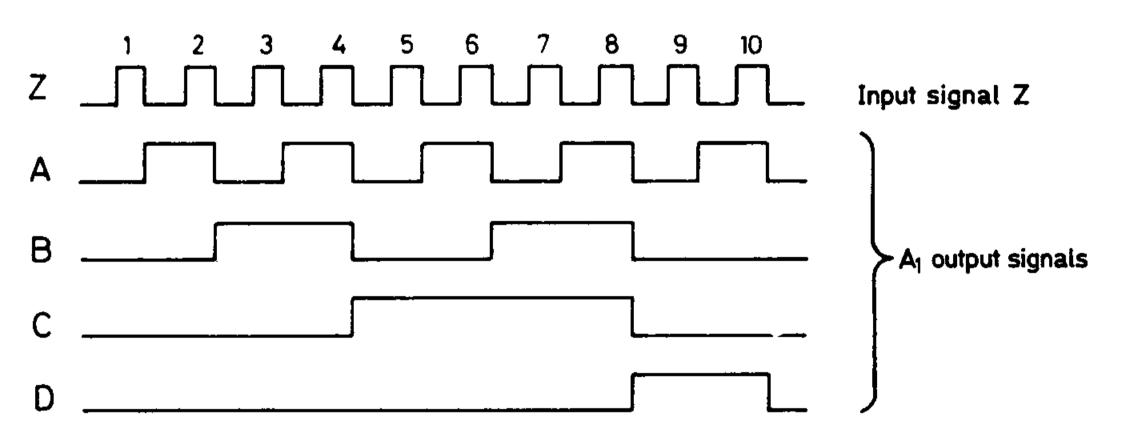

The amplifier described operates from a 15 V supply and delivers 8 W into a 4  $\Omega$  load.