**April 2008**

# DC/DC µModule Regulator Printed Circuit Board Design Guidelines

(LTM802x Series are used for this discussion)

By David Ng

The LTM8020, LTM8021, LTM8022 and LTM8023 µModule® regulators are complete easy-to-use encapsulated stepdown DC/DC regulators intended to take the pain and aggravation out of implementing a switching power supply onto a system board. With a µModule regulator, you only need an input cap, output cap and one or two resistors to complete the design. As one might imagine, this high level of integration greatly simplifies the task of printed circuit board design, reducing the effort to four categories: component footprint generation, component placement, routing the nets, and thermal vias.

#### **Component Footprint Generation**

One of the first things to do when designing a printed circuit board is generate the footprint or decal for each component. The components required to complete the LTM8020, LTM8021, LTM8022 and LTM8023 designs are common resistors and capacitors that have industry standard footprints. The basic information necessary to generate the footprint for a LTM8020, LTM8021, LTM8022 or LTM8023 is given in the package outline drawing, which can be found in the "Package Description" section of the data sheet, which is also accessible online at:

http://www.linear.com/designtools/packaging/index.jsp

It is indexed by package drawing number, which is also found in the "Package Description" section of the data sheet.

Next, choose an appropriate pad size. For the LTM8020, LTM8021, LTM8022, and LTM8023, square pads with sides measuring between 0.025" and 0.029" will work for most applications. Make the pads non-solder mask defined (NMSD), with a solder mask expansion of zero to 0.004" or 0.1mm per side.

The LTM80xx series of  $\mu$ Module regulators have both I/O and power connections. The I/O connections are typically

routed with a trace. The power and ground connections are usually hooked up by laying planes. If the  $\mu$ Module regulator footprint uses a solder mask expansion of zero, all of the pads will be the same size. If the solder mask expansion is greater than zero, the power pads will be bigger than the I/O pads.

Take a moment to examine the pad pattern. Note that the pads surrounding the V<sub>IN</sub> net have been depopulated. The reason for this is because each of the LTM8020, LTM8021, LTM8022 and LTM8023 µModule regulators are rated for 36V<sub>DC</sub> operation. According to IPC 2221, Generic Standard on Printed Board Design, Table 6-1, uncoated external printed circuit board conductors, such as solder pads, with 31V to 50V between them must be separated by at least 0.6mm, or 0.0236". On the LTM80xx series of µModule regulators, the square pads are 0.025" on a side, placed at a 0.050" pitch. If the µModule regulator operates above 31V steady state, the actual printed circuit board pad may not exceed 0.0257" before violating the IPC-2221 standard. In this case, it is best to make the footprint pad opening 0.025" NMSD with a zero solder mask expansion. If no adjacent pins operate above 30V, any size pad with a net opening between 0.025" and 0.029" will suffice.

### **Component Placement**

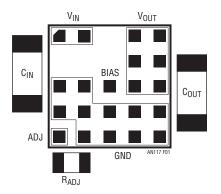

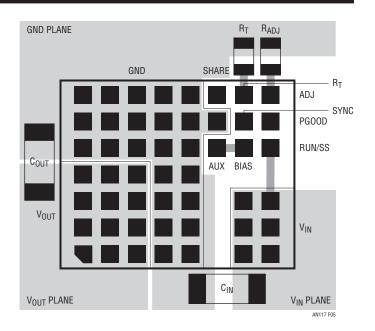

In general, components should be placed in a manner which results in traces that are as short as possible. There are very few components to put down so component placement is simple. For example, on the LTM8020, the typical components are the  $\mu Module$  regulator, a single output voltage resistor, along with an input and output cap. In order to keep the traces as short as possible, place the set resistor  $R_{ADJ}$  adjacent to the ADJ pad, the input cap  $C_{IN}$  next to  $V_{IN}$  and the output cap  $C_{OUT}$  next to  $V_{OUT}$ . An example of this is shown in Figure 1.

LT, LTC, LTM, µModule, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

an117fa

Figure 1. LTM8020 Example Component Placement

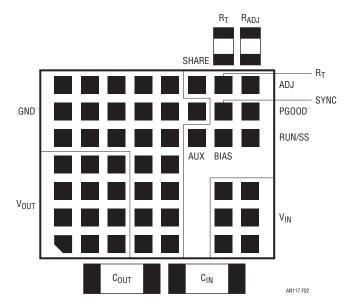

In the case of the LTM8022 and LTM8023, there are two caps and two resistors. The component placement guidelines are very similar to those for the LTM8020. Place the set resistor  $R_{ADJ}$  adjacent to the ADJ pad, the input cap  $C_{IN}$  next to  $V_{IN}$  and the output cap  $C_{OUT}$  next to  $V_{OUT}.$  The remaining part,  $R_T,$  needs to be placed as close as possible to the  $\mu Module$  regulator's  $R_T$  pad. This is shown in Figure 2.

Figure 2. LTM8023 Example Component Placement

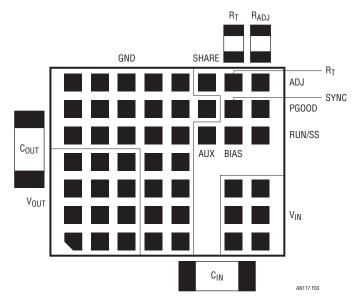

It is also possible to place the  $C_{OUT}$  capacitor in an alternate position, where the GND connection is not so close to that of  $C_{IN}$ . In most applications, the location of  $C_{OUT}$  relative to  $C_{IN}$  is not critical. In circuits where it is important to keep output noise to a minimum, it is better to place  $C_{OUT}$

as shown in Figure 3, where the GND connection of  $C_{OUT}$  is farther away from that of  $C_{IN}$ . There are large current pulses flowing through  $C_{IN}$ , so moving the  $C_{OUT}$  GND connection away from that of  $C_{IN}$  will reduce the coupling between the two capacitors.

Figure 3. Moving the  $C_{OUT}$  Capacitor Away from  $C_{IN}$  Can Reduce Output Noise

#### **Routing Nets**

With the low number of components placed such that the traces are as short as possible, the job of routing nets is pretty straightforward. The task of routing nets breaks down into routing traces and laying planes.

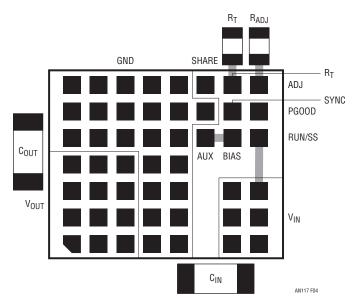

Traces are used to route the low current nets. For the LTM8023 example above, traces are used for everything except the  $V_{IN},\,V_{OUT}$  and GND nets. The  $R_T$  and ADJ simply connect to the  $R_T$  and  $R_{ADJ}$  resistors. The BIAS and RUN/SS connections depend upon the specific design. The LTM8022 and LTM8023 pad patterns are designed with the layout in mind. In most applications, BIAS is connected to either  $V_{AUX}$  or  $V_{IN},\,so$  BIAS is conveniently located for easy access to  $V_{AUX}$  or  $V_{IN}.$  Furthermore, for those cases where a connection to external voltage source is necessary, the BIAS pad is located adjacent to an edge row, allowing easy access to external circuitry.

The RUN/SS pad is either connected to  $V_{\text{IN}}$  or an external signal source, so it is located next to the  $V_{\text{IN}}$  pads on an

TECHNOLOGY TECHNOLOGY

an117fa

outer row. Figure 4 shows an example of the LTM8023 where BIAS is connected to  $V_{AUX}$  and RUN/SS is connected to  $V_{IN}$ , and  $R_T$  and ADJ to external resistors. The traces are shown in gray. The remaining I/O pins, SHARE, SYNC and PG are also easily accessed.

Figure 4. The Placement of the I/O Pins Makes Them Easy to Route

Next, place the power and ground plane, which should be as wide as possible for good thermal and EMI performance. As shown in Figure 5, these planes, shown in gray, should together fill nearly all of the remaining copper area underneath the  $\mu$ Module regulator. In the example of Figure 5, there is a wide gap between the  $V_{IN}$  and other planes, which applies for greater than 30V input voltages.

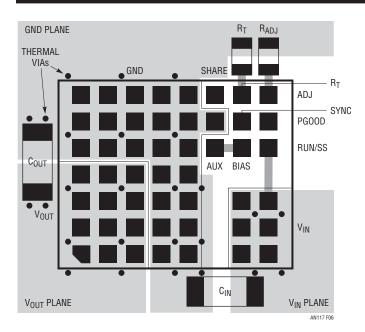

#### Thermal and Electrical Interconnect Vias

The last task is to place thermal and electrical interconnect vias. The LTM8020, LTM8021, LTM8022 and LTM8023  $\mu$ Module regulators use the printed circuit board to spread the power dissipated within the product. So it is important to place vias underneath and around the  $\mu$ Module regulator to distribute heat throughout the layers of printed circuit board. In general, a printed circuit board will have several ground planes, so adding vias should be easily accomplished. If the  $V_{OUT}$  and  $V_{IN}$  nets are carried on multiple layers, vias should be added to them, as well.

Figure 5. Suggested Power and Ground Planes for LTM8023. Note the Wide Gap that Separates the High Voltage  $V_{\text{IN}}$  Net From Other Nets, in Compliance with IPC-2221

Most printed circuit board designs consider planes to be both electrically and thermally equipotential. That is, the voltage gradient across the plane is assumed to be an ideal zero volts, and that the thermal resistance from a point to any other point is negligible. This is not actually true, especially from the thermal perspective, but using vias is a simple and inexpensive way of achieving a design whose performance approaches this ideal.

Figure 6 shows a layout example with interconnect vias on the  $V_{IN}$ ,  $V_{OUT}$  and GND planes. The vias are all the same size, with a 0.010" drill hole and 0.015" outer diameter. This sized via fits easily between pads of the same net, and has a good current carrying capability. With careful placement, vias with a 0.035" outer diameter may be used without overlapping adjacent pads.

Vias act as very good electrical conductors to interior planes and serve as heat pipes to allow the printed circuit board to act as the heat sink. For the best performance and reliability, the  $\mu$ Module regulator should be operated as cool as possible, so one might conclude that the best design has as many vias that will possibly fit. Each via, however, starts as a hole drilled into the board, which reduces the amount of copper that is present on the printed circuit

## **Application Note 117**

Figure 6. Use Vias to Conduct Electrical Power to Internal Planes and as Heat Pipes to Distribute Heat Throughout the Printed Circuit Board

board layers for electrical conduction. It is thus possible to have too many vias, so please consult your organization's design guidelines.

#### **Conclusion**

The high level of integration of the LTM8020, LTM8021, LTM8022 and LTM8023  $\mu$ Module regulators simplifies the task of the printed circuit board design for your power system. The whole job can be summarized as four tasks as shown in Table 1.

Table 1. µModule Regulator Printed Circuit Board Design

| TASK                                        | DESCRIPTION/NOTES                                                                                            |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Footprint Generation                        | Get package outline drawing from the data sheet or http://www.linear.com/designtools/packaging/index.jsp     |

|                                             | • If adjacent pins have greater than 30V, use 0.025" NSMD pads, otherwise, use 0.025" to 0.029" NSMD pads    |

|                                             | Use a solder mask expansion between zero and 0.004"                                                          |

| Component Placement                         | Place components to keep trace lengths as short as possible                                                  |

|                                             | Physically separate C <sub>IN</sub> and C <sub>OUT</sub> GND connections if minimum switching noise required |

| Route Nets                                  | Use layout design features to minimize routing complexity                                                    |

|                                             | Extend copper planes as far as practical for good EMI and thermal performance                                |

| Thermal and Electrical<br>Interconnect Vias | Use vias to connect to internal layers                                                                       |

|                                             | Place vias to conduct heat to internal layers                                                                |

|                                             | • 0.010" ID, 0.015" OD fits between pads of the same net                                                     |

|                                             | • Up to 0.035" OD vias may be used for higher heat transfer with careful placement                           |