Application Note 73

February 1999

LT1339 Design Manual Designing the Power Converter

Dale Eagar

#### PREFACE

#### Switching Power Converter: an Early Example

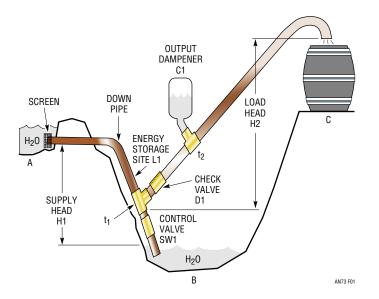

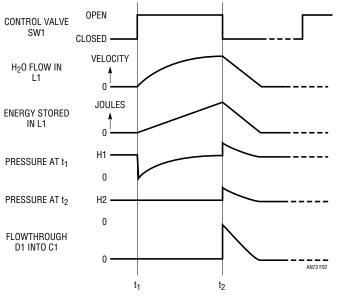

Although the origin of switching power converters is lost in antiquity, some early machines have been identified that work on this principle. Among the first was the hydraulic impulse pump, in use centuries before the use of electricity (see Figure 1). This device allows some of the energy in the stream of water flowing from point A to point B to be diverted to pump a smaller amount of water from point B to point C. Here is how this "water hammer" works (refer to Figures 1 and 2). First, the control valve SW1 opens at time t<sub>1</sub> and flow commences through the downpipe L1. As the velocity of water flow in the downpipe increases, so does the energy stored in the moving mass. (E =  $1/2MV^2$ , where M = mass of the moving water, V = the velocity of the moving water, and E = energy, usually expressed in Joules). When the valve SW1 has been open long enough for the water flow rate to reach a valve that is a significant percentage of the theoretical maximum flow rate, we shut the valve SW1. This is  $t_2$  in Figure 2. By shutting the control valve SW1 at time  $t_2$ , we attempt to arrest the flow through the downpipe. One thing about energy—it doesn't like being abandoned, so the pressure rises until something gives. Lucky for our downpipe, we have a check valve that can open and divert the otherwise-trapped energy into C1, the output damper. Enough H<sub>2</sub>O moves through the check valve D1 and into C1 at a pressure head above the load head H2 to remove all kinetic energy associated with the down flow in the downpipe. Hence, for every hogshead of water that flows into the downpipe, a partial hogshead of water is delivered to the barrel at point C.

Figure 1. Hydraulic Impulse Pump (Water Hammer)

Figure 2. Water Hammer Waveforms

#### **TABLE OF CONTENTS**

| Introduction and Data Sheet |    |

|-----------------------------|----|

| Introduction                |    |

| Data Sheet                  | 6  |

| Block Diagram               |    |

| Operation                   |    |

| Applications Information    |    |

| Typical Applications        |    |

| Package Descriptions        |    |

| Related Parts               |    |

| Expanded Pin Descriptions   |    |

| SYNC (Pin 1)                |    |

| 5V <sub>BFF</sub> (Pin 2)   |    |

| CT (Pin 3)                  |    |

| SL/ÀDJ (Pin 4)              |    |

| I <sub>AVE</sub> (Pin 5)    |    |

| SS (Pin 6)                  |    |

| V <sub>C</sub> (Pin 7)      |    |

| SGND (Pin 8)                |    |

| V <sub>FB</sub> (Pin 9)     |    |

| V <sub>REF</sub> (Pin 10)   |    |

| SENSE <sup>+</sup> (Pin 11) |    |

| SENSE <sup>-</sup> (Pin 12) |    |

| RUN/SHDN (Pin 13)           |    |

| PHASE (Pin 14)              |    |

| PGND (Pin 15)               |    |

| BG (Pin 16)                 |    |

| 12V <sub>IN</sub> (Pin 17)  |    |

| TS (Pin 18)                 |    |

| TG (Pin 19)                 |    |

| V <sub>B00ST</sub> (Pin 20) |    |

| Buck Regulator Design       |    |

| Overview                    |    |

| Graphical Design Example    |    |

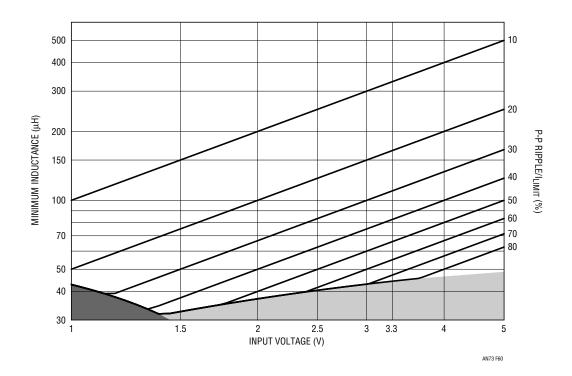

| 3.3V Output Graph Set       |    |

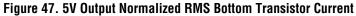

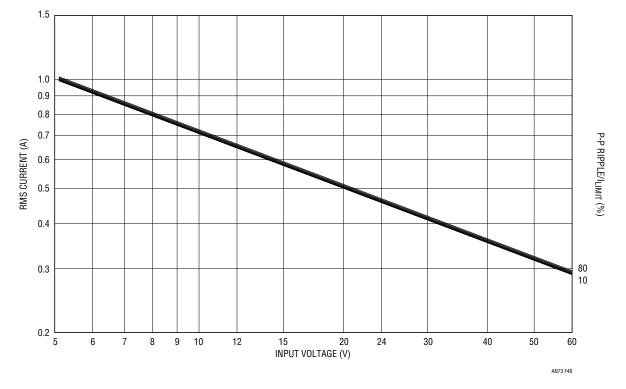

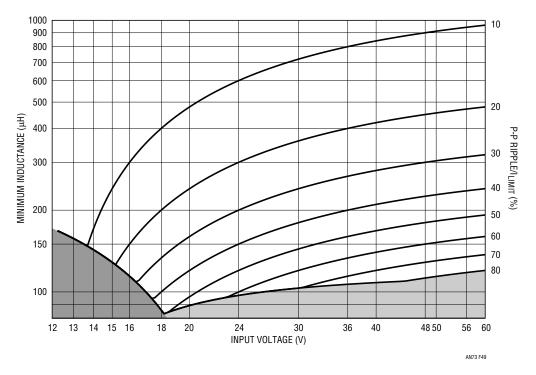

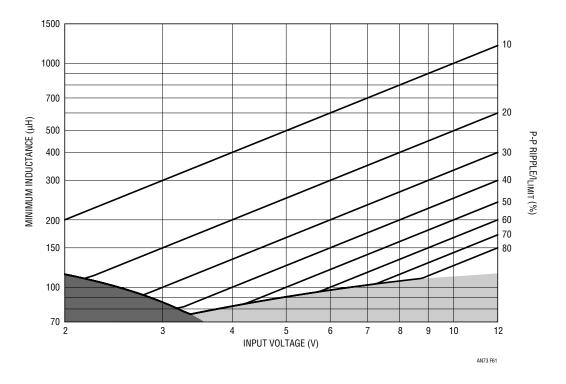

| 5V Output Graph Set         |    |

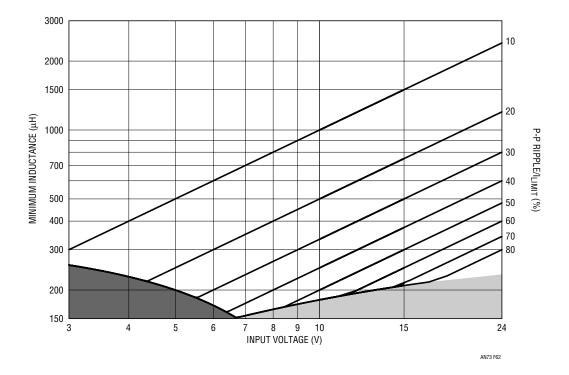

| 12V Output Graph Set        |    |

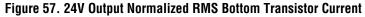

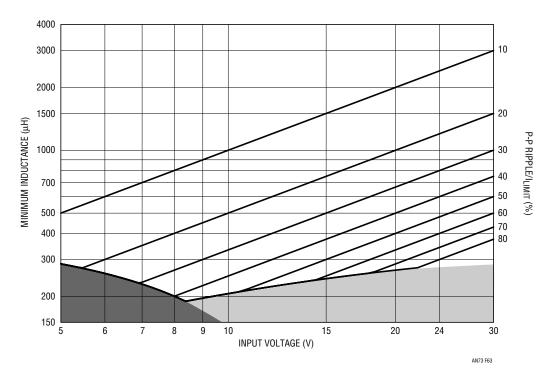

| 24V Output Graph Set        | 53 |

| Boost Converters                                                                                                                                                                                              |                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Characteristics of the Synchronous Switching Boost Converter                                                                                                                                                  | 58                    |

| Conclusion                                                                                                                                                                                                    | 59<br>59              |

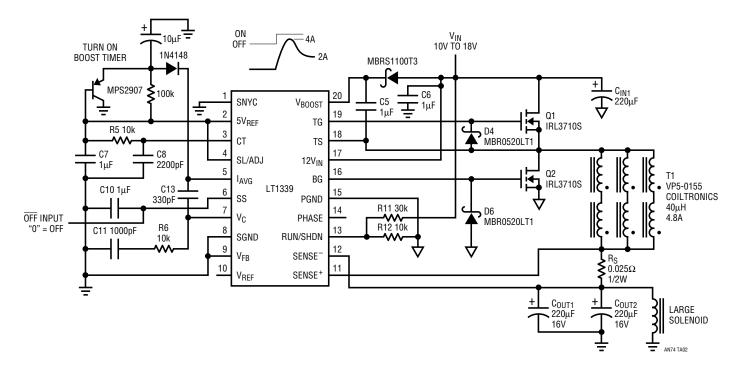

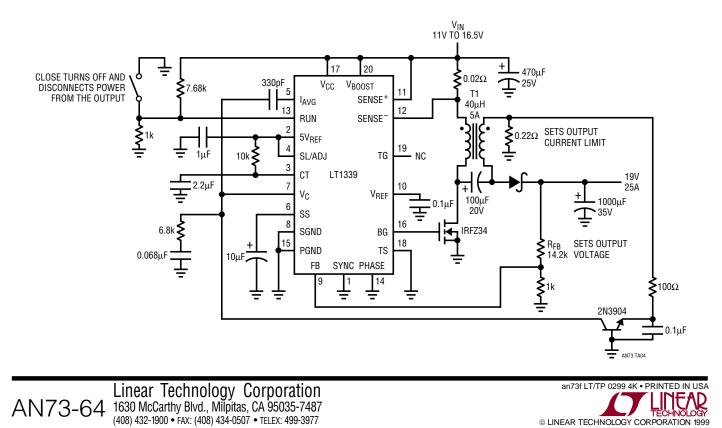

| Typical Applications 6   28V to 5V/20A Buck Converter 6   Constant-Current Solenoid Driver with 2× Turn-On Boost 6   2.5A SEPIC Converter. The Output Voltage Can Be Lower or Higher Than the Input Voltage 6 | <b>63</b><br>63<br>64 |

#### INTRODUCTION

The advent of the switching regulator has greatly reduced the size, weight and volume of power conversion circuitry, while improving both the speed of response and efficiency. With the output voltage requirements going ever lower and currents ever higher, close scrutiny is applied to the loss mechanisms of the power converter. The loss mechanisms are divided into three classes: resistance loss, fixed voltage loss and switching loss. Resistance losses are caused by the circuit resistances (input capacitor ESR, power switch on-resistance, DC and AC resistance of the inductor, resistance of any current-sense elements, resistance in the output diode and ESR in the output capacitors), each multiplied by the squares of their respective currents. Fixed voltage losses associated with diode forward drops can be calculated by multiplying diode forward voltage by diode current. Switching losses are caused by both the finite turn-on and turn-off times of the MOSFETs and the stray capacitance on the source of

the top MOSFET. As the trend toward higher output current progresses, the first thing to do is minimize all losses caused by resistance (because the power is proportional to I<sup>2</sup>R). It is easy to minimize resistance because we have available very low ESR capacitors. low on-resistance MOSFETs and low series-resistance inductors. We have controllers that place a very small voltage across the current sense resistors. We do such a good job of dropping the resistive loss mechanisms that the output diode forward-voltage drop becomes the greatest loss mechanism. This is how the mandate for synchronous rectification comes about. Synchronous rectification is achieved by replacing the output diode with a low on-resistance switch. With synchronous rectification, efficiencies are higher, and, more importantly, power dissipated in the switching power supply is lower, often eliminating the need for heat sinks and/or fans.

### High Power Synchronous DC/DC Controller

### FEATURES

- High Voltage: Operation Up to 60V

- High Current: Dual N-Channel Synchronous Drive Handles Up to 10,000pF Gate Capacitance

- Programmable Average Load Current Limiting

- 5V Reference Output with 10mA External Loading Capability

- Programmable Fixed Frequency Synchronizable Current Mode Operation Up to 150kHz

- Undervoltage Lockout with Hysteresis

- Programmable Start Inhibit for Power Supply Sequencing and Protection

- Adaptive Nonoverlapping Gate Drive Prevents Shoot-Through

### **APPLICATIONS**

- 48V Telecom Power Supplies

- Personal Computers and Peripherals

- Distributed Power Converters

- Industrial Control Systems

- Lead-Acid Battery Backup Systems

#### Automotive and Heavy Equipment

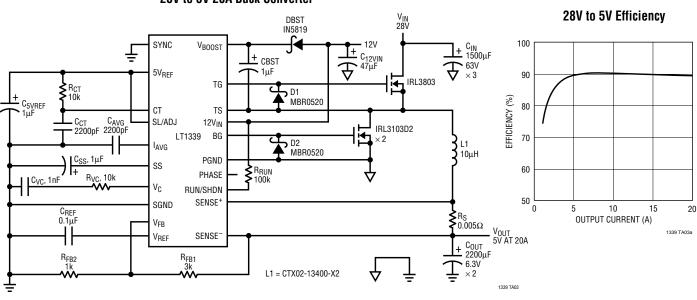

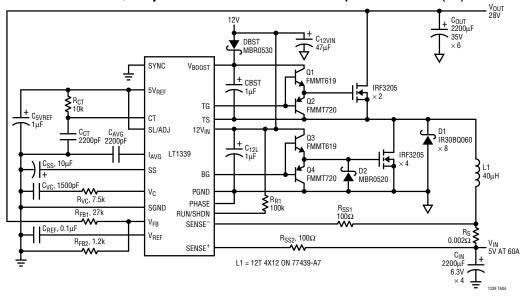

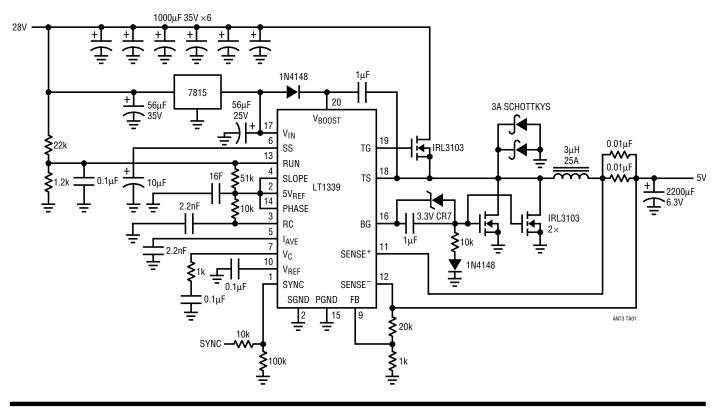

**TYPICAL APPLICATION**

## DESCRIPTION

The LT®1339 is a high power synchronous current mode switching regulator controller. The IC drives dual N-channel MOSFETs to create a single IC solution for high power DC/DC converters in applications up to 60V.

The LT1339 incorporates programmable average current limiting, allowing accurate limiting of DC load current independent of inductor ripple current. The IC also incorporates user-adjustable slope compensation for minimization of magnetics at duty cycles up to 90%.

The LT1339 timing oscillator operating frequency is programmable and can be synchronized up to 150kHz. Minimum off-time operation provides main switch protection. The IC also incorporates a soft start feature that is gated by both shutdown and undervoltage lockout conditions.

An output phase reversal pin allows flexibility in configuration of converter types, including inverting and negative topologies.

T, LTC and LT are registered trademarks of Linear Technology Corporation.

AN73-6

## 28V to 5V 20A Buck Converter

### ABSOLUTE MAXIMUM RATINGS

#### (Note 1)

| Supply Voltages                                       |

|-------------------------------------------------------|

| Power Supply Voltage (12V <sub>IN</sub> )–0.3V to 20V |

| Topside Supply Voltage (V <sub>BOOST</sub> )          |

| $V_{TS} - 0.3V$ to $V_{TS} + 20V$ ( $V_{MAX} = 75V$ ) |

| Topside Reference Pin Voltage (TS)–0.3V to 60V        |

| Input Voltages                                        |

| Sense Amplifier Input Common Mode–0.3V to 60V         |

| RUN/SHDN Pin Voltage–0.3V to 12V <sub>IN</sub>        |

| All Other Inputs0.3V to 7V                            |

| Maximum Currents                                      |

| 5V Reference Output Current                           |

| Maximum Temperatures                                  |

| Operating Ambient Temperature Range                   |

| LT1339C 0°C to 70°C                                   |

| LT1339I40°C to 85°C                                   |

| Storage Temperature Range –65°C to 150°C              |

| Lead Temperature (Soldering, 10 sec)                  |

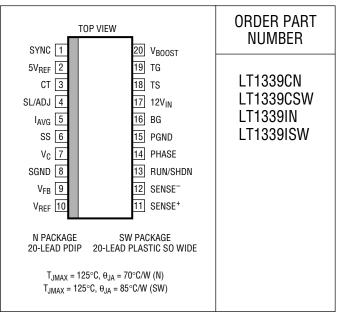

### PACKAGE/ORDER INFORMATION

Consult factory for Military grade parts.

### **ELECTRICAL CHARACTERISTICS**

$12V_{IN} = V_{BOOST} = 12V$ ,  $V_C = 2V$ , TS = 0V,  $V_{FB} = V_{REF} = 1.25V$ ,  $C_{TG} = C_{BG} = 3000$  pF,  $T_A = 25^{\circ}C$  unless otherwise noted.

| SYMBOL                | PARAMETER                                                                                                              | CONDITIONS                        |   | MIN         | ТҮР                 | MAX          | UNITS        |

|-----------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---|-------------|---------------------|--------------|--------------|

| Supply and            | I Protection                                                                                                           |                                   |   |             |                     |              | <u> </u>     |

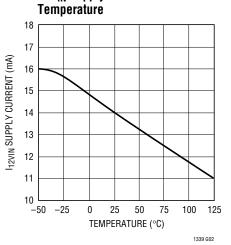

| I <sub>12VIN</sub>    | DC Active Supply Current (Note 2)<br>DC Standby Supply Current                                                         | V <sub>RUN/SHDN</sub> < 0.5V      | • |             | 14<br>150           | 20<br>250    | mA<br>μA     |

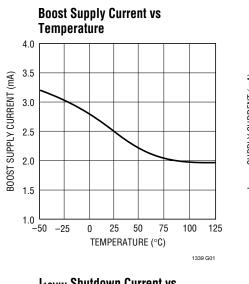

| IBOOST                | DC Active Supply Current (Note 2)<br>DC Standby Supply Current                                                         | V <sub>RUN/SHDN</sub> < 0.5V      |   |             | 2.2<br>0            |              | mA<br>μA     |

| V <sub>RUN/SHDN</sub> | Shutdown Rising Threshold                                                                                              |                                   | • | 1.15        | 1.25                | 1.35         | V            |

| V <sub>SSHYST</sub>   | Shutdown Threshold Hysteresis                                                                                          |                                   |   |             | 25                  |              | mV           |

| I <sub>SS</sub>       | Soft Start Charge Current                                                                                              |                                   | • | 4           | 8                   | 14           | μA           |

| V <sub>UVLO</sub>     | Undervoltage Lockout Threshold - Falling<br>Undervoltage Lockout Threshold - Rising<br>Undervoltage Lockout Hysteresis |                                   | • | 8.20<br>200 | 9.00<br>9.35<br>350 | 9.75<br>9.95 | V<br>V<br>mV |

| 5V Referen            | 100                                                                                                                    |                                   |   |             |                     |              |              |

| V <sub>REF5</sub>     | 5V Reference Voltage                                                                                                   | Line, Load and Temperature        | • | 4.75        | 5.00                | 5.25         | V            |

|                       | 5V Reference Line Regulation                                                                                           | $10V \le 12V_{IN} \le 15V$        | • |             | 3                   | 5            | mV/V         |

| I <sub>REF5</sub>     | 5V Reference Load Range - DC<br>Pulse                                                                                  |                                   | • |             |                     | 10<br>20     | mA<br>mA     |

|                       | 5V Reference Load Regulation                                                                                           | $0 \le I_{REF5} \le 20 \text{mA}$ | • |             | -1.25               | -2           | V/A          |

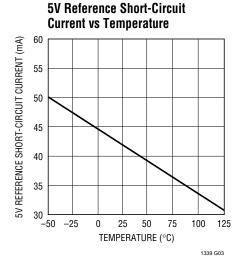

| I <sub>SC</sub>       | 5V Reference Short-Circuit Current                                                                                     |                                   |   |             | 45                  |              | mA           |

### **ELECTRICAL CHARACTERISTICS**

$12V_{IN} = V_{BOOST} = 12V$ ,  $V_C = 2V$ , TS = 0V,  $V_{FB} = V_{REF} = 1.25V$ ,  $C_{TG} = C_{BG} = 3000$  pF,  $T_A = 25^{\circ}C$  unless otherwise noted.

| SYMBOL             | PARAMETER                                                                | CONDITIONS                                                                 |          | MIN            | ТҮР            | MAX               | UNITS    |

|--------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------|----------|----------------|----------------|-------------------|----------|

| Error Amp          | lifier                                                                   |                                                                            |          |                |                |                   |          |

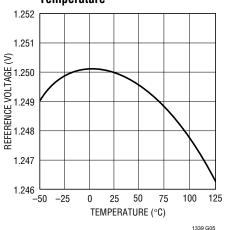

| V <sub>FB</sub>    | Error Amplifier Reference Voltage                                        | Measured at Feedback Pin                                                   | •        | 1.242<br>1.235 | 1.250<br>1.250 | 1.258<br>1.265    | V<br>V   |

| I <sub>FB</sub>    | Feedback Input Current                                                   | V <sub>FB</sub> = V <sub>REF</sub>                                         | •        | 0.1            | 0.5            | 1.0               | μA       |

| 9 <sub>m</sub>     | Error Amplifier Transconductance                                         |                                                                            | •        | 1200           | 2000           | 3200              | μmho     |

| Av                 | Error Amplifier Voltage Gain                                             |                                                                            | •        | 1500           | 3000           |                   | V/V      |

| I <sub>VC</sub>    | Error Amplifier Source Current<br>Error Amplifier Sink Current           | V <sub>FB</sub> – V <sub>REF</sub> = 500mV                                 | •        | 200<br>280     | 275<br>400     |                   | μA<br>μA |

| V <sub>VC</sub>    | Absolute V <sub>C</sub> Clamp Voltage                                    | Measured at V <sub>C</sub> Pin                                             |          |                | 3.5            |                   | V        |

| V <sub>SENSE</sub> | Peak Current Limit Threshold<br>Average Current Limit Threshold (Note 4) | Measured at Sense Inputs<br>Measured at Sense Inputs                       | •        | 170<br>110     | 190<br>120     | 130               | mV<br>mV |

| VIAVG              | Average Current Limit Threshold                                          | Measured at I <sub>AVG</sub> Pin                                           |          |                | 2.5            |                   | V        |

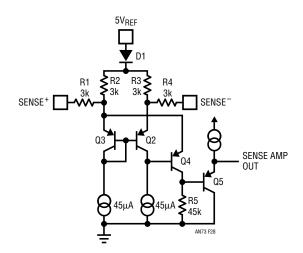

| Current S          | ense Amplifier                                                           |                                                                            | •        |                |                |                   |          |

| Av                 | Amplifier DC Gain                                                        | Measured at I <sub>AVG</sub> Pin                                           |          |                | 15             |                   | V/V      |

| V <sub>OS</sub>    | Amplifier Input Offset Voltage                                           | $2V < V_{CMSENSE} < 60V,$<br>SENSE <sup>+</sup> - SENSE <sup>-</sup> = 5mV | •        | 0.1            |                |                   | mV       |

| I <sub>B</sub>     | Input Bias Current                                                       | Sink (V <sub>CMSENSE</sub> > 5V)<br>Source (V <sub>CMSENSE</sub> = 0V)     | •        |                | 45<br>700      | 75<br>1200        | μA<br>μA |

| Oscillator         |                                                                          |                                                                            |          |                |                |                   |          |

| f <sub>0</sub>     | Operating Frequency, Free Run<br>Frequency Programming Error (Note 3)    | f <sub>0</sub> ≤ 150kHz                                                    | •        | -5             |                | 150<br>5          | kHz<br>% |

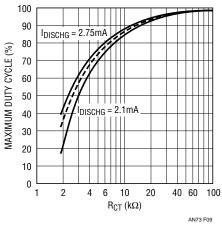

| I <sub>CT</sub>    | Timing Capacitor Discharge Current                                       | LT1339C<br>LT1339I                                                         | •        | 2.20<br>2.10   | 2.50<br>2.50   | 2.75<br>2.75      | mA<br>mA |

| V <sub>SYNC</sub>  | SYNC Input Threshold                                                     | Rising Edge                                                                | •        | 0.8            |                | 2.0               | V        |

| f <sub>SYNC</sub>  | SYNC Frequency Range                                                     | f <sub>SYNC</sub> ≤ 150kHz                                                 | •        | f <sub>0</sub> |                | 1.4f <sub>0</sub> |          |

| Output Dr          | ivers                                                                    | <u> </u>                                                                   | <b>I</b> |                |                |                   |          |

| V <sub>TG,BG</sub> | Undervoltage Output Clamp<br>Standby Mode Output Clamp                   | 12V <sub>IN</sub> ≤ 8V<br>V <sub>RUN</sub> < 0.5V                          | •        |                | 0.4            | 0.7<br>0.1        | V<br>V   |

| V <sub>TG</sub>    | Top Gate On Voltage<br>Top Gate Off Voltage                              |                                                                            | •        | 11.0           | 11.9<br>0.4    | 12.0<br>0.7       | V<br>V   |

| t <sub>TGR</sub>   | Top Gate Rise Time                                                       |                                                                            | •        |                | 130            | 200               | ns       |

| t <sub>TGF</sub>   | Top Gate Fall Time                                                       |                                                                            | •        |                | 60             | 140               | ns       |

| V <sub>BG</sub>    | Bottom Gate On Voltage<br>Bottom Gate Off Voltage                        |                                                                            | •        | 11.0           | 11.9<br>0.4    | 12.0<br>0.7       | V<br>V   |

| t <sub>BGR</sub>   | Bottom Gate Rise Time                                                    |                                                                            | •        |                | 70             | 200               | ns       |

| t <sub>BGF</sub>   | Bottom Gate Fall Time                                                    |                                                                            | •        |                | 60             | 140               | ns       |

The  ${\ensuremath{\bullet}}$  denotes specifications which apply over the full operating temperature range.

**Note 1:** Absolute maximum ratings are those values beyond which the life of a device may be impaired.

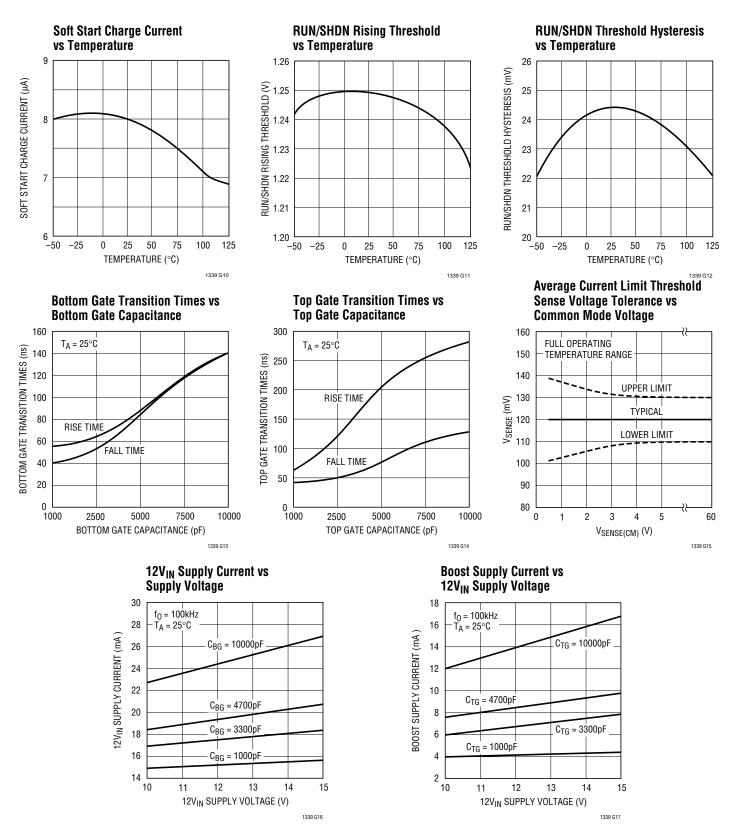

**Note 2:** Supply current specification does not include external FET gate charge currents. Actual supply currents will be higher and vary with operating frequency, operating voltages and the type of external FETs used. See Application Information section.

**Note 3:** Test condition:  $R_{CT} = 16.9k$ ,  $C_{CT} = 1000pF$ .

**Note 4:** Test Condition:  $V_{CMSENSE} = 10V$ .

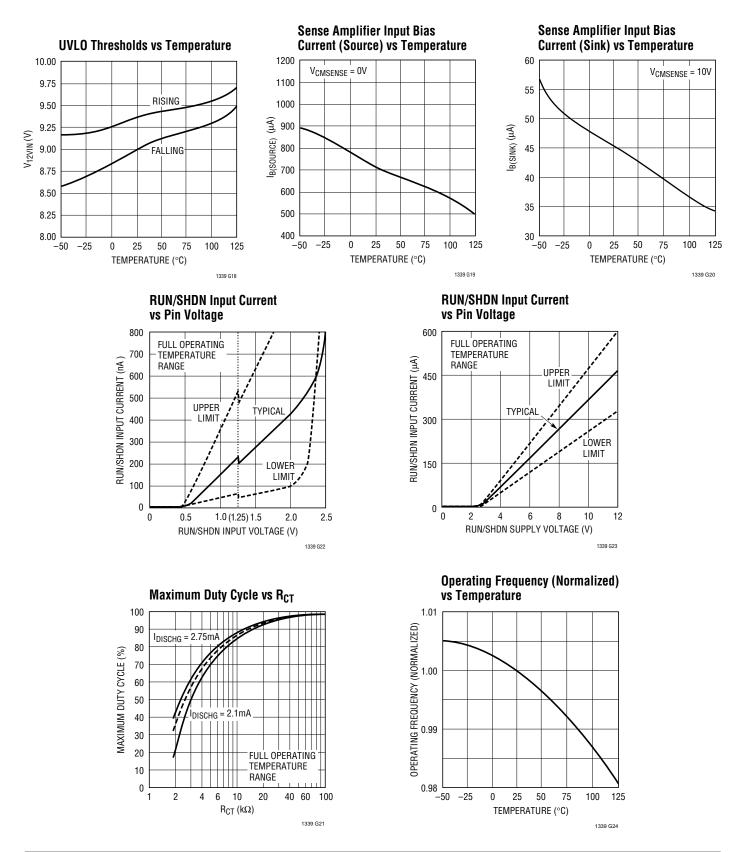

### **TYPICAL PERFORMANCE CHARACTERISTICS**

**12VIN Supply Current vs**

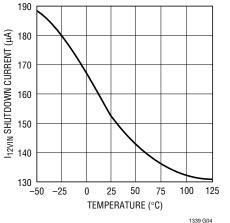

I<sub>12VIN</sub> Shutdown Current vs Temperature

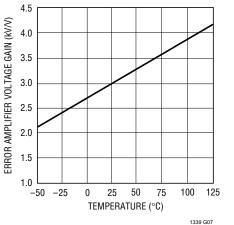

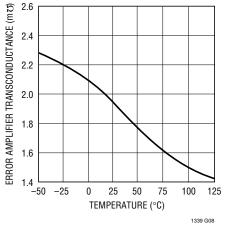

Error Amplifier Voltage Gain vs Temperature

Error Amplifier Transconductance vs Temperature

5V Reference Voltage vs Temperature

Error Amplifier Maximum Source Current vs Temperature

AN73-10

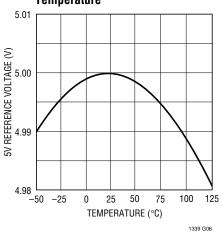

### **TYPICAL PERFORMANCE CHARACTERISTICS**

**TECHNOLOGY**

### **TYPICAL PERFORMANCE CHARACTERISTICS**

### PIN FUNCTIONS

**SYNC (Pin 1):** Oscillator Synchronization Pin with TTL-Level Compatible Input. Input drives internal rising edge triggered one-shot; sync signal on/off times should be  $\geq 1 \mu s$  (10% to 90% DC at 100kHz). Does not contain internal pull-up. Connect to SGND if not used.

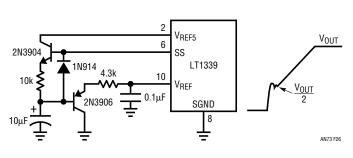

$5V_{REF}$  (Pin 2): 5V Output Reference. Allows connection of external loads up to 10mA DC. (Reference is not available in shutdown.) Typically bypassed with 1µF capacitor to SGND.

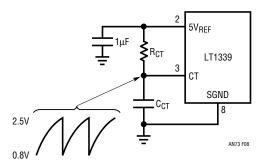

**CT (Pin 3):** Oscillator Timing Pin. Connect a capacitor ( $C_{CT}$ ) to ground and a pull-up resistor ( $R_{CT}$ ) to the 5V<sub>REF</sub> supply. Typical values are CT = 1000pF and 10k  $\leq R_{CT} \leq$  30k.

**SL/ADJ (Pin 4):** Slope Compensation Adjustment. Allows increased slope compensation for certain high duty cycle applications. Resistive loading of the pin increases effective slope compensation. A resistor divider from the  $5V_{REF}$  pin can tailor the onset of additional slope compensation to specific regions in each switch cycle. Pin can be floated or connected to  $5V_{REF}$  if no additional slope compensation is required. (See Applications Information section for slope compensation details.)

**I<sub>AVG</sub> (Pin 5):** Average Current Limit Integration. Frequency response characteristic is set using the  $50k\Omega$  output impedance and external capacitor to ground. Averaging roll-off typically set at 1 to 2 orders of magnitude under switching frequency. (Typical capacitor value ~1000pF for  $f_0 = 100$ kHz.) Shorting this pin to SGND will disable the average current limit function.

**SS (Pin 6):** Soft Start. Generates ramping threshold for regulator current limit during start-up and after UVLO event by sourcing about 8µA into an external capacitor.

$V_C$  (Pin 7): Error Amplifier Output. RC load creates dominant compensation in power supply regulation feedback loop to provide optimum transient response. (See Applications Information section for compensation details.)

**SGND (Pin 8):** Small-Signal Ground. Connect to negative terminal of C<sub>OUT</sub>.

$V_{FB}$  (Pin 9): Error Amplifier Inverting Input. Used as voltage feedback input node for regulator loop. Pin sources about 0.5µA DC bias current to protect from an open feedback path condition.

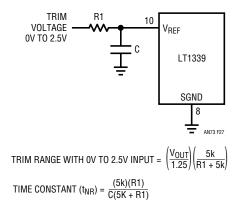

$V_{REF}$  (Pin 10): Bandgap Generated Voltage Reference Decoupling. Connect a capacitor to signal ground. (Typical capacitor value ~0.1  $\mu$ F.)

**SENSE<sup>+</sup> (Pin 11):** Current Sense Amplifier Inverting Input. Connect to most positive (DC) terminal of current sense resistor.

**SENSE**<sup>-</sup> (**Pin 12**): Current Sense Amplifier Noninverting Input. Connect to most negative (DC) terminal of current sense resistor.

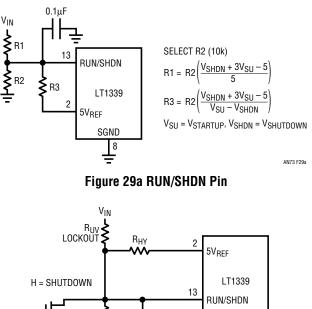

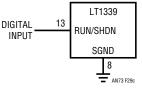

**RUN/SHDN (Pin 13):** Precision Referenced Shutdown. Can be used as logic level input for shutdown control or as an analog monitor for input supply undervoltage protection, etc. IC is enabled when RUN/SHDN pin rising edge exceeds 1.25V. About 25mV of hysteresis helps assure stable mode switching. All internal functions are disabled in shutdown mode. If this function is not desired, connect RUN/SHDN to  $12V_{IN}$  (typically through a 100k resistor). See Applications Information section.

**PHASE (Pin 14):** Output Driver Phase Control. If Pin 14 is not connected (floating), the topside driver operates the main switch, with the bottom side driver operating the synchronous switch. Shorting Pin 14 to ground reverses the roles of the output drivers. PHASE is typically shorted to ground for inverting and boost configurations. Positive buck configuration requires the PHASE pin to float. See Applications Information section.

**PGND (Pin 15):** Power Ground. References the bottom side output switch and internal driver control circuits. Connect with low impedance trace to  $V_{IN}$  decoupling capacitor negative (ground) terminal.

**BG (Pin 16):** Bottom Side Output Driver. Connects to gate of bottom side external power FET.

$12V_{\text{IN}}$  (Pin 17): 12V Power Supply Input. Bypass with at least  $1\mu\text{F}$  to PGND.

**TS (Pin 18):** Boost Output Driver Reference. Typically connects to source of topside external power FET and inductive switch node.

**TG (Pin 19):** Topside (Boost) Output Driver. Connects to gate of topside external power FET.

$V_{BOOST}$  (Pin 20): Topside Power Supply. Bootstrapped via 1µF capacitor tied to switch node (Pin 18) and Schottky diode connected to the 12V<sub>IN</sub> supply.

#### VIN PHASE CT 5V<sub>REF</sub> 12V<sub>IN</sub> VBOOST MAIN SWITCH TS NONOVERLAPPING SWITCH LOGIC BG SYNC SWITCH பா UVLO CIRCUIT OSC ▲ SL/ADJ ONE SHOT SYNC SENSE SRSENSE $\times 15$ SENSE<sup>-</sup> IC1 V<sub>OUT</sub> CURRENT + 0.5µA SENSE AMP ന $V_{FB}$ $\mathcal{T}$ ΕA $\mathsf{V}_{\mathsf{REF}}$ 1.25V Œ 2.5V 5V<sub>REF</sub> 5V 8μΑ 50k REFERENCE SOFT START AVERAGE CURRENT RUN/SHDN LIMIT CIRCUIT П ENABLE 1.25V IAVG 1339 • BD

### FUNCTIONAL BLOCK DIAGRAM

### **OPERATION** (Refer to Functional Block Diagram)

#### **Basic Control Loop**

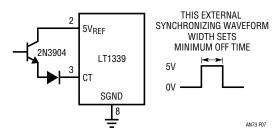

The LT1339 uses a constant frequency, current mode synchronous architecture. The timing of the IC is provided through an internal oscillator circuit, which can be synchronized to an external clock, programmable to operate at frequencies up to 150kHz. The oscillator creates a modified sawtooth wave at its timing node (CT) with a slow charge, rapid discharge characteristic.

During typical positive buck operation, the main switch MOSFET is enabled at the start of each oscillator cycle. The main switch stays enabled until the current through the switched inductor, sensed via the voltage across a series sense resistor ( $R_{SENSE}$ ), is sufficient to trip the current comparator (IC1) and, in turn, reset the RS latch. When the RS latch resets, the main switch is disabled, and the synchronous switch MOSFET is enabled. Shoot-through prevention logic prohibits enabling of the synchronous switch until the main switch is fully disabled. If the current comparator threshold is not obtained throughout the entire oscillator charge period, the RS latch is bypassed and the main switch is disabled during the oscillator discharge time. This "minimum off time" assures adequate charging of the bootstrap supply, protects the main switch, and is typically about 1 $\mu$ s.

### **OPERATION** (Refer to Functional Block Diagram)

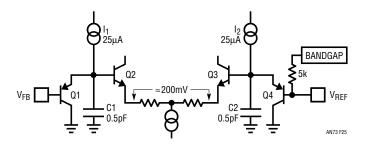

The current comparator trip threshold is set on the  $V_C$  pin, which is the output of a transconductance amplifier, or error amplifier (EA). The error amplifier integrates the difference between a feedback voltage (on the  $V_{FB}$  pin) and an internal bandgap generated reference voltage of 1.25V, forming a signal that represents required load current. If the supplied current is insufficient for a given load, the output will droop, thus reducing the feedback voltage. The error amplifier forces current out of the  $V_C$  pin, increasing the current comparator threshold. Thus, the circuit will servo until the provided current is equal to the required load and the average output voltage is at the value programmed by the feedback resistors.

#### Average Current Limit

The output of the sense amplifier is monitored by a single pole integrator comprised of an external capacitor on the  $I_{AVG}$  pin and an internal impedance of approximately  $50k\Omega$ . If this averaged value signal exceeds a level corresponding to 120mV across the external sense resistor, the current comparator threshold is clamped and cannot continue to rise in response to the error amplifier. Thus, if average load current requirements exceed 120mV/R<sub>SENSE</sub>, the supply will current limit and the output voltage will fall out of regulation. The average current limit circuit monitors the sense amplifier output without slope compensation or ripple current contributions, therefore the average load current limit threshold is unaffected by duty cycle.

#### Undervoltage Lockout

The LT1339 employs an undervoltage lockout circuit (UVLO) that monitors the 12V supply rail. This circuit disables the output drive capability of the LT1339 if the 12V supply drops below about 9V. Unstable mode switching is prevented through 350mV of UVLO threshold hysteresis.

#### Adaptive Nonoverlapping Output Stage

The FET driver output stage implements adaptive nonoverlapping control. This circuitry maintains dead time independent of the type, size or operating conditions of the switch elements. The control circuit monitors the output gate drive signals, insuring that the switch gate (being disabled) is fully discharged before enabling the other switch driver.

#### Shutdown

The LT1339 can be put into low current shutdown mode by pulling the RUN/SHDN pin low, disabling all circuit functions. The shutdown threshold is a bandgap referred voltage of 1.25V typical. Use of a precision threshold on the shutdown circuit enables use of this pin for undervoltage protection of the  $V_{IN}$  supply and/or power supply sequencing.

#### Soft Start

The LT1339 incorporates a soft start function that operates by slowly increasing the internal current limit. This limit is controlled by clamping the V<sub>C</sub> node to a low voltage that climbs with time as an external capacitor on the SS pin is charged with about  $8\mu$ A. This forces a graceful climb of output current capability, and thus a graceful increase in output voltage until steady-state regulation is achieved. The soft start timing capacitor is clamped to ground during shutdown and during undervoltage lockout, yielding a graceful output recovery from either condition.

#### **5V Internal Reference**

Power for the oscillator timing elements and most other internal LT1339 circuits is derived from an internal 5V reference, accessible at the  $5V_{REF}$  pin. This supply pin can be loaded with up to 10mA DC (20mA pulsed) for convenient biasing of local elements such as control logic, etc.

#### **Slope Compensation**

For duty cycles greater than 50%, slope compensation is required to prevent current mode duty cycle instability in the regulator control loop. The LT1339 employs internal slope compensation that is adequate for most applications. However, if additional slope compensation is desired, it is available through the SL/ADJ pin. Excessive slope compensation will cause reduction in maximum load current capability and therefore is not desirable.

#### R<sub>SENSE</sub> Selection for Output Current

$R_{SENSE}$  generates a voltage that is proportional to the inductor current for use by the LT1339 current sense amplifier. The value of  $R_{SENSE}$  is based on the required load current. The average current limit function has a typical threshold of 120mV/R\_{SENSE}, or:

$R_{SENSE} = 120 mV/I_{LIMIT}$

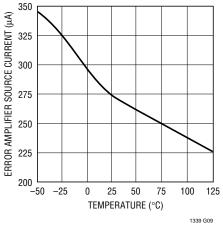

Operation with  $V_{SENSE}$  common mode voltage below 4.5V may slightly degrade current limit accuracy. See Average Current Limit Threshold Tolerance vs Common Mode Voltage curve in the Typical Performance Characteristics section for more information.

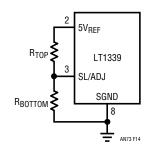

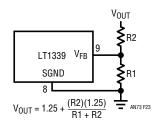

#### **Output Voltage Programming**

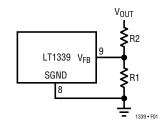

Output voltage is programmed through a resistor feedback network to  $V_{FB}$  (Pin 9) on the LT1339. This pin is the inverting input of the error amplifier, which is internally referenced to 1.25V. The divider is ratioed to provide 1.25V at the  $V_{FB}$  pin when the output is at its desired value.

The output voltage is thus set following the relation:

$V_{OUT} = 1.25(1 + R2/R1)$

when an external resistor divider is connected to the output as shown in Figure 1.

Figure 1. Programming LT1339 Output Voltage

If high value feedback resistors are used, the input bias current of the V<sub>FB</sub> pin (1 $\mu$ A maximum) could cause a slight increase in output voltage. A Thevenin resistance at the V<sub>FB</sub> pin of <5k is recommended.

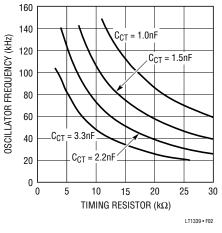

### Oscillator Components $\mathbf{R}_{\text{CT}}$ and $\mathbf{C}_{\text{CT}}$

The LT1339 oscillator creates a modified sawtooth wave at its timing node (CT) with a slow charge, rapid discharge characteristic. The rapid discharge time corresponds to the minimum off-time of the PWM controller. This limits maximum duty cycle ( $\rm DC_{MAX}$ ) to:

$DC_{MAX} = 1 - (t_{DISCH})(f_0)$

This relation corresponds to the minimum value of the timing resistor ( $R_{CT}$ ), which can be determined according to the following relation ( $R_{CT}$  vs DC<sub>MAX</sub> graph appears in the Typical Performance Characteristics section):

$$R_{CT(MIN)} \approx [(0.8)(10^{-3})(1 - DC_{MAX})]^{-1}$$

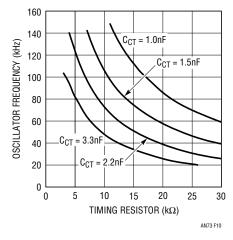

Values for  $R_{CT} > 15k$  yield maximum duty cycles above 90%. Given a timing resistor value, the value of the timing capacitor ( $C_{CT}$ ) can then be determined for desired operating frequency ( $f_0$ ) using the relation:

$$C_{\text{CT}} \approx \frac{\left(1/f_{0}\right) - \left(100\right)\left(10^{-9}\right)}{\left(R_{\text{CT}}/1.85\right) + \frac{1.75}{\left(2.5\right)\left(10^{-3}\right) - \left(3.375/R_{\text{CT}}\right)}}$$

A plot of Operating Frequency vs  $R_{CT}$  and  $C_{CT}$  is shown in Figure 2. Typical 100kHz operational values are  $C_{CT}$  = 1000pF and  $R_{CT}$  = 16.9k.

Figure 2. Oscillator Frequency vs  $R_{CT},\,C_{CT}$

### Average Current Limit

The average current limit function is implemented using an external capacitor ( $C_{AVG}$ ) connected from  $I_{AVG}$  to SGND that forms a single pole integrator with the 50k $\Omega$  output

impedance of the  $I_{AVG}$  pin. The integrator corner frequency is typically set 1 to 2 orders of magnitude below the oscillator frequency and follows the relation:

$$f_{-3dB} = (3.2)(10^{-6})/C_{AVG}$$

The average current limit function can be disabled by shorting the  $I_{AVG}\xspace$  pin directly to SGND.

#### Soft Start Programming

The current control pin (V<sub>C</sub>) limits sensed inductor current to zero at voltages less than a transistor V<sub>BE</sub>, to full average current limit at V<sub>C</sub> = V<sub>BE</sub> + 1.8V. This generates a 1.8V full regulation range for average load current. An internal voltage clamp forces the V<sub>C</sub> pin to a V<sub>BE</sub> – 100mV above the SS pin voltage. This 100mV "dead zone" assures 0% duty cycle operation at the start of the soft start cycle, or when the soft start pin is pulled to ground. Given the typical soft start current of 8µA and a soft start timing capacitor C<sub>SS</sub>, the start-up delay time to full available average current will be:

$t_{SS} = (1.5)(10^5)(C_{SS})$

#### Boost Supply

The  $V_{BOOST}$  supply is bootstrapped via an external capacitor. This supply provides gate drive to the topside switch FET. The bootstrap capacitor is charged from  $12V_{IN}$  through a diode when the switch node is pulled low.

The diode reverse breakdown voltage must be greater than  $V_{IN}$  + 12 $V_{IN}$ . The bootstrap capacitor should be at least 100 times greater than the total input capacitance of the topside FET. A capacitor in the range of 0.1µF to 1µF is generally adequate for most applications.

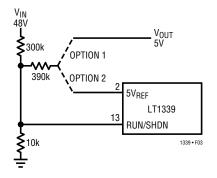

## Shutdown Function—Input Undervoltage Detect and Threshold Hysteresis

The LT1339 RUN/SHDN pin uses a bandgap generated reference threshold of about 1.25V. This precision threshold allows use of the RUN/SHDN pin for both logic-level shutdown applications and analog monitoring applications such as power supply sequencing.

Because an LT1339 controlled converter is a power transfer device, a voltage that is lower than expected on the input supply could require currents that exceed the sourcing capabilities of that supply, causing the system to lock up in an undervoltage state. Input supply start-up protection can be achieved by enabling the RUN/SHDN pin using a resistor divider from the input supply to ground. Setting the divider output to 1.25V when that supply is almost fully enabled prevents the LT1339 regulator from drawing large currents until the input supply is able to provide the required power.

If additional hysteresis is desired for the enable function, an external feedback resistor can be used from the LT1339 regulator output. If connection to the regulator output is not desired, the  $5V_{REF}$  internal supply pin can be used. Figure 3 shows a resistor connection on a 48V to 5V converter that yields a 40V V<sub>IN</sub> start-up threshold for regulator enable and also provides about 10% input referred hysteresis.

Figure 3. Input Supply Sequencing Programming

The shutdown function can be disabled by connecting the RUN/SHDN pin to the  $12V_{\rm IN}$  rail. This pin is internally clamped to 2.5V through a 20k series input resistance and will therefore draw about 0.5mA when tied directly to 12V. This additional current can be minimized by making the connection through an external resistor (100k is typically used).

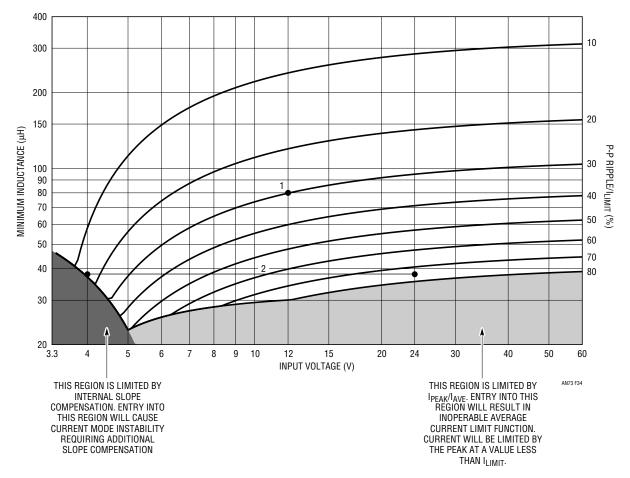

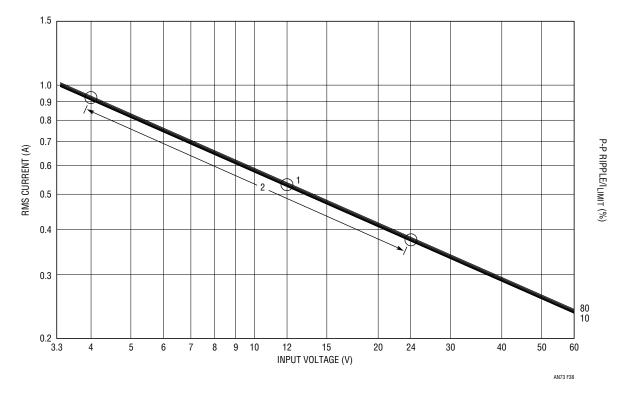

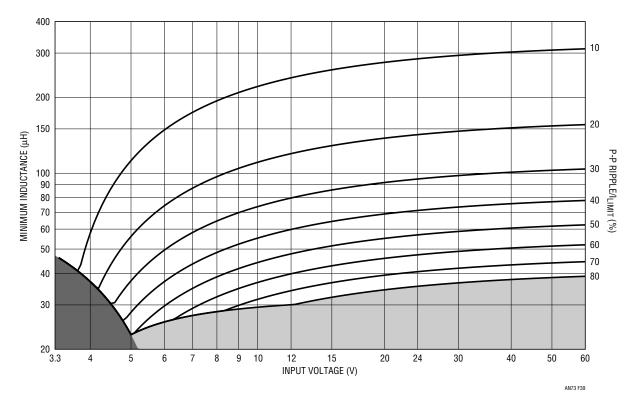

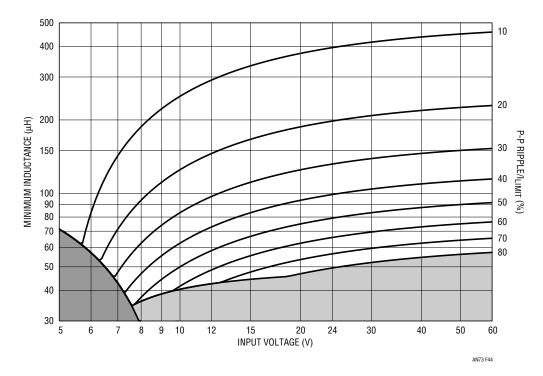

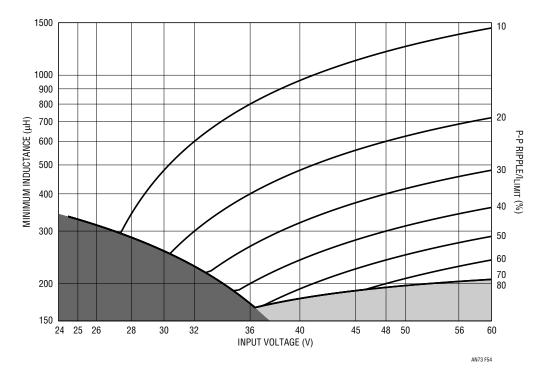

#### **Inductor Selection**

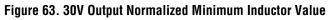

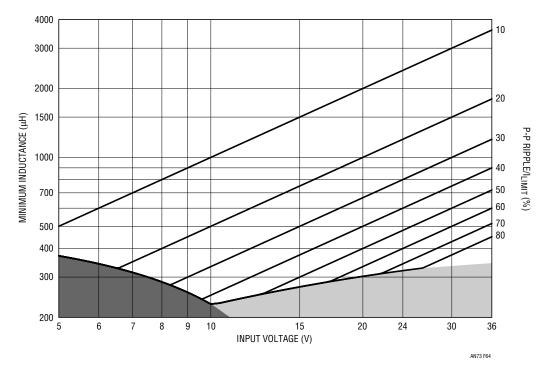

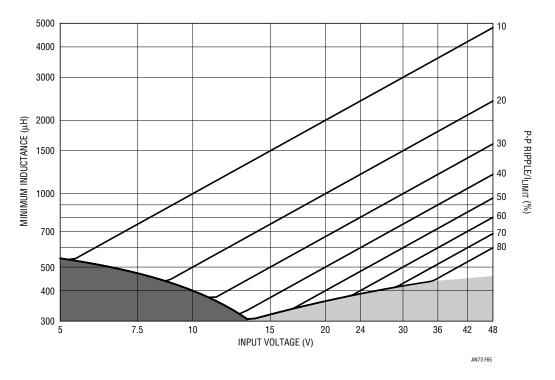

The inductor for an LT1339 converter is selected based on output power, operating frequency and efficiency requirements. Generally, the selection of inductor value can be reduced to desired maximum ripple current in the inductor ( $\Delta$ I). For a buck converter, the minimum inductor value for a desired maximum operating ripple current can be determined using the following relation:

$$L_{MIN} = \frac{(V_{OUT})(V_{IN} - V_{OUT})}{(\Delta I)(f_0)(V_{IN})}$$

where  $f_0$  = operating frequency. Given an inductor value (L), the peak inductor current is the sum of the average inductor current ( $I_{AVG}$ )and half the inductor ripple current ( $\Delta I$ ), or:

$$I_{PK} = I_{AVG} + \frac{(V_{OUT})(V_{IN} - V_{OUT})}{(2)(L)(f_0)(V_{IN})}$$

The inductor core type is determined by peak current and efficiency requirements. The inductor core must withstand peak current without saturating, and series winding resistance and core losses should be kept as small as is practical to maximize conversion efficiency.

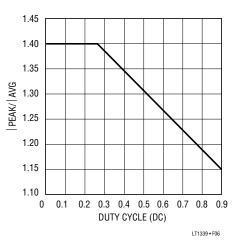

The LT1339 peak current limit threshold is 40% greater than the average current limit threshold. Slope compensation effects reduce this margin as duty cycle increases. This margin must be maintained to prevent peak current limit from corrupting the programmed value for average current limit. Programming the peak ripple current to less than 15% of the desired average current limit value will assure porper operation of the average current limit feature through 90% duty cycle (see Slope Compensation section).

#### **Oscillator Synchronization**

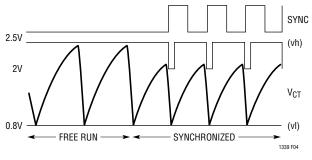

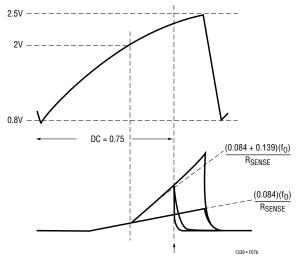

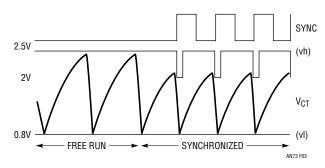

The LT1339 oscillator generates a modified sawtooth waveform at the C<sub>T</sub> pin between low and high thresholds of about 0.8V (vl) and 2.5V (vh) respectively. The oscillator can be synchronized by driving a TTL level pulse into the SYNC pin. This inputs to a one-shot circuit that reduces the oscillator high threshold to 2V for about 200ns. The SYNC input signal should have minimum high/low times of  $\geq 1 \mu s$ .

#### **Slope Compensation**

Current mode switching regulators that operate with a duty cycle greater than 50% and have continuous inductor current can exhibit duty cycle instability. While a regulator will not be damaged and may even continue to function

Figure 4. Free Run and Synchronized Oscillator Waveforms (at  $\ensuremath{\mathsf{C}_T}$  Pin)

acceptably during this type of subharmonic oscillation, an irritating high-pitched squeal is usually produced.

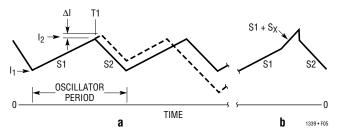

The criterion for current mode duty cycle instability is met when the increasing slope of the inductor ripple current is less than the decreasing slope, which is the case at duty cycles greater than 50%. This condition is illustrated in Figure 5a. The inductor ripple current starts at  $I_1$ , at the beginning of each oscillator switch cycle. Current increases at a rate S1 until the current reaches the control trip level 12. The controller servo loop then disables the main switch (and enables the synchronous switch) and inductor current begins to decrease at a rate S2. If the current switch point  $(I_2)$  is perturbed slightly and increased by  $\Delta I$ , the cycle time ends such that the minimum current point is increased by a factor of (1 + S2/S1)to start the next cycle. On each successive cycle, this error is multiplied by a factor of S2/S1. Therefore, if S2/S1 is  $\geq$  1, the system is unstable.

Subharmonic oscillations can be eliminated by augmenting the increasing ripple current slope (S1) in the control loop. This is accomplished by adding an artificial ramp on the inductor current waveform internal to the IC (with a slope  $S_X$ ) as shown in Figure 5b. If the sum of the slopes S1 +  $S_X$  is greater than S2, the condition for subharmonic oscillation no longer exists.

For a buck converter, the required additional current waveform slope, or "Slope Compensation," follows the relation:

$$S_{X} \ge \left(\frac{V_{IN}}{L}\right)(2DC-1)$$

Figure 5. Inductor Current at DC > 50% and Slope Compensation Adjusted Signal

For duty cycles less than 50% (DC < 0.5),  $S_X$  is negative and is not required. For duty cycles greater than 50%,  $S_X$ takes on values dependent on S1 and duty cycle. This leads to a minimum inductance requirement for a given  $V_{IN}$  and duty cycle of:

$$L_{\rm MIN} = \left(\frac{V_{\rm IN}}{S_{\rm X}}\right) (2DC - 1)$$

The LT1339 contains an internal  $S_X$  slope compensation ramp that has an equivalent current referred value of:

$$0.084 \left( \frac{f_0}{R_{SENSE}} \right)$$

Amp/s

where  $f_0$  is oscillator frequency. This yields a minimum inductance requirement of:

$$L_{MIN} \ge \frac{(V_{IN})(R_{SENSE})(2DC-1)}{(0.084)(f_0)}$$

A down side of slope compensation is that, since the IC servo loop senses an increase in perceived inductor current, the internal current limit functions are affected such that the maximum current capability of a regulator is reduced by the same amount as the effective current referred slope compensation. The LT1339, however, uses a current limit scheme that is independent of slope compensation effects (average current limit). This provides operation at any duty cycle with no reduction in current sourcing capability, provided ripple current peak amplitude is less than 15% of the current limit value. For example, if the supply is set up to current limit at 10A, as long as the peak inductor current is less than 11.5A, duty cycles up to 90% can be achieved without compromising the average current limit value.

If an inductor smaller than the minimum required for internal slope compensation (calculated above as  $L_{MIN}$ ) is desired, additional slope compensation is required. The LT1339 provides this capability through the SL/ADJ pin. This feature is implemented by referencing this pin via a resistor divider from the 5V<sub>REF</sub> pin to ground. The additional slope compensation will be affected at the point in the oscillator waveform (at pin CT) corresponding to the voltage set by the resistor divider. Additional slope compensation can be calculated using the relation:

$$S_{XADD} = \frac{(2500)(f_0)}{(R_{EQ})(R_{SENSE})}$$

Amp/s

where  $R_{EQ}$  is the effective resistance of the resistor divider. Actual compensation will be somewhat greater due to internal curvature correction circuitry that imposes an exponential increase in the slope compensation waveform, further increasing the effective compensation slope up to 20% for a given setting.

Figure 6. Maximum Ripple Current (Normalized) vs Duty Cycle for Average Current Limit

Design Example:

$$\label{eq:VIN} \begin{split} V_{IN} &= 20V\\ V_{OUT} &= 15V \;(DC = 0.75)\\ R_{SENSE} &= 0.01\Omega\\ f_0 &= 100 \text{kHz}\\ L &= 5\mu\text{H} \end{split}$$

The minimum inductor usable with no additional slope compensation is:

$$L_{\text{MIN}} \ge \frac{(20V)(0.01\Omega)(1.5-1)}{(0.084)(100000)} = 11.9\mu\text{H}$$

Since L =  $5\mu$ H is less than L<sub>MIN</sub>, additional slope compensation is necessary. The total slope compensation required is:

$$S_X \ge \left(\frac{20V}{5\mu H}\right) (1.5 - 1) = (2) (10^6)$$

Amp/s

Subtracting the internally generated slope compensation and solving for the required effective resistance at SL/ADJ yields:

$$R_{EQ} \le \frac{(2500)(f_0)}{(2)(10^6)(R_{SENSE}) - (0.084)(f_0)} = 21.5k$$

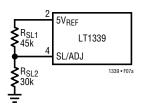

Setting the resistor divider reference voltage at 2V assures that the additional compensation waveform will be enabled at 75% duty cycle. As shown in Figure 7a, using

Figure 7a. External Slope Compensation Resistors

Figure 7b. Slope Compensation Waveforms

$R_{SL1}$  = 45k and  $R_{SL2}$  = 30k sets the desired reference voltage and has a  $R_{EQ}$  of 18k, which meets both design requirements. Figure 7b shows the slope compensation effective waveforms both with and without the SL/ADJ external resistors.

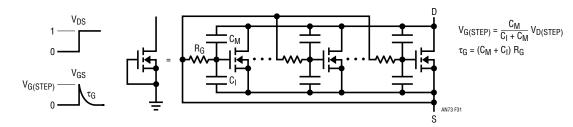

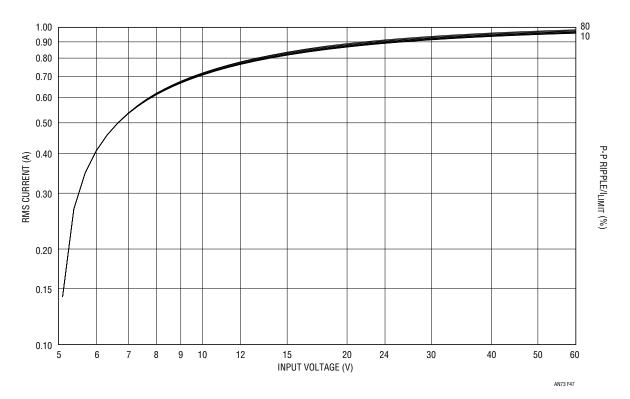

#### **Power MOSFET and Catch Diode Selection**

External N-channel MOSFET switches are used with the LT1339. The positive gate-source drive voltage of the LT1339 for both switches is roughly equivalent to the  $12V_{\rm IN}$  supply voltage, so standard threshold MOSFETs can be used.

Selection criteria for the power MOSFETs include the "ON" resistance ( $R_{DS(ON)}$ ), reverse transfer capacitance ( $C_{RSS}$ ), maximum drain-source voltage ( $V_{DSS}$ ) and maximum output current.

The power FETs selected must have a maximum operating  $V_{DSS}$  exceeding the maximum  $V_{IN}.\,V_{GS}$  voltage maximum must exceed the  $12V_{IN}$  supply voltage.

Once voltage requirements have been determined,  $R_{DS(ON)}$  can be selected based on allowable power dissipation and required output current.

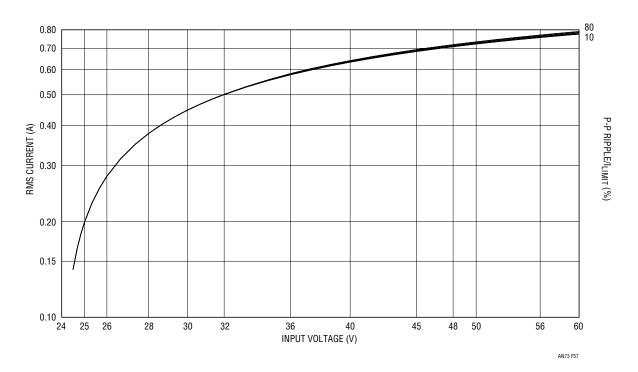

In an LT1339 buck converter, the average inductor current is equal to the DC load current. The average currents through the main and synchronous switches are:

$$I_{MAIN} = (I_{LOAD})(DC)$$

$I_{SYNC} = (I_{LOAD})(1 - DC)$

The  $\mathsf{R}_{DS(ON)}$  required for a given conduction loss can be calculated using the relation:

$\mathsf{P}_{\mathsf{LOSS}} = (\mathsf{I}_{\mathsf{SWITCH}})^2(\mathsf{R}_{\mathsf{DS}(\mathsf{ON})})$

In high voltage applications ( $V_{IN} > 20V$ ), the topside switch is required to slew very large voltages. As  $V_{IN}$  increases, transition losses increase through a square relation, until it becomes the dominant power loss term in the main switch. This transition loss takes the form:

$P_{TR}\approx (k)(V_{IN})^2(I_{MAX})(C_{RSS})(f_0)$

where k is a constant inversely related to the gate drive current, approximated by k = 2 in LT1339 applications.

The maximum power loss terms for the switches are thus:

$P_{MAIN} = (DC)(I_{MAX})^{2}(1 + \delta)(R_{DS(ON)}) + 2(V_{IN})^{2}(I_{MAX})(C_{RSS})(f_{0})$   $P_{SYNC} = (1 - DC)(I_{MAX})^{2}(1 + \delta)(R_{DS(ON)})$

The  $(1 + \delta)$  term in the above relations is the temperature dependency of  $R_{DS(ON)}$ , typically given in the form of a normalized  $R_{DS(ON)}$  vs Temperature curve in a MOSFET data sheet.

In some applications, parasitic FET capacitances couple the negative going switch node transient onto the bottom gate drive pin of the LT1339, causing a negative voltage in excess of the Absolute Maximum Rating to be imposed on that pin. Connection of a catch Schottky (rated to about 1A is typically sufficient) from this pin to ground will eliminate this effect.

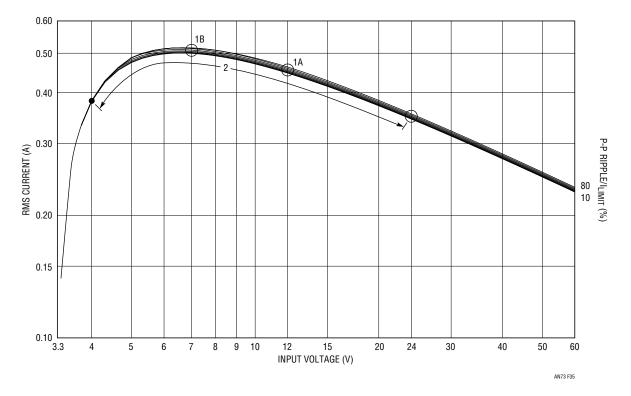

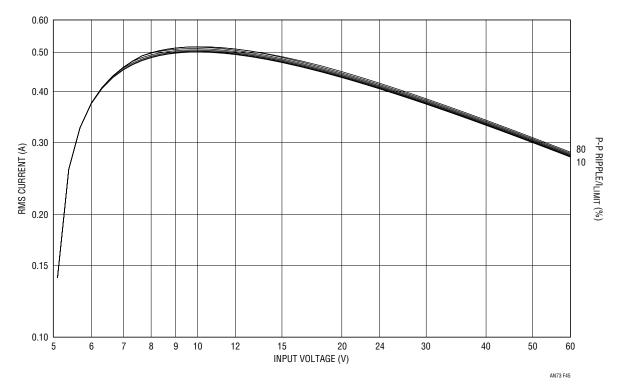

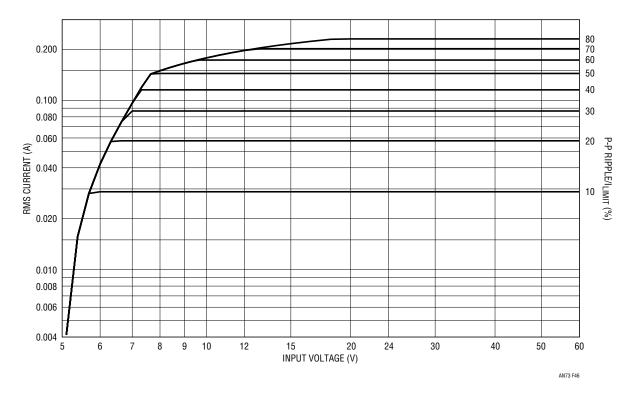

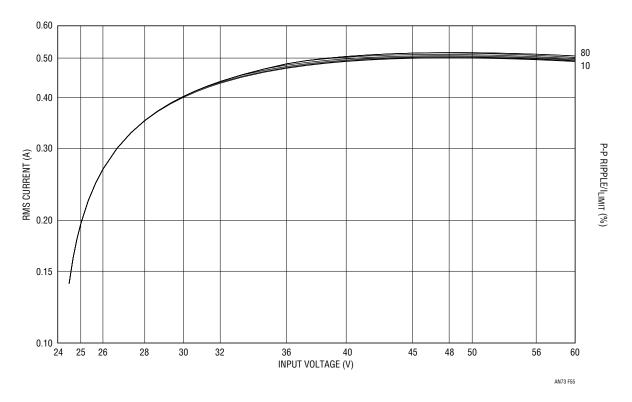

#### $C_{\rm IN}$ and $C_{\rm OUT}$ Supply Decoupling Capacitor Selection

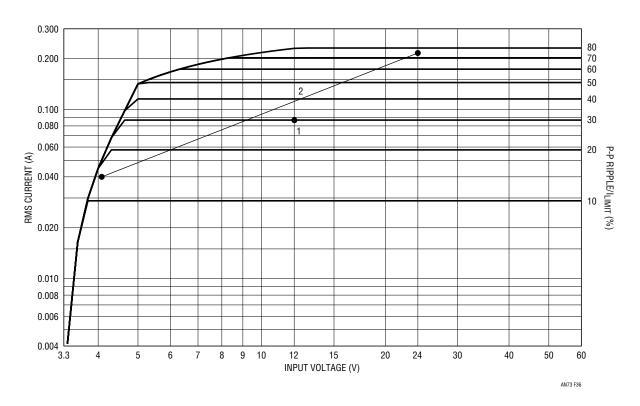

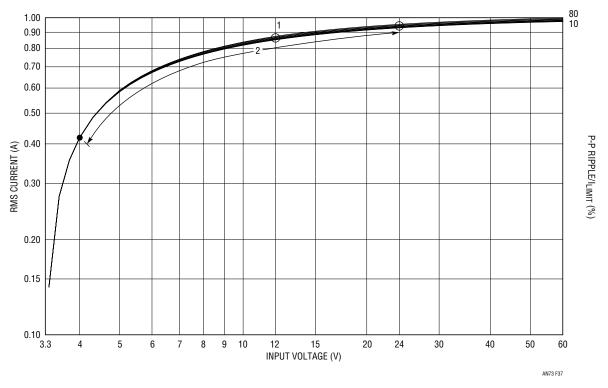

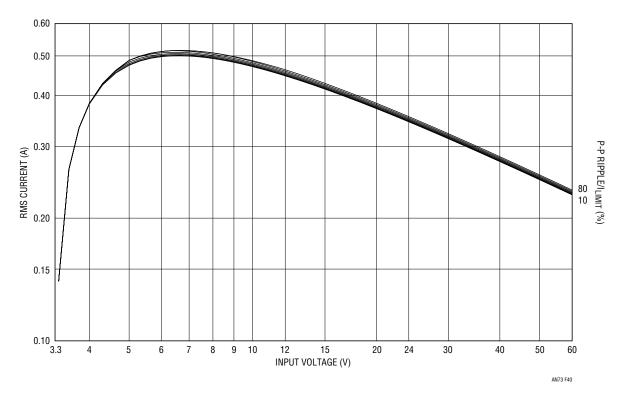

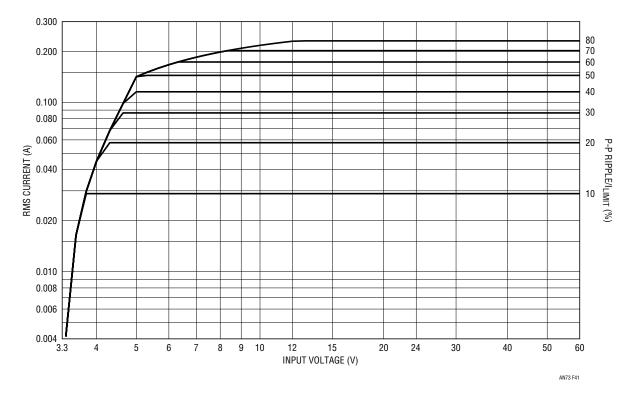

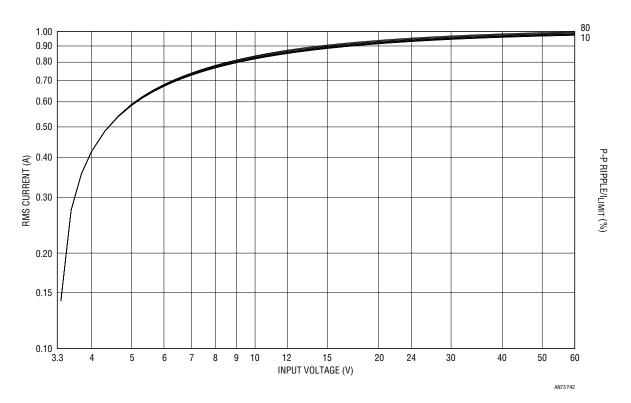

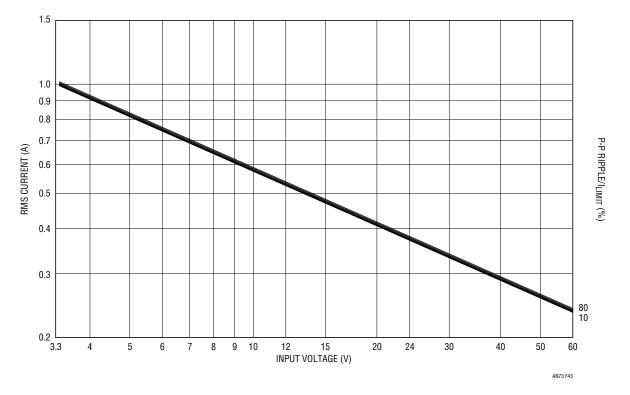

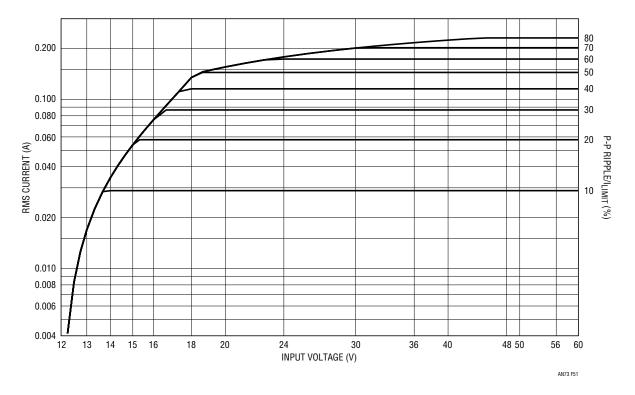

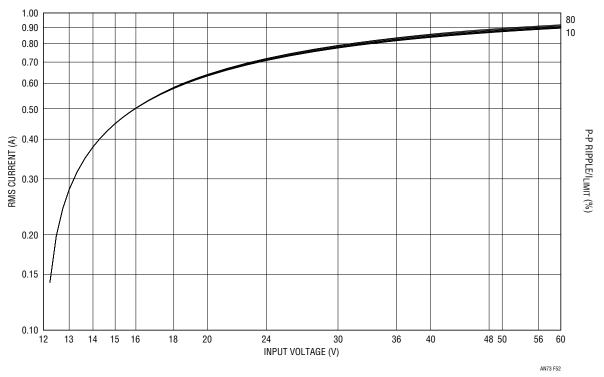

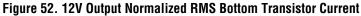

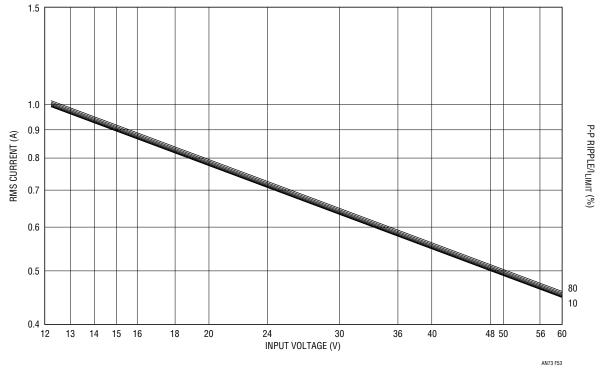

The large currents typical of LT1339 applications require special consideration for the converter input and output supply decoupling capacitors. Under normal steady state operation, the source current of the main switch MOSFET is a square wave of duty cycle  $V_{OUT}/V_{IN}$ . Most of this current is provided by the input bypass capacitor. To prevent large input voltage transients and avoid bypass capacitor heating, a low ESR input capacitor sized for the maximum RMS current follows the relation:

$$I_{\text{RMS}} \approx \frac{(I_{\text{MAX}})(V_{\text{OUT}}(V_{\text{IN}} - V_{\text{OUT}}))^{1/2}}{V_{\text{IN}}}$$

which peaks at a 50% duty cycle, when  $I_{RMS} = I_{MAX}/2$ . Capacitor ripple current ratings are often based on only 2000 hours (three months) lifetime; it is advisable to derate either the ESR or temperature rating of the capacitor for increased MTBF of the regulator.

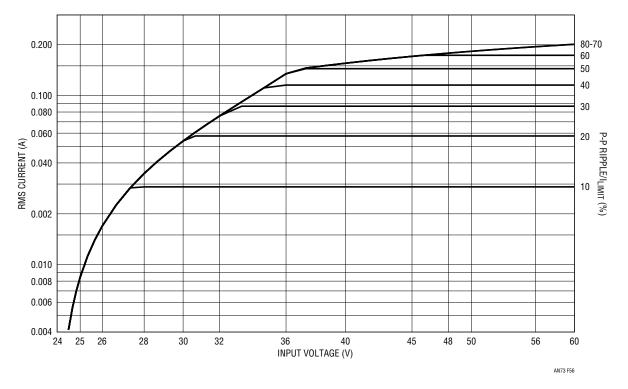

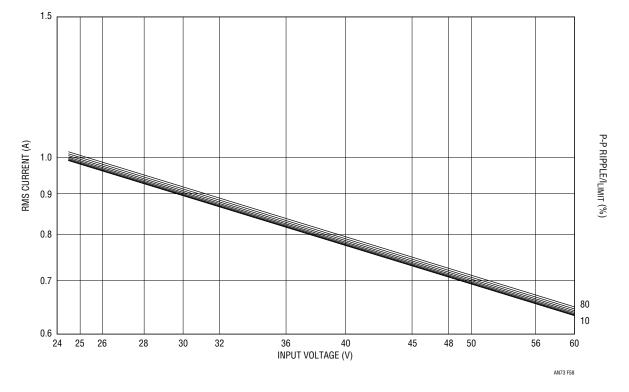

The output capacitor in a buck converter generally has much less ripple current than the input capacitor. Peak-to-peak ripple current is equal to that in the inductor ( $\Delta I_L$ ), typically a fraction of the load current. C<sub>OUT</sub> is selected to reduce output voltage ripple to a desirable value given an expected output ripple current. Output ripple ( $\Delta V_{OUT}$ ) is approximated by:

$\Delta V_{OUT} \approx \Delta I_{L} \{ \text{ESR} + [(4)(f_0) \bullet C_{OUT}]^{-1} \}$ where  $f_0$  = operating frequency.

#### **Efficiency Considerations and Heat Dissipation**

High output power applications have inherent concerns regarding power dissipation in converter components. Although high efficiencies are achieved using the LT1339, the power dissipated in the converter climbs to relatively high values when the load draws large amounts of power. Even at 90% efficiency, an application that provides 500W to the load has conversion loss of 55W.

I<sup>2</sup>R dissipation through the switches, sense resistor and inductor series resistance create substantial losses under high currents. Generally, the dominant I<sup>2</sup>R loss is evident in the FET switches. Loss in each switch is proportional to the conduction time of that switch. For example, in a 48V to 5V converter the synchronous FET conducts load current for almost 90% of the cycle time and thus, requires greater consideration for dissipating I<sup>2</sup>R power.

Gate charge/discharge current creates additional current drain on the 12V supply. If powered from a high voltage input through a linear regulator, the losses in that regulator device can become significant. A supply solution bootstrapped from the output would draw current from a lower voltage source and reduce this loss component.

Transition losses are significant in the topside switch FET when high  $V_{\text{IN}}$  voltages are used. Transition losses can be estimated as:

$$P_{TLOSS} \approx 2(V_{IN})^2(I_{MAX})(C_{RSS})(f_0)$$

Since the conduction time in the main switch of a 48V to 5V converter is small, the  $I^2R$  loss in the main switch FET is also small. However, since the FET gate must switch up past the 48V input voltage, transition loss can become a significant factor. In such a case, it is often prudent to take the increased  $I^2R$  loss of a smaller FET in order to reduce  $C_{RSS}$  and thus, the associated transition losses.

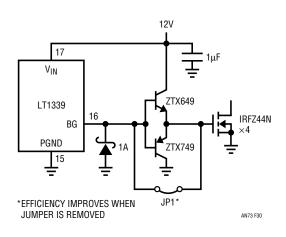

#### **Gate Drive Buffers**

The LT1339 is designed to drive relatively large capacitive loads. However, in certain applications, efficiency improvements can be realized by adding an external buffer stage to drive the gates of the FET switches. When the

switch gates load the driver outputs such that rise/fall times exceed about 100ns, buffers can sometimes result in efficiency gains. Buffers also reduce the effect of back injection into the bottom side driver output due to coupling of switch node transitions through the switch FET  $C_{MILLER}$ .

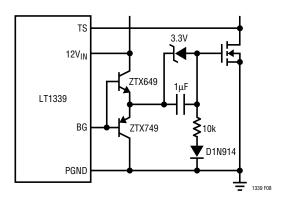

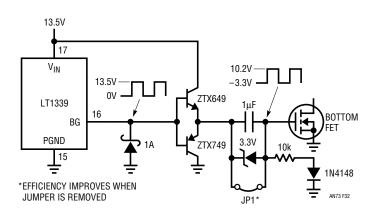

#### Paying the Physicists

In high power synchronous buck configurations, certain physical characteristics of the external MOSFET switches can impact conversion efficiency. As the input voltage approaches about 30V, the bottom MOSFETs will begin to exhibit "phantom turn-on." This phenomenon is caused by coupling of the instantaneous voltage step on the bottom side switch drain through  $C_{\rm MILLER}$  to the device gate, yielding internal localized gate-source voltages above the turn-on threshold of the FET. This generates a shoot-through blip that ultimately eats away at efficiency numbers. In Figure 8 a negative prebias circuit is added to the bottom side gate. The addition of this ~3V of negative offset to the bottom gate drive provides additional off-state voltage range to prevent phantom turn-on.

This type of prebias circuit is used in the 48V to 5V, 50A converter pictured in the Typical Applications section.

As currents increase beyond the 10A to 15A range, the bottom side FET body diode experiences hard turn-on during switch dead time due to local current loop inductance preventing the timely transfer of charge to the Schottky catch diode. The charge current required to commutate this body diode creates a high dV/dt Schottky avalanche when the diode charge is finally exhausted (due to an effective inductor current discontinuity at the moment the body diode no longer requires charge). This generates an increased turn-on power burst in the topside switch, causing additional conversion efficiency loss. This effect of this parasitic inductance can be reduced by using  $FETKEY^{TM}$  MOSFETs, which have parallel catch Schottky

Figure 8. Bottom Side Driver Negative Prebias Circuit

not available for high voltages, so as input voltage continues to increase, they can no longer be used. Because this necessitates the use of discrete FETs and Schottkys, interdigitation of a number of smaller devices is required to minimize parasitic inductances. This technique is also used in the 48V to 5V, 50A converter shown in the Typical Applications section.

#### Optimizing Transient Response—Compensation Component Values

The dominant compensation point for an LT1339 converter is the V<sub>C</sub> pin (Pin 7), or error amplifier output. This pin is connected to a series RC network,  $R_{VC}$  and  $C_{VC}$ . The infinite permutations of input/output filtering, capacitor ESR, input voltage, load current, etc. make for an empirical method of optimizing loop response for a specific set of conditions.

Loop response can be observed by injecting a step change in load current. This can be achieved by using a switchable load. With the load switching, the transient response of the output voltage can be observed with an oscilloscope. Iterating through RC combinations will yield optimized response. Refer to LTC Application Note 19 in *1990 Linear Applications Handbook, Volume 1* for more information.

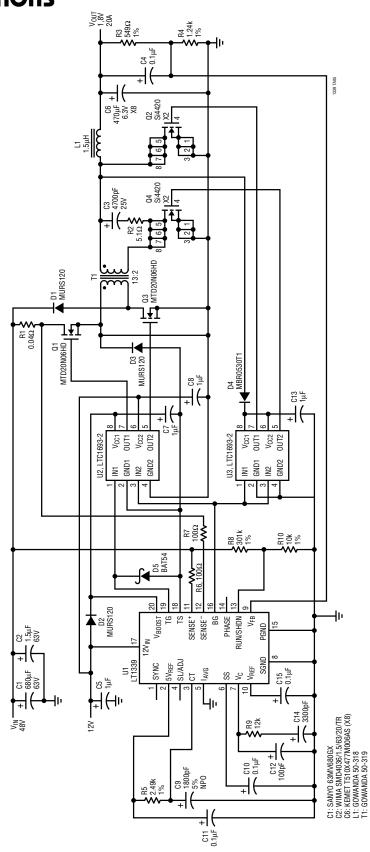

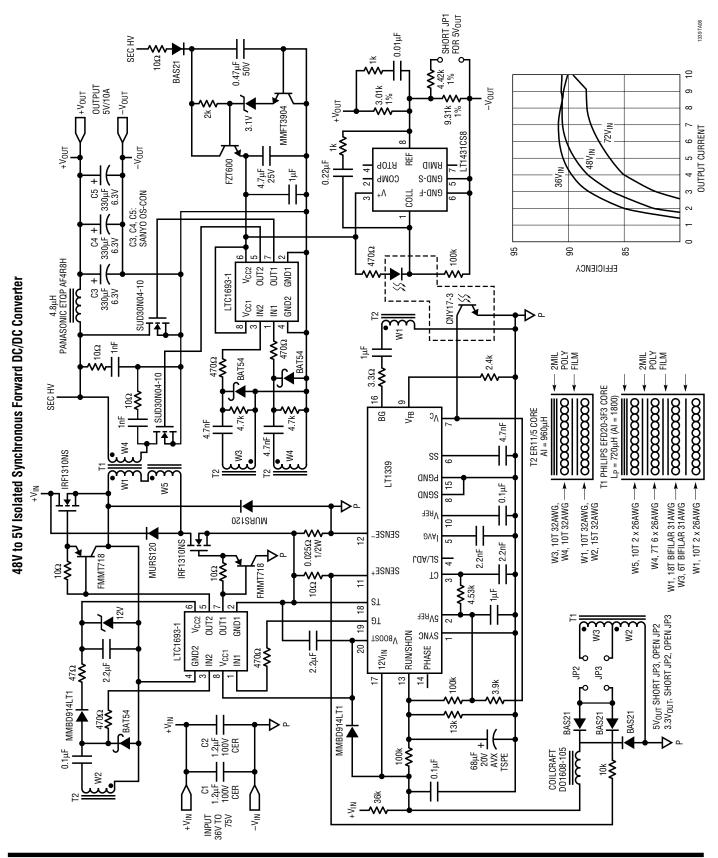

### TYPICAL APPLICATIONS

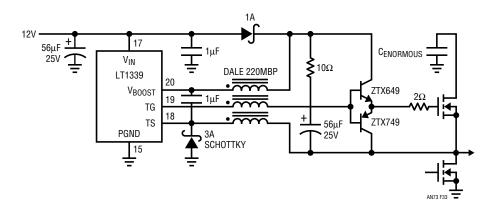

48V to 1.8V 2-Transistor Synchronous Forward Converter

**TECHNOLOGY**

AN73-22

### TYPICAL APPLICATIONS

### TYPICAL APPLICATIONS

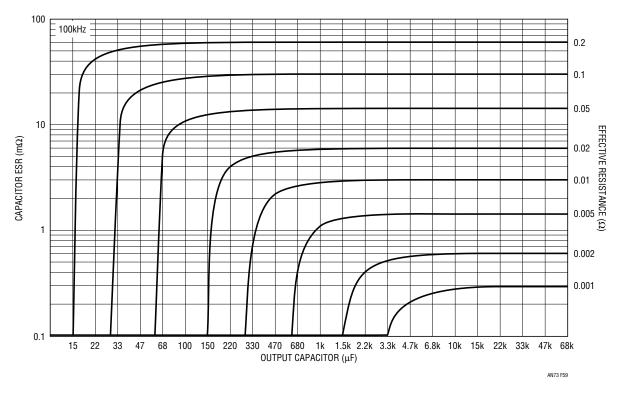

5V to 28V DC/DC Synchronous Boost Converter Limits Input Current at 60A (DC)

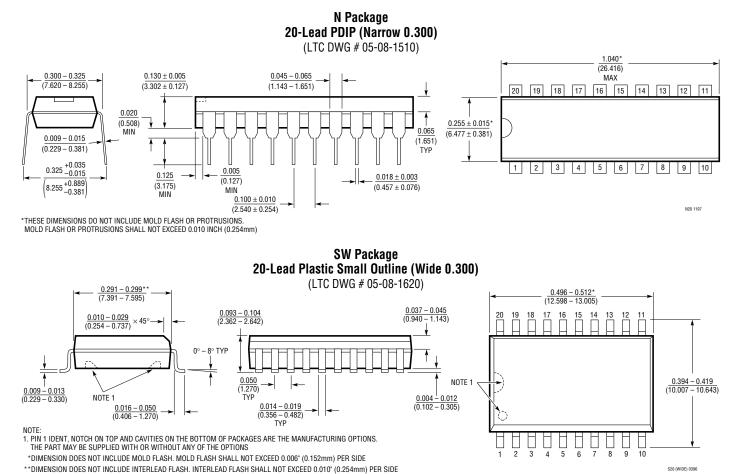

PACKAGE DESCRIPTION

Dimensions in inches (millimeters) unless otherwise noted.

AN73-24

### TYPICAL APPLICATION

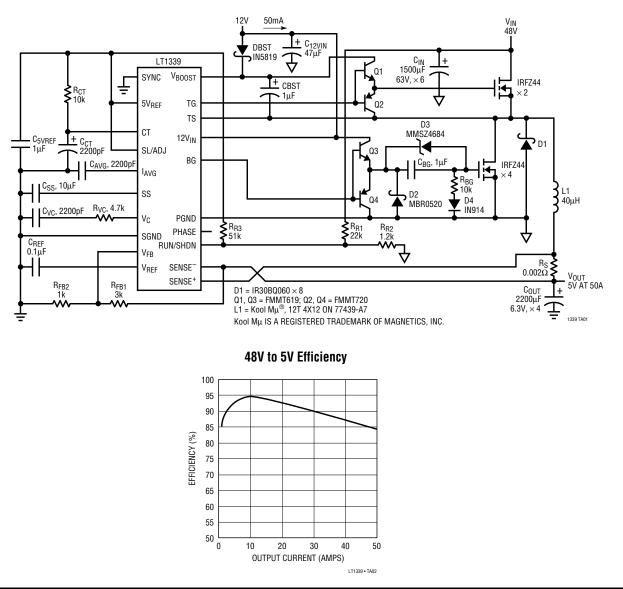

48V to 5V 50A DC/DC Converter with Input Supply Start-Up Protection

### **RELATED PARTS**

| PART NUMBER | DESCRIPTION                                                       | COMMENTS                                                  |

|-------------|-------------------------------------------------------------------|-----------------------------------------------------------|

| LT1158      | Half-Bridge N-Channel MOSFET Driver                               | Current Limit Protection, 100% of Duty Cycle              |

| LT1160      | Half-Bridge N-Channel MOSFET Driver                               | Up to 60V Input Supply, No Shoot-Through                  |

| LT1162      | Dual Half-Bridge N-Channel MOSFET Driver                          | V <sub>IN</sub> to 60V, Good for Full-Bridge Applications |

| LT1336      | Half-Bridge N-Channel MOSFET Driver                               | Smooth Operation at High Duty Cycle (95% to 100%)         |

| LTC®1530    | High Power Step-Down Switching Regulator Controller               | Excellent for 5V to 3.xV Up to 50A                        |

| LTC1435A    | High Efficiency, Low Noise Current Mode Step-Down DC/DC Converter | Drives Synchronous N-Channel MOSFETs                      |

| LTC1438     | Dual High Efficiency, Low Noise Synchronous Step-Down Controller  | Tight 1% Reference                                        |

| LT1680      | High Power DC/DC Current Mode Step-Up Controller                  | High Side Current Sense, Up to 60V Input                  |

#### EXPANDED PIN DESCRIPTIONS

#### SYNC (PIN 1) OSCILLATOR SYNCHRONIZATION PIN

This pin allows the user to synchronize the LT1339 to an external clock.

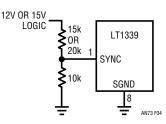

The synchronized frequency must be faster than the freerunning frequency of the LT1339. This logic-level input can be driven from TTL or 3.3V or 5V CMOS. Its threshold is set at  $2.2V_{BE}$ , about 1.5V, and it exhibits no hysteresis. Its duty factor can be almost anything, but you must ensure that the pulse is at least 500ns wide, whether asserted high or low. The internal synchronization event is triggered on the rising edge of the SYNC pulse; this event triggers an internal 200ns one-shot. While the output of the internal one-shot is asserted, the high level trip point of the CT pin is reduced from 2.5V to 2V (see Figure 3).

Figure 3. Free Run and Synchronized Oscillator Waveforms (at Pin CT)

If, during the 200ns at the output of the internal one-shot, the ramp voltage on the CT pin is above 2V, an early reset is initiated. Normal reset is initiated at 2.5V. The functions performed by the reset event are:

- 1. The CT pin (Pin 3) is discharged by the LT1339 to 0.8 V

- 2. The beginning of a new on cycle ensues (the top gate goes high in buck mode or the bottom gate goes high in boost mode, depending on the logic level of the PHASE pin).

The SYNC pin is used to pull the oscillator frequency up from the free-running frequency set by  $R_{CT}$  and  $C_{CT}$ , so the free-running frequency should be set low enough (20% lower than the desired running frequency) to ensure synchronization. If unused, this pin should be tied either to SGND or to  $5V_{REF}$ , the latter having a penalty of an additional 1mA of quiescent operating current. Leaving this pin floating is bad form. If this pin is to be driven from

12V or 15V logic, a resistor divider is recommended, as shown in Figure 4.

Figure 4. Synchronizing from Higher Voltage Logic Families

Pulling the SYNC pin above  $5V_{REF}$  by a diode drop forward biases an internal diode which begins to source current into  $5V_{REF}$ , which has no provision to sink current. This is not recommended.

#### SYNCHRONIZING MULTIPLE LT1339s

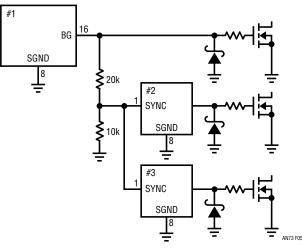

There are two basic schemes to synchronize multiple power converters: master/slave synchronization and multiphase synchronization.

#### Master/Slave Synchronization

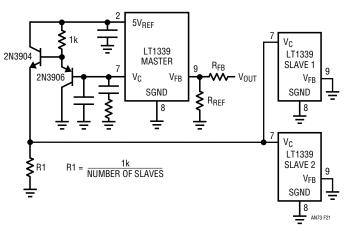

In master/slave synchronization, one LT1339 (the master) is set to free-run at the frequency desired for the whole system and the other LT1339(s) are slaved from the master. Figure 5 details the master/slave connection. The free-running frequencies of the slaves are set 20% lower than the free-running frequency of the master. In such a system, if the master LT1339 stops switching (shuts down) the slaves free-run at their natural frequency until the master resumes switching.

Figure 5. Master/Slave Synchronization

## Application Note 73

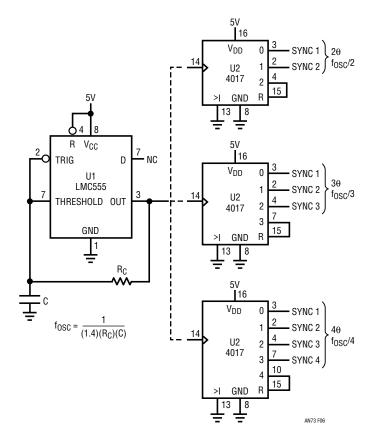

#### Multiphase Synchronization

Multiphase synchronization is very useful in systems where high ripple current mandates massive input capacitors in a buck or forward regulator, or massive output capacitors in a boost regulator. Refer to Figure 6. The master oscillator (U1) is set to run at *n* times the desired running frequency, where *n* is the number of phases desired. Select the subcircuit of U2 that matches the number of phases you desire (or make more phases by looking up the 4017 data sheet and choosing additional [up to ten] phases). Simply connect the sync outputs of Figure 6 to the SYNC pins of the respective LT1339s. Set up the LT1339s to free-run 20% slower than the synchronizing frequency,  $f_{OSC}/n$ .

Figure 6. Mulitphase Synchronization

#### Wide-Range Synchronization

The LT1339 oscillator can be synchronized over a wider frequency range by acting directly on the CT pin. This can

be done by pulling the CT pin above 2.5V; this sets an internal flip-flop, which, while set, keeps the LT1339 in the deadtime phase of operation. The deadtime phase is maintained until the CT pin is brought down to 0.8V. During the dead-time phase, the LT1339 enters and remains in the following state:

- 1. The main transistor (top FET of buck, bottom FET of boost) is off.

- 2. The synchronous transistor (bottom FET of buck, top FET of boost) is on.

- 3. A 2.5mA current source is discharging the CT pin.

The LT1339 will stay in this state as long as the CT pin is held above 0.8V.

When the CT pin is released, the internal discharge current (2.5mA) will pull it down to 0.8V, the internal flip-flop is reset and the next on cycle begins:

- 1. The synchronous transistor is turned off

- 2. The main transistor is turned on.

- 3. The 2.5mA discharge current is switched off.

Refer to Figure 7. This synchronization scheme has the advantage of allowing synchronization over the full operating range of the LT1339, but has the disadvantage of disabling the slope compensation. Due to the internal structures of the LT1339, the CT pin should not be pulled above 3.5V; doing so may seriously confuse the internal logic.

Figure 7. Wide-Range Synchronization Using the CT Pin

#### 5V<sub>REF</sub> (PIN 2) OUTPUT REFERENCE

This is *your* reference, the reference to power your external logic, amplifiers and the supply to tailor the inputs of the LT1339 to your needs—it is  $5V \pm 250mV$  over line, load and temperature. You can draw up to 10mA

from this pin. Sourcing current into this pin is not recommended because it has no pull-down capability other than the normal operating current of the logic of the LT1339. It is used as the reference for the oscillator section through  $R_T$ . To set up hysteresis for the RUN pin, connect an appropriate resistor from the RUN pin to the 5V<sub>REF</sub> pin. Finally, the 5V<sub>REF</sub> pin is used with the SL/ADJ pin to set the maximum duty factor or additional slope compensation when needed. Internally, the 5V<sub>REF</sub> pin is used to power practically all internal functions, with only the RUN/SHDN comparator and both gate drive circuits powered from other sources. This pin should be decoupled to ground (SGND) with a 1µF capacitor having an ESR less than 10 $\Omega$ . The decoupling capacitor can be anything from 0.1µF to many thousands of microfarads.

#### CT (PIN 3) OSCILLATOR TIMING PIN

The free-running (nonsynchronized) frequency of the LT1339 is set up by the R<sub>CT</sub> and C<sub>CT</sub> combination connected to this pin (see Figure 8). The value of the resistor R<sub>CT</sub> sets up the minimum off-time of the LT1339. Refer to Figure 9 for duty factor verses R<sub>CT</sub> in k $\Omega$ . If you would like

Figure 8. Oscillator Pin Connection + Waveform

Figure 9. Duty Factor vs R<sub>CT</sub>

to limit maximum duty factor to a number less than 90%, a better way to do so is described in the SL/ADJ (Pin 4) pin description.

Figure 10 shows the Oscillator Frequency vs  $R_{CT}$  and  $C_{CT}.$

Figure 10. Oscillator Frequency vs  $R_{CT}$ ,  $C_{CT}$

## SL/ADJ (PIN 4) SLOPE COMPENSATION ADJUSTMENT PIN

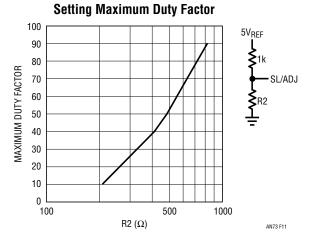

This pin is used to limit maximum duty factor and/or introduce additional slope compensation to the LT1339.

#### Limiting Maximum Duty Factor

Figure 11 details how to use the SL/ADJ pin to limit maximum duty factor. Limiting the maximum duty factor effectively limits the voltage input-to-output ratio where the converter can transform power. If you think of the converter as a DC variac, limiting the duty factor limits how far the variac can be turned. What function limiting duty factor performs depends upon the topology used:

- 1. In a synchronous buck converter, decreasing the maximum duty factor increases the dropout voltage. This could be used to set the minimum input voltage at which a given output voltage can be reached. It also limits the load-step response time when at the lowest input voltage.

- 2. In a synchronous boost converter, decreasing the maximum duty factor decreases the maximum available output voltage at a given input voltage. This could be used as an overvoltage protection default. Limiting duty factor can also affect the load step response time when operating at the minimum input voltage.

- 3. In a forward converter, decreasing the maximum duty factor is highly desirable because it prevents transformer core saturation, resulting in a robust design.

- 4. In all topologies, limiting the maximum duty factor can be used to prevent operation at duty factors at which the circuit would experience current mode instability, but this function is better performed by setting the UV lockout voltage appropriately.

Figure 11. Using the Slope Comp Pin to Limit Duty Factor

#### Adding More Slope Compensation

At duty factors greater than 50%, an instability enters the current mode switcher world: current mode instability. This is seen as a two-cycle sequence: first, a cycle with a long on-time and short off-time, then a cycle with a short on-time and a long off-time. Current mode instability *always* happens at exactly half of the switching frequency and is completely independent of other forms of subharmonic oscillation. Current mode instability is independent of the control loop and can be observed when a voltage source is substituted for the control loop. Current mode instability occurs whenever the rising main inductor current ramp is slower than the falling main inductor current ramp. To make a design that can run at duty factors approaching unity, slope compensation is a must. The LT1339 has built-in slope compensation that is adequate for most buck converter designs, but if you have a boost converter running at very high duty factors, you may need more slope compensation.

If your system exhibits current mode instability, you will need to add slope compensation or increase the inductance of the main inductor. For the procedure to calculate the correct value for the main inductor, refer to the section entitled "Boost," or "Buck", according to which topology you have, and look up the "Inductor Selection" subsection. To add slope compensation to your existing design, use this procedure:

- 1. By varying  $V_{IN}$ , measure the minimum duty factor at which current mode instability occurs. If the duty factor is 50% or less, you are not looking at current mode instability; check loop stability.

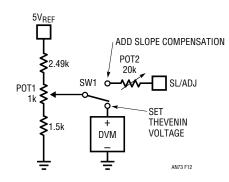

- 2. Construct the subcircuit shown in Figure 12 and connect it to your switcher.

Figure 12. Slope Compensation Adjustment Setup Circuit

- 3. Power up and switch SW1 to the "set Thevenin voltage" position.

- 4. Select a Thevenin voltage from Table 1 that corresponds to a duty factor that is 10% less than you found in step 1.

| DF  | V <sub>THEVININ</sub> |  |  |  |

|-----|-----------------------|--|--|--|

| 90% | 2.37                  |  |  |  |

| 80% | 2.23                  |  |  |  |

| 70% | 2.09                  |  |  |  |

| 60% | 1.922                 |  |  |  |

| 50% | 1.744                 |  |  |  |

Table 1. Thevinin Voltages for Slope Compensation

- 5. Adjust POT1 for that Thevenin voltage, as read on the DVM.

- 6. Adjust POT2 for maximum resistance and set SW1 for "Add slope compensation."

- 7. Decrease the resistance of POT2 to correct the current mode instability at the minimum input voltage and maximum load current allowed.

- 8. Calculate from the equations in Figure 13 the resistor values needed to construct the slope-compensation network shown in Figure 14.

$$R_{THEV} = \frac{1}{\left[\frac{1}{(V_{THEV} / 5V)(4k)}\right] + \left[\frac{1}{(5V - V_{THEV}) / (5V)(4k)}\right]}$$

$$R_{SELECT} = (R_{POT2})(0.8)$$

(Margin)

$R_{TOTAL} = R_{THEV} + R_{SELECT}$

$\mathsf{R}_{\mathsf{TOP}} = \frac{(\mathsf{R}_{\mathsf{TOTAL}})(5)}{\mathsf{V}_{\mathsf{THEV}}}$

$R_{BOTTOM} = \frac{(R_{TOTAL})(5)}{5 - V_{THEV}}$

Figure 13. Calculating the Resistor Values for a 2-Resistor Slope Compensation Network

Figure 14. Two Resistor Slope Compensation

For the new design, refer to the "Inductor Selection" subsection of the section describing the topology you are designing.

The slope compensation in your system need only be enough to handle the steady-state operation at minimum  $V_{IN}$  with maximum  $V_{OUT}$  and maximum load current (UV lockout can be set to limit minimum input voltage and  $I_{RSENSE}$  can be set to limit maximum current). If the

converter is stable in steady-state operation, it will also be free from current mode instability during load-stepinduced duty factor variations.

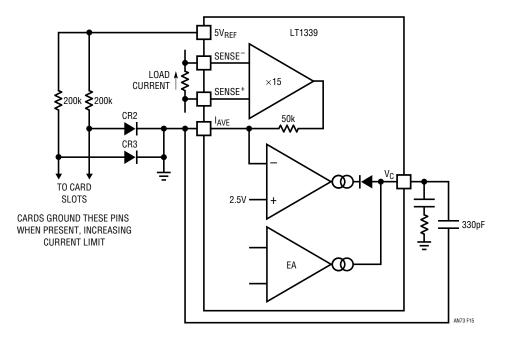

# I<sub>AVE</sub> (PIN 5) AVERAGE CURRENT LOOP INTEGRATION CAPACITOR

This pin is used to smooth out the triangular wave shape of the current waveform and, in the process, to set up the loop compensation of the current limit loop. In the buck or boost converter, the current waveform in the inductor of the power converter is roughly triangular, the average of which represents the DC output current of the buck converter (DC input current for a boost converter). This main inductor current is converted into a voltage by the current sense resistor. The voltage across the sense resistor is applied to the SENSE<sup>-</sup> and SENSE<sup>+</sup> pins of the LT1339. Inside, it is amplified by a gain of 15 and is then offset by a  $V_{BE}$  so that 700mV represents zero programmed peak inductor current. This current signal representing inductor current is then given an impedance of 50k and brought out to the IAVE pin. Placing a capacitor from the  $I_{AVE}$  pin to the V<sub>C</sub> pin (Pin 7), sets up an integration network that smooths out the triangular ripple, yielding a DC voltage that represents the average current. This DC voltage is subtracted from 2.5V and converted to a current by a transconductance amplifier. If the resultant current is negative, it is subtracted from the error amplifier's output current. The transconductance of the conversion is 0.03A/V. Once the current reaches its threshold, the average current limit loop comes to life, taking control of the main control loop. The power converter changes from a constant voltage source to a constant current source. If the average current limit feature is not used, this pin should be grounded.

## Using the I<sub>AVE</sub> Pin to Implement an Adjustable Current Limit.

Refer to Figure 15. This circuit is a system-level application using the LT1339 where there is a motherboard that uses one-half of the available power and two daughter boards that, when present, each use one-quarter of the total available power. Using this circuit, one can protect the motherboard and daughterboards with current limits set appropriately for the actual load.

Figure 15. Multiple Level Automatic Current Limit

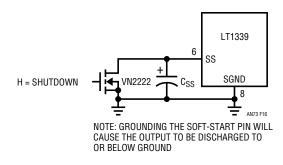

#### **SS (PIN 6) SOFT-START INTEGRATION CAPACITOR**

This pin, with its associated external capacitor, generates a ramp that limits the maximum voltage possible on the  $V_{C}$ pin. The V<sub>C</sub> pin is clamped by a PNP transistor to be  $1V_{BE}$ (~0.7V) maximum above the SS pin. This allows the current output of the power converter to start at zero and rise to the operating load current at a rate slower than the loop response. Soft-start ramps minimize or completely eliminate overshoot at turn-on. This pin is actively pulled to ground when either the 12V<sub>IN</sub> pin voltage drops below the UV lockout point, disabling operation (see the section on the 12V<sub>IN</sub> pin for details), or the RUN/SHDN pin is below its low voltage trip point (see the section on the RUN/ SHDN pin for details). When the voltages on both the 12V<sub>IN</sub> and the RUN/SHDN pins enable operation, approximately  $8\mu$ A is sourced out of this pin, charging C<sub>SS</sub>, the capacitor connected between ground and this pin. This current can vary from 4µA to 20µA. For tighter chargecurrent tolerance, an external resistor is recommended between the 5V<sub>RFF</sub> pin and the SS pin, setting up a much higher (100µA) charge current. The voltage on this pin is internally clamped at 3.5V and any resistor pulling up on this pin should be sized to limit the current to 150µA.

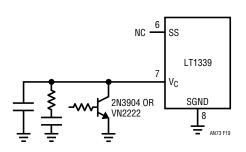

When the LT1339 pulls this pin low, the discharge current is 10mA. This discharge current becomes available whenever the voltage at the  $12V_{IN}$  pin is greater than 3V. When the soft-start pin is fully discharged by the internal discharge transistor, the peak current programmed is zero. Grounding the SS pin will stop the top FET drive from turning on. The bottom FET drive will be on for the maximum time as set up by the running frequency and dead-time. Using the internal charge current, the time to full current is nominally Time (s) =  $0.8 \cdot 10^5$ C. If this pin is unused, it should be left floating. If your design requires that the V<sub>REF5</sub> output be active while the LT1339 output is shut down, use the circuit detailed in Figure 16.

Figure 16. Shutdown While Keeping 5V<sub>REF</sub> Circuit Alive

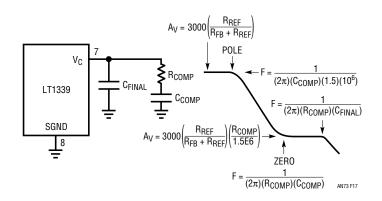

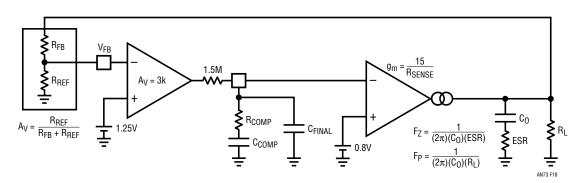

#### V<sub>C</sub> (PIN 7) CONTROL LOOP COMPENSATION NODE

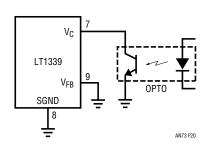

This pin comprises the output of the error amplifier and the input of the peak current comparator. Normally it is used to compensate the output voltage control loop. Compensation is performed by adding a pole and a zero to the control loop function; sometimes an additional pole is needed—this is provided by CFINAL. These two poles and one zero are configured by connecting this pin in the manner indicated in Figure 17. The total voltage loop is detailed in Figure 18. If your design requires gating on and off, use the RUN/SHDN pin as your first choice. If, however, you need to keep 5V<sub>BFF</sub> alive during the shutdown period, the V<sub>C</sub> pin can be pulled down by an NPN transistor or MOSFET, as shown in Figure 19. This allows the softstart function to work independently of the gating signal. If soft-start is desired on each turn-on of your gating sequence, refer to Figure 16 in the soft-start pin description. When using optoelectronic feedback in a forward converter, ground the feedback pin and connect the optoisolator to the  $V_{C}$  pin according to Figure 20.

Figure 17. Control Loop Compensation

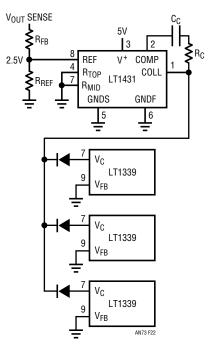

#### **Current Sharing Multiple Power Converters**

As with the synchronization of multiple LT1339 power converters, current sharing can be achieved by two different strategies: master/slave current sharing and peer-level sharing controlled by a system master control loop.

- 1. Master/slave current sharing is performed by the circuit detailed in Figure 21.

- 2. Operating peer-level power converters with a master system loop is detailed in Figure 22.

Figure 19. Gating the Power Converter On and Off Without Soft Start

Figure 20. Optical Feedback Scheme

Figure 18. Total Voltage Loop

Figure 21. Master/Slave Current Sharing

Figure 22. Peer Level Current Sharing

#### SGND (PIN 8) SIGNAL GROUND

This is the "clean" ground pin; it is for the returns of  $C_{CT}$ , the feedback resistor divider,  $C_{COMP}$ ,  $C_{5VREF}$ ,  $C_{IAVE}$ ,  $C_{VREF}$  and  $C_{SOFTSTART}$ . This pin also is the reference for the RUN/SHDN pin. This pin is electrically connected to the PGND inside the LT1339; the resistance between these pins is approximately  $10\Omega$ . On the PCB there should be a trace connecting this pin to the PGND pin. This connecting trace should be situated so that no switching frequency AC or power level DC current flows through it. Placing the LT1339 on a ground plane with PGND and SGND connected to the plane works well.

#### V<sub>FB</sub> (PIN 9) FEEDBACK PIN FOR OUTPUT VOLTAGE CONTROL

This pin is the inverting input to the error amplifier. The input voltage at the V<sub>FB</sub> pin is subtracted from the voltage on the V<sub>REF</sub> pin and converted into an error current by the error amplifier's transconductance of 0.002A/V. The LT1339, using its loop gain and current-controlled engine, is constantly forcing this pin to 1.250V. Thus, the output voltage is set by a resistor divider (See Figure 23) connected to this pin.

Figure 23. Programming LT1339's Output Voltage

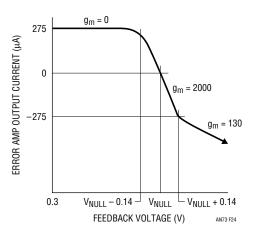

#### **Error Amplifier Characteristics**