PUBLICATION NUMBER: 10215-0022B

**JULY 1989**

**RECOMMUNICATIONS**

# R-2368 / URR RADIO RECEIVER

# INSTRUCTION MANUAL

PUBLICATION NUMBER: 10215-0022B JULY 1989

# R-2368/URR RADIO RECEIVER

# INSTRUCTION MANUAL

Copyright © 1989 By Harris Corporation All Rights Reserved

Equipment manufactured by Harris Corporation, RF Communications Group meets stringent quality and safety standards. However, high voltages are present in many radio products, and only a skilled technician should attempt to remove outer covers and make adjustments or repairs. All personnel who operate and maintain the equipment should be familiar with this page as a safety preparedness measure. Although this procedure is reproduced as a service to the personnel involved with this equipment, Harris Corporation assumes no liability regarding any injuries incurred during the operation and repair of such equipment, or the administration of this suggested procedure.

#### **ELECTRICAL SHOCK: EMERGENCY PROCEDURE**

The victim will appear unconscious and may not be breathing. If the victim is still in contact with the voltage source, disconnect the power source in a manner safe to you, or remove the victim from the source with an insulated aid (wooden pole or rope). Next, determine if the victim is breathing and has a pulse. If there is a pulse but no breathing, administer artificial respiration. If there is no pulse and no breathing, perform CPR (if you have been trained to do so). If you have not been trained to perform CPR, administer artificial respiration anyway. Never give fluids to an unconscious person.

## WHEN BREATHING STOPS

**FIRST**, send someone to get a **DOCTOR**. **THEN**, administer first aid to restore breathing (artificial respiration):

IF A VICTIM APPEARS TO BE UNCONSCIOUS

TAP VICTIM ON THE SHOULDER AND SHOUT,

"ARE YOU OKAY?"

### IF THERE IS NO RESPONSE

TILT THE VICTIM'S HEAD, CHIN POINTING UP. Place one hand under the victim's neck and gently lift. At the same time, push with the other hand on the victim's forehead. This will move the tongue away from the back of the throat to open the airway.

IMMEDIATELY LOOK, LISTEN, AND FEEL FOR AIR.

While maintaining the backward head tilt position, place your cheek and ear close to the victim's mouth and nose. Look for the chest to rise and fall while you listen and feel for the return of air. Check for about five seconds.

## IF THE VICTIM IS NOT BREATHING

GIVE FOUR QUICK BREATHS.

Maintain the backward head tilt, pinch the victim's nose with the hand that is on the victim's forehead to prevent leakage of air, open your mouth wide, take a deep breath, seal your mouth around the victim's mouth, and blow into the victim's mouth with four quick but full breaths just as fast as you can. When blowing, use only enough time between breaths to lift your head slightly for better inhalation.

If you do not get an air exchange when you blow, it may help to reposition the head and try again.

AGAIN, LOOK, LISTEN, AND FEEL FOR AIR EXCHANGE.

CHANGE RATE TO ONE BREATH EVERY FIVE SECONDS.

For more information about these and other life-saving techniques, contact your Red Cross chapter for training "When Breathing Stops" reproduced with permission from an American Red Cross Poster

#### **TABLE OF CONTENTS**

| Paragraph |                                           |       |   |   |   |   |   |   |   |   |   |   |   | Page |

|-----------|-------------------------------------------|-------|---|---|---|---|---|---|---|---|---|---|---|------|

|           | Specifications                            |       |   |   |   |   |   |   |   |   |   |   |   | viii |

|           | About This Manual .                       | •     | ٠ | • | • | • | • | ٠ | • | • | • | • | • | xi   |

|           | SECTION 1 - INTRODUCT                     | ION   |   |   |   |   |   |   |   |   |   |   |   |      |

| 1.1       | Introduction                              |       |   |   |   |   |   |   |   |   |   |   |   | 1-1  |

| 1.2       | General Description .                     |       |   |   |   |   |   |   |   |   |   |   |   | 1-1  |

| 1.3       | Receiver Features .                       |       |   |   |   |   |   |   |   |   |   |   |   | 1-3  |

| 1.4       | Compatibility                             |       |   |   |   |   |   |   |   |   |   |   |   | 1-3  |

| 1.5       | Customer Options                          |       | - |   | - |   |   |   |   |   |   |   | - | 1-4  |

| 1.6       | Specialized Requiremen                    | ts .  |   |   |   |   |   |   |   |   |   |   | • | 1-5  |

|           | SECTION 2 - INSTALLATI                    | ON    |   |   |   |   |   |   |   |   |   |   |   |      |

| 2.1       | Introduction                              |       |   |   |   |   |   |   |   |   |   |   |   | 2-1  |

| 2.2       | Unpacking and Inspection                  |       |   |   |   |   |   |   |   |   |   |   |   | 2-1  |

| 2.3       | Ancillary Kit                             |       |   |   |   |   |   |   |   |   |   |   |   | 2-1  |

| 2.4       | Site Selection                            |       |   |   |   |   |   |   |   |   |   |   |   | 2-1  |

| 2.4.1     | Antennas                                  |       |   |   |   |   |   |   |   | • | • | • | • | 2-2  |

| 2.5       | Mechanical Installation                   |       |   |   |   |   |   |   |   | • | • | • | • | 2-2  |

| 2.6       | Power Requirements .                      |       |   |   |   |   |   |   |   | • | • | • | • | 2-2  |

| 2.7       | Input/Output Connectio                    |       |   |   |   |   |   |   |   | • | • | • | • | 2-2  |

| 2.8       | Initial Setup and Adjustr                 |       |   |   |   |   |   |   |   | • | • | • | • | 2-4  |

| 2.8.1     | Memory Backup Battery                     |       |   |   |   |   |   |   |   |   |   |   |   | 2-4  |

| 2.8.2     | Remote Control Interfac                   |       |   |   |   |   |   |   |   |   |   |   |   | 2-8  |

| 2.8.3     | USB, LSB and ISB Line Au                  |       |   |   |   |   |   |   |   |   |   |   |   | 2-10 |

| 2.8.4     | Adjusting Front Panel Di                  |       |   |   |   |   |   |   |   |   |   |   |   | 2-10 |

| 2.9       | Functional Checkout Pro                   |       |   |   |   |   |   |   |   |   |   |   | • | 2-11 |

| 2.9.1     |                                           | ·ceuu |   |   |   |   |   |   |   |   |   |   | • | 2-11 |

| 2.9.1.1   | Frequency Entry                           |       |   |   |   |   |   |   |   |   |   |   |   | 2-11 |

| 2.9.1.2   |                                           |       |   |   |   |   |   |   |   |   |   |   |   | 2-11 |

| 2.9.1.3   | Mode Selection                            | •     | • | • | • | • | • | • | • | • | • | • | • | 2-12 |

| 2.9.1.4   | Bandwidth Selection .                     | •     | • | • |   | • | • | • | • | • | • | • | • | 2-12 |

| 2.9.1.5   | AGC Selection                             |       |   |   |   |   |   |   |   |   |   |   |   | 2-12 |

| 2.9.1.6   | PEO Coloction                             |       |   |   |   |   |   |   |   |   |   |   |   | 2-12 |

| 2.9.1.7   | RF Gain                                   | •     | • | • | • | • | - | • | • | • | • | • | • |      |

| 2.9.1.8   | AF Gain                                   | •     | • | • | • | ٠ | • | • | • | • | • | • | • | 2-13 |

| 2.9.1.9   | Load Memory Function                      | •     | • | • | • | • | • | ٠ | • | • | • | ٠ |   | 2-13 |

| 2.9.1.10  | •                                         | •     | • | • | • | • | • | • | • | • | • | • | • | 2-13 |

|           | Channelized Reception Local/Remote Switch | •     | • | • | • | • | • | • | • | • | • | • | • | 2-14 |

| 2.9.1.11  |                                           | •     | • | • | • | - | • | ٠ | • | • | • | • | • | 2-14 |

| 2.9.1.12  | Meter Switch                              | •     | • | • | • | • | ٠ | • | • | ٠ | ٠ | • | • | 2-14 |

| 2.9.1.13  | COR Control                               | •     | • | • | • | • | • | • | • | • | ٠ |   | • | 2-15 |

| 2.9.2     | Program Mode                              |       | • | • | • | • | • |   |   | • | • | • | • | 2-15 |

| 2.9.2.1   | Recall Memory Function                    |       | • | • | • | • | • | ٠ | • |   | ٠ |   | • | 2-15 |

| 2.9.2.2   | Program Group Function                    |       |   |   |   |   |   |   | • | • |   |   |   | 2-15 |

| 2.9.3     |                                           |       |   |   |   |   | • |   |   |   |   |   |   | 2-15 |

| 2021      | Channel Scan                              |       |   |   |   |   |   |   |   |   |   |   |   | 2 16 |

### **TABLE OF CONTENTS (Cont.)**

| Paragraph |                                                                        | Page       |

|-----------|------------------------------------------------------------------------|------------|

|           | SECTION 2 - INSTALLATION (Cont.)                                       |            |

| 2.9.3.2   | Group Scan                                                             |            |

| 2.9.4     | Self-Test (BITE)                                                       |            |

| 2.9.5     | Reconnection                                                           | 2-16       |

|           | SECTION 3 - OPERATION                                                  |            |

| 3.1       | Introduction                                                           |            |

| 3.2       | Controls and Indicators                                                |            |

| 3.2.1     | Power, AF Gain, RF Gain, and COR                                       | 3-1        |

| 3.2.2     | Tuning Wheel and Keypad Entries for Channel, Frequency, BFO, and Group | 3-1        |

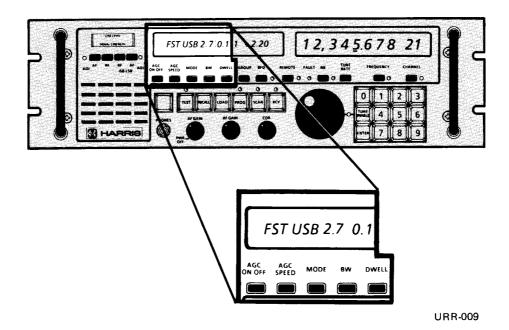

| 3.2.3     | AGC, Mode, BW, and Dwell                                               | 3-4        |

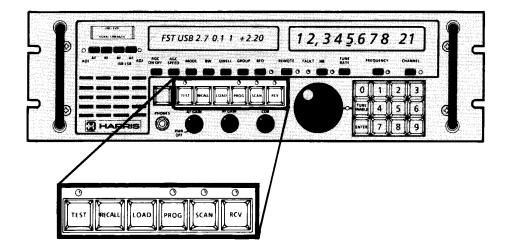

| 3.2.4     | TEST, RECALL, LOCAL, PROG, SCAN, and RCV Controls                      |            |

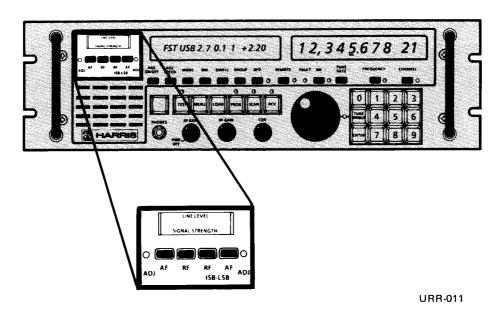

| 3.2.5     | Front Panel Meter                                                      |            |

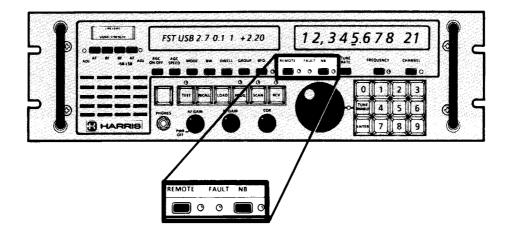

| 3.2.6     | Remote, Fault, and NB (Noise Blanker)                                  | 3-7<br>3-8 |

|           |                                                                        |            |

| 3.3       | Power Up                                                               | 3-9        |

| 3.4       | Receiver (Non-Channelized) Operation                                   |            |

| 3.4.1     | Operating Procedure                                                    | 3-9        |

| 3.5       | Programming the Receiver for Channelized Operation                     |            |

| 3.5.1     | Channel Programming Procedure                                          |            |

| 3.5.2     | Group Programming Procedure                                            |            |

| 3.5.3     | Entering Auxiliary Channel Procedure                                   |            |

| 3.6       | Programmed Receiver Operation                                          | 3-14       |

| 3.6.1     | Standard (Non-scanning) Channelized Operation                          | 3-14       |

| 3.6.2     | Automatic Scanning                                                     | 3-14       |

| 3.6.2.1   | Channel Scanning Procedure                                             |            |

| 3.6.2.2   | Group Scanning Setup Procedure                                         |            |

| 3.6.2.3   | Terminating the Scan Function                                          |            |

| 3.7       | Remote Operation                                                       |            |

|           | SECTION 4 - TECHNICAL DESCRIPTION                                      |            |

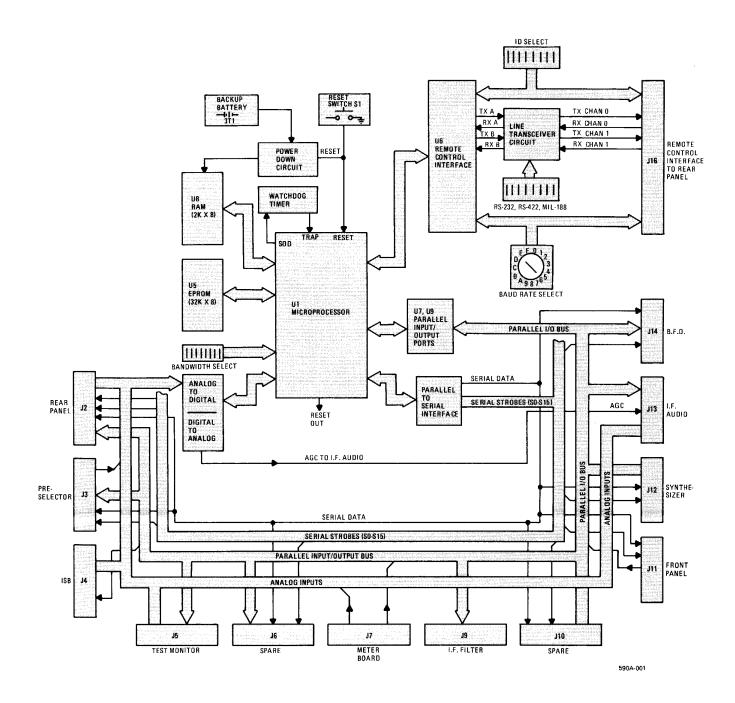

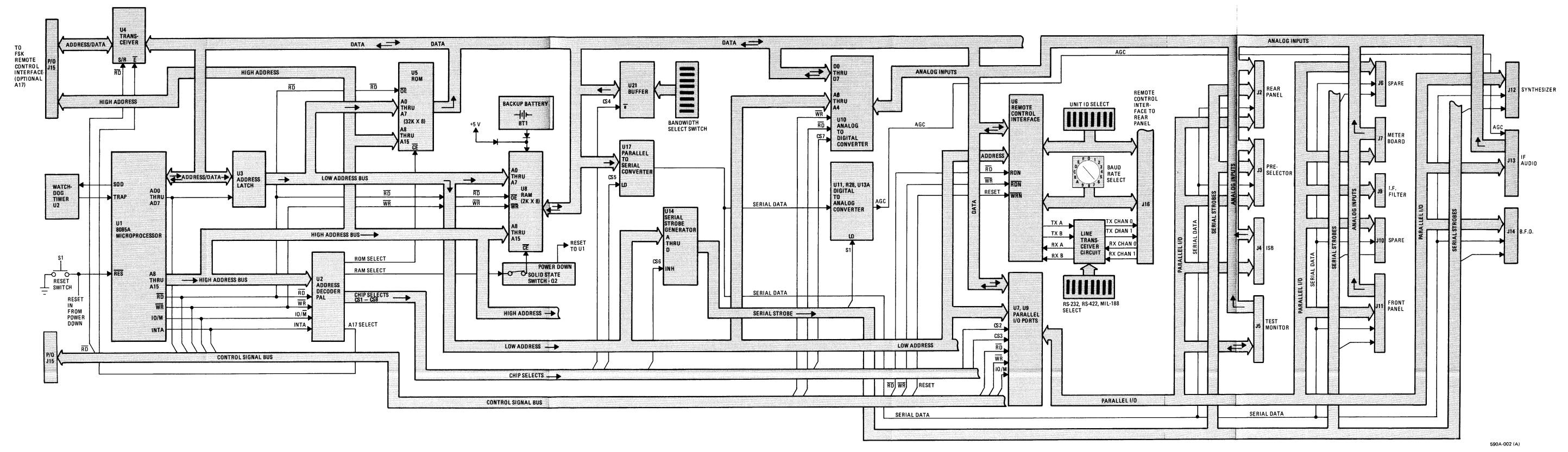

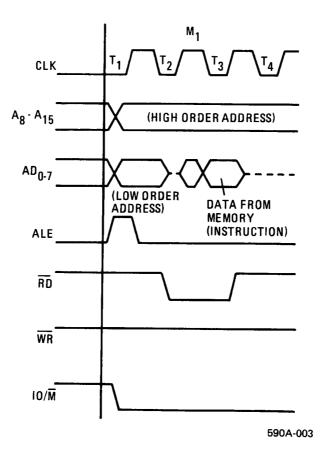

| 4.1       | Introduction                                                           | 4-1        |

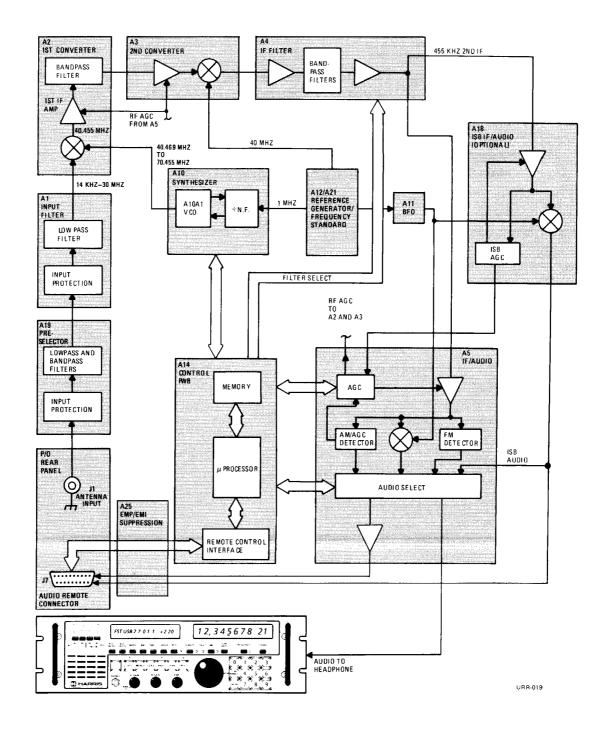

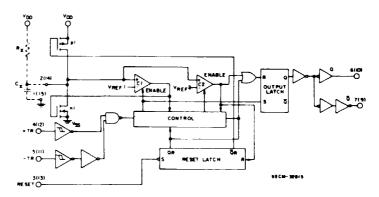

| 4.2       | Receiver Operation                                                     | 4-1        |

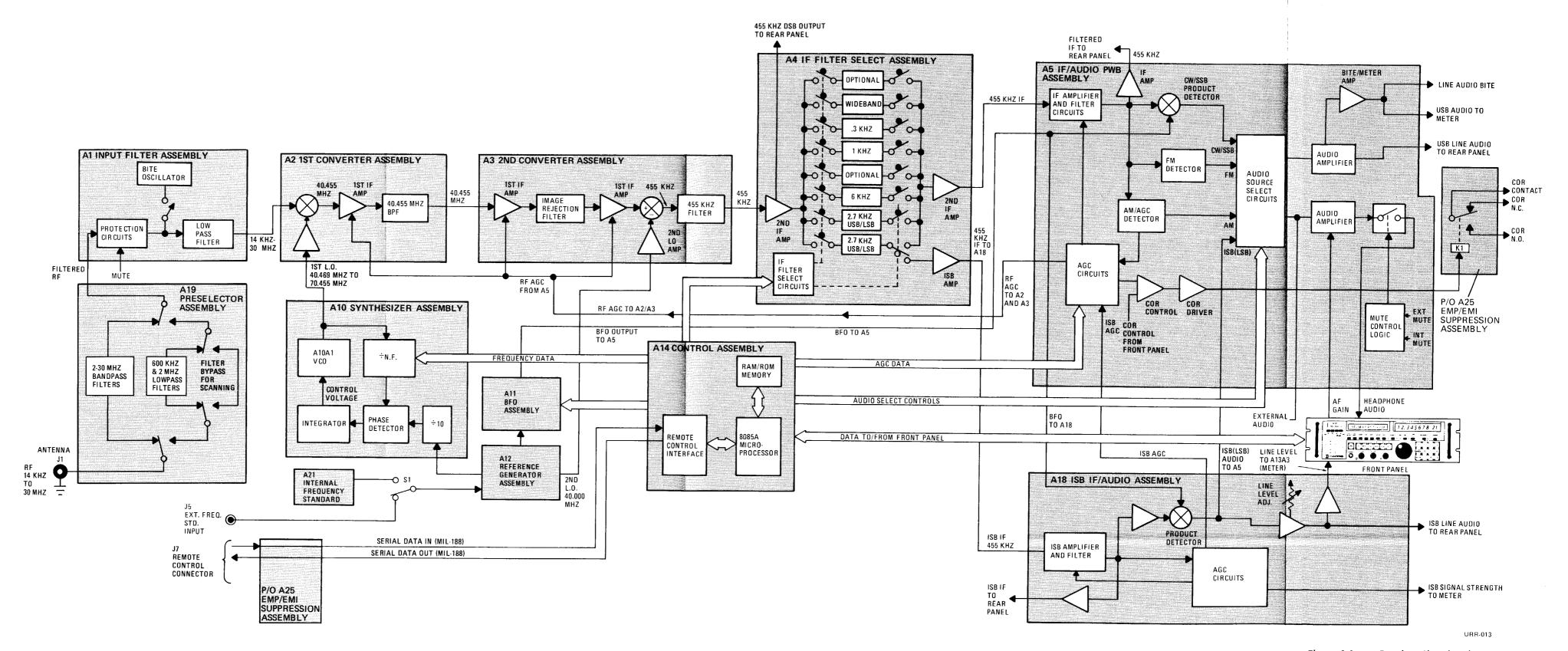

| 4.2.1     | Receiver Signal Path                                                   | 4-1        |

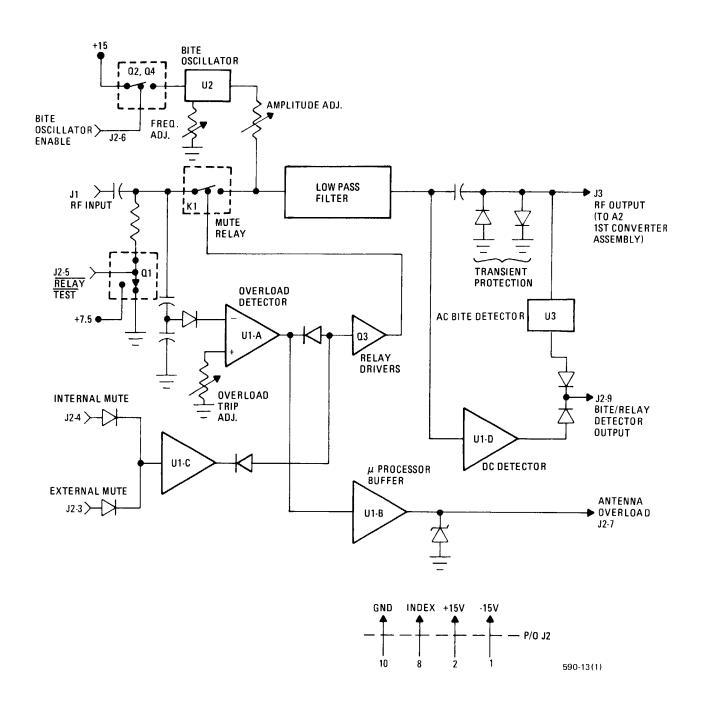

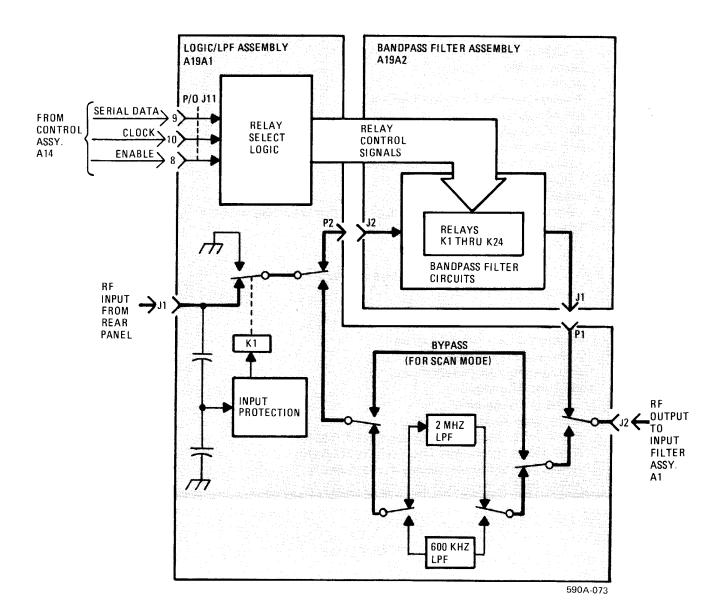

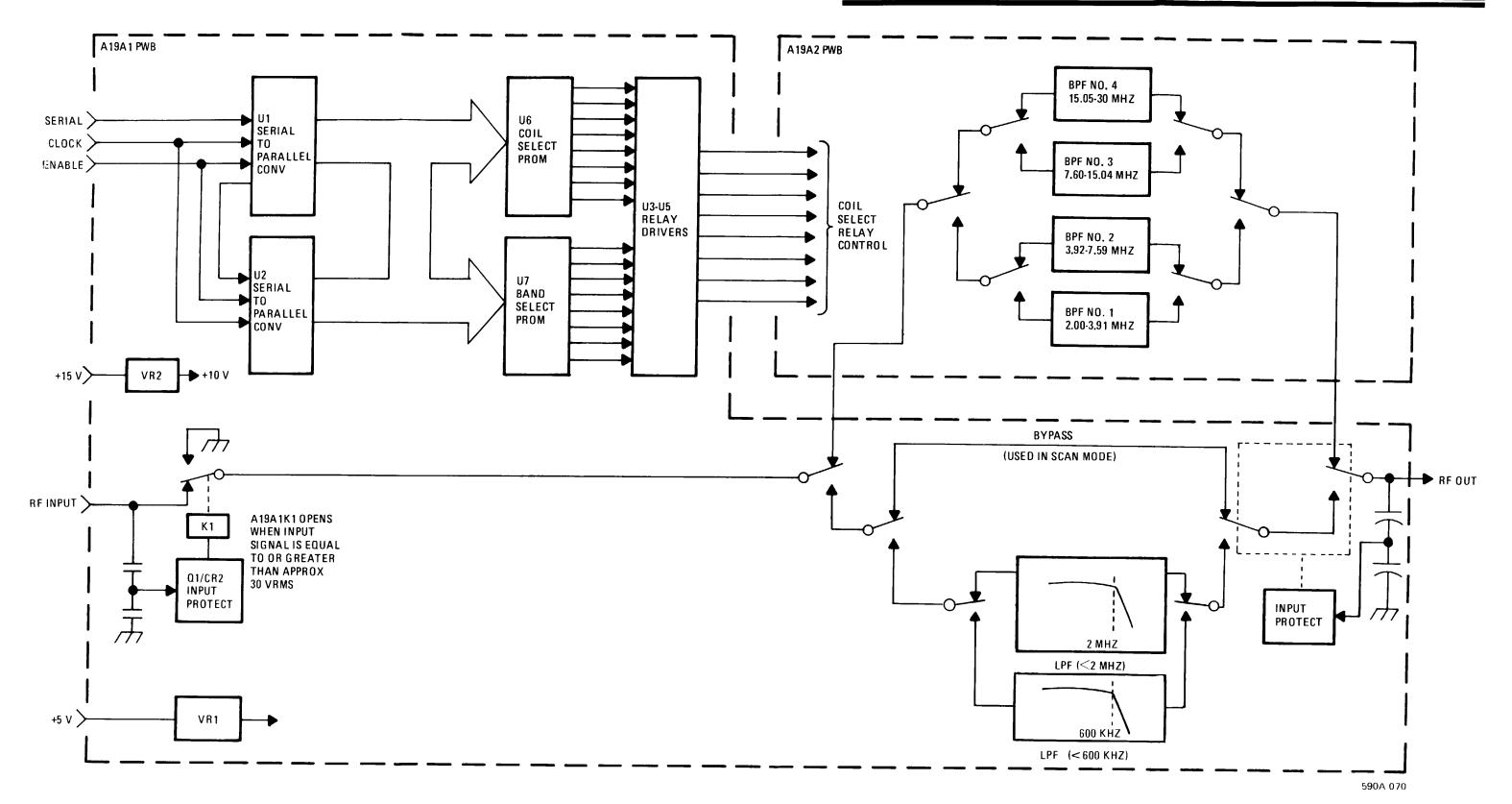

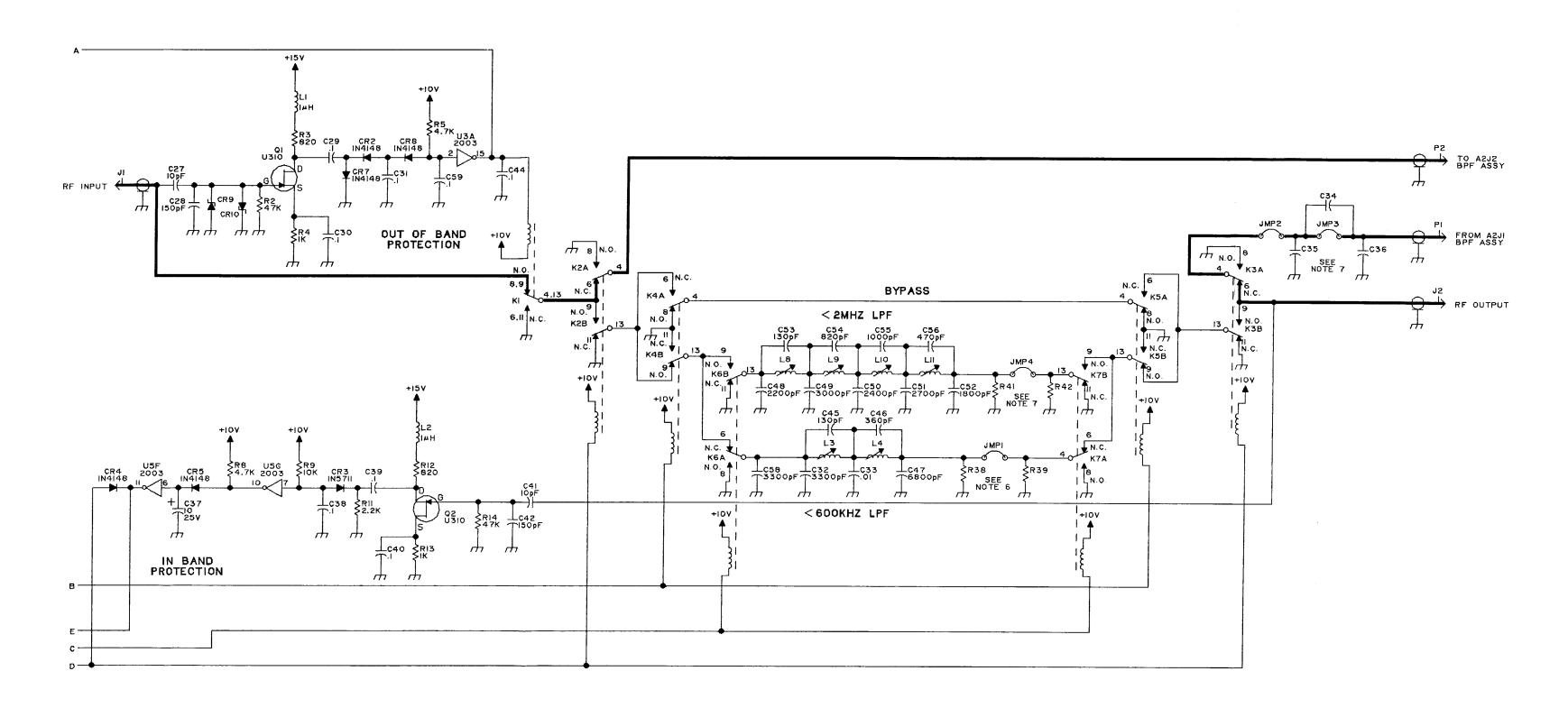

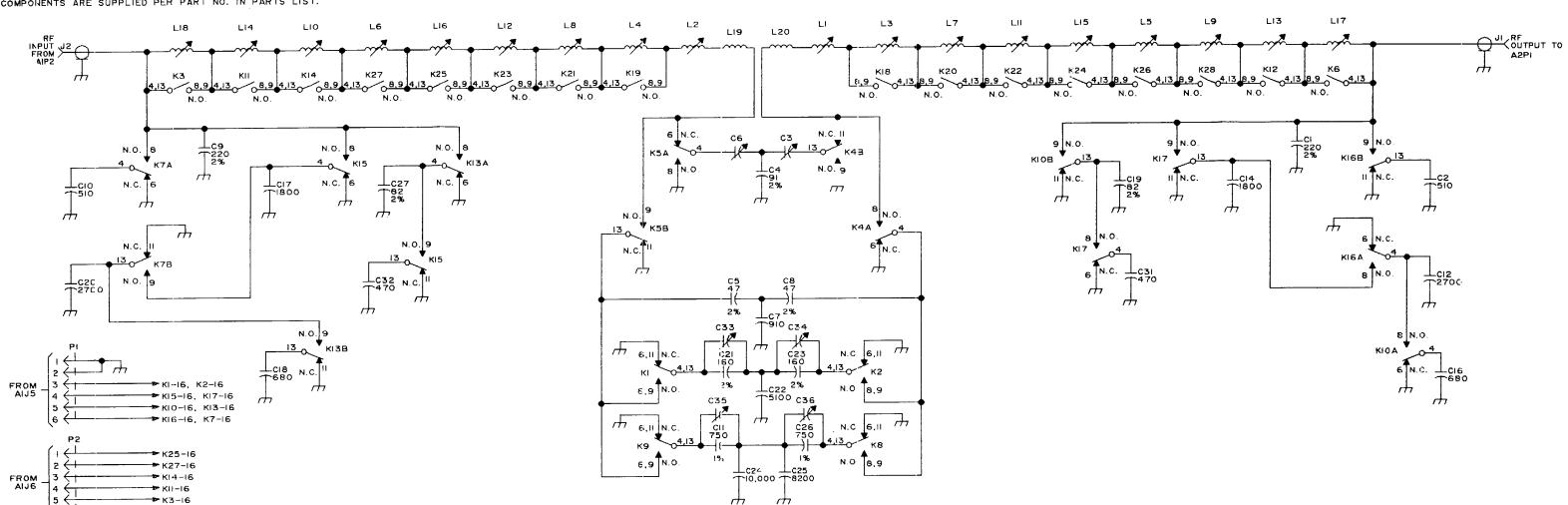

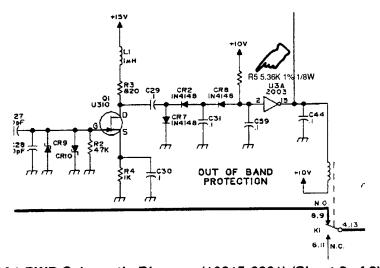

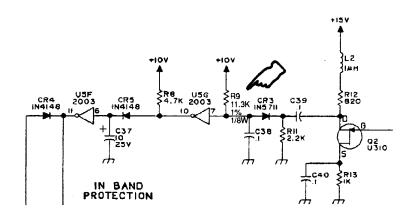

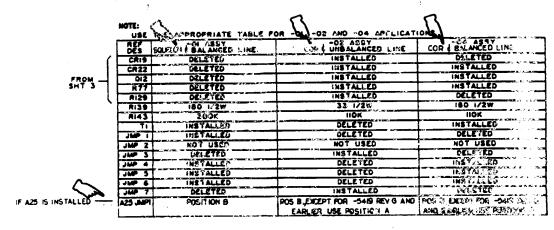

| 4.2.1.1   | Preselector Assembly A19 and Input Filter Assembly A1                  | 4-2        |

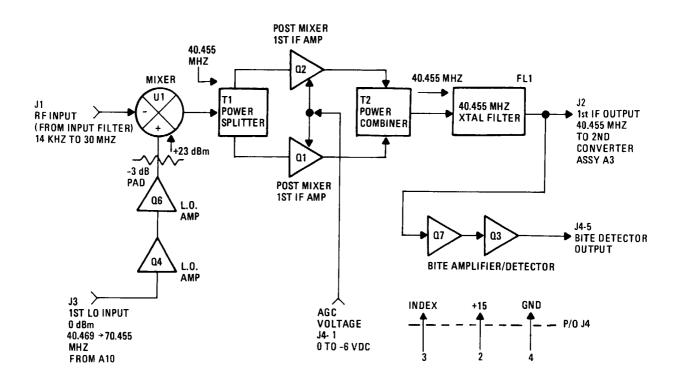

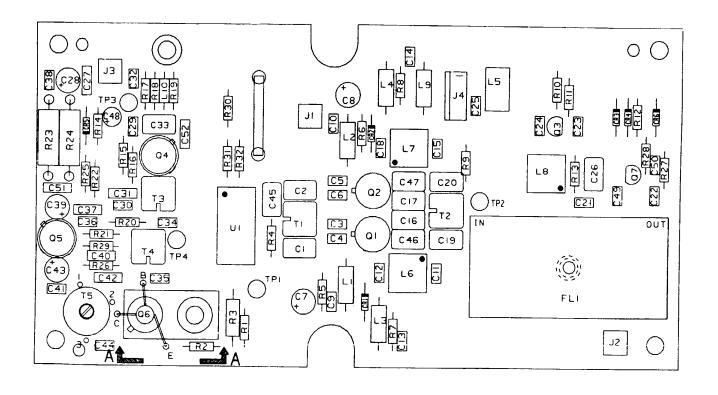

| 4.2.1.2   | First Converter Assembly A2                                            | 4-2        |

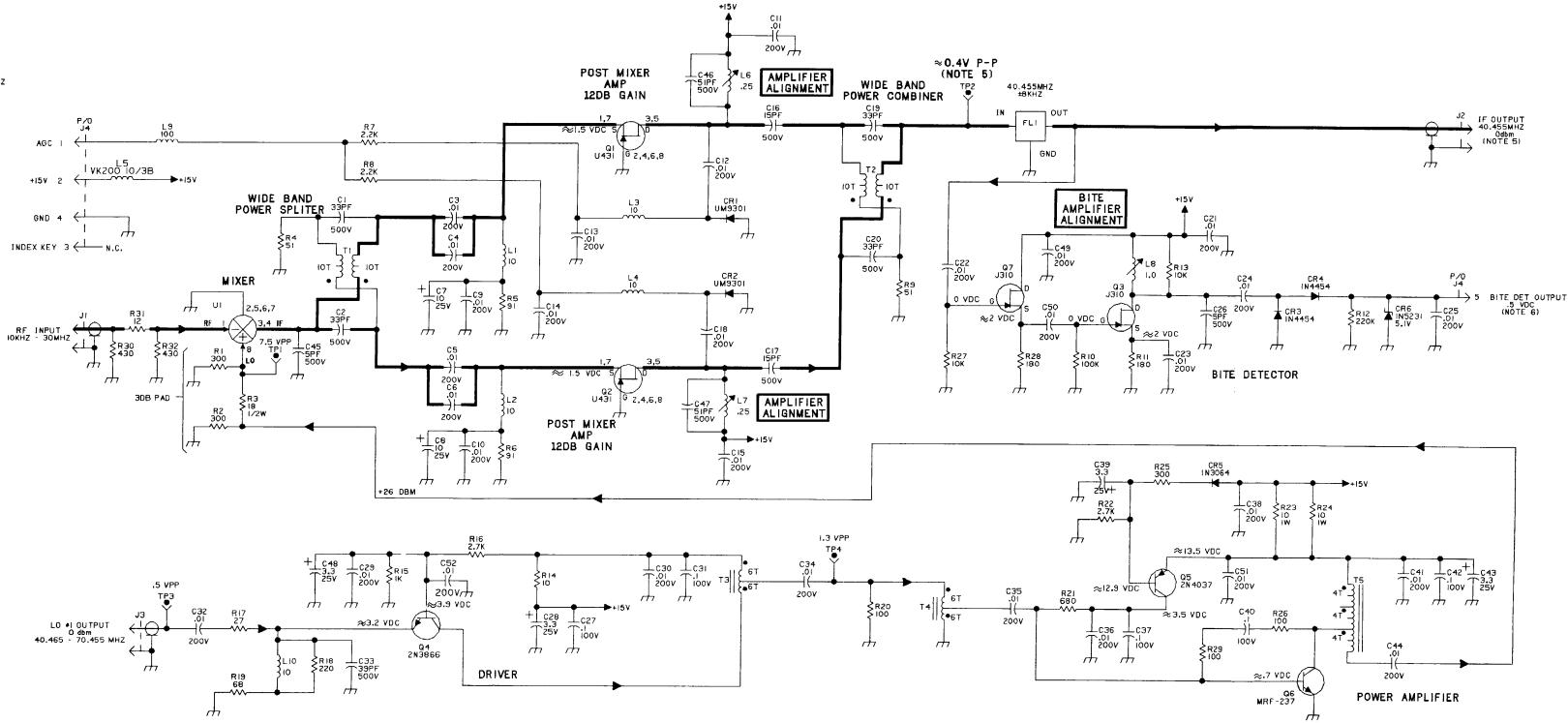

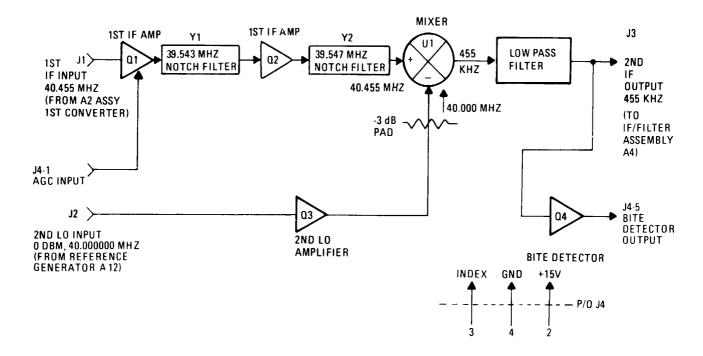

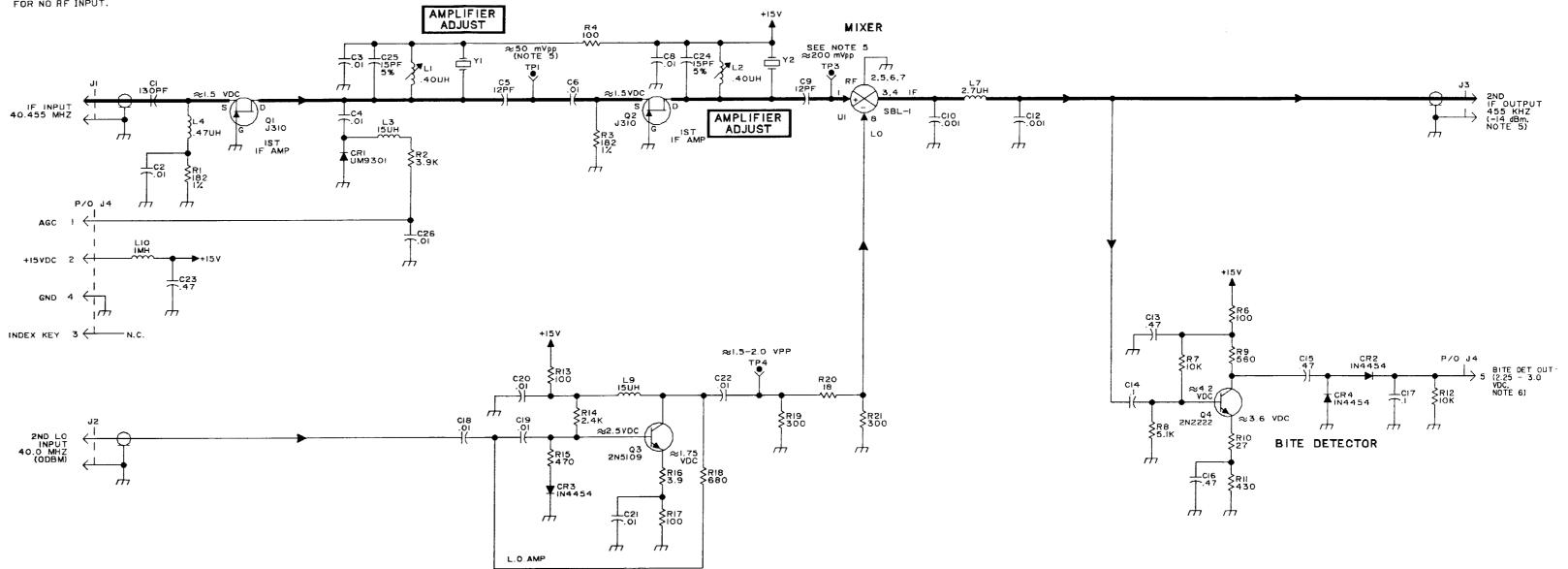

| 4.2.1.3   | Second Converter Assembly A3                                           | 4-2        |

| 4.2.1.4   | •                                                                      | 4-2<br>4-2 |

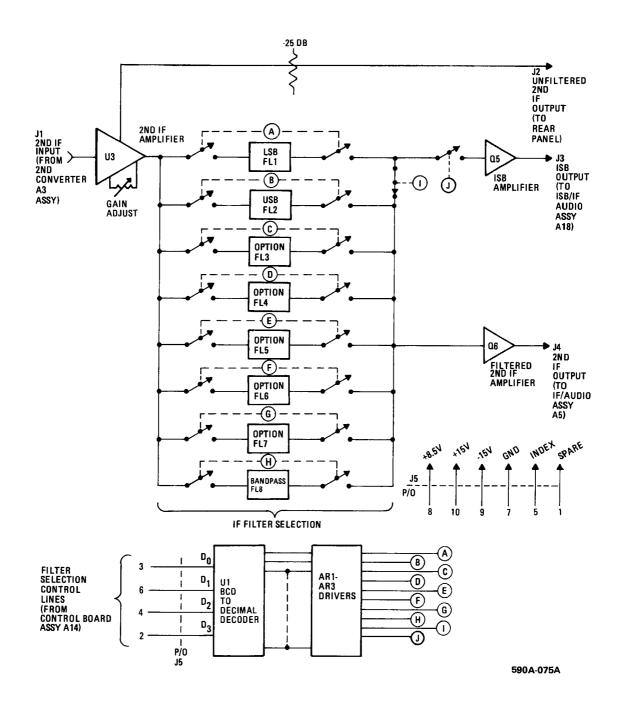

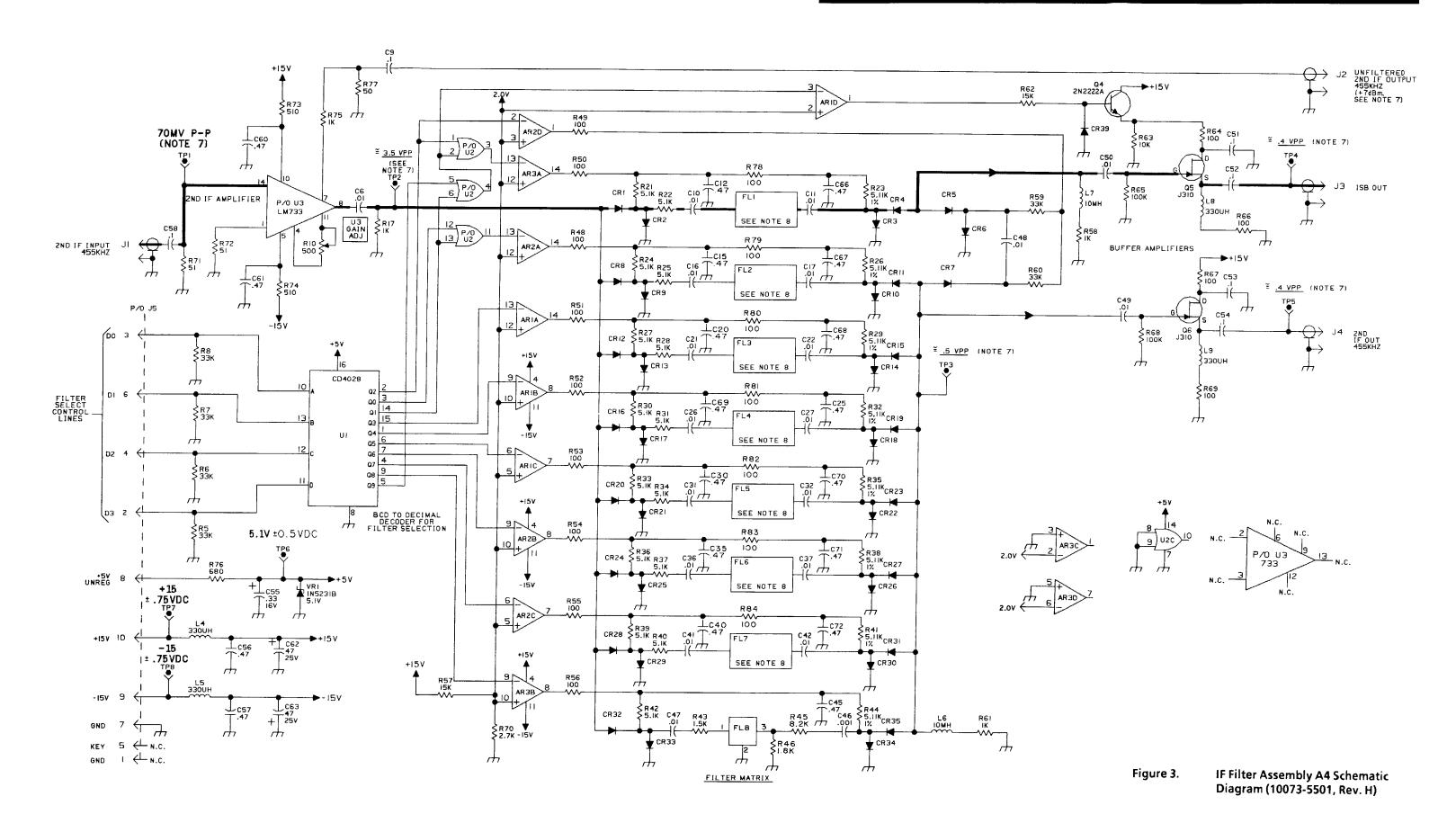

|           | IF Filter Assembly A4                                                  |            |

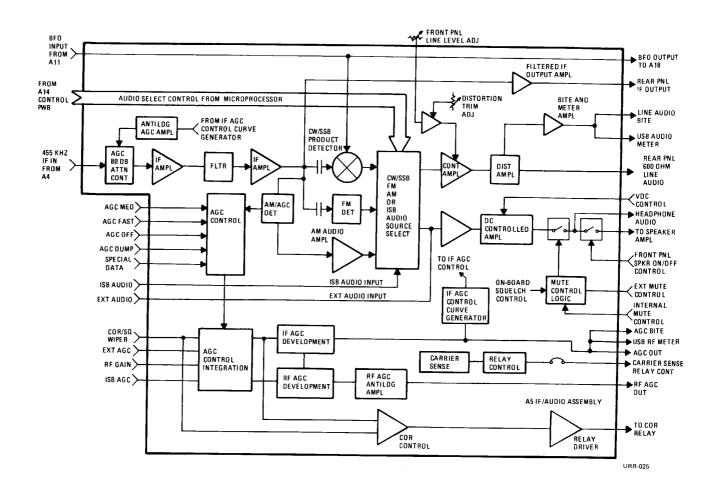

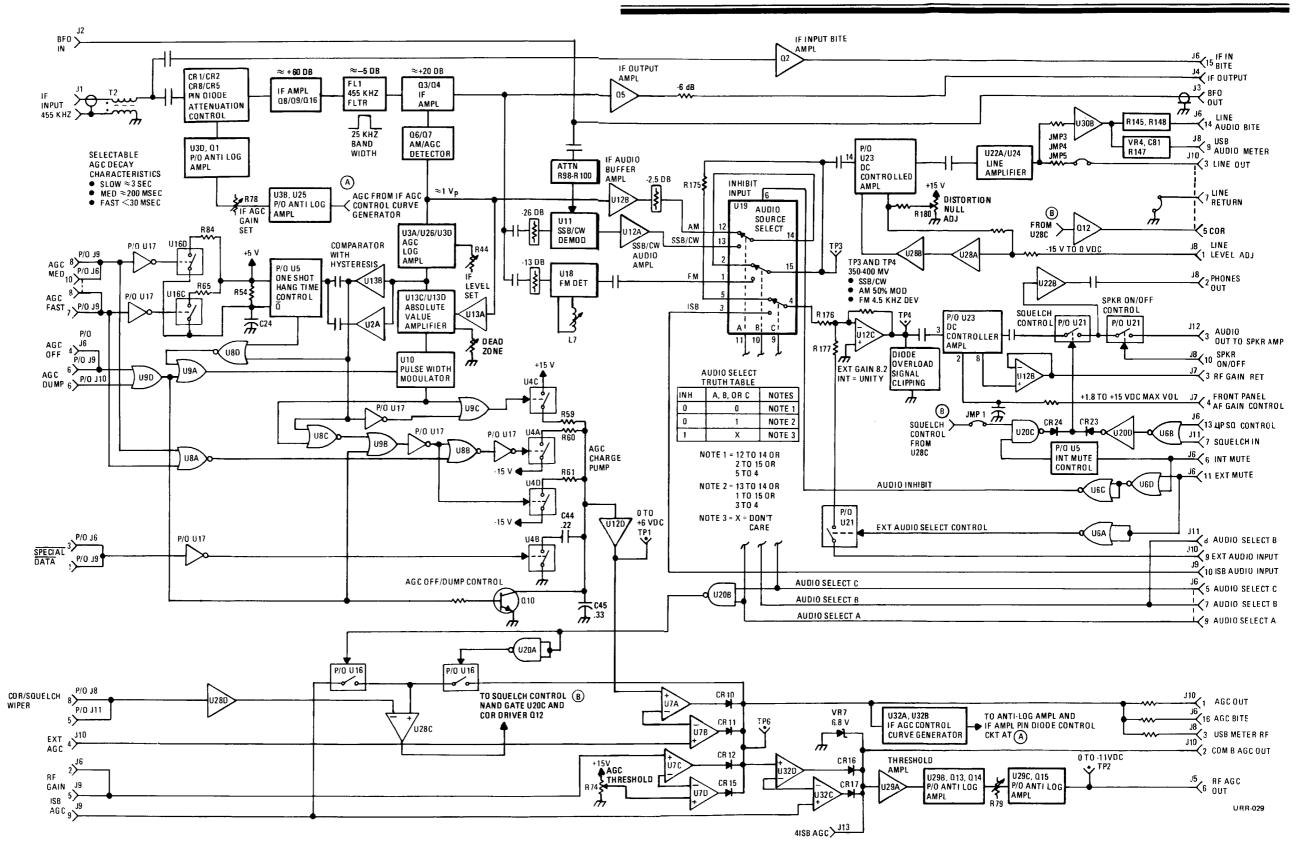

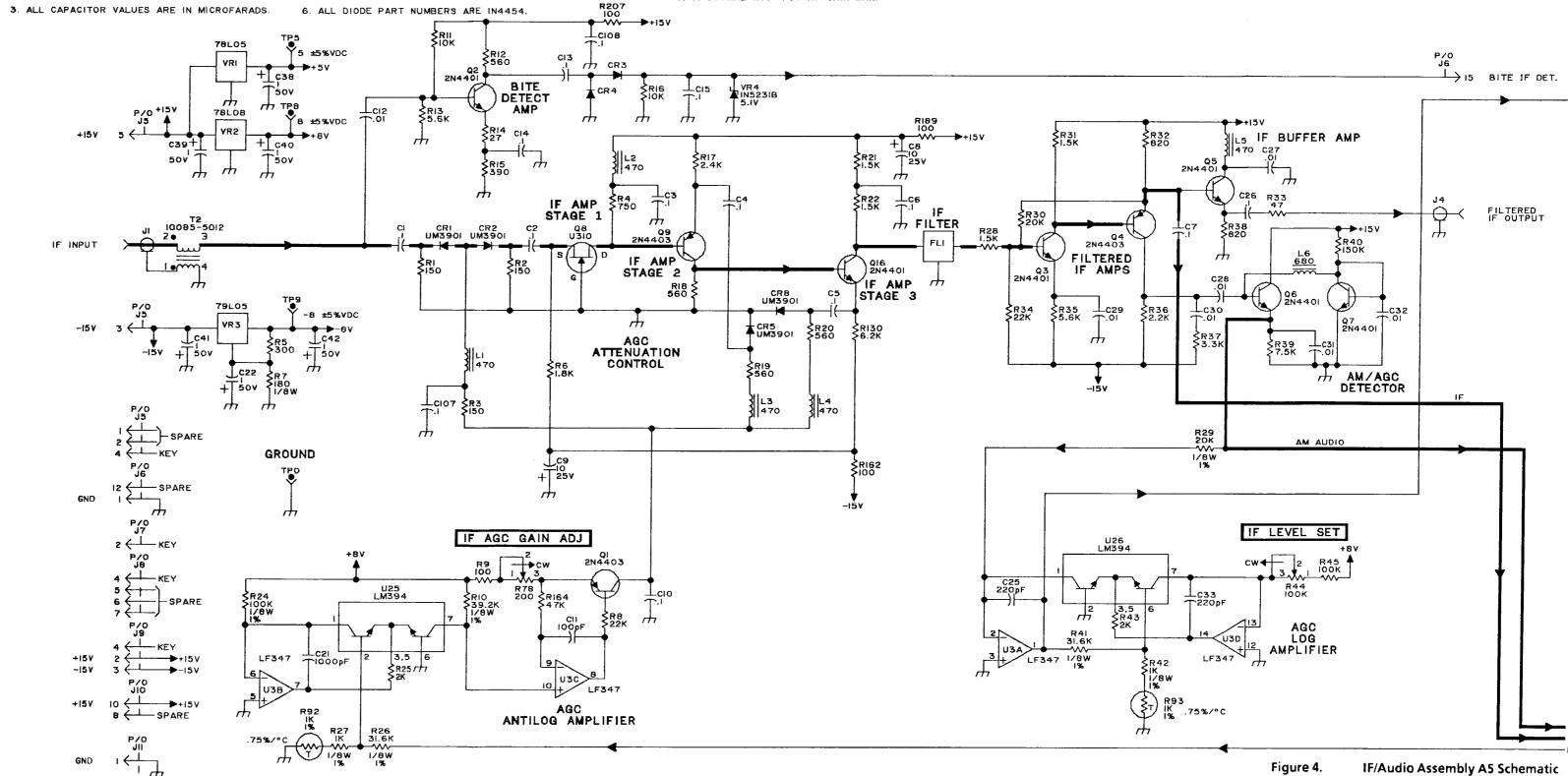

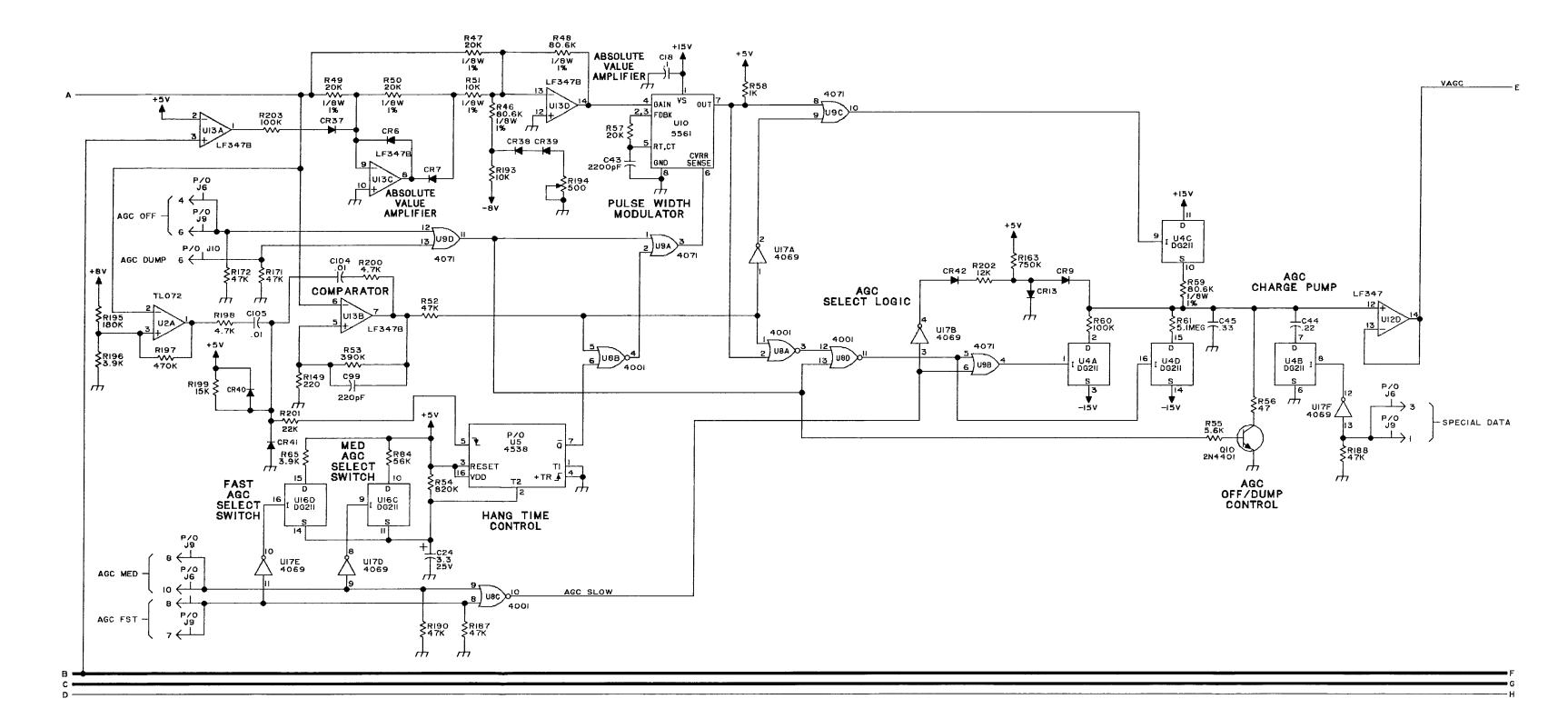

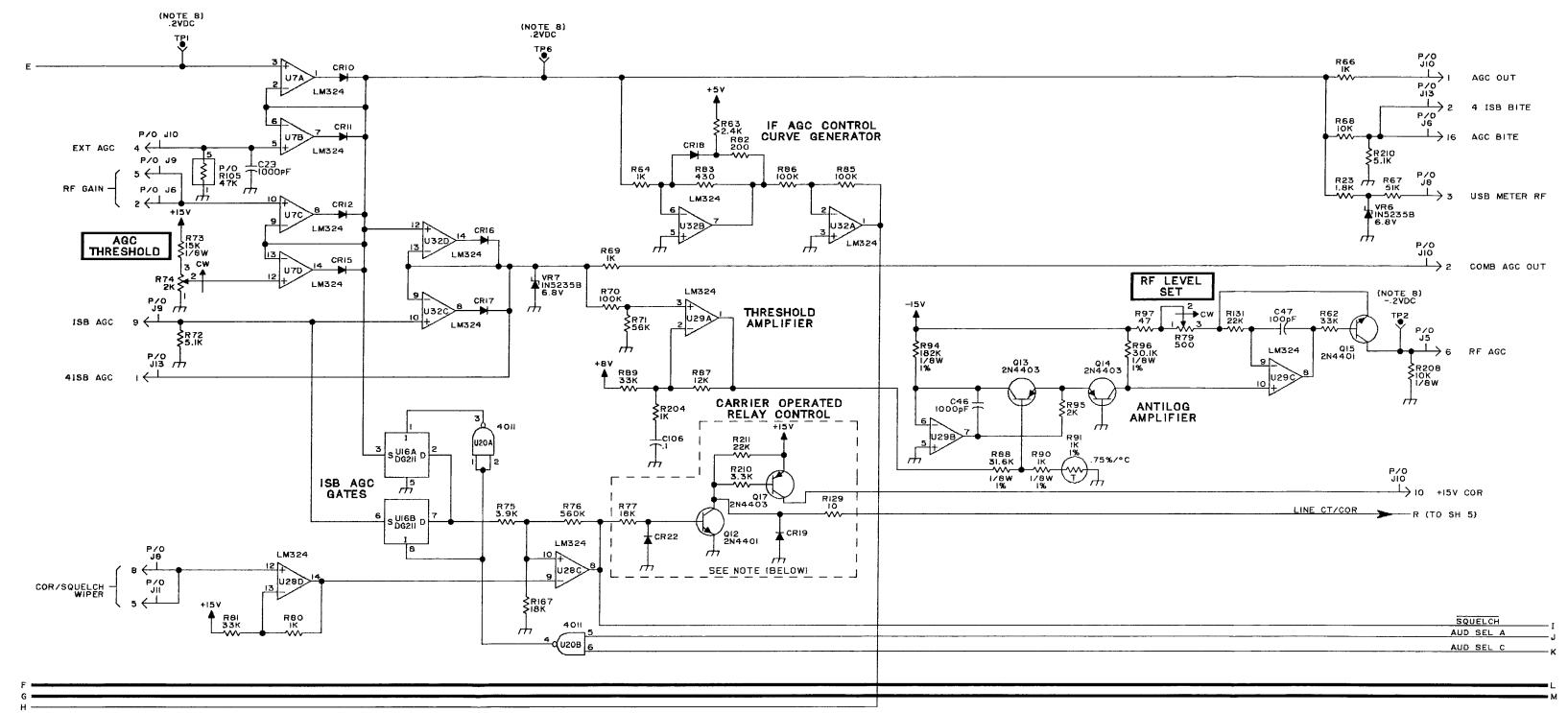

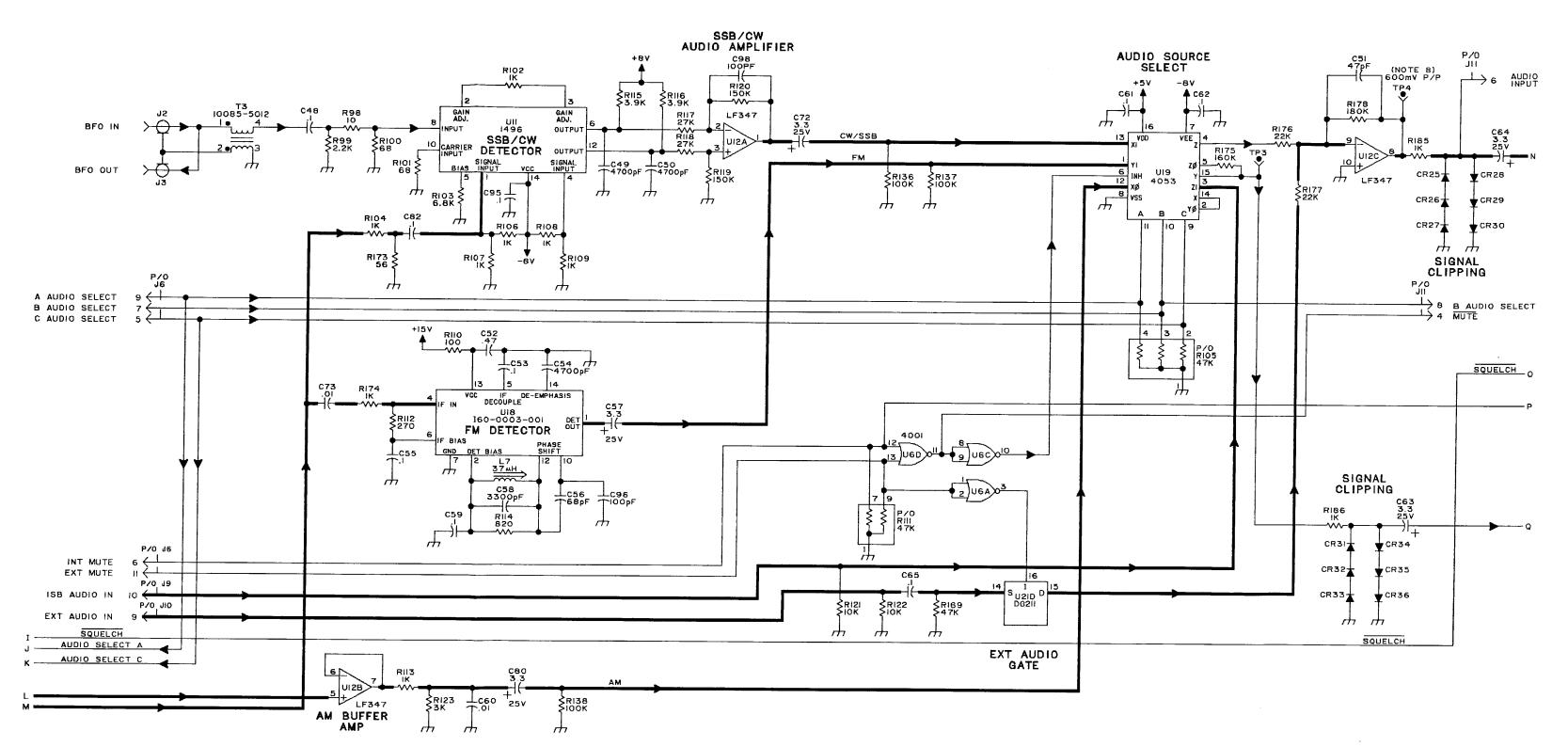

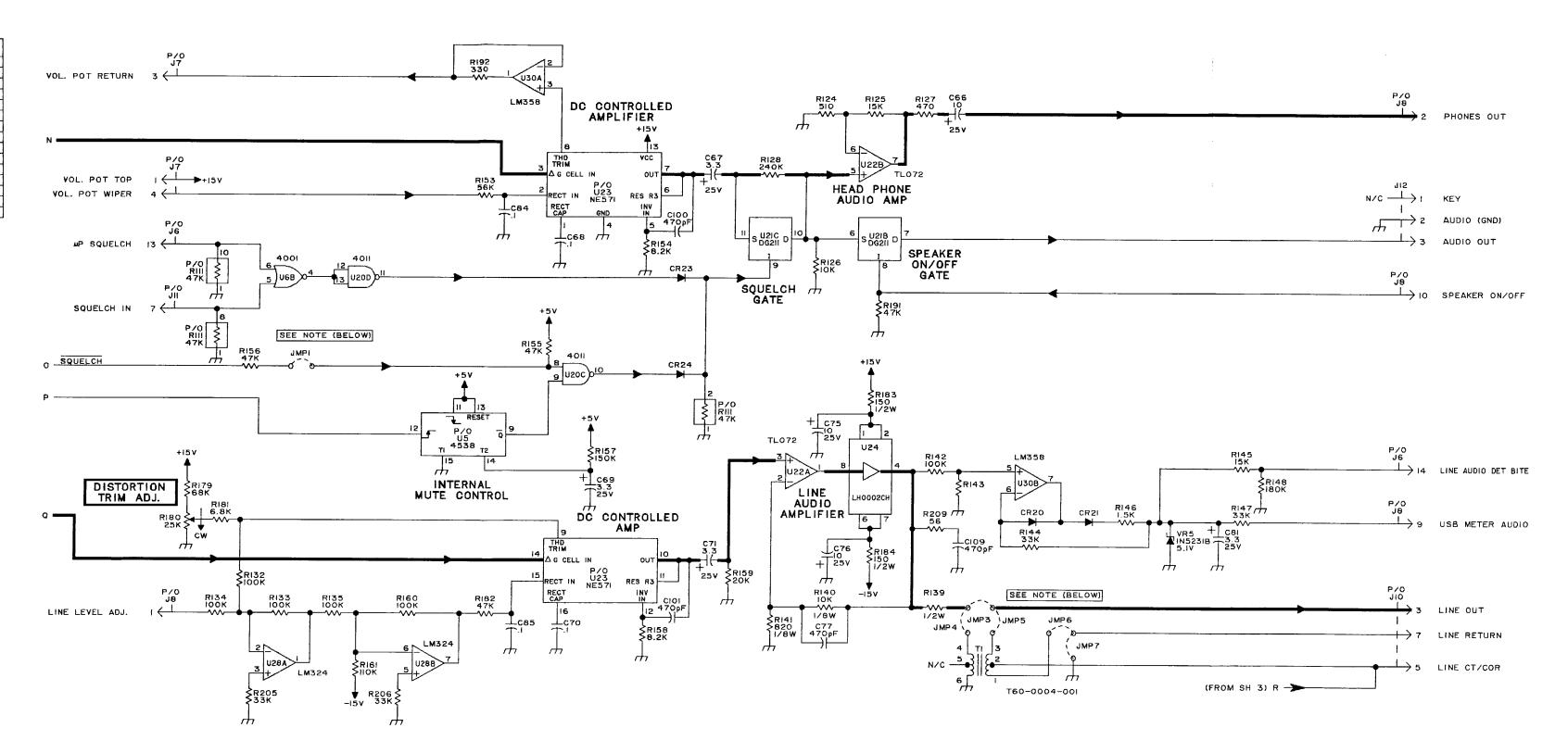

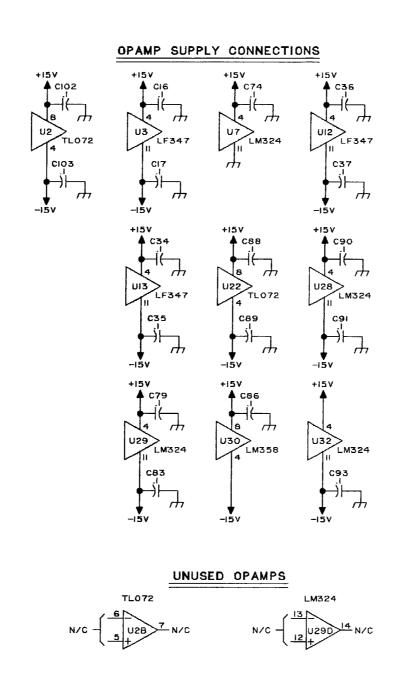

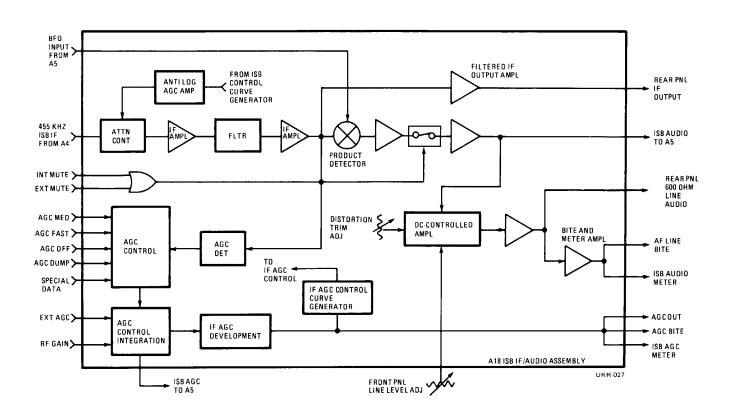

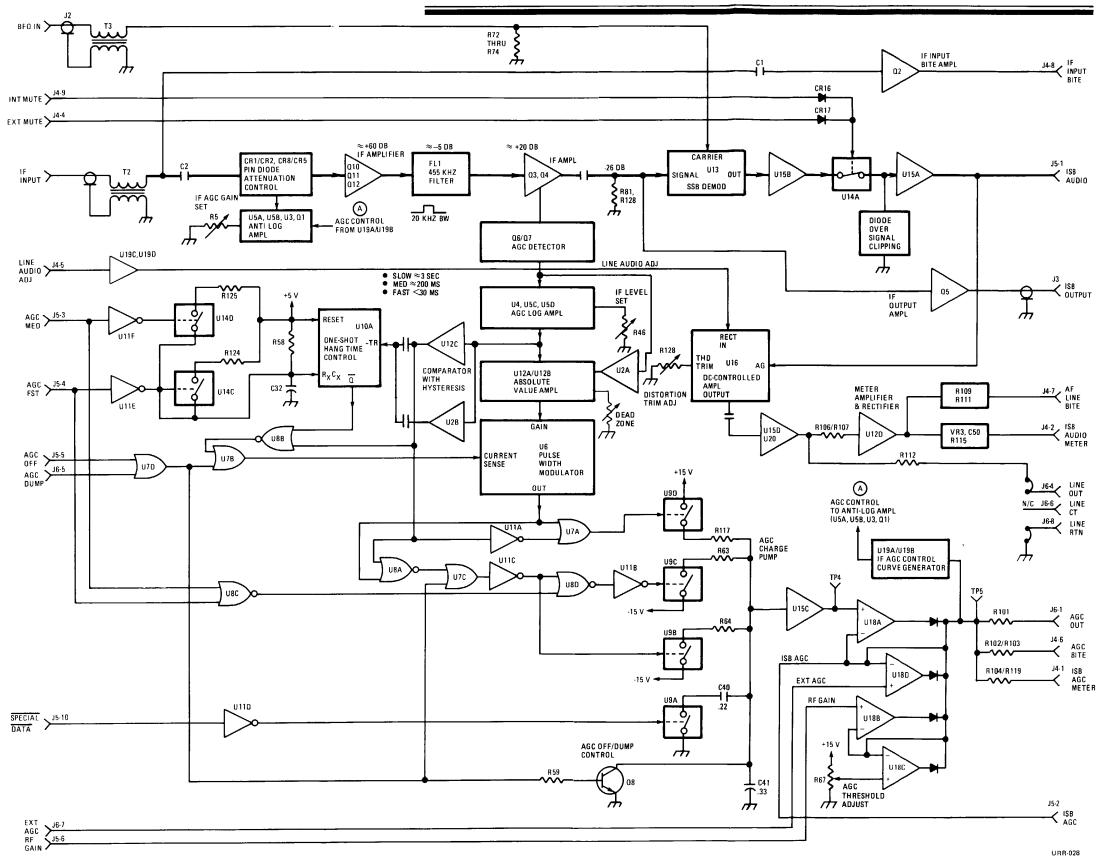

| 4.2.1.5   | IF/Audio Assembly A5                                                   | 4-6        |

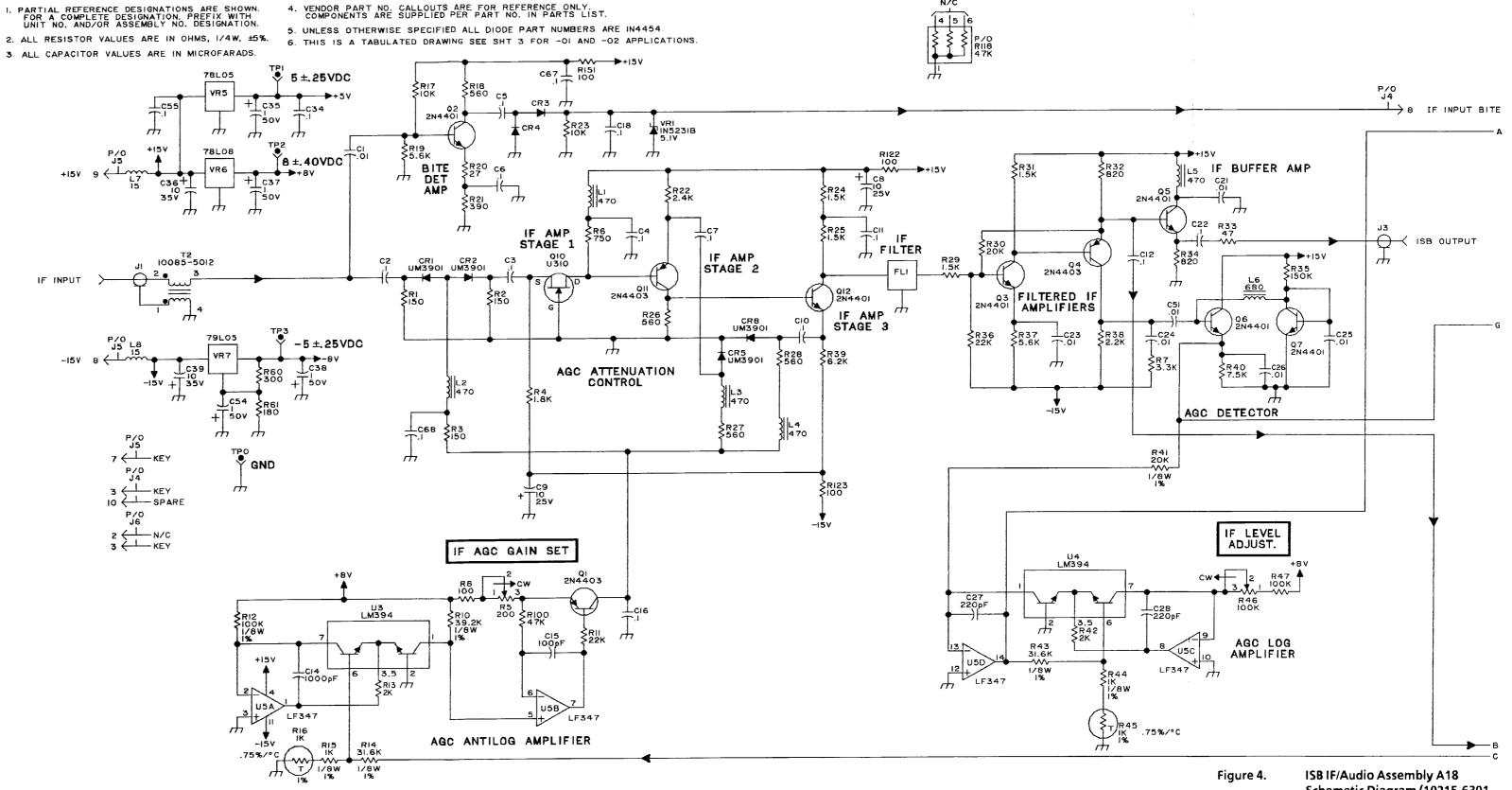

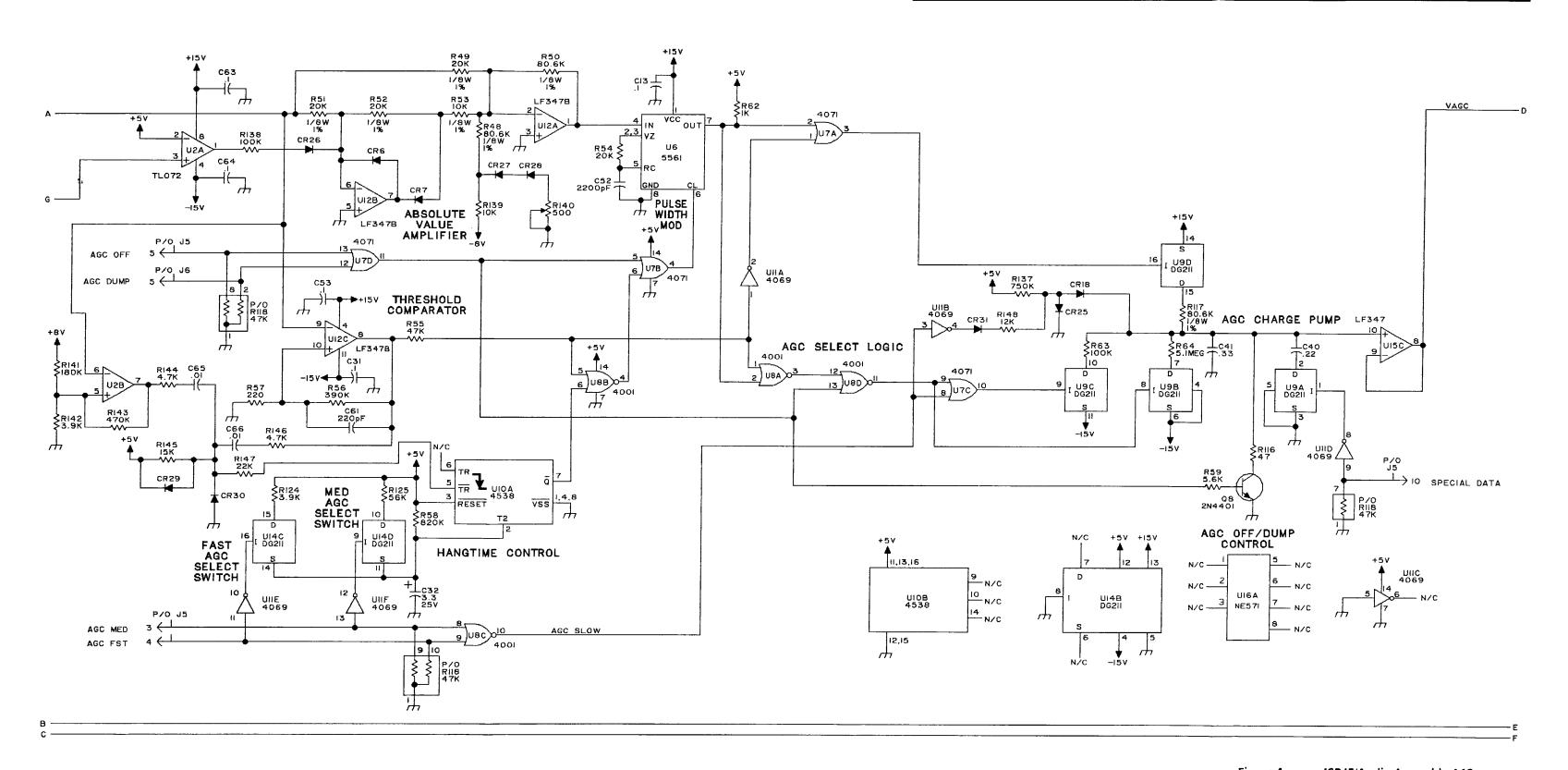

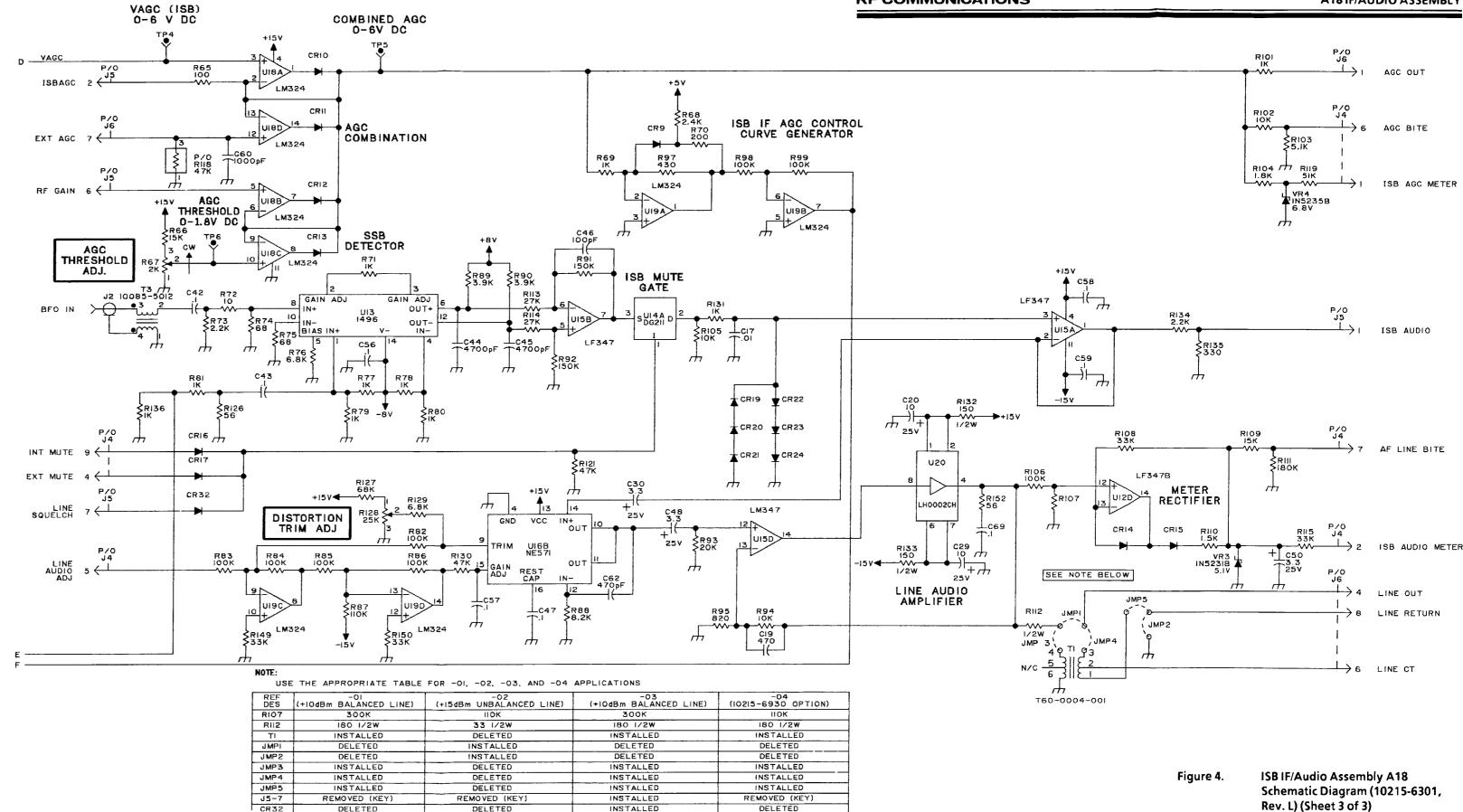

| 4.2.1.6   | ISB IF/Audio Assembly A18                                              | 4-6        |

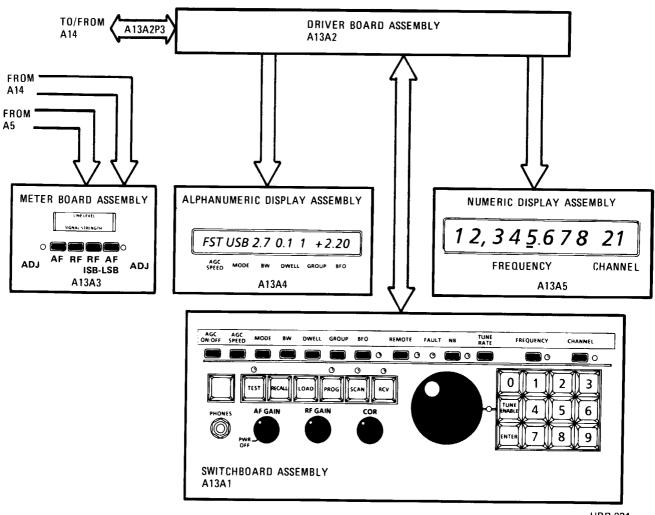

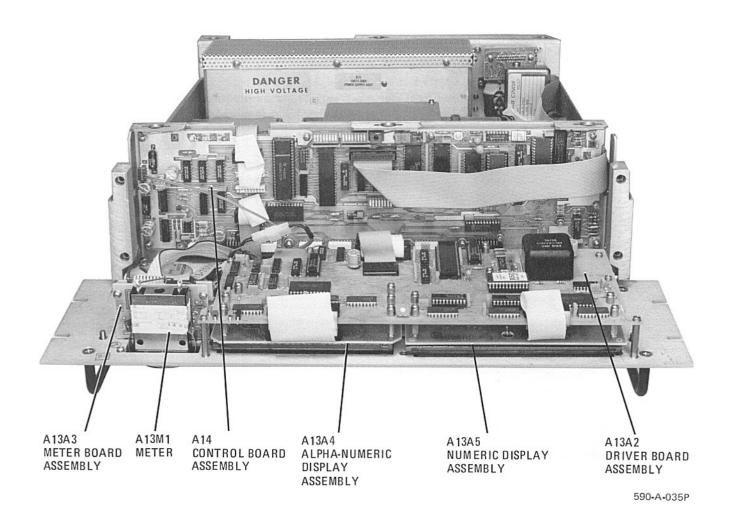

| 4.2.1.7   | Meter Board A13A3                                                      | 4-6        |

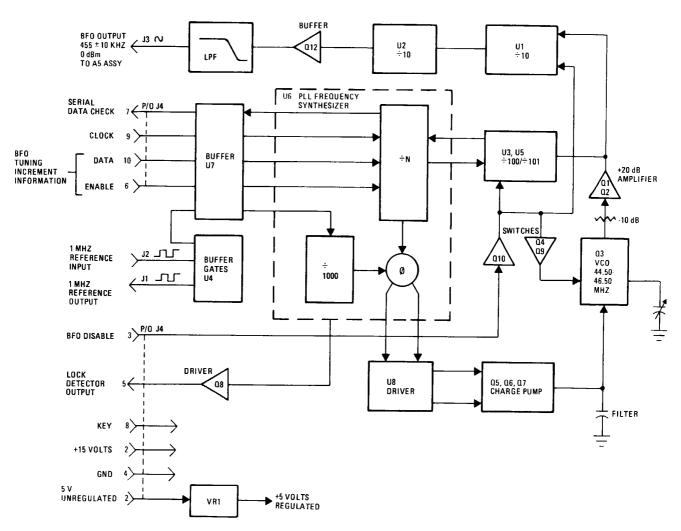

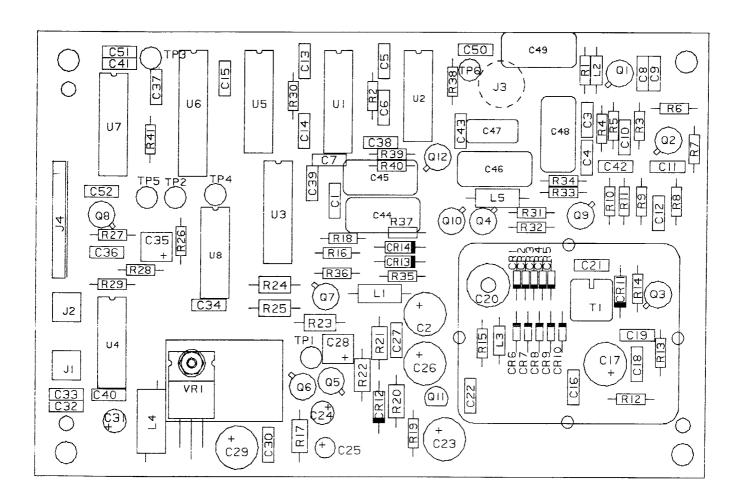

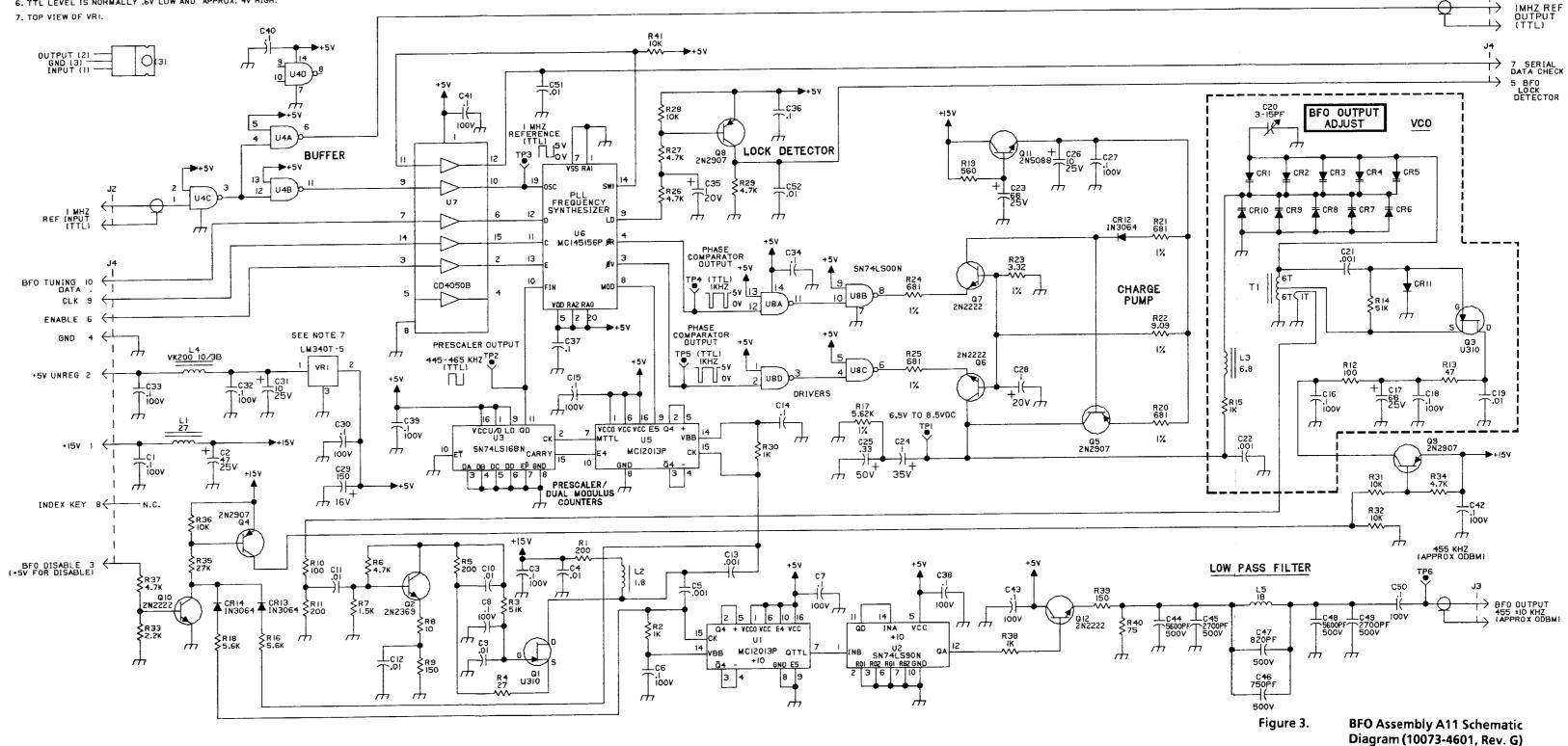

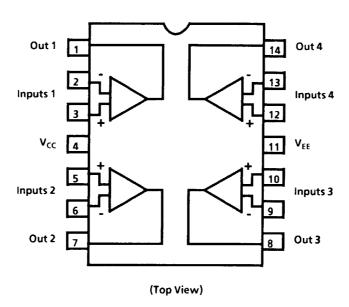

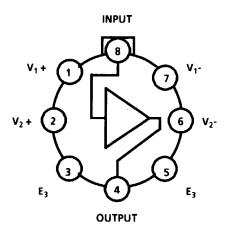

| 4.2.2     | Synthesizer BFO, Front Panel, and Control Assemblies                   | 4-7        |

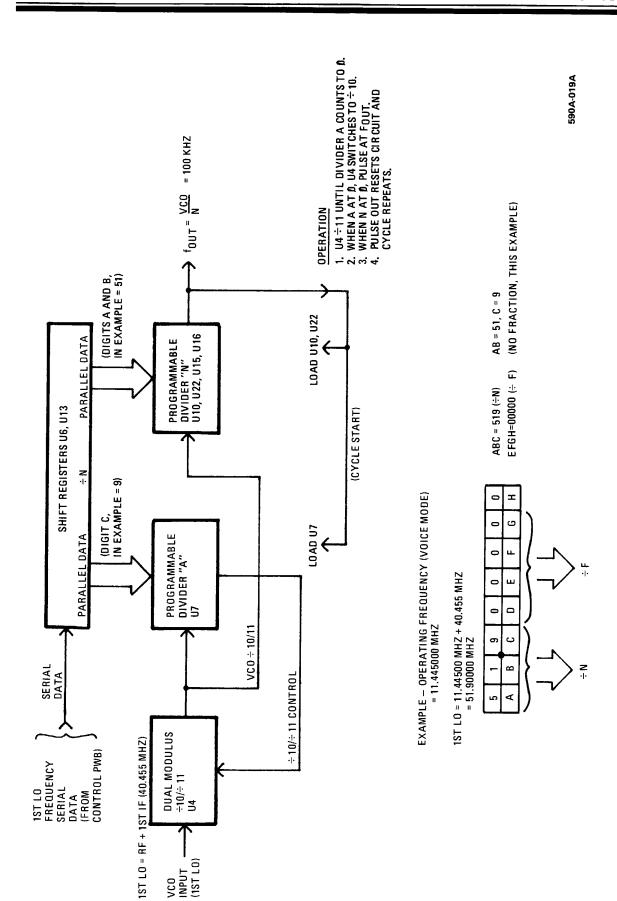

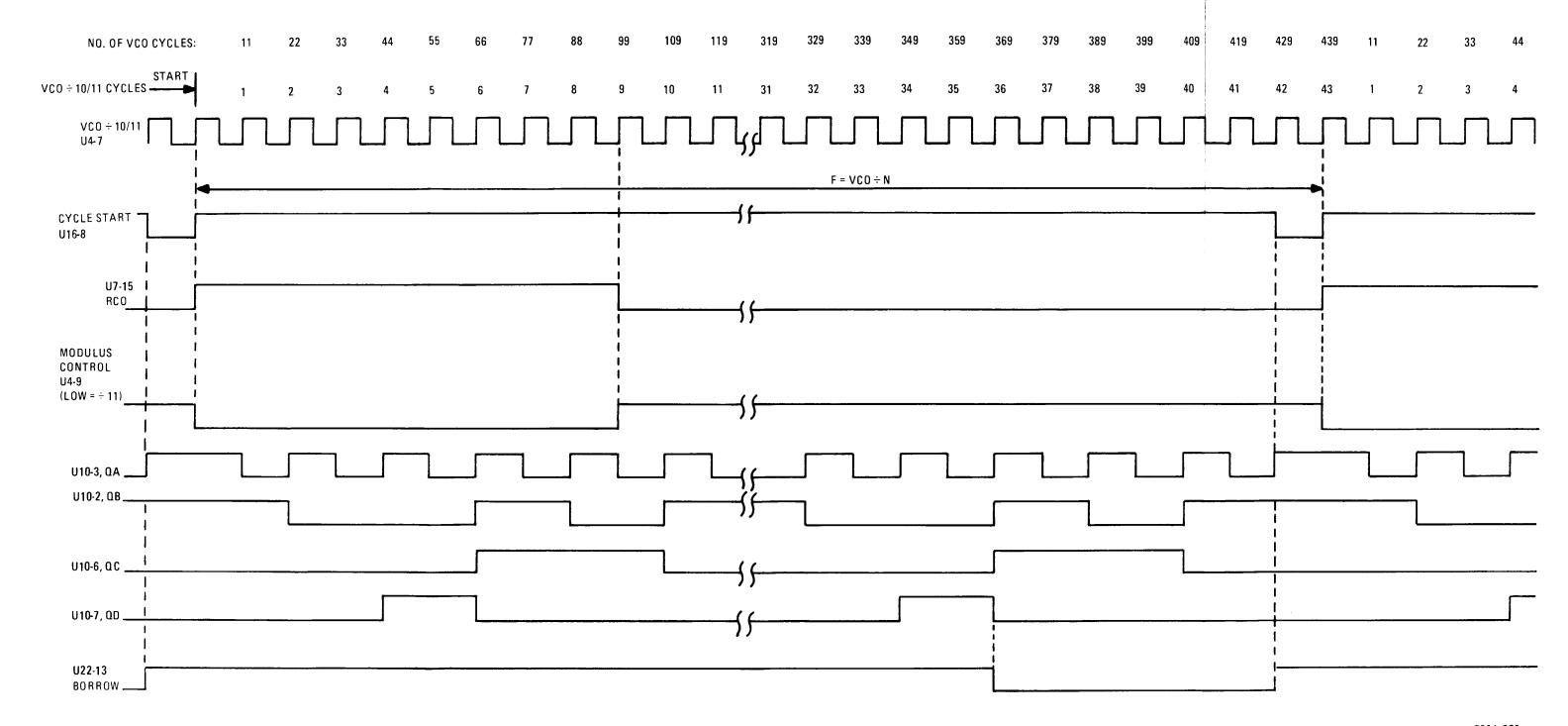

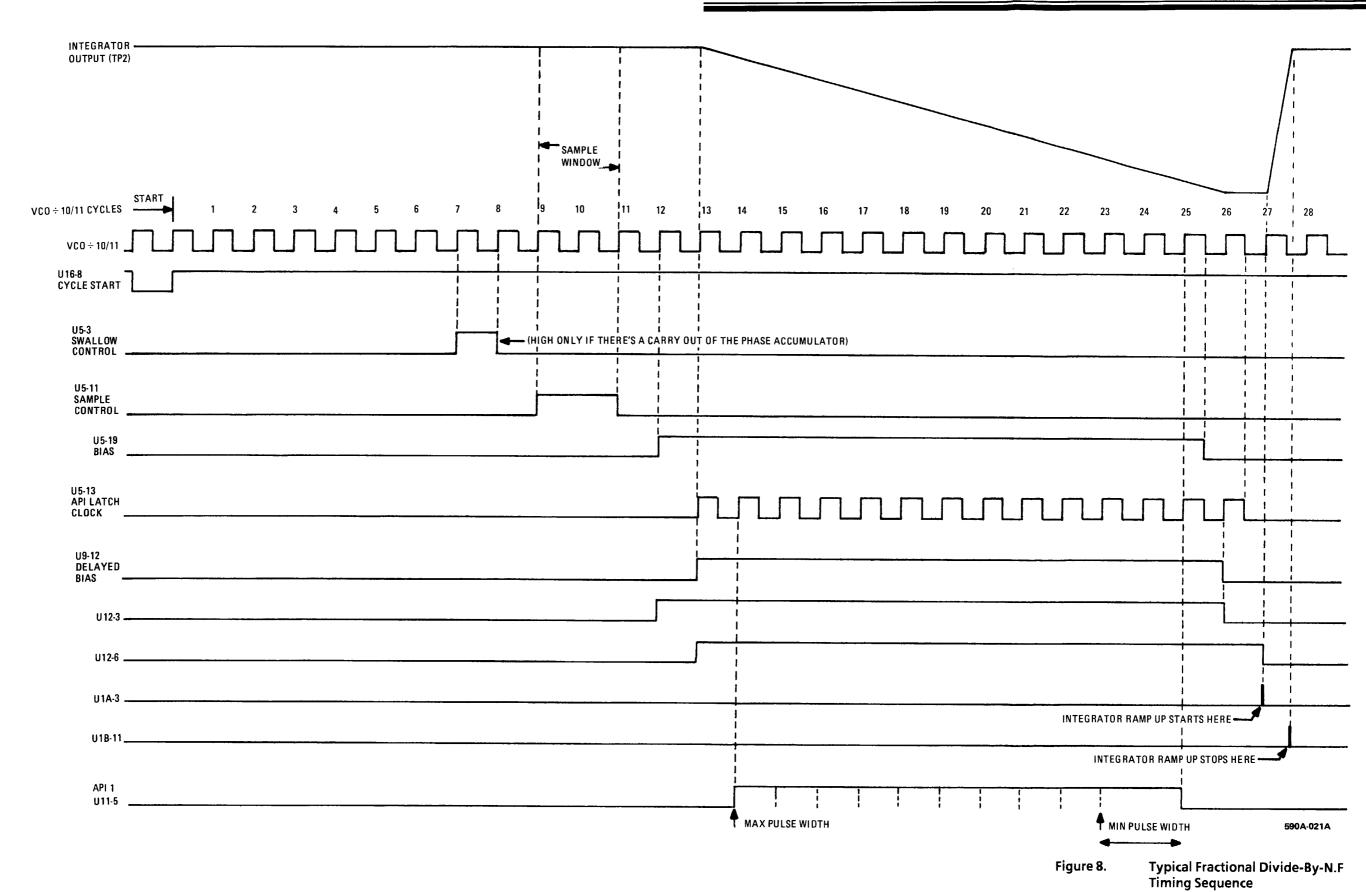

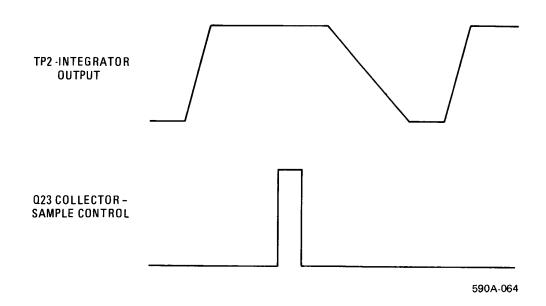

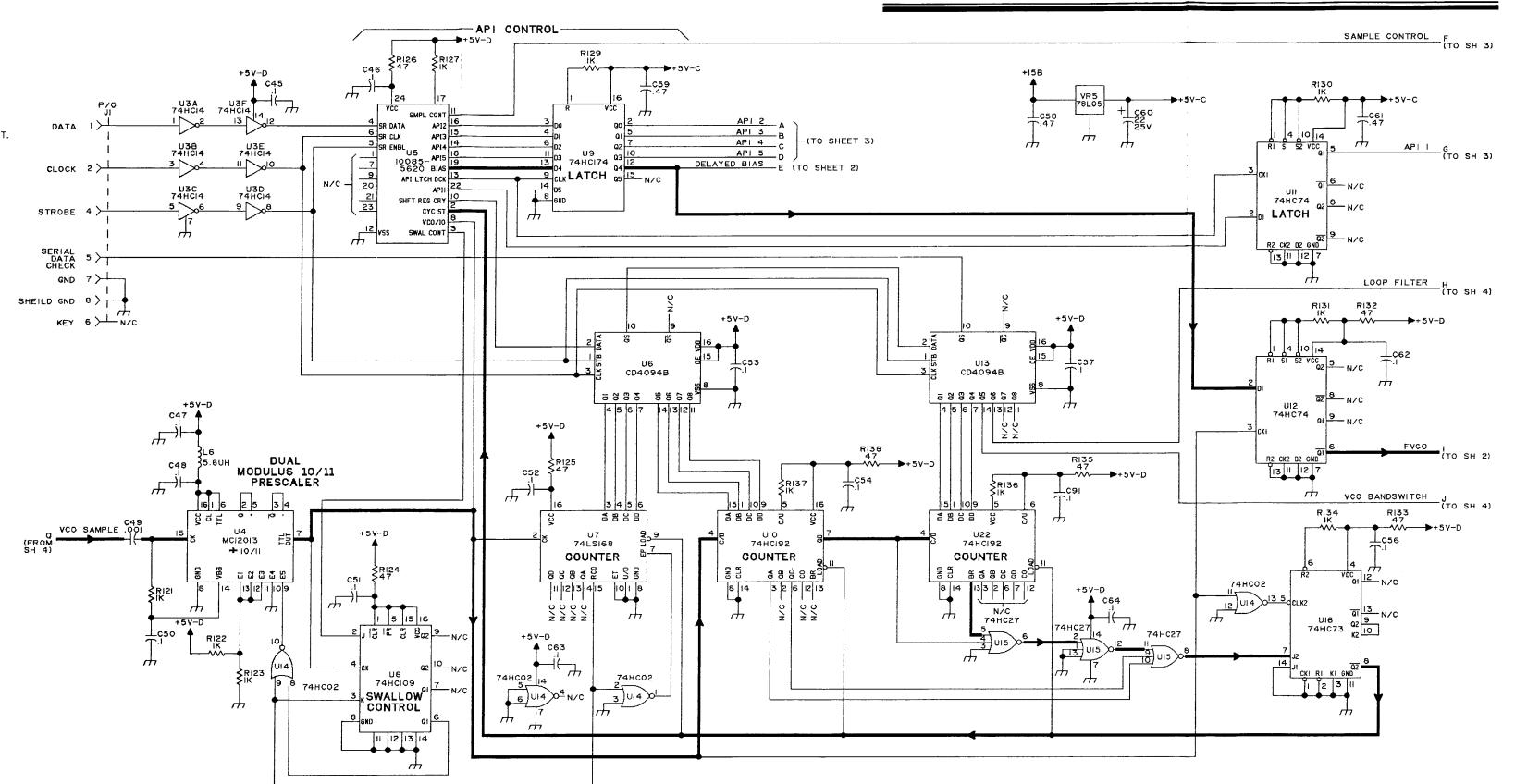

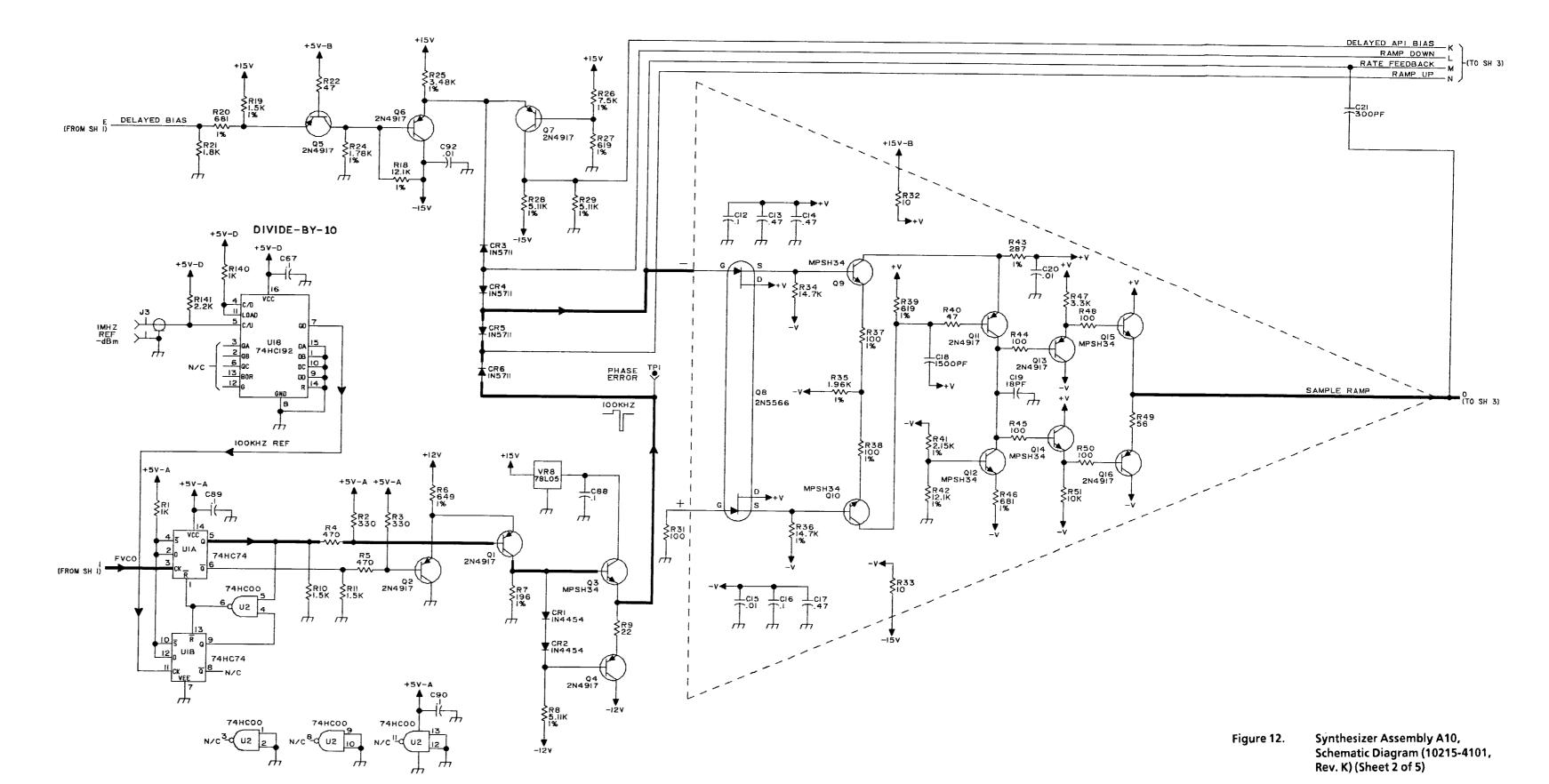

| 4.2.3     | Frequency Synthesizer Assembly A10                                     | 4-7        |

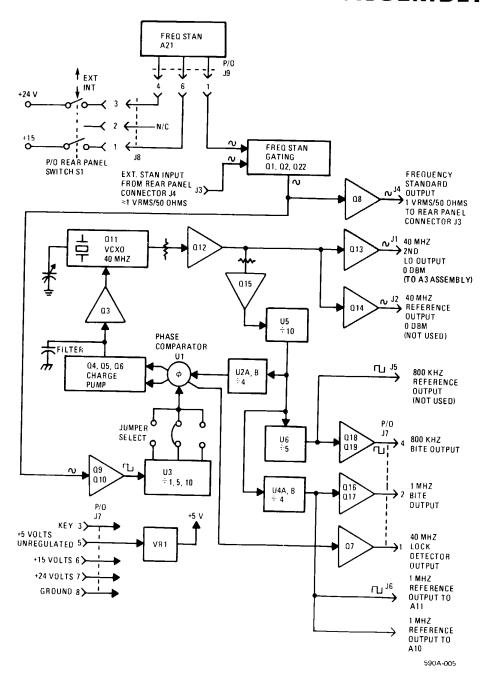

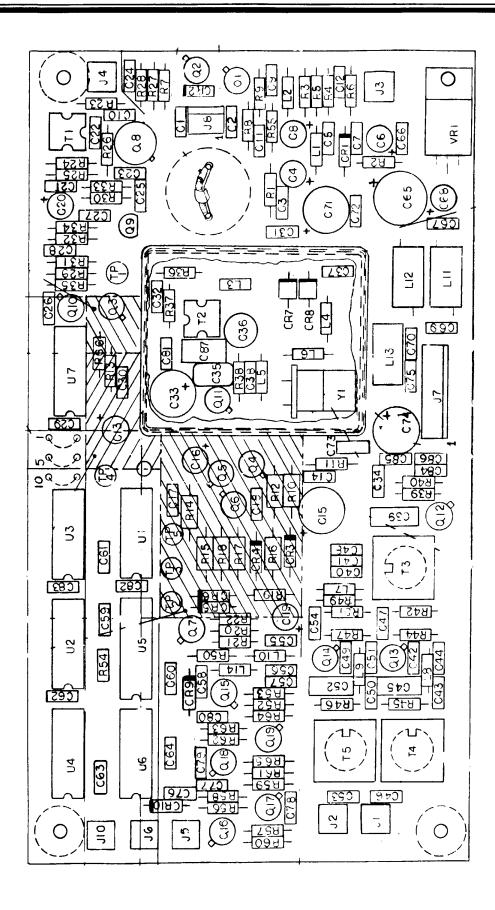

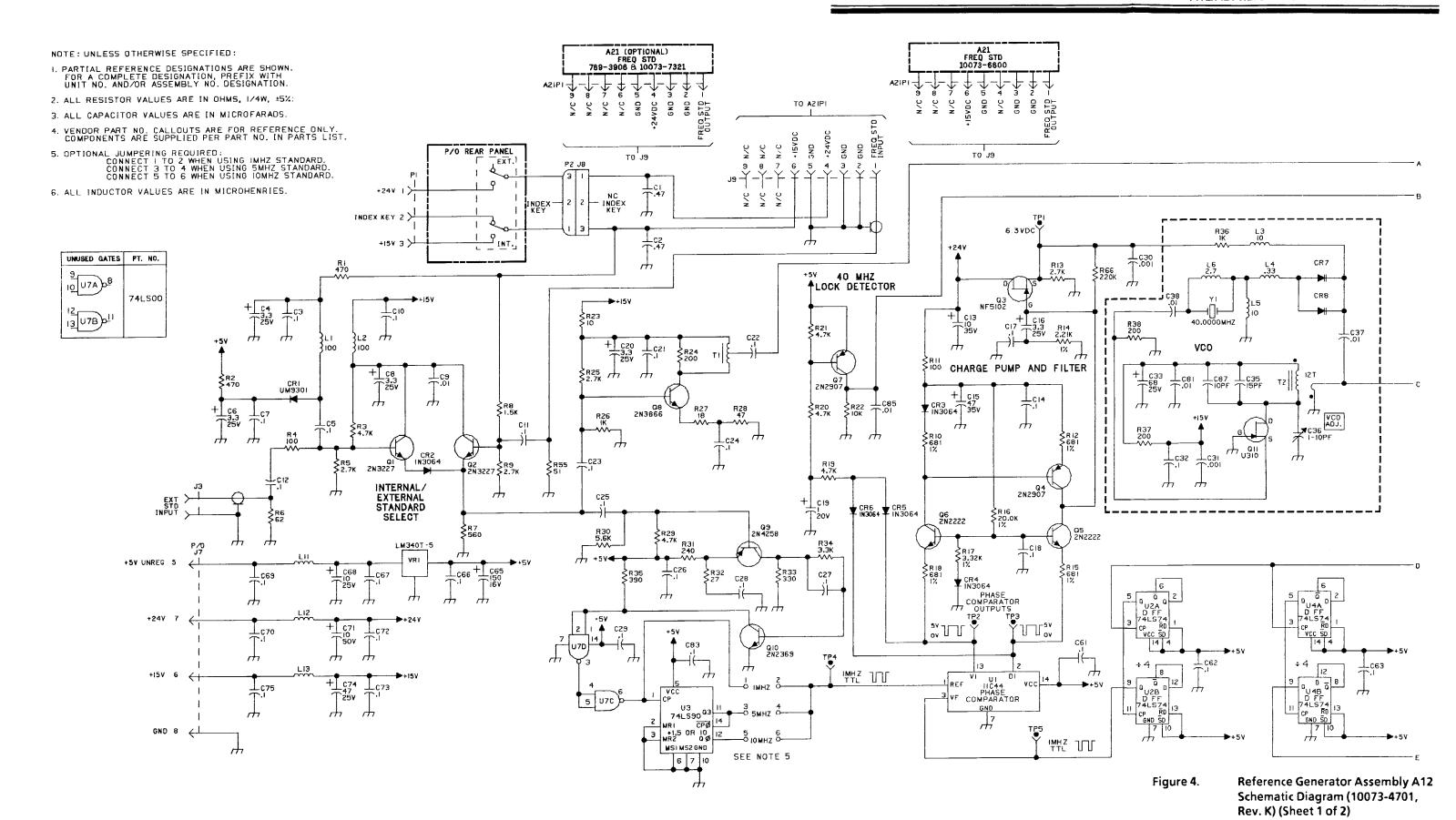

| 4.2.4     | BFO Assembly A12                                                       | 4-7        |

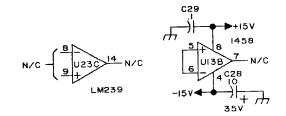

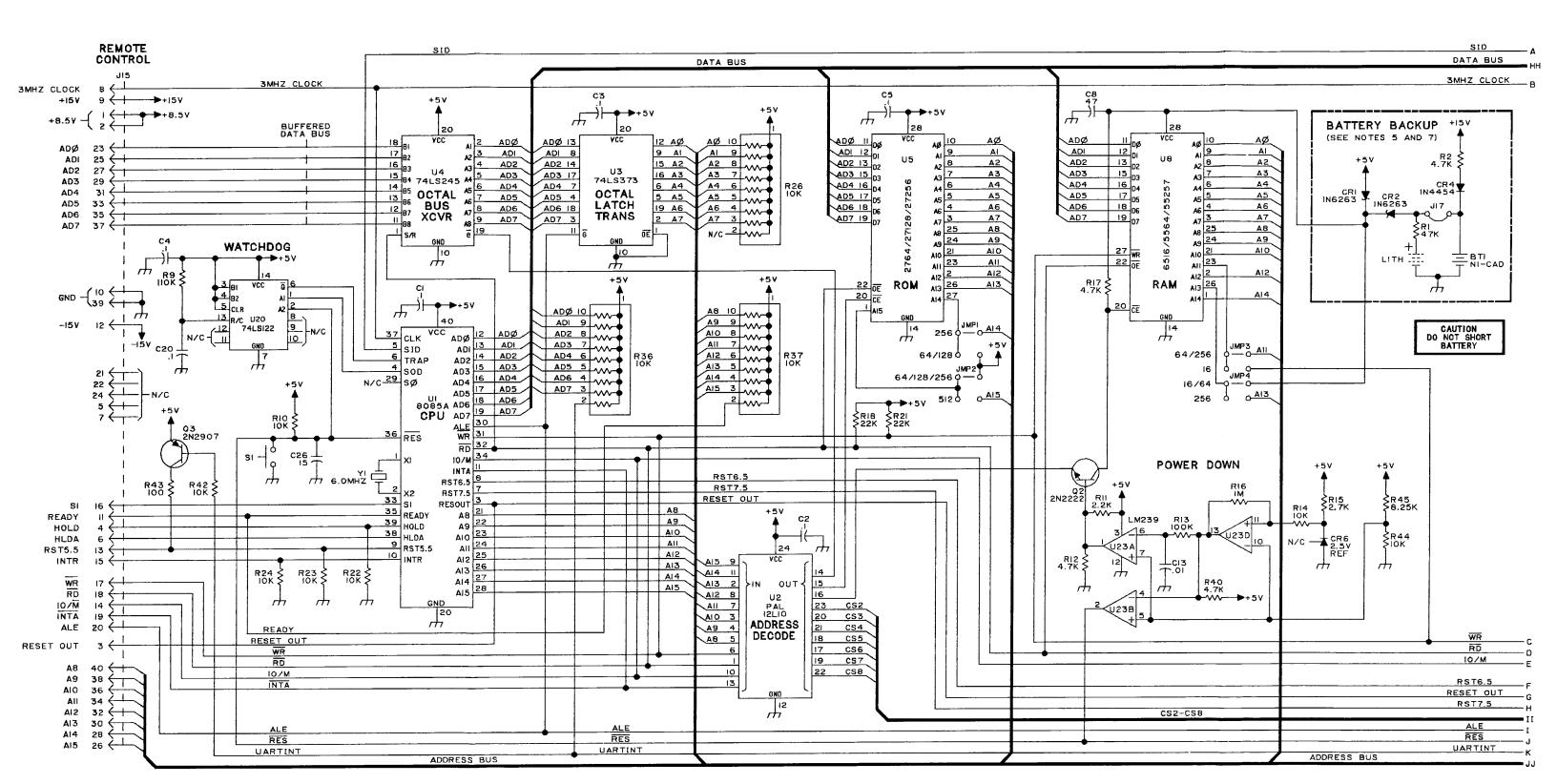

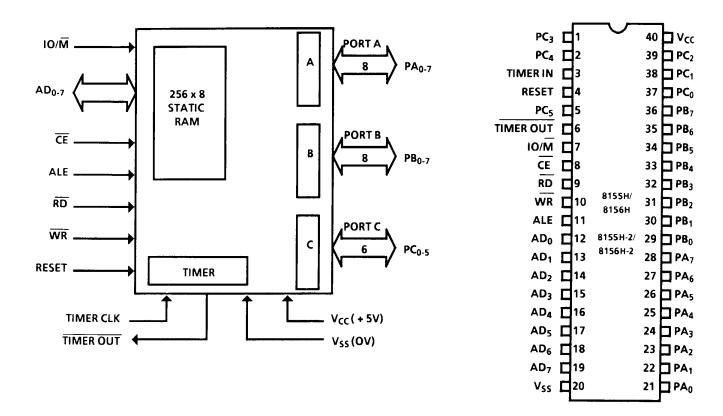

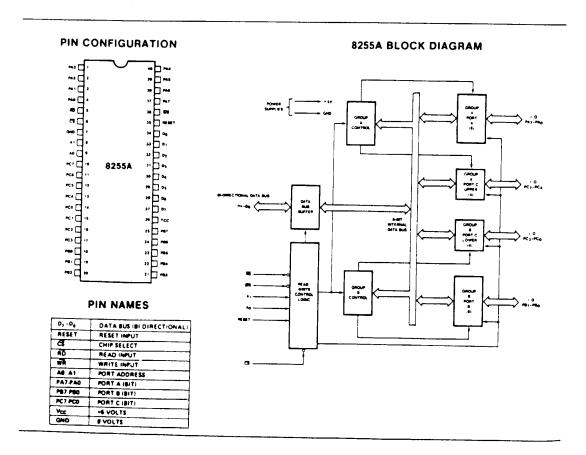

| 4.2.5     | Control PWB Assembly A14                                               | 4-7        |

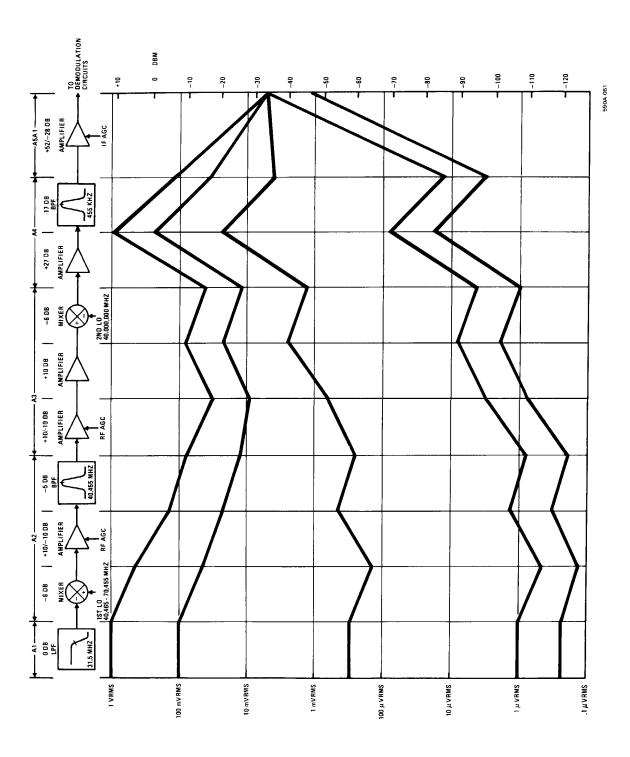

| 4.3       | Conversion Between dBm and Vrms                                        | 4-7        |

#### **TABLE OF CONTENTS (Cont.)**

| Paragraph  |                                                       | Page         |

|------------|-------------------------------------------------------|--------------|

|            | SECTION 5 - MAINTENANCE                               |              |

| 5.1        | Introduction                                          | 5-1          |

| 5.2        | PWB Repairs                                           | 5-1          |

| 5.3        | MOSFET Replacement                                    | 5-1          |

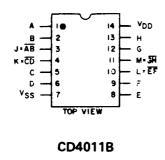

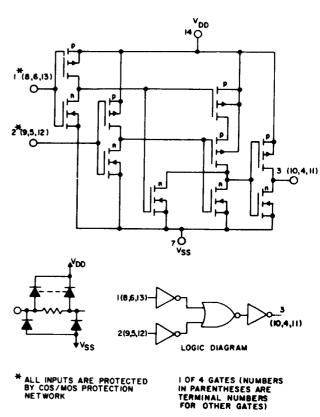

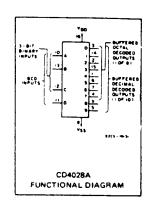

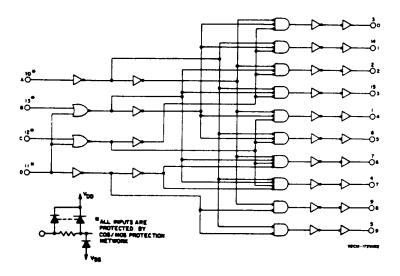

| 5.4        | CMOS Handling and Replacement                         | 5-2          |

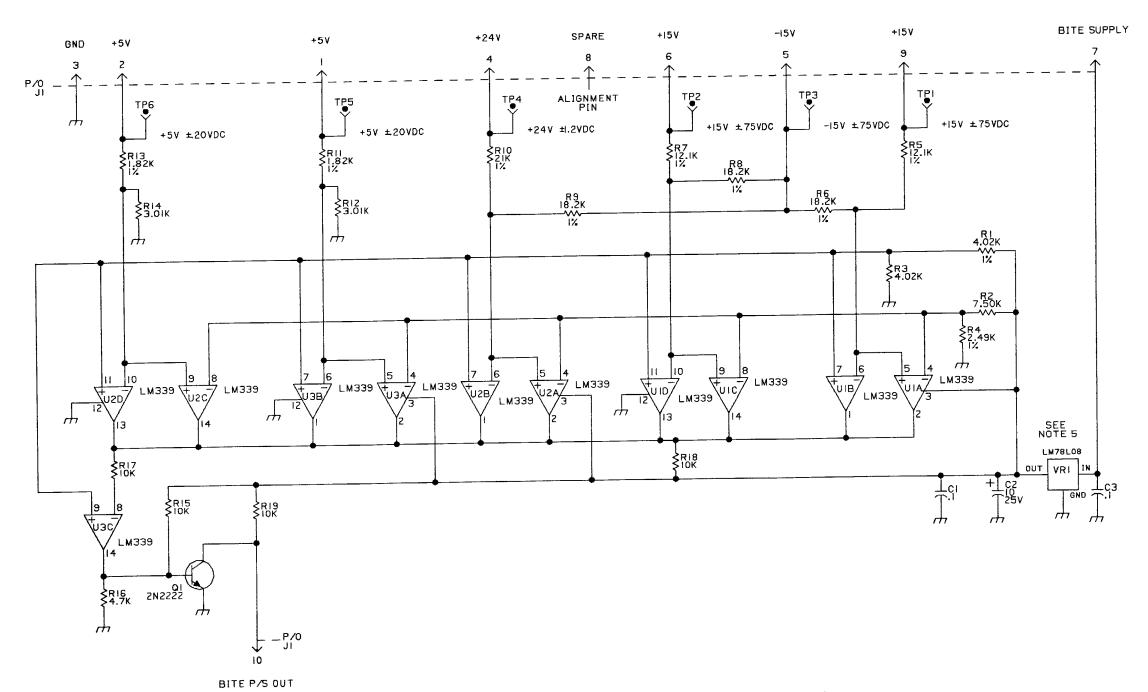

| 5.5        | Built-In Test Equipment (BITE) Self-Diagnostics       | 5- <b>2</b>  |

| 5.5.1      | Continuous Self-Test Monitoring                       | 5-5          |

| 5.5.2      | Self-Diagnostic Operation                             | 5-5          |

| 5.5.2.1    | Lamp Test                                             | 5-5          |

| 5.5.2.2    | ROM Test (Assembly A14)                               | 5-5          |

| 5.5.2.3    | RAM Test (Assembly A14)                               | 5-5          |

| 5.5.2.4    | I/O Port Tests                                        | 5-5          |

| 5.5.2.5    | Serial Data Test                                      | 5-6          |

| 5.5.2.6    | Reference Generator Test (Assembly A12)               | 5-6          |

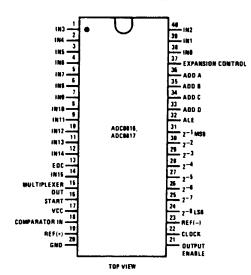

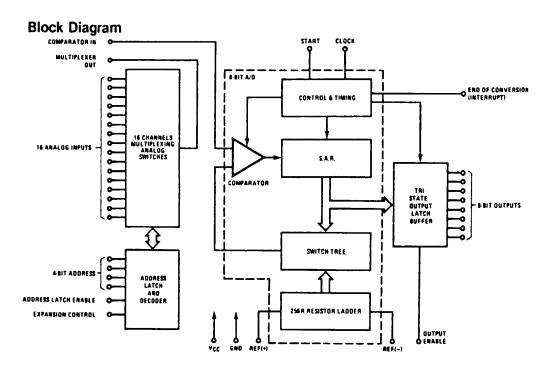

| 5.5.2.7    | A/D Converter Tests                                   | 5-6          |

| 5.5.2.8    | Phase Locked Loop (PLL) Tests                         | 5-6          |

| 5.5.2.9    | Input Filter Test (Assembly A1)                       | 5-6          |

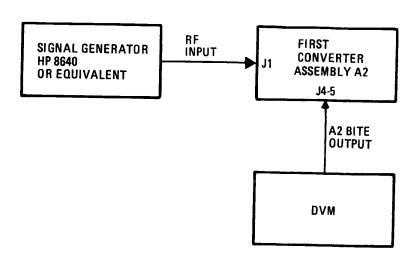

| 5.5.2.10   | First Converter Test (Assembly A2)                    | 5-7          |

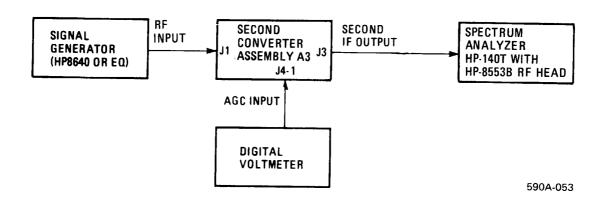

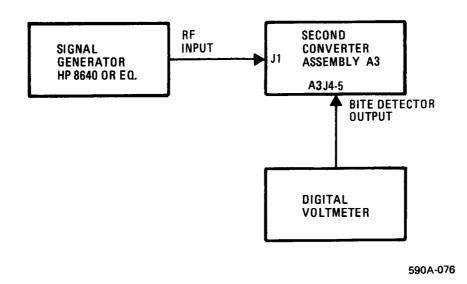

| 5.5.2.11   | Second Converter Test (Assembly A3)                   | 5-7          |

| 5.5.2.12   | IF Filter Test (Assembly A4)                          | 5 <i>7</i>   |

| 5.5.2.13   | IF Audio Test (Assembly A5)                           | 5-8          |

| 5.5.2.14   | ISB IF/Audio Test (Assembly A18)                      | 5-9          |

| 5.5.2.15   | LCU Test (Optional Assembly A17, If Installed)        | 5-9          |

| 5.5.3      | Self-Diagnostics Sequence Summary                     | 5-10         |

| 5.5<br>5.6 | Supplement to Built-In Test Capabilities              | 5-10         |

| 5.6.1      |                                                       |              |

|            | Abnormal Front Panel Displays                         | 5-13         |

| 5.6.2      | Abnormal Operation, But With No Built-In Test Failure | 5-13         |

| 5.6.3      | Fault Indications With Multiple Causes                | 5-14         |

| 5.7        | Receiver Performance Test Procedures                  | 5-15         |

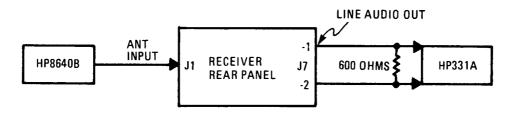

| 5.7.1      | Sensitivity Test                                      | 5-16         |

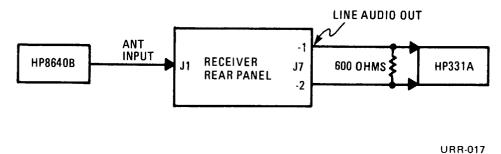

| 5.7.2      | Audio Output Level and Distortion Test                | 5-17         |

| 5.7.2.1    | Line Output Check                                     | 5-18         |

| 5.7.2.2    | Headphone Output Check                                | 5-1 <b>9</b> |

| 5.7.3      | AGC Range                                             | 5-1 <b>9</b> |

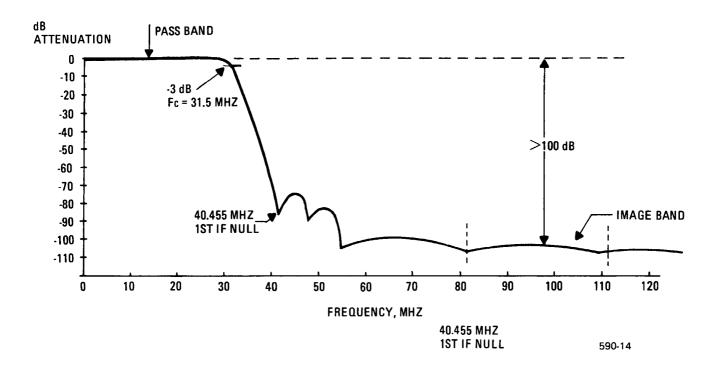

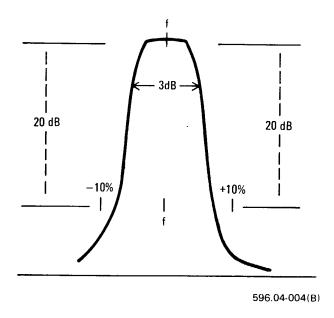

| 5.7.4      | IF Filter Selectivity                                 | 5-20         |

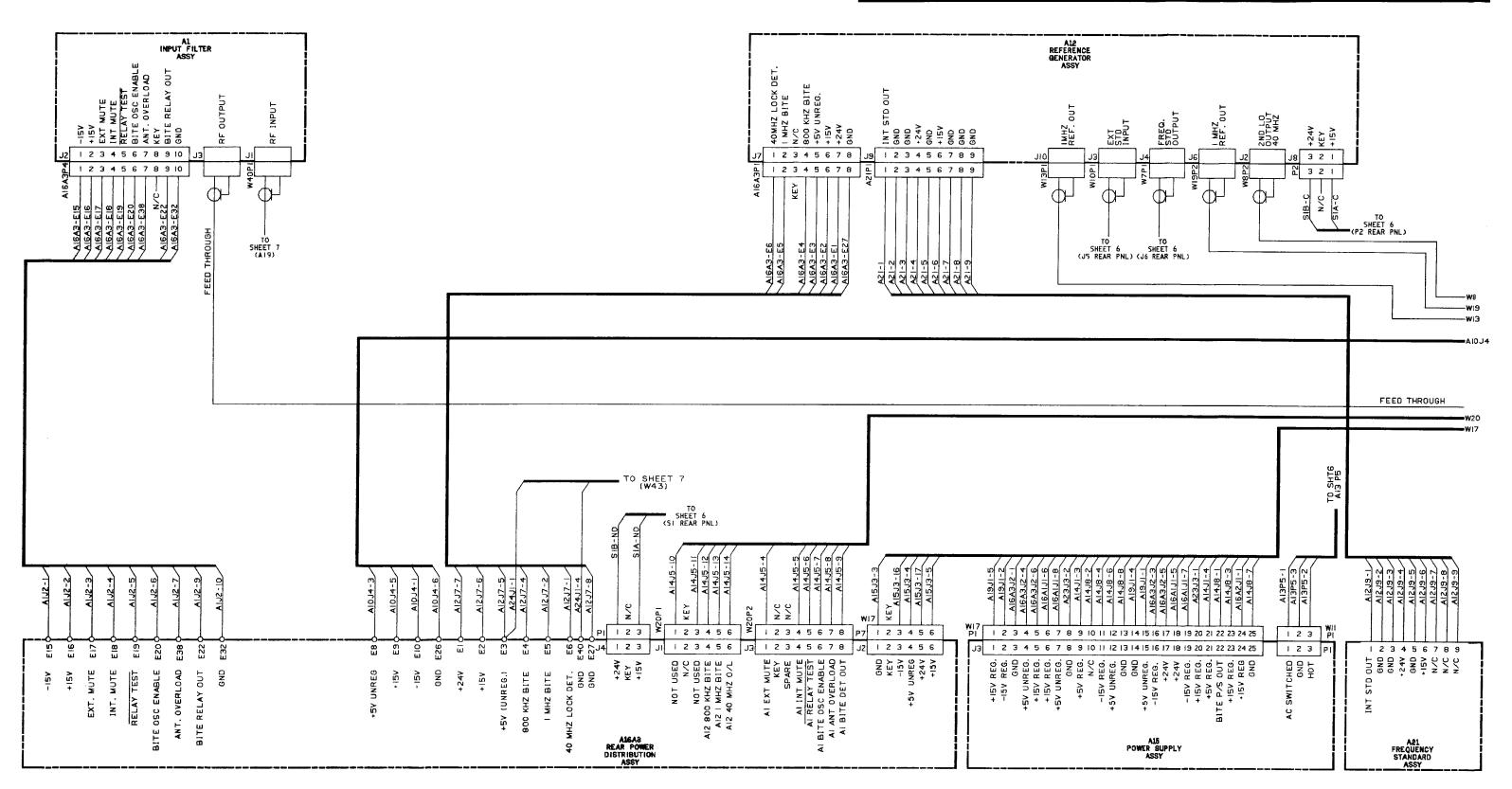

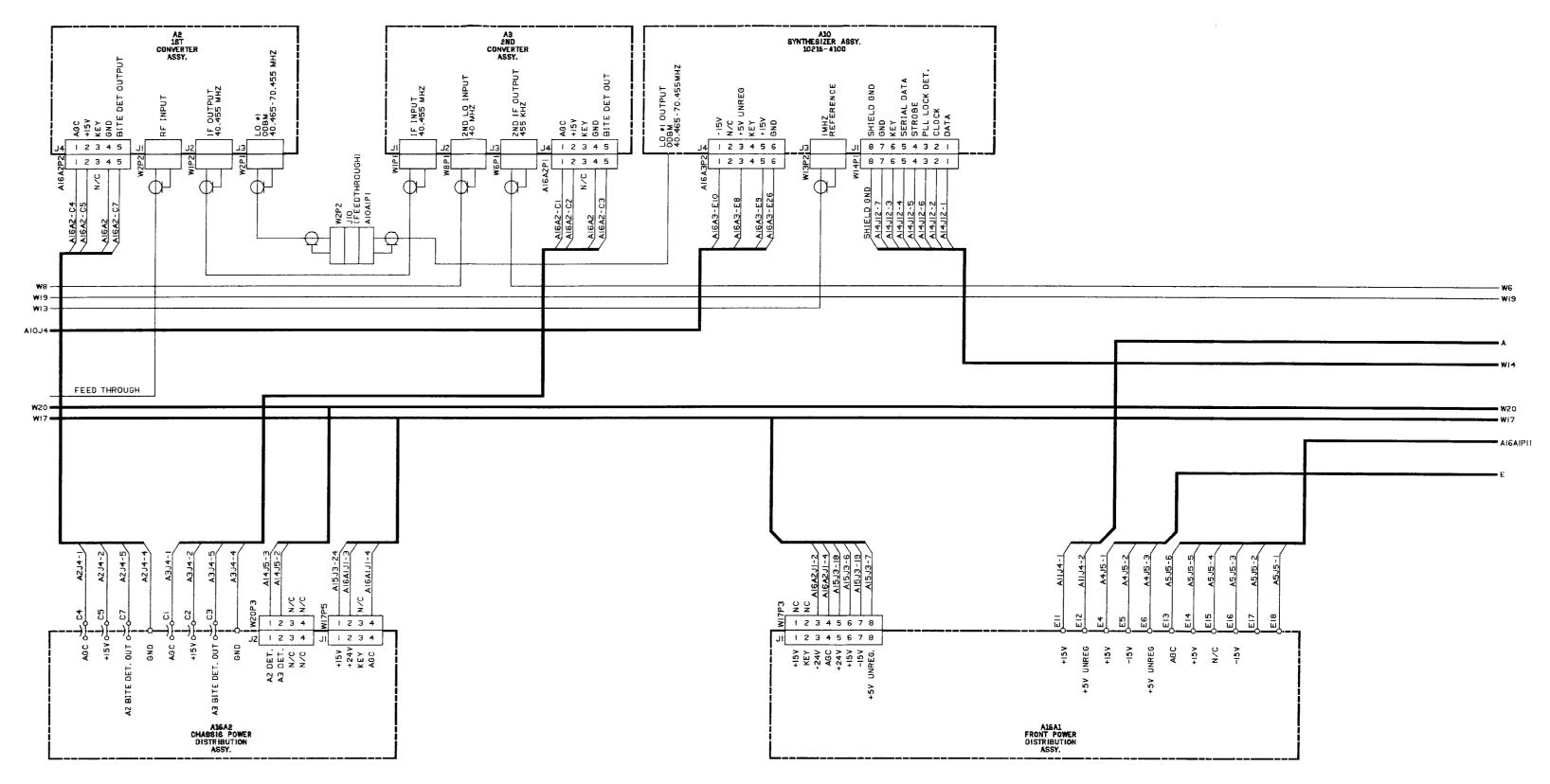

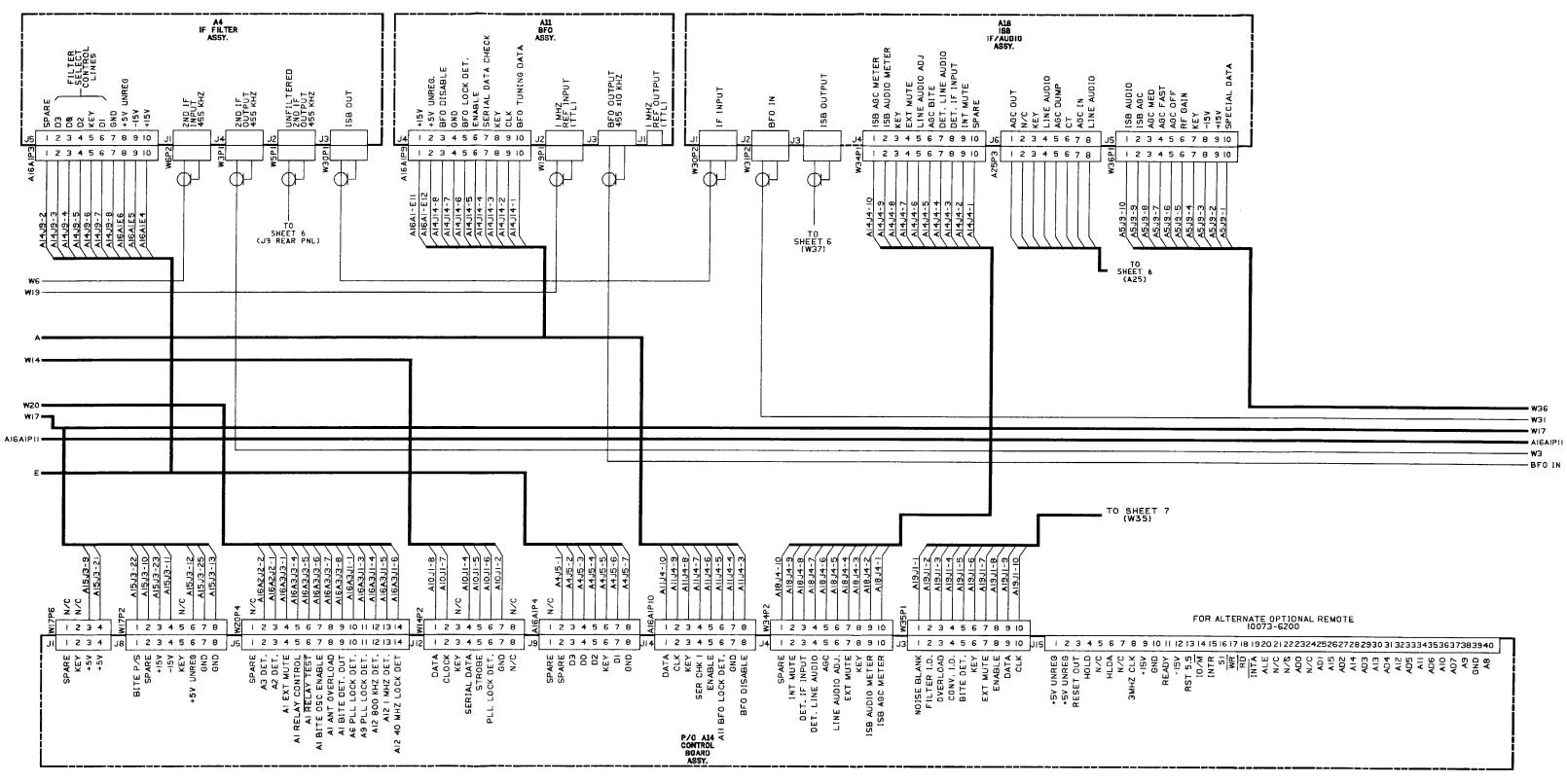

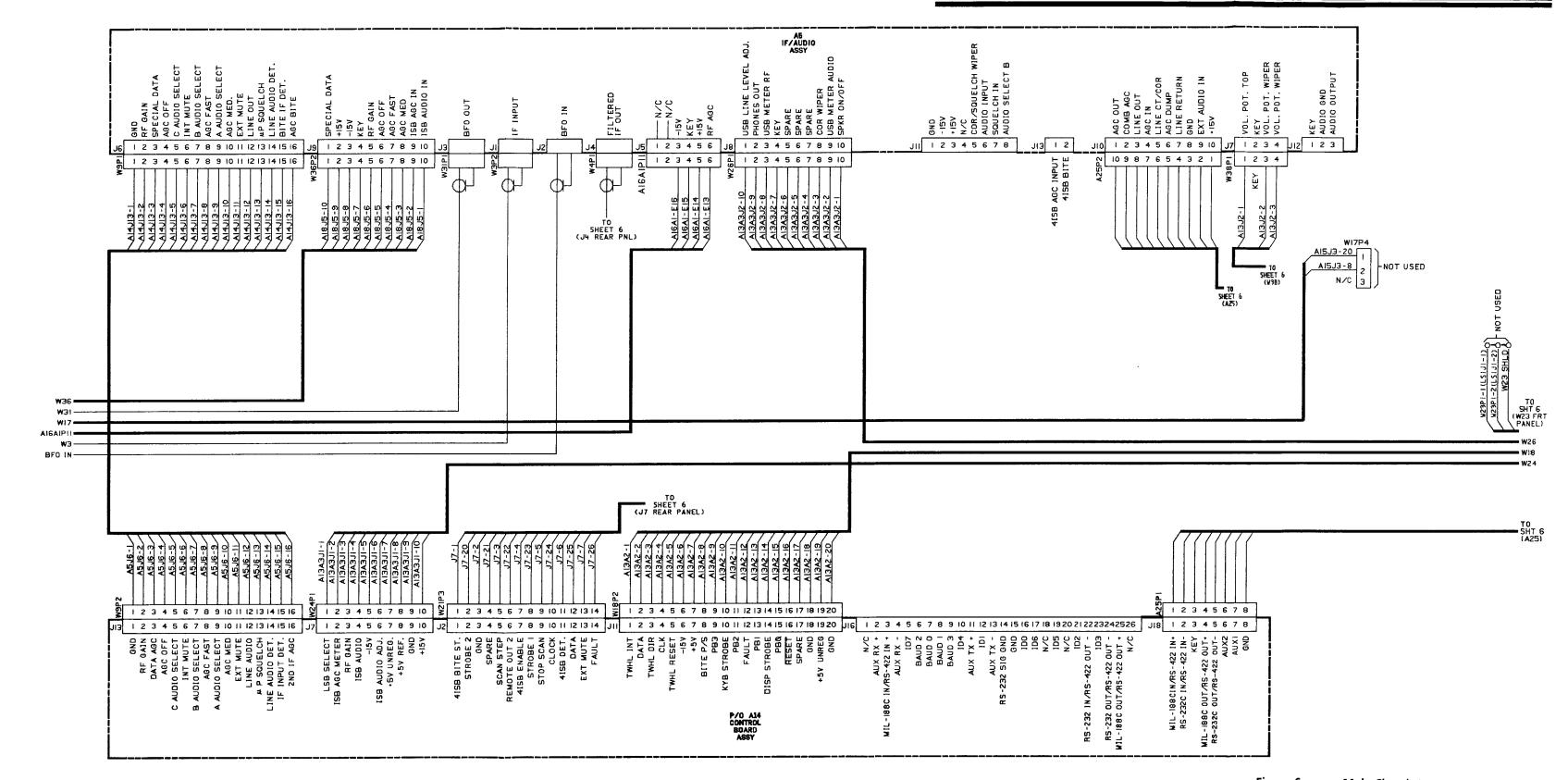

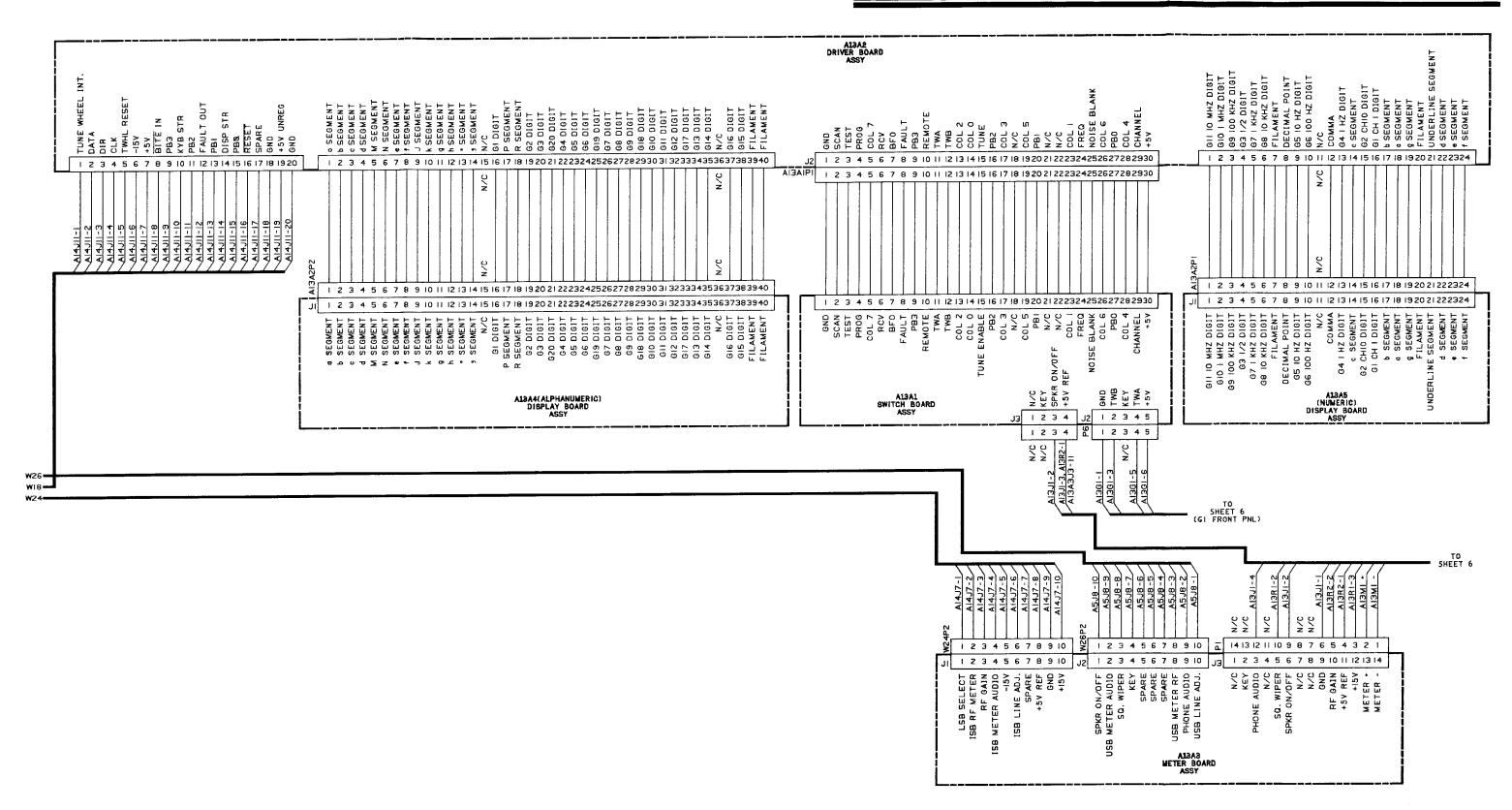

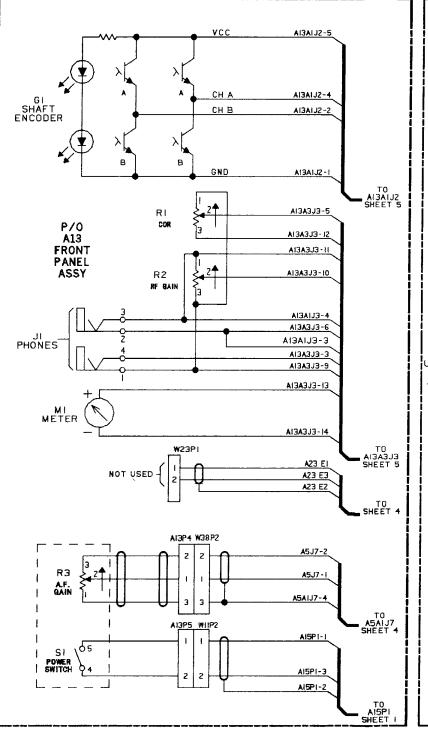

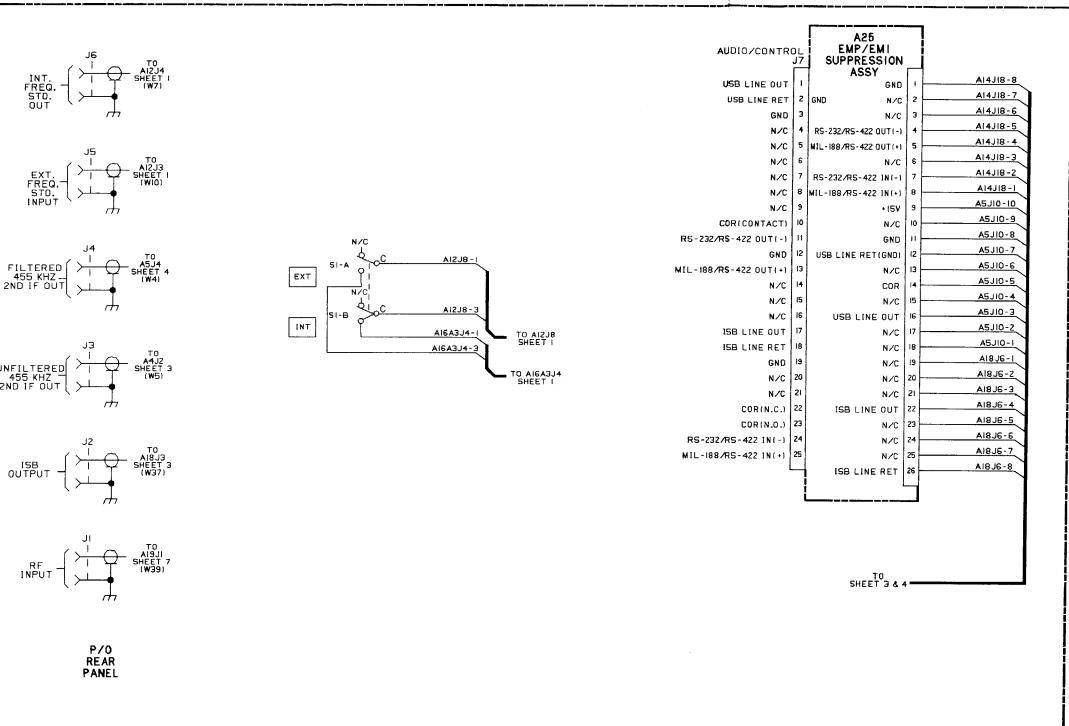

|            | MAIN CHASSIS INTERCONNECTION                          |              |

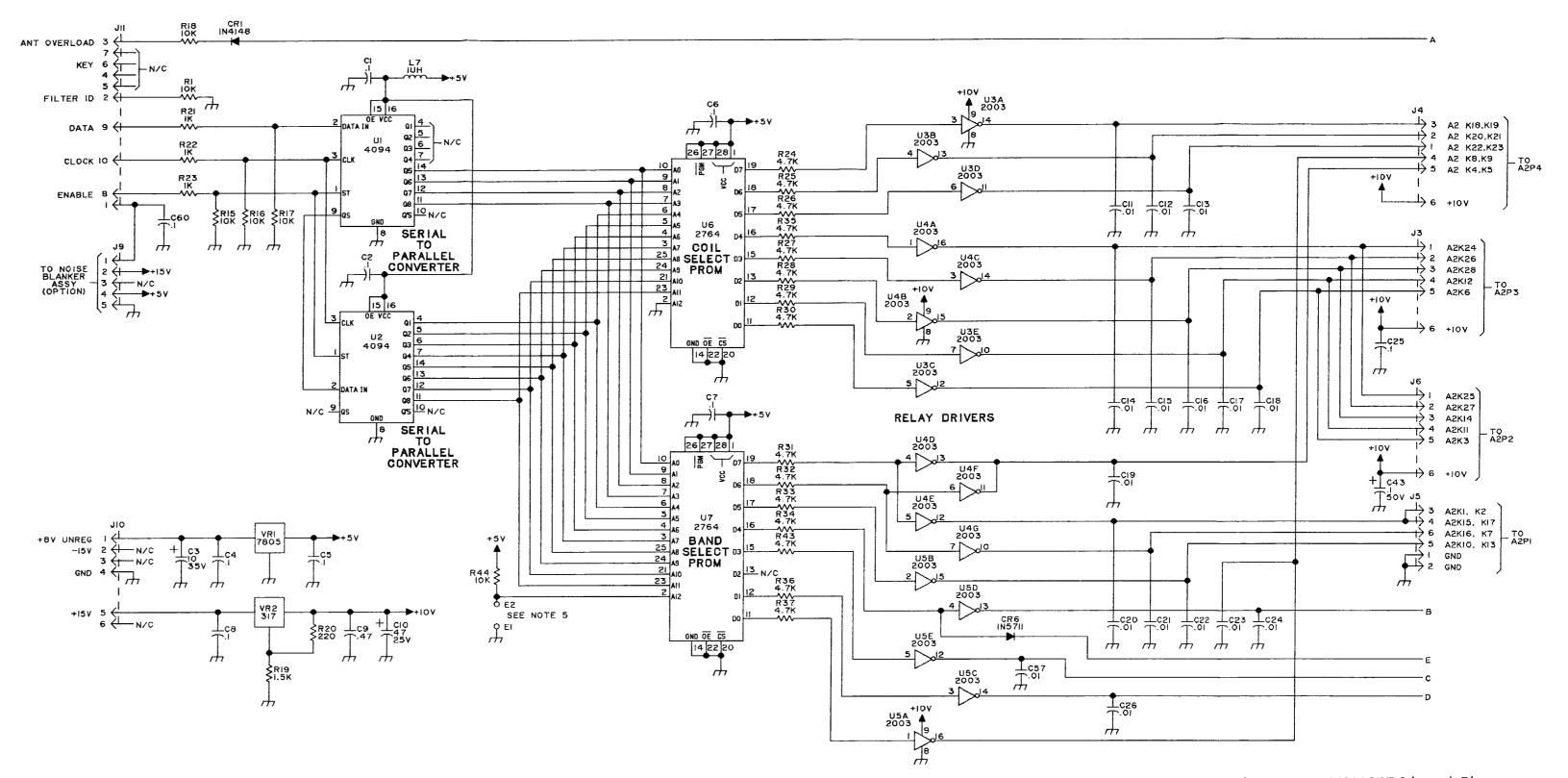

|            | A1 INPUT FILTER ASSEMBLY                              |              |

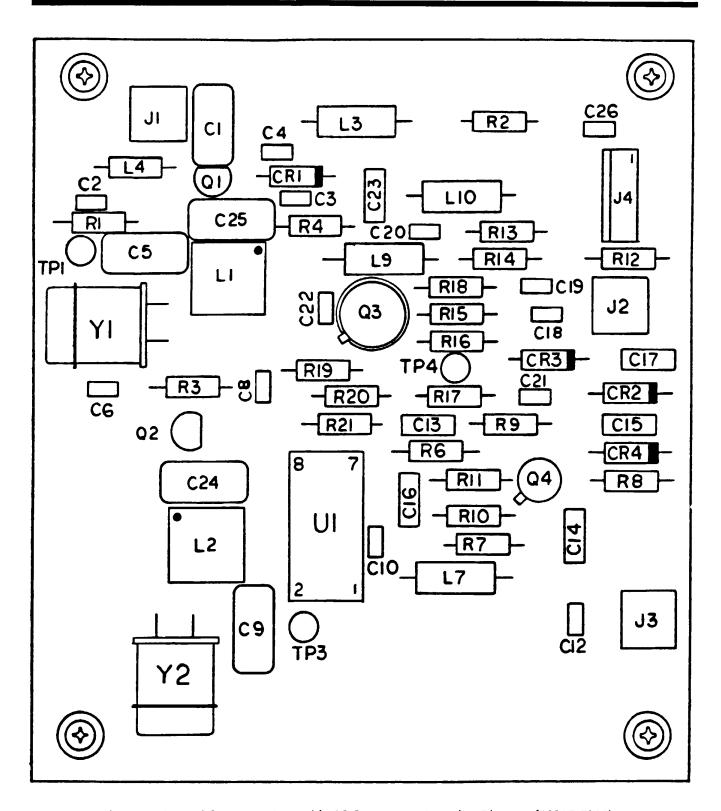

**A2 FIRST CONVERTER ASSEMBLY**

A3 SECOND CONVERTER ASSEMBLY

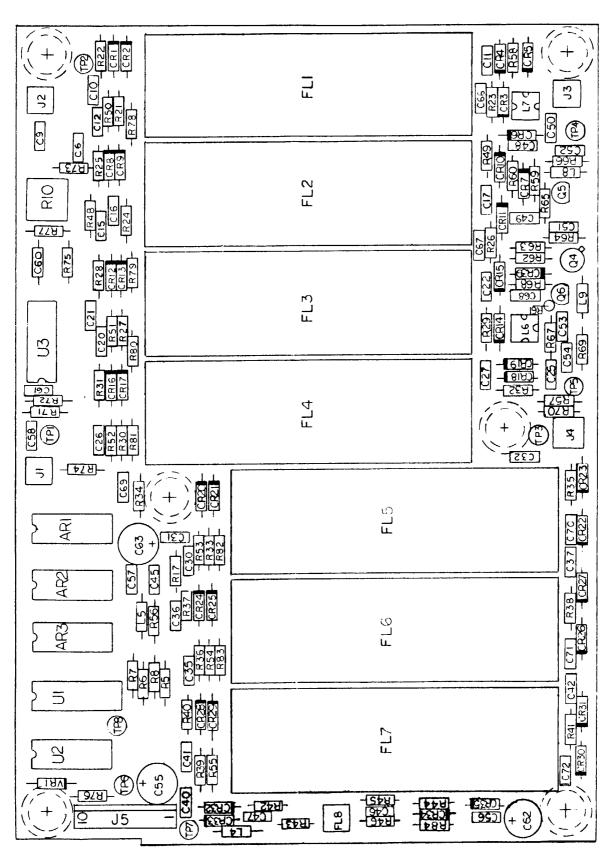

**A4 IF FILTER ASSEMBLY**

A5 IF/AUDIO PWB ASSEMBLY

#### **TABLE OF CONTENTS (Cont.)**

| Paragraph |                                      | Page |

|-----------|--------------------------------------|------|

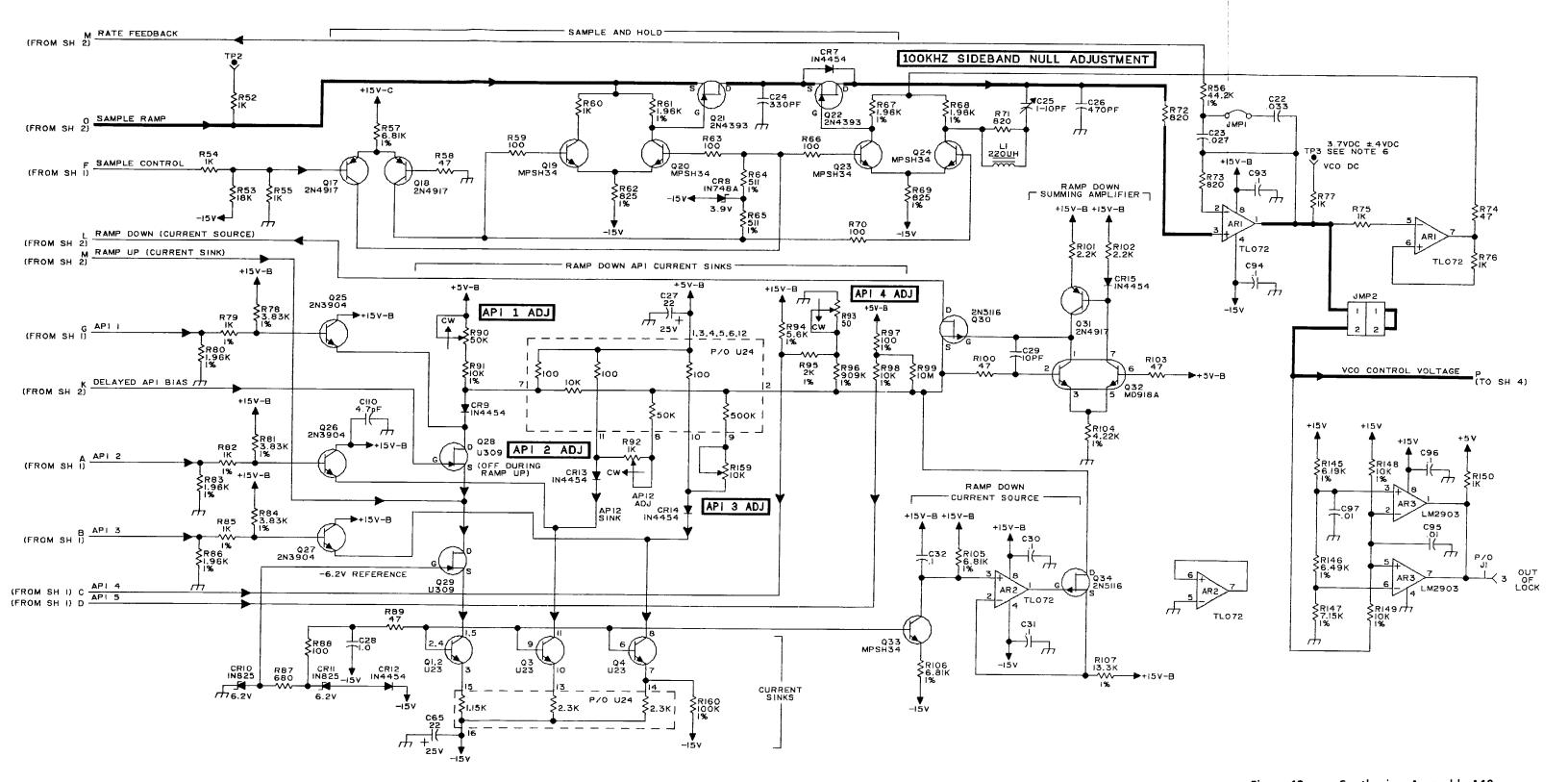

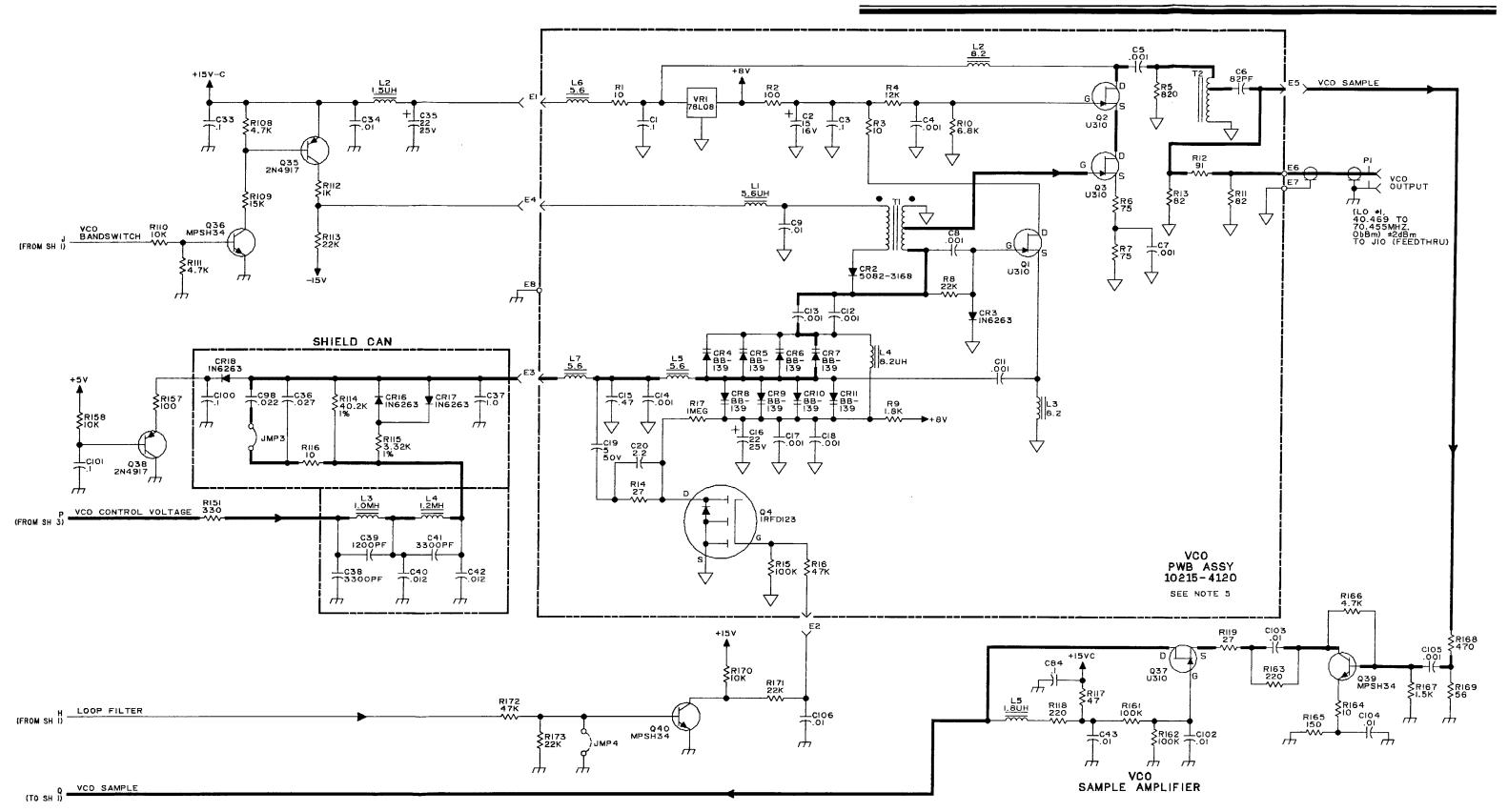

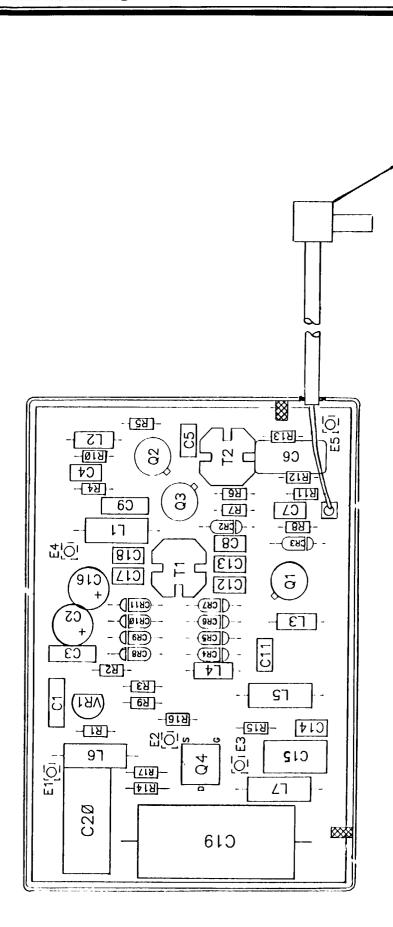

|           | A10 SYNTHESIZER ASSEMBLY             |      |

|           | A11 BFO ASSEMBLY                     |      |

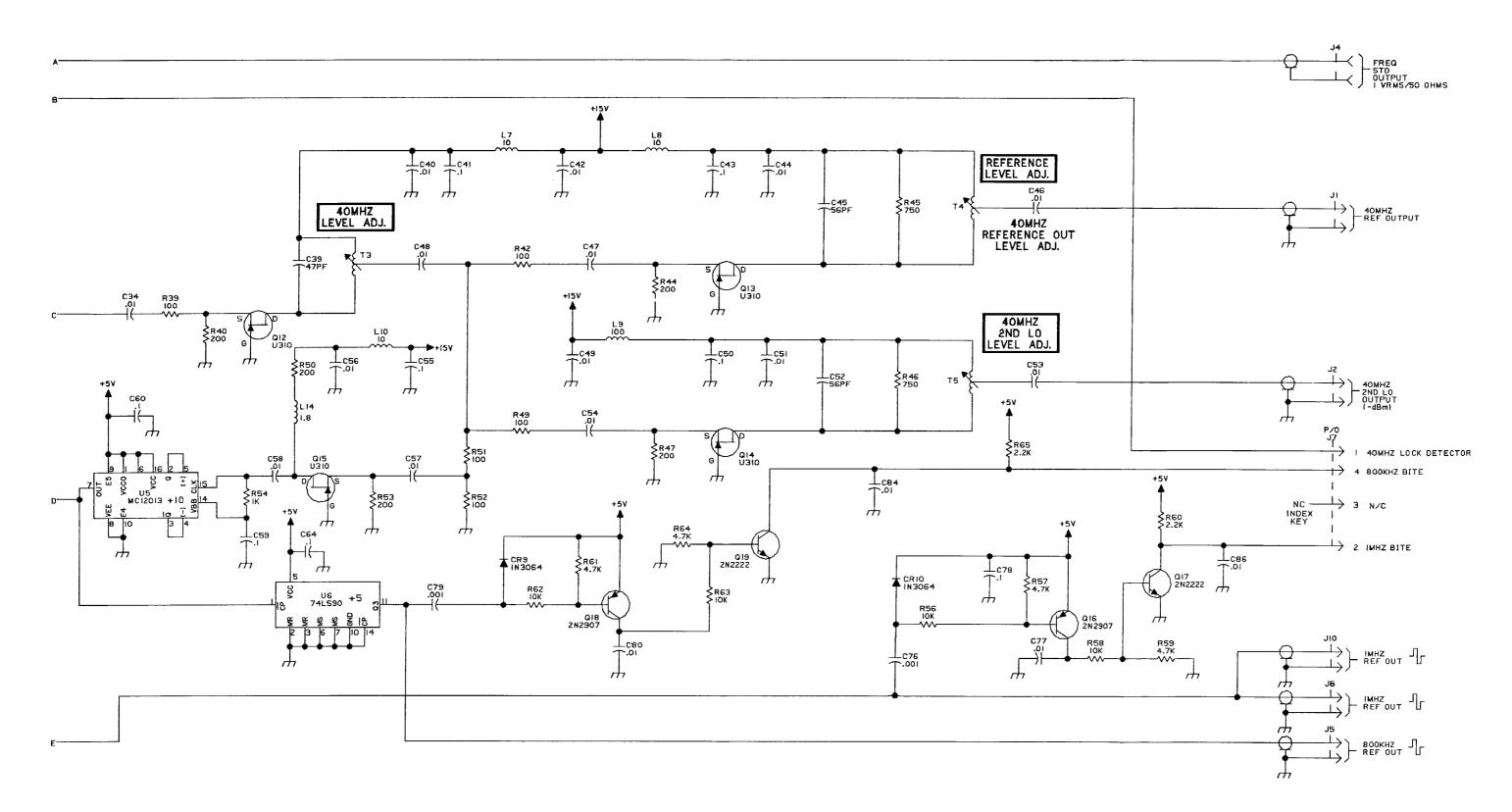

|           | A12/A21 REFERENCE GENERATOR ASSEMBLY |      |

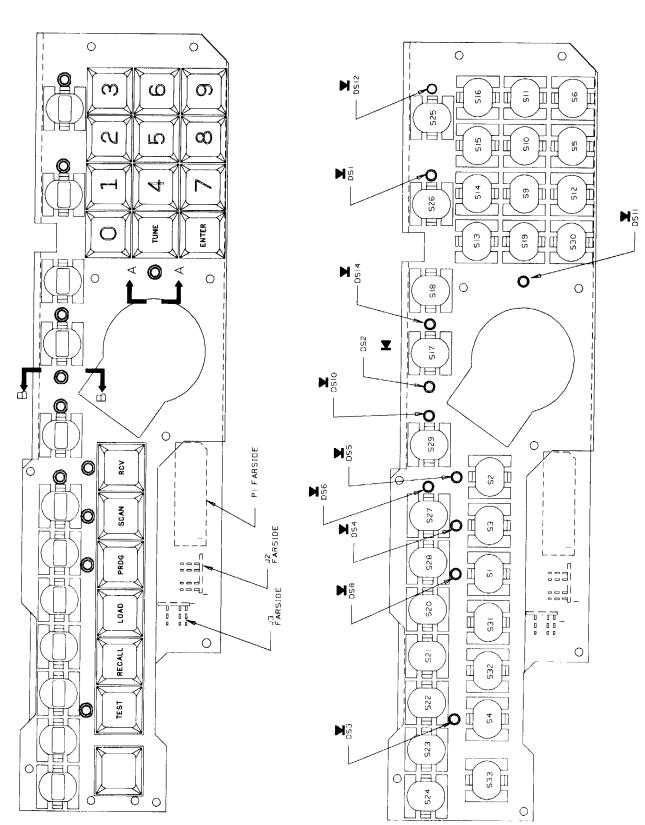

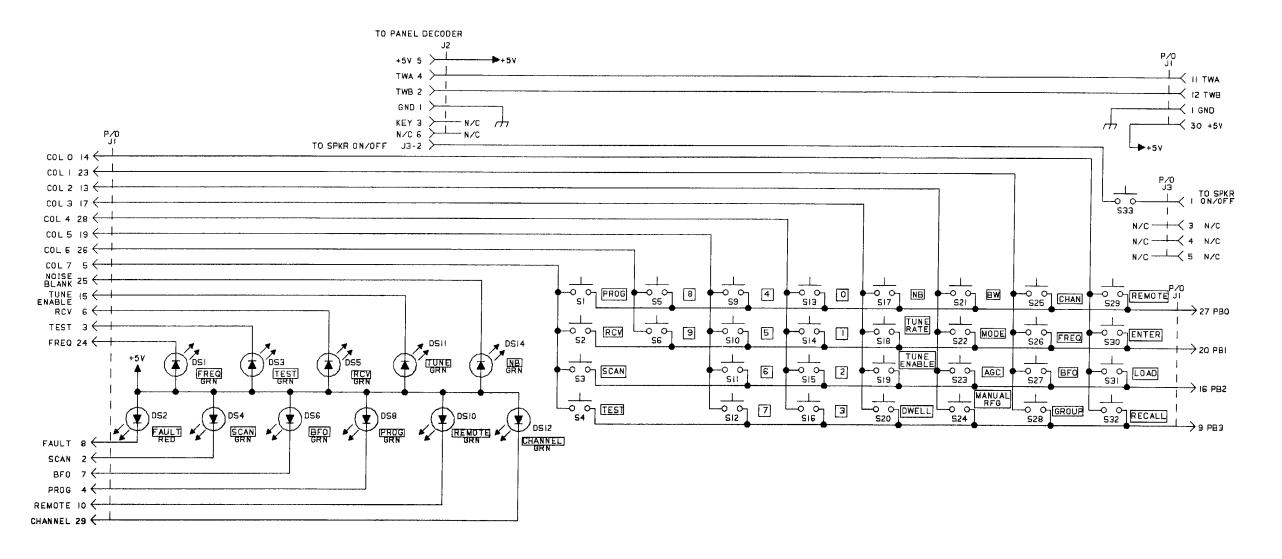

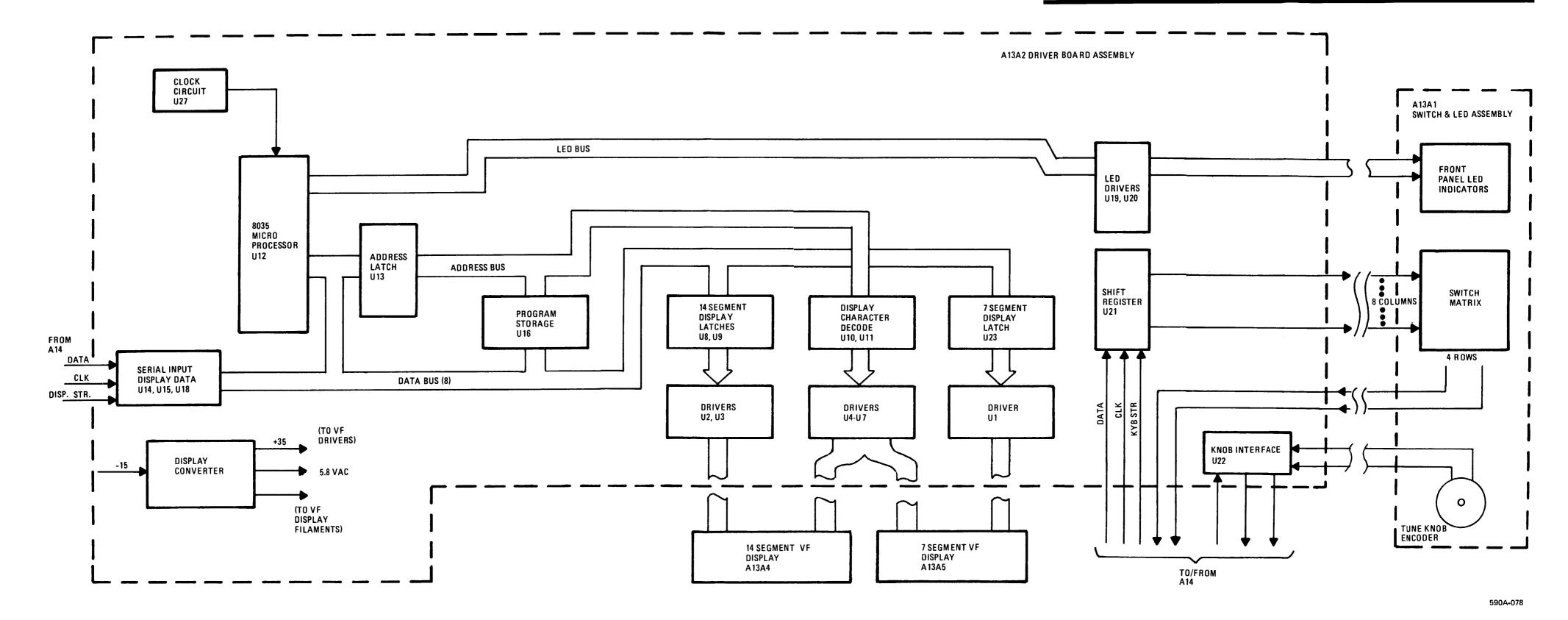

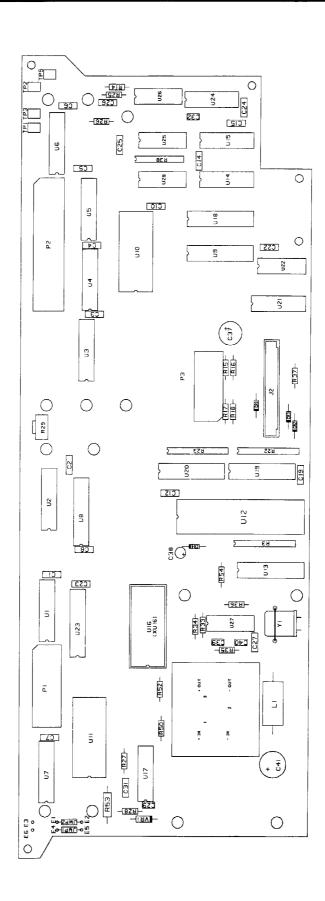

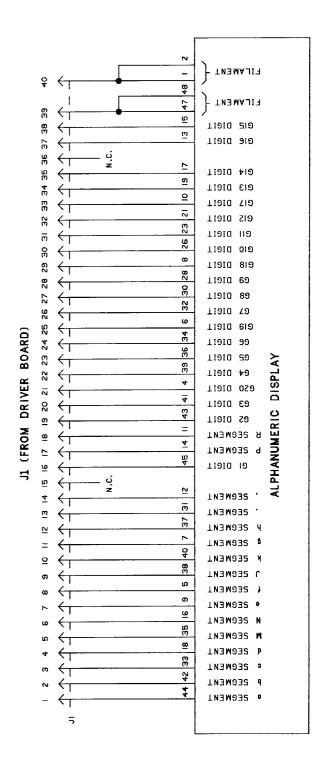

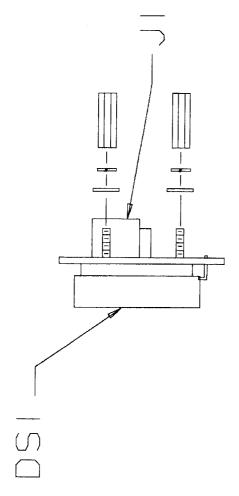

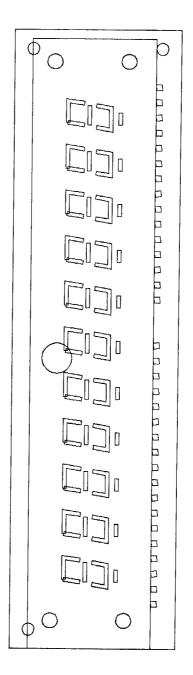

|           | A13 FRONT PANEL ASSEMBLY             |      |

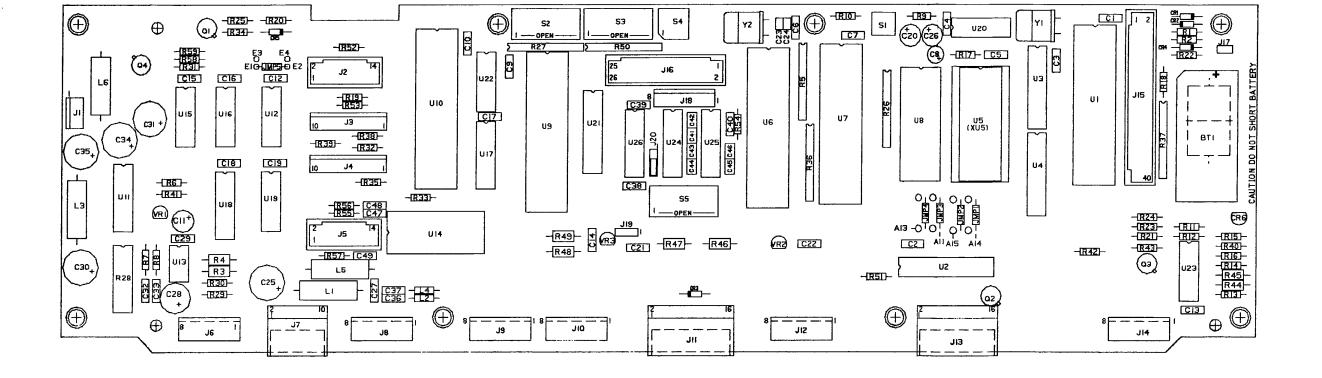

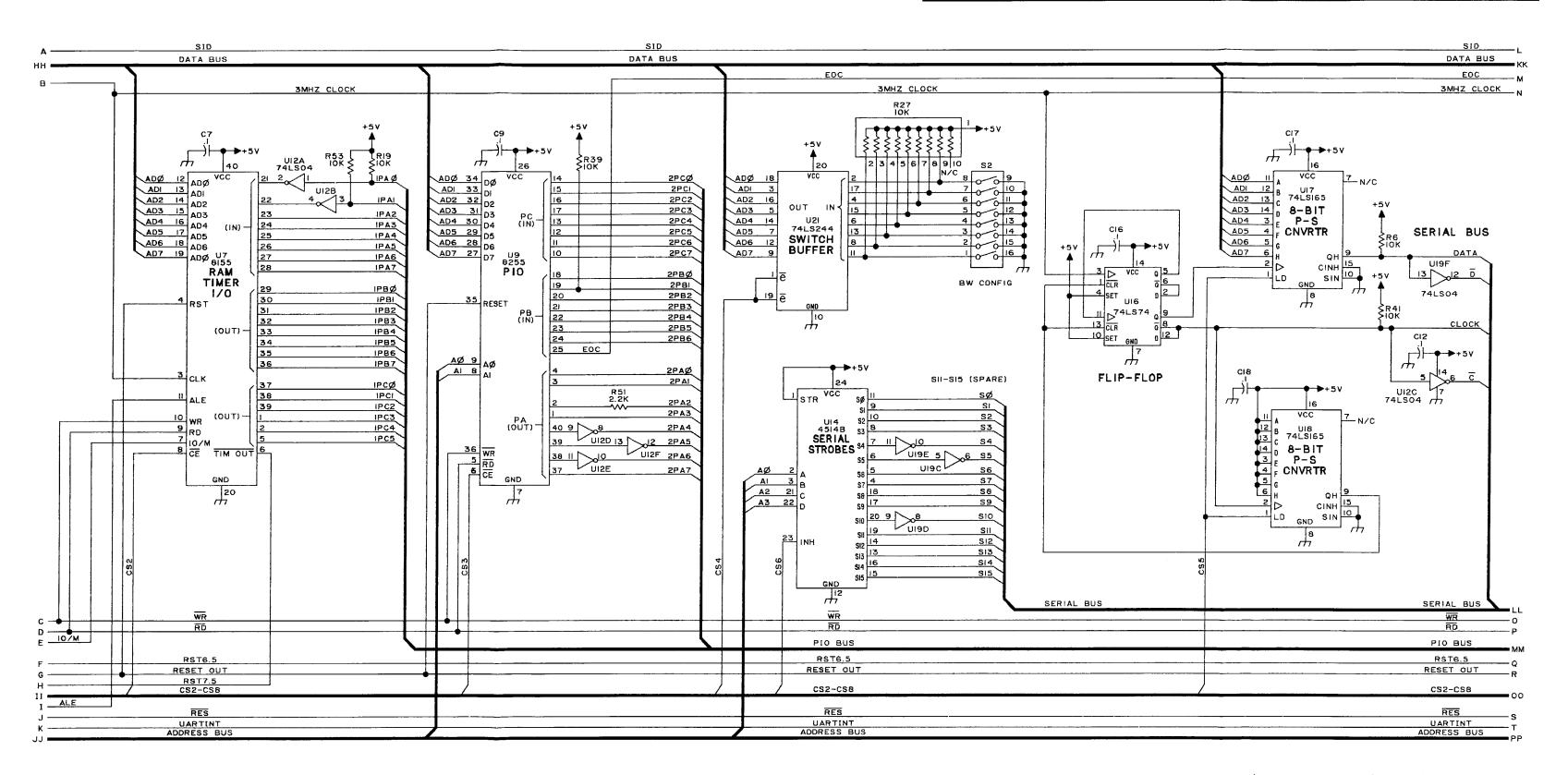

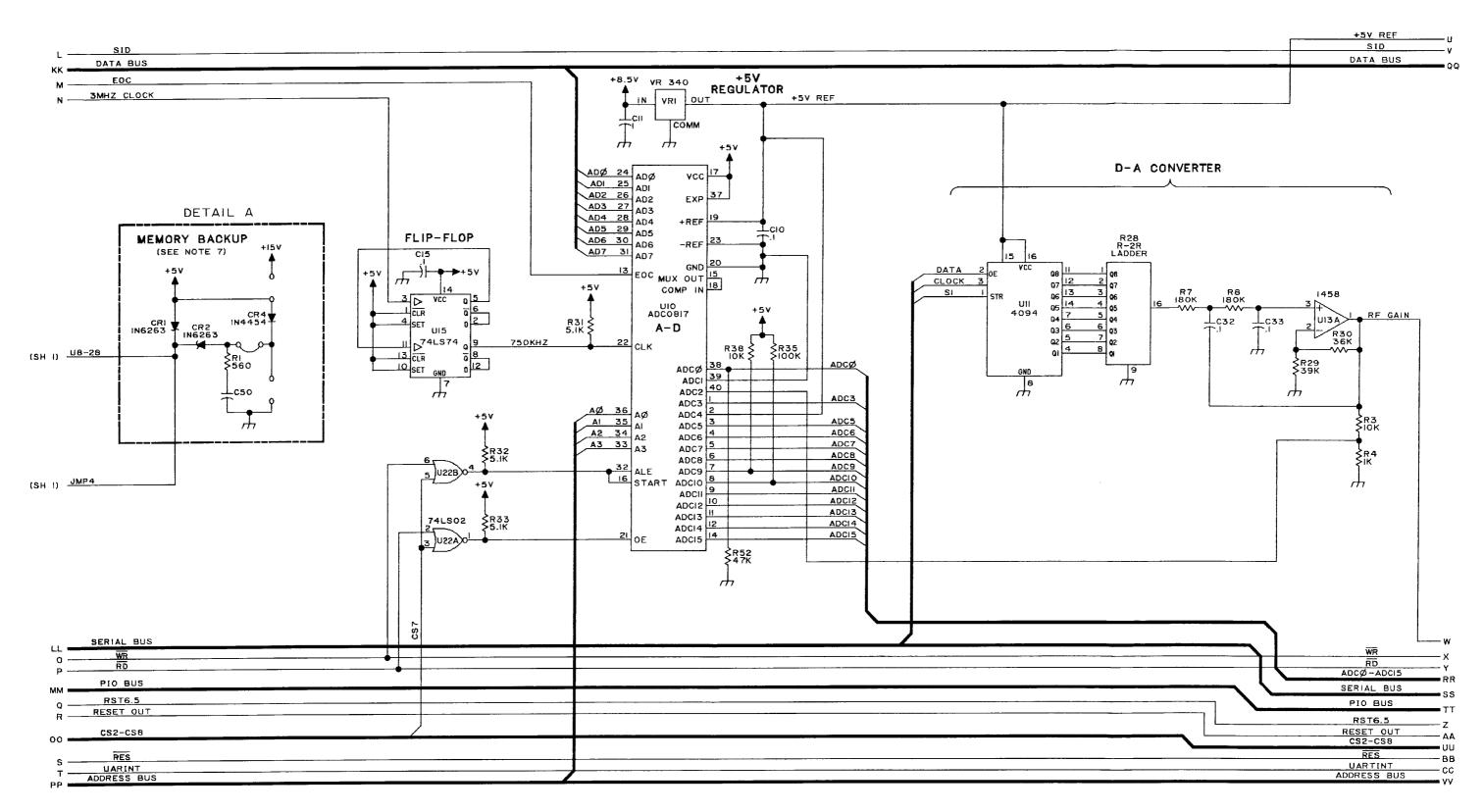

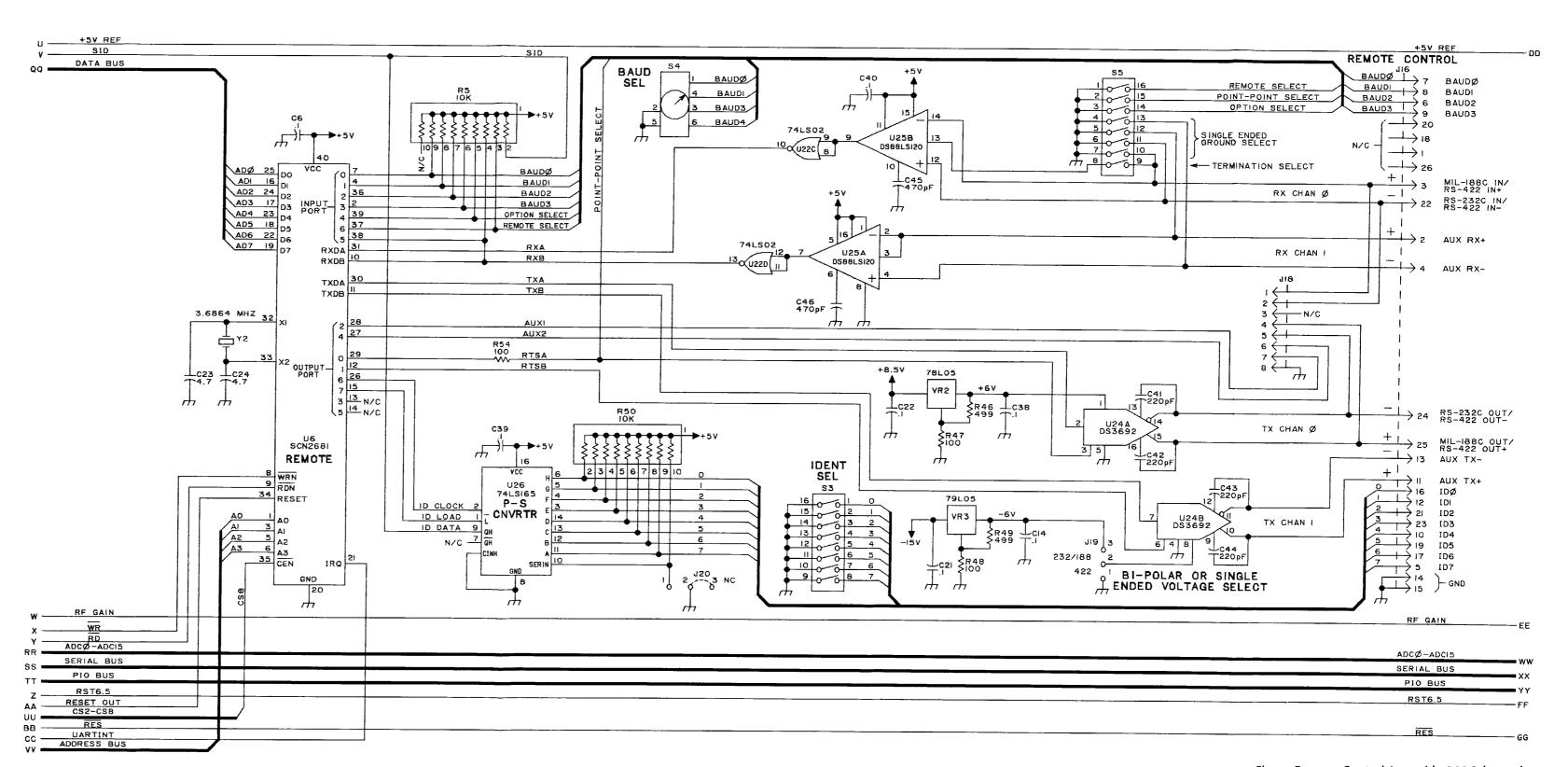

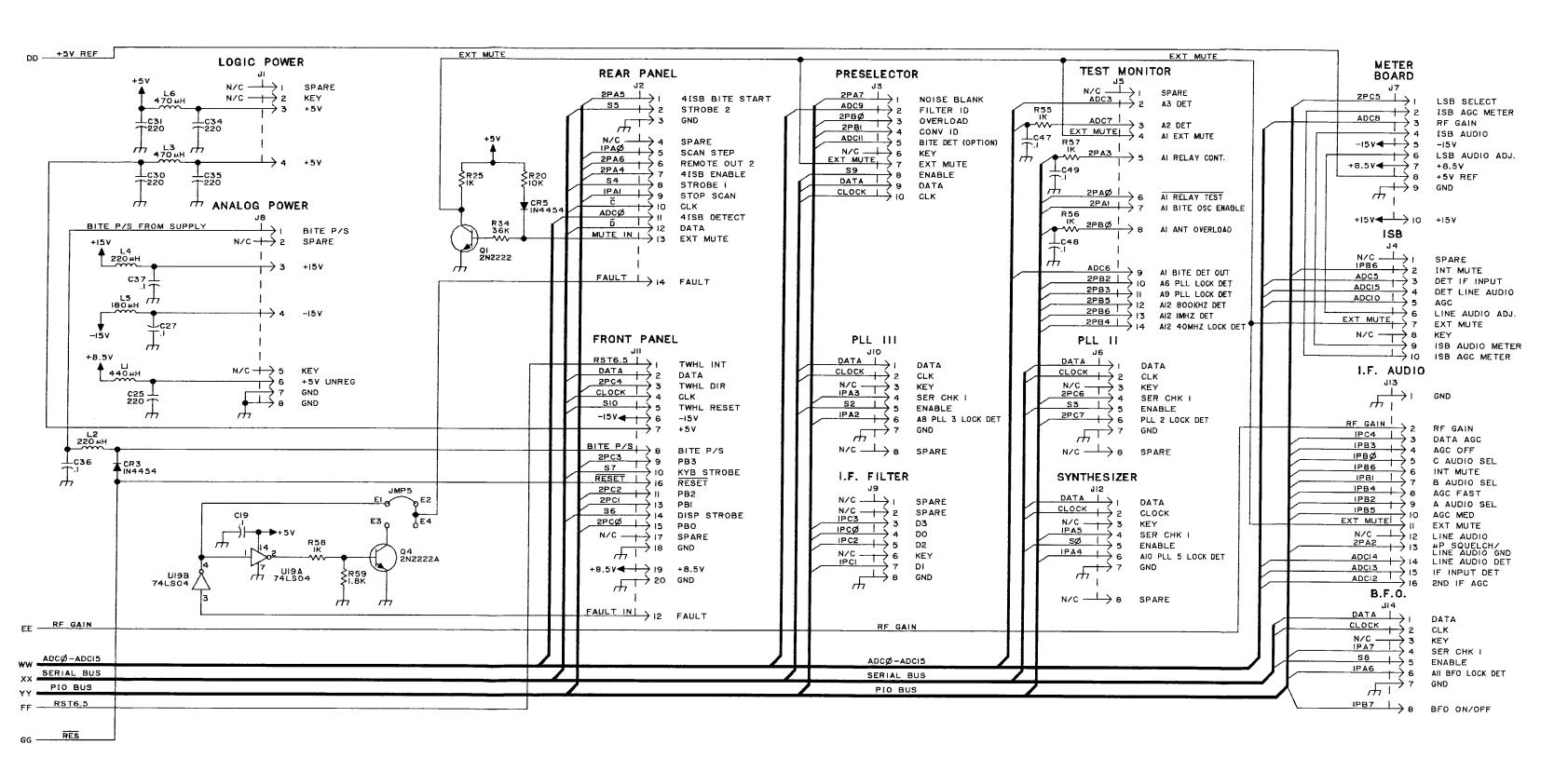

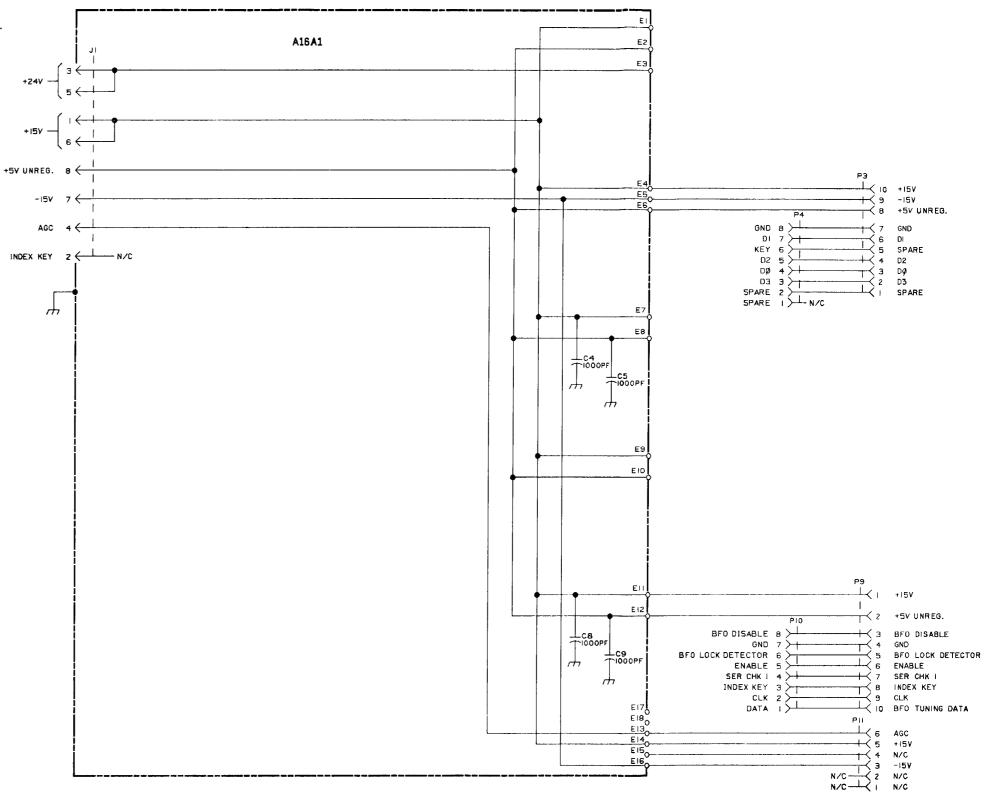

|           | A14 CONTROL BOARD ASSEMBLY           |      |

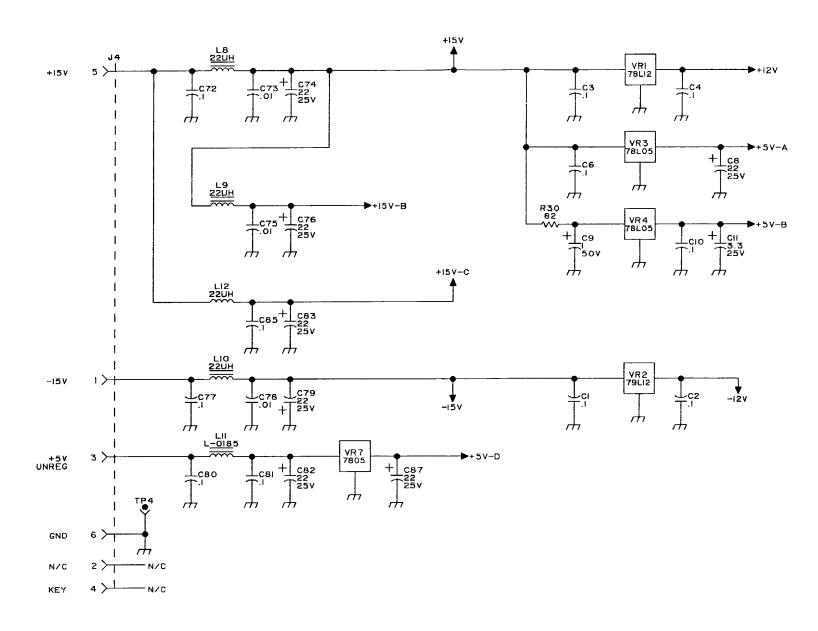

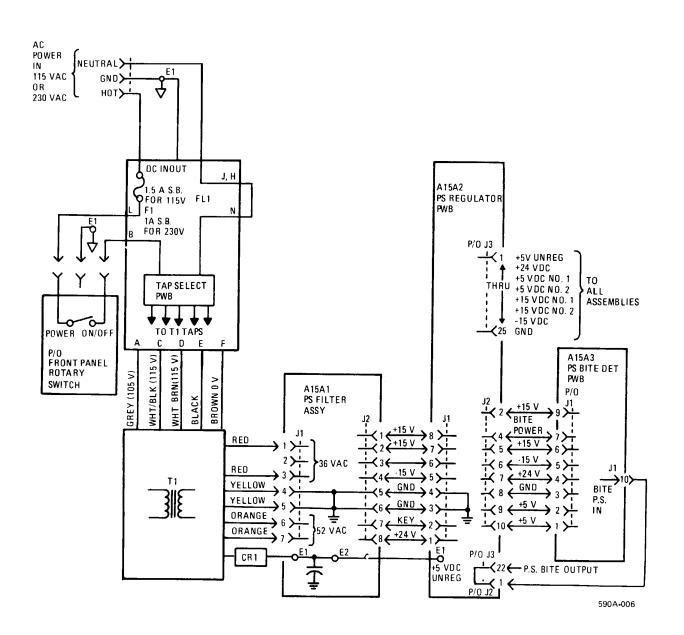

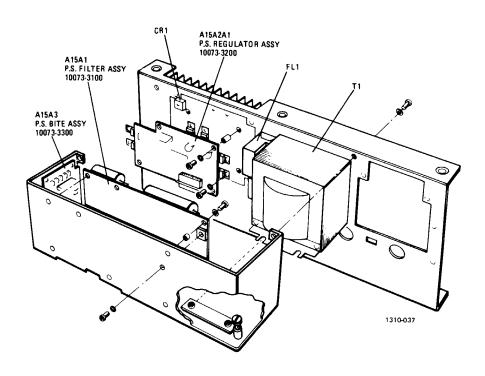

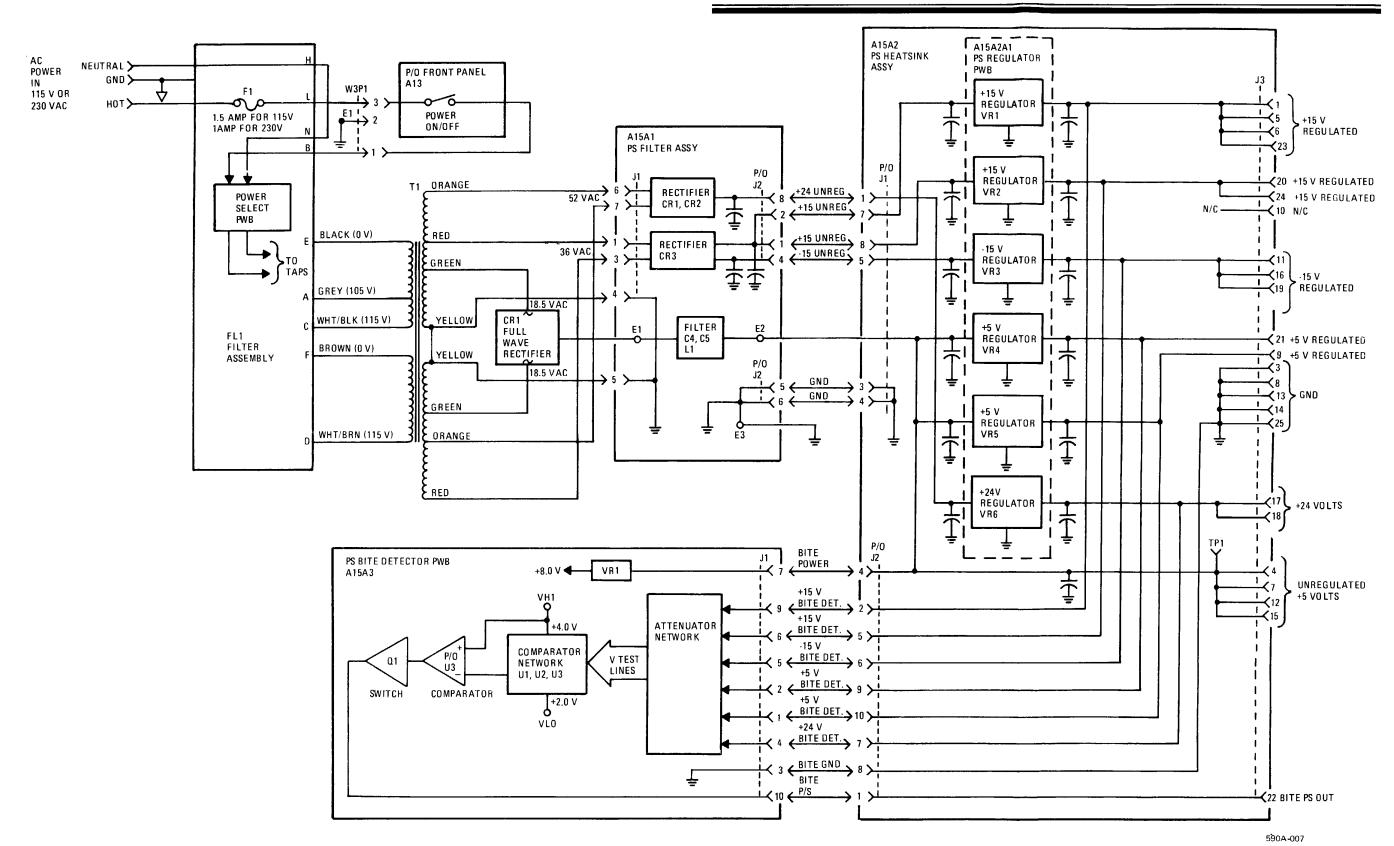

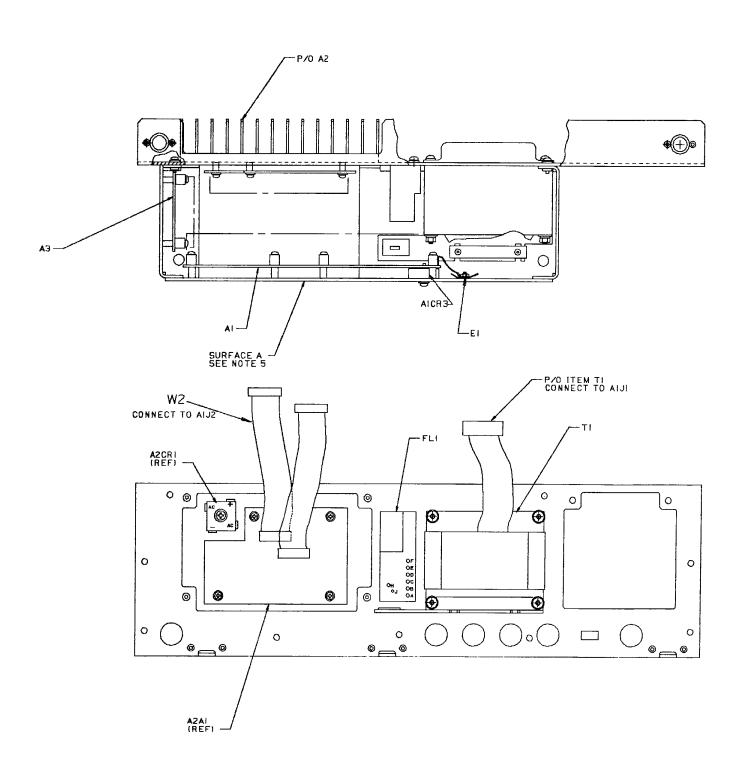

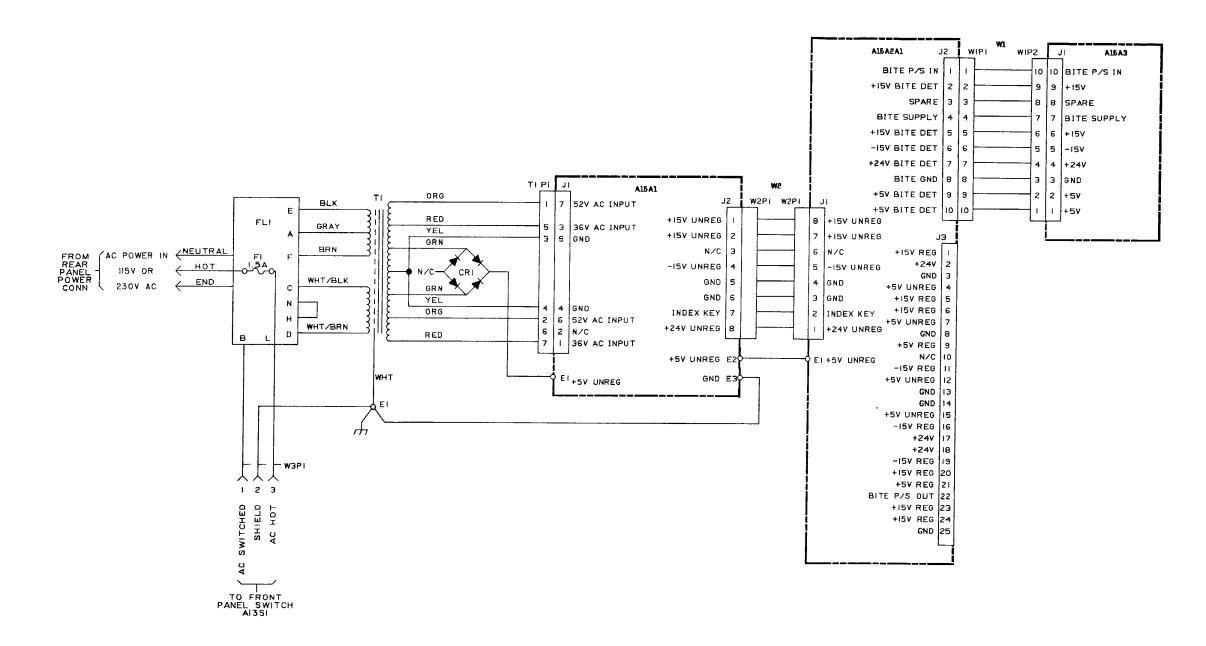

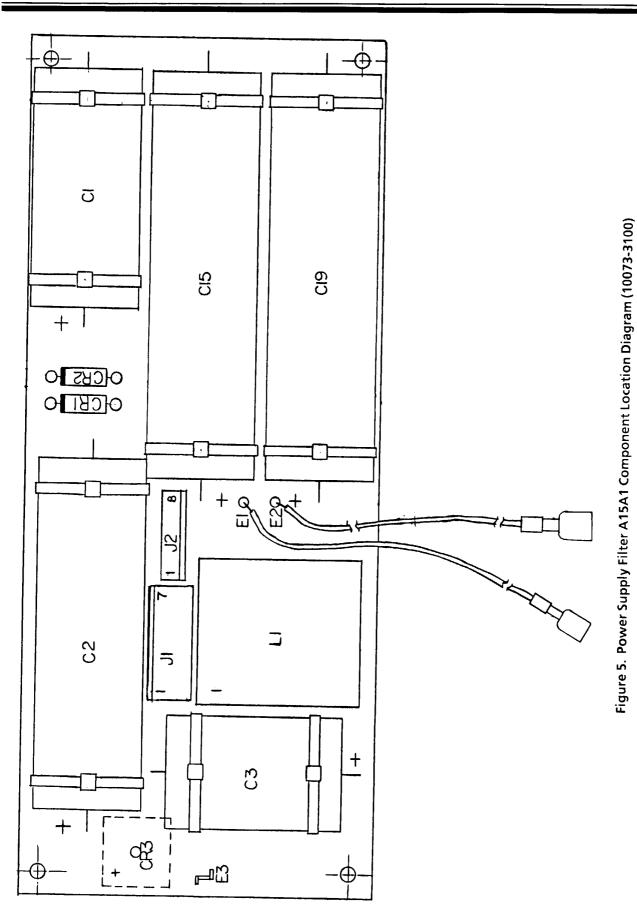

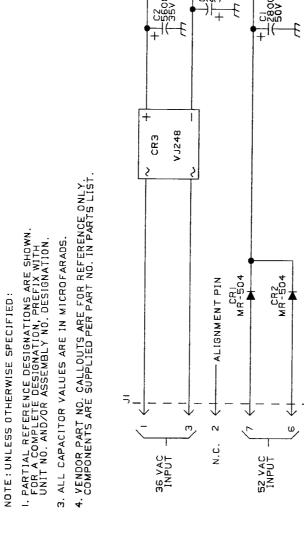

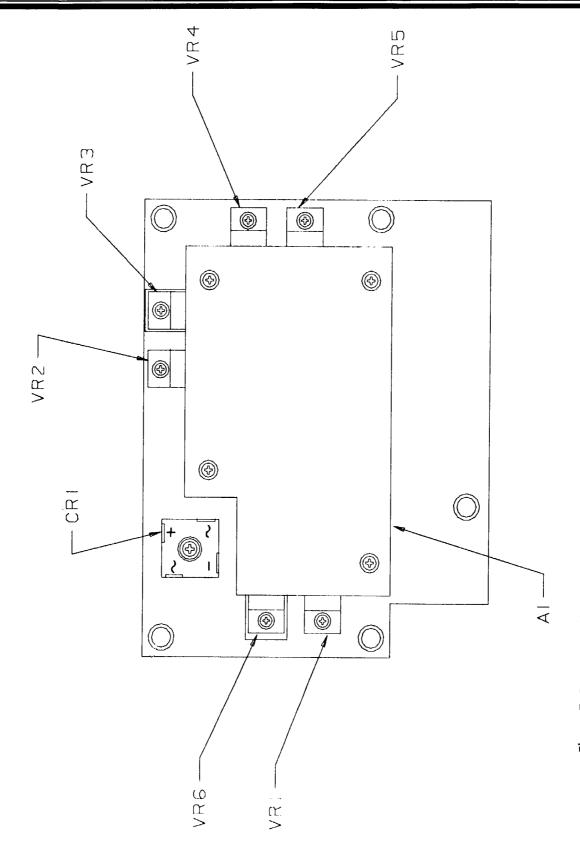

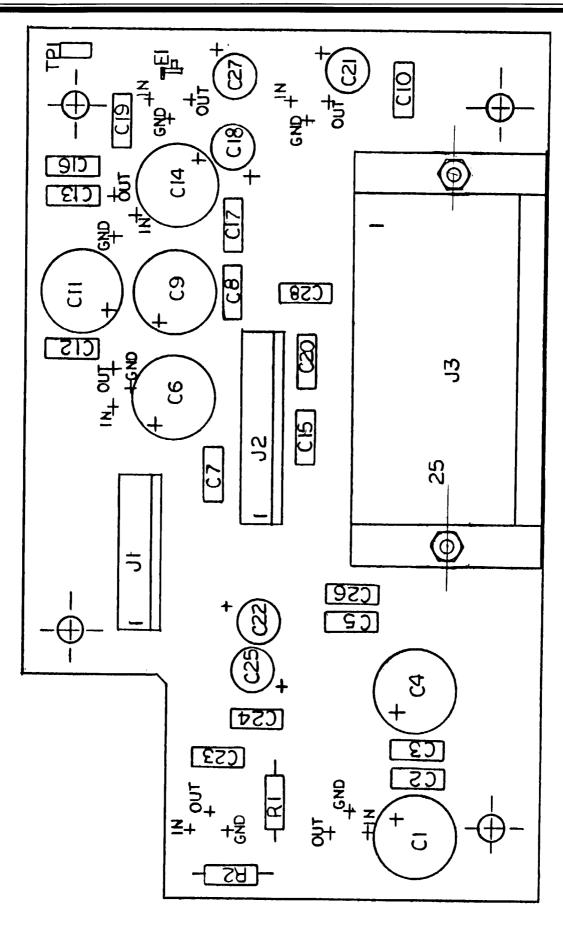

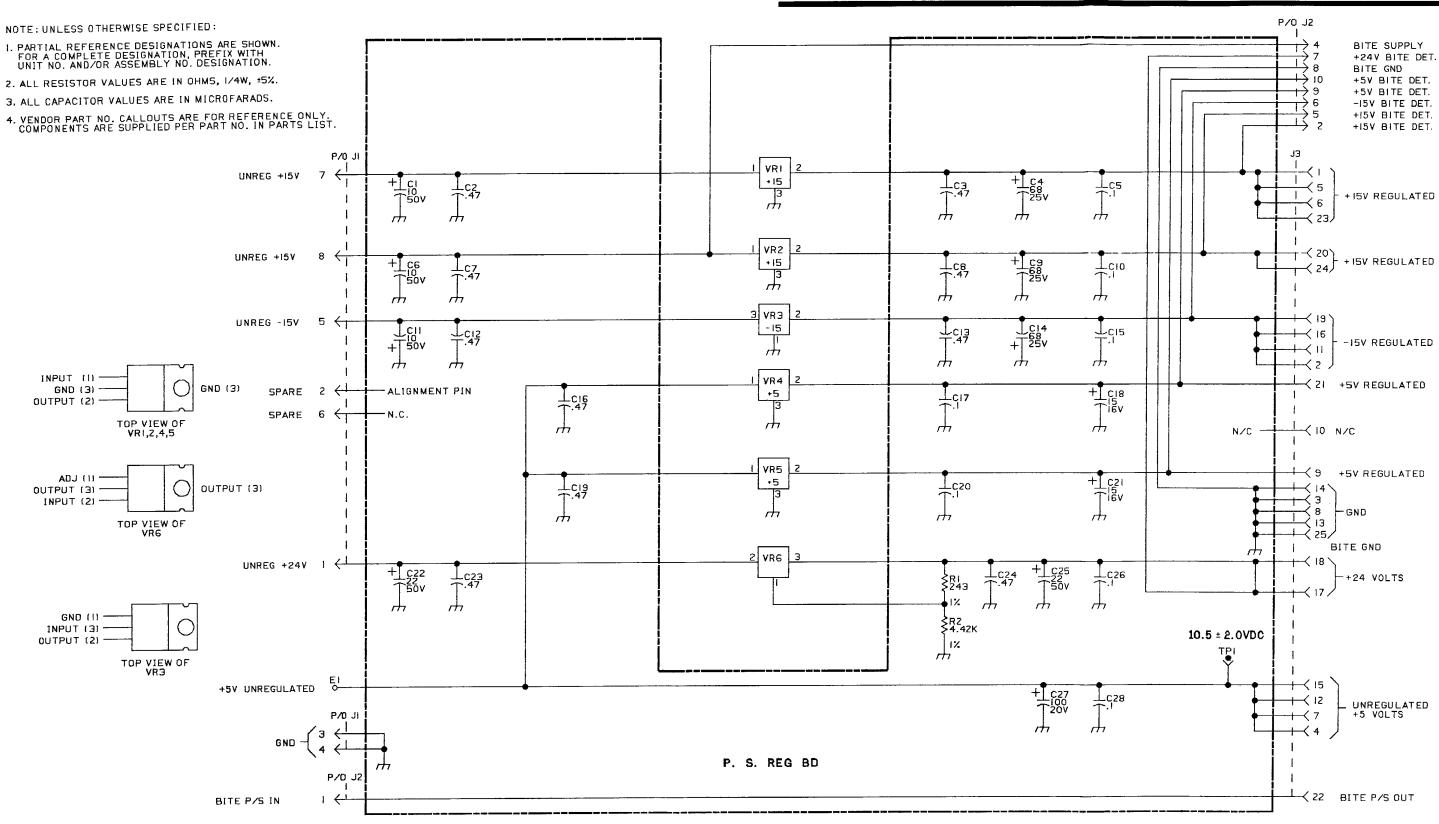

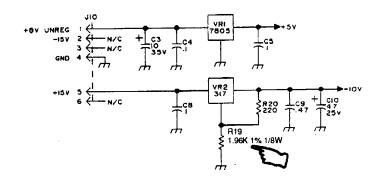

|           | A15 POWER SUPPLY ASSEMBLY            |      |

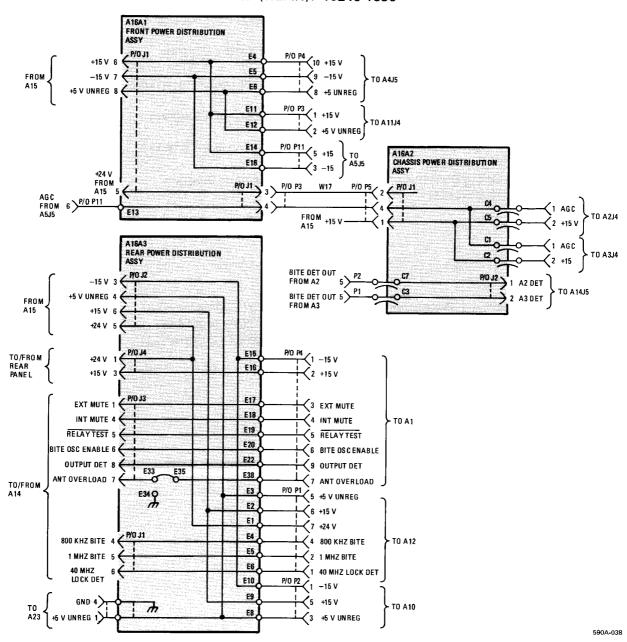

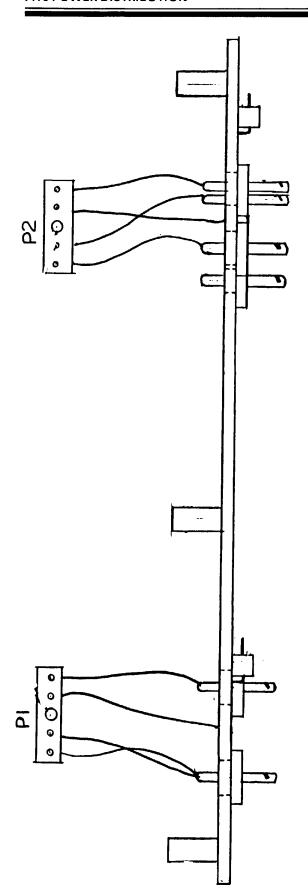

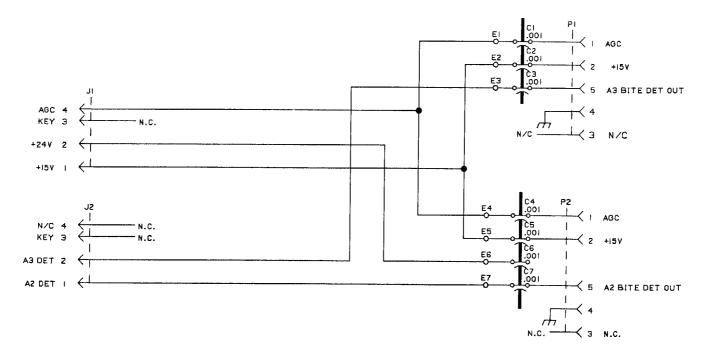

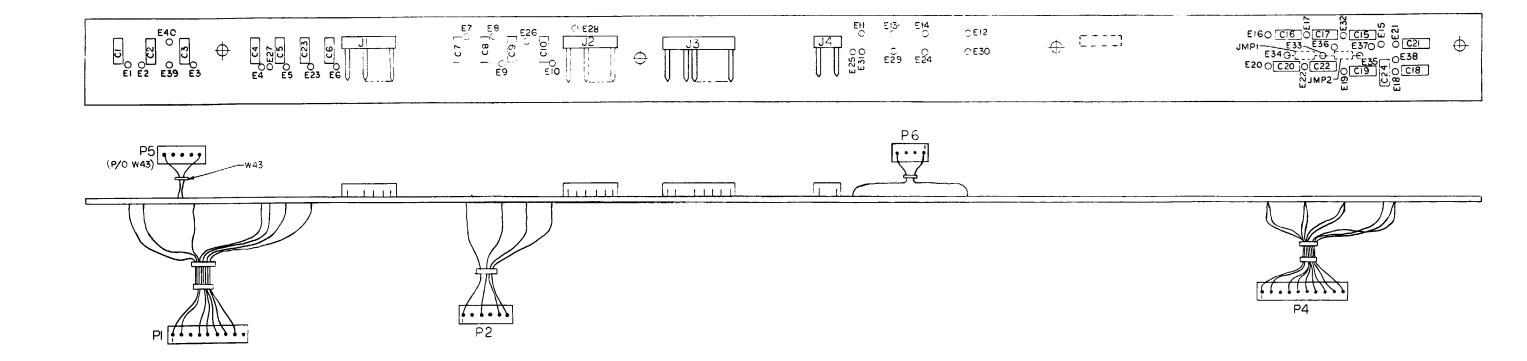

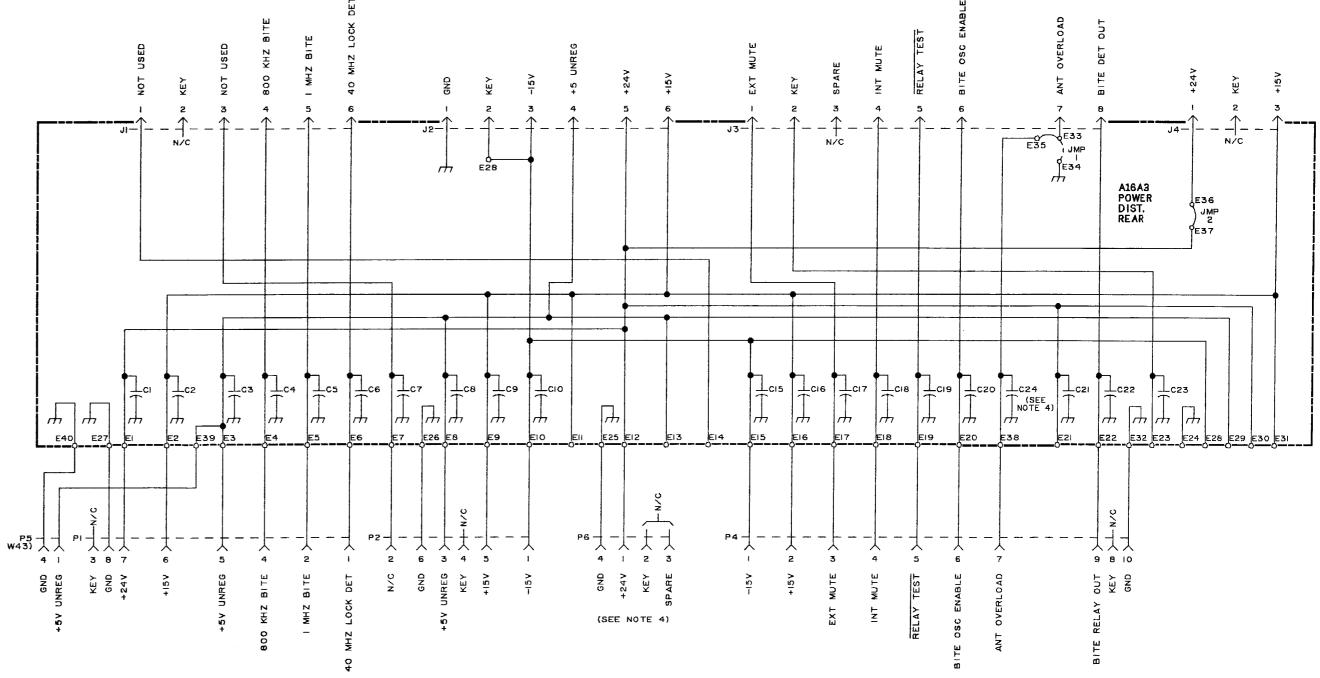

|           | A16 POWER DISTRIBUTION ASSEMBLIES    |      |

|           | A18 ISB IF/AUDIO ASSEMBLY            |      |

|           | A19 PRESELECTOR ASSEMBLY             |      |

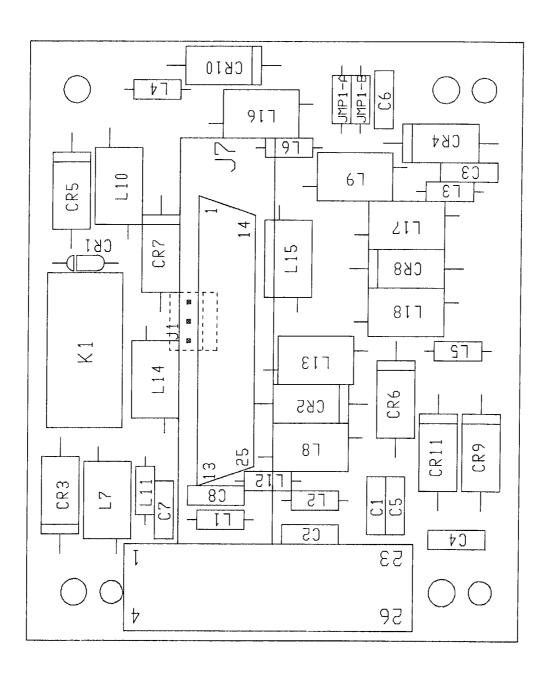

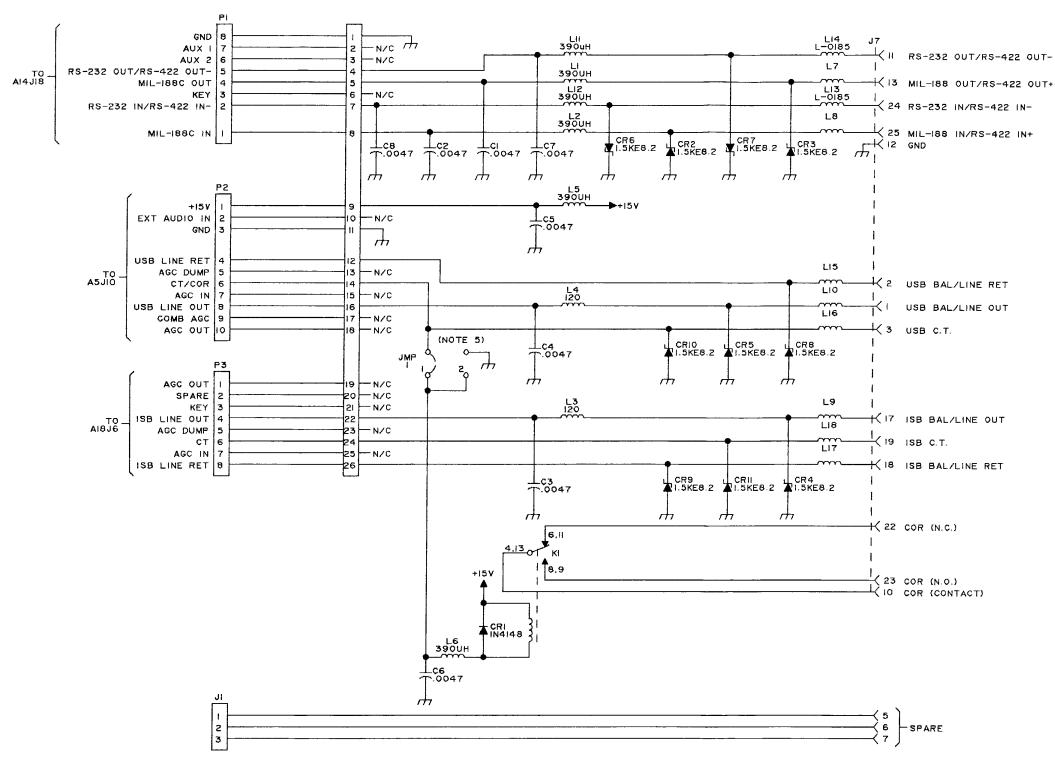

|           | A25 EMP/EMI SUPPRESSION ASSEMBLY     |      |

|           | APPENDIX                             |      |

#### **LIST OF FIGURES**

|                                                                | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

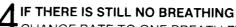

| Receiver                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

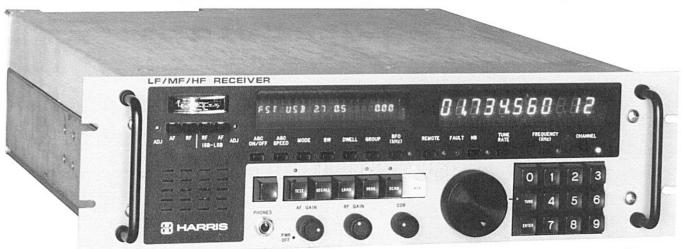

| Typical Receiver Applications                                  | 1-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

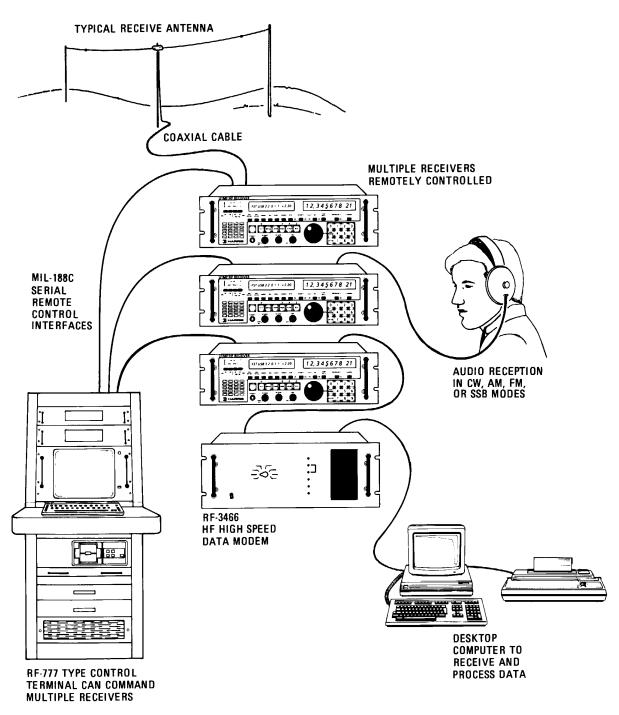

| Typical Doublet Antenna Installation                           | 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Desk Mount Dimensions                                          | 2-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Rack Mounting Details                                          | 2-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Rear Panel                                                     | 2-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

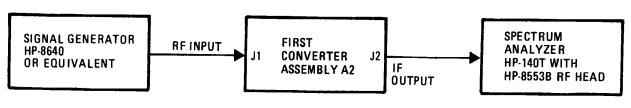

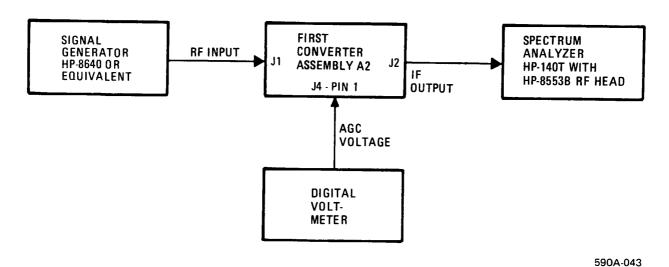

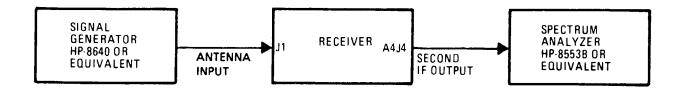

| Functional Test Setup                                          | 2-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Power ON/OFF, AF Gain, RF Gain, and COR                        | 3-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Channel, Frequency, BFO, and Group Display Entries             | 3-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| AGC, Mode, BW, and Dwell Displays and Controls                 | 3-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Speaker, Test, Recall, Load, Program, Scan and Receive Control | 3-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Front Panel Meter and Controls                                 | 3-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Remote, Fault and Noise blanker (NB) Controls and Indicators   | 3-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

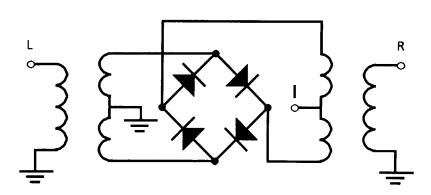

|                                                                | 4-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Receiver Gain Distribution                                     | 4-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

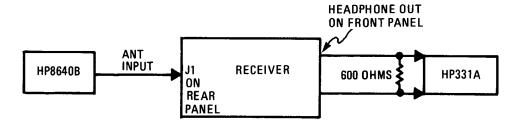

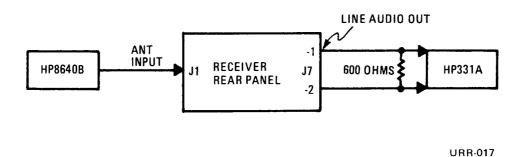

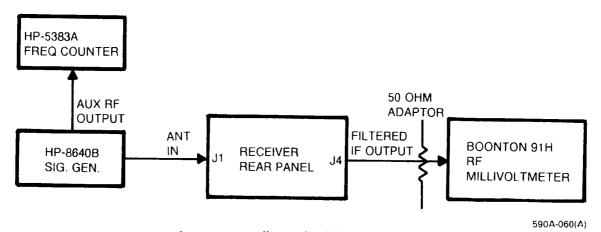

| Sensitivity Test Setup                                         | 5-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| •                                                              | 5-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                | 5-19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ·                                                              | 5-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

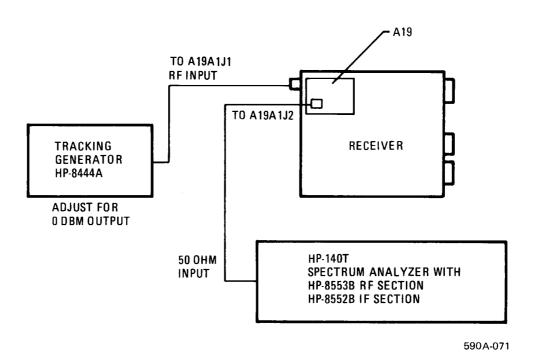

| IF Filter Selectivity Test Setup                               | 5-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                | Typical Receiver Applications Typical Doublet Antenna Installation Desk Mount Dimensions Rack Mounting Details Rear Panel Functional Test Setup Power ON/OFF, AF Gain, RF Gain, and COR Channel, Frequency, BFO, and Group Display Entries AGC, Mode, BW, and Dwell Displays and Controls Speaker, Test, Recall, Load, Program, Scan and Receive Control Front Panel Meter and Controls Remote, Fault and Noise blanker (NB) Controls and Indicators Receiver Signal Path Block Diagram Receiver Gain Distribution Sensitivity Test Setup Line Audio Test Setup Phone Audio Test Setup AGC Range Test Setup |

)

#### **LIST OF TABLES**

| Table |                                                            | Page        |

|-------|------------------------------------------------------------|-------------|

| 1-1   | Optional Equipment                                         | 1-4         |

| 2-1   | Ancillary Kit (P/N 10215-0021)                             | 2-1         |

| 2-2   | Calculation of Doublet Antenna Element Lengths             | 2-4         |

| 2-3   | Rear Panel Connector J7                                    | 2-8         |

| 2-4   | Remote Control Interface Configuration Switch Setting      | 2-9         |

| 2-5   | Serial Interface Baud Rate Switch Settings                 | 2-10        |

| 2-6   | ID Number Switch Weights                                   | 2-10        |

| 2-7   | Typical Filter Complement                                  | 2-12        |

| 2-8   | Programmed Channels                                        | 2-13        |

| 4-1   | Conversion of dBm to Vrms across 50 ohms (0 dBm = 1 mWatt) | 4-8         |

| 5-1   | Fault Code Listing                                         | 5-3         |

| 5-2   | BFO Tuning Range                                           | 5-6         |

| 5-3   | AM and SSB Test Results and Fault Locations                | 5- <b>9</b> |

| 5-4   | Self-Diagnostics Sequence Summary                          | 5-10        |

| 5-5   | Test Procedures                                            | 5-16        |

| 5-6   | Sensitivity Test Reports                                   | 5-17        |

| 5-7   | Audio Output Level and Distortion Test Report              | 5-18        |

| 5-8   | IF Filter Response Test Report                             | 5-21        |

#### SPECIFICATIONS FOR LF/MF/HF SYNTHESIZED RECEIVER

Frequency Range:

14 kHz to 29.999999 MHz

**Frequency Resolution:**

1 Hz increments standard

Tuning:

Continuous via tuning wheel in seven selectable

rates or direct entry via keypad.

**Tuning Time:**

Tuning time between any two frequencies is less

than 20 msec.

Frequency Stability - Internal:

± 0.5 part in 107-Standard

FREQUENCY STANDARD I/O

Input:

1 MHz, 0 dBm minimum

Output:

1 MHz, 0 dBm minimum

**Channel Memory:**

100-channel capacity capable of being loaded locally or remotely with complete receiver

parameters.

Scanning:

Scan any set of consecutive channel numbers (channel scan) or one of the ten preprogrammed sets of random channel numbers (group scan).

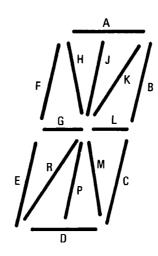

Readout/Display:

Receiver frequency, BFO frequency offset, channel assignment, mode, IF BW/filters, AGC,

BITE, dwell, scan group.

BFO:

10 Hz synthesized tuning, ± 9.99 kHz.

Remote Control:

A microprocessor-based system capable of accepting asynchronous serial data in accordance

with MIL-STD-188C.

**Remote Control Functions:**

Frequency, Channel Select, IF BW, Mode, AGC-TC, BFO, Fault-BITE Status, Scan Select, RF/IF

Gain, and Channel Load.

Internal Preselector:

Digital Preselector - standard

**Maximum Signal Input:**

Receiver protected at 25 watts available power

input.

Modes of Operation:

CW, 2-ISB, AM, FM, LSB, USB, FSK with external

demodulator.

COR:

Carrier Operated Relay

#### SPECIFICATIONS FOR LF/MF/HF SYNTHESIZED RECEIVER (Cont.)

Sensitivity:

For 10 dB (S + N) ÷ N ratio

CW: 0.2 µV (300 Hz) AM: 2.5 μV (6 kHz)

SSB: 0.6 μV

Note: Below 200 kHz, sensitivity may degrade 14

IF Bandwidths:

IF Filter: 3 dB BW (kHz)

CW: 0.3 AM: 6.0 FM: 16 USB: 2.7 LSB: 2.7

**INTERMODULATION**

In-Band:

-40 dB or better for (2) 50 mV (-13 dBm) signals

within the IF passband.

Out-of-Band:

-90 dB or better for (2) -20 dBm signals separated

100 kHz or more.

**Cross Modulation:**

10% or better for a 900 mV ( + 12 dBm) 30% modulated interfering signal removed 100 kHz or greater from the desired signal of 30 uV (-77

dBm).

**Reciprocal Mixing:**

The apparent noise appearing at the Receiver input when in a 3 kHz bandwidth, caused by a -17 dBm signal 100 kHz off tune, is less than 0.3

uV (-117 dBm).

Quieting Ultimate (S + N) ÷ N:

35 dB.

**SPURIOUS RESPONSES**

Image and IF:

-80 dB

Spurious:

Internal -101 dBm equivalent or less, external -80

dB.

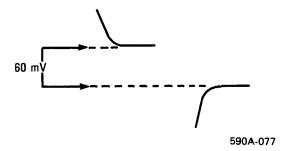

AGC

Range:

$\leq$  3 dB audio output variation for 2  $\mu$ V to 200 mV

signal range. (Threshold internally adjustable

from 1.0 to 5.0  $\mu$ V).

**Time Constants:**

3 ranges < 20 msec

Attack Time:

Fast: <35 msec

Decay + Hang Times:

Medium: 200 ± 50 msec Slow: 2.5 ± .5 sec

Manual: 100 dB range

#### SPECIFICATIONS FOR LF/MF/HF SYNTHESIZED RECEIVER (Cont.)

**AUDIO OUTPUTS:**

Phone:

+ 15 dBm/600 ohms/5% distortion

Line Output:

+ 15 dBm/600 ohms/5% distortion

**Hum and Noise:**

Less than 35 dB

Pass Band Ripple:

3 dB max.

IF Outputs:

455 kHz.

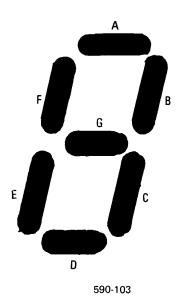

**Built-In Test Diagnostics:**

Fault isolation to module with front panel

alphanumeric indication.

**Power Requirements:**

115 Vac, 60 Hz, 90 watts

Temperature:

Operating: 0°C to +50°C

Non-Operating: -62°C to +71°C

**Humidity:**

0 to 95%

Size:

Rack mount and desk mount capability

5.25 H x 19 W x 19.5 D (behind front panel)

in. max.

(13.3 H x 48.3 W x 49.5 D cm).

Weight:

40 lbs. (18 kg)

#### **ABOUT THIS MANUAL**

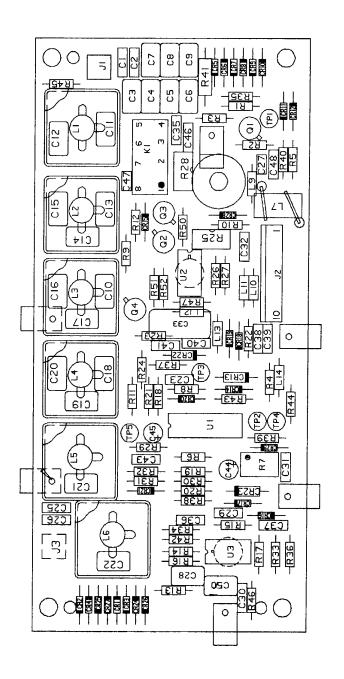

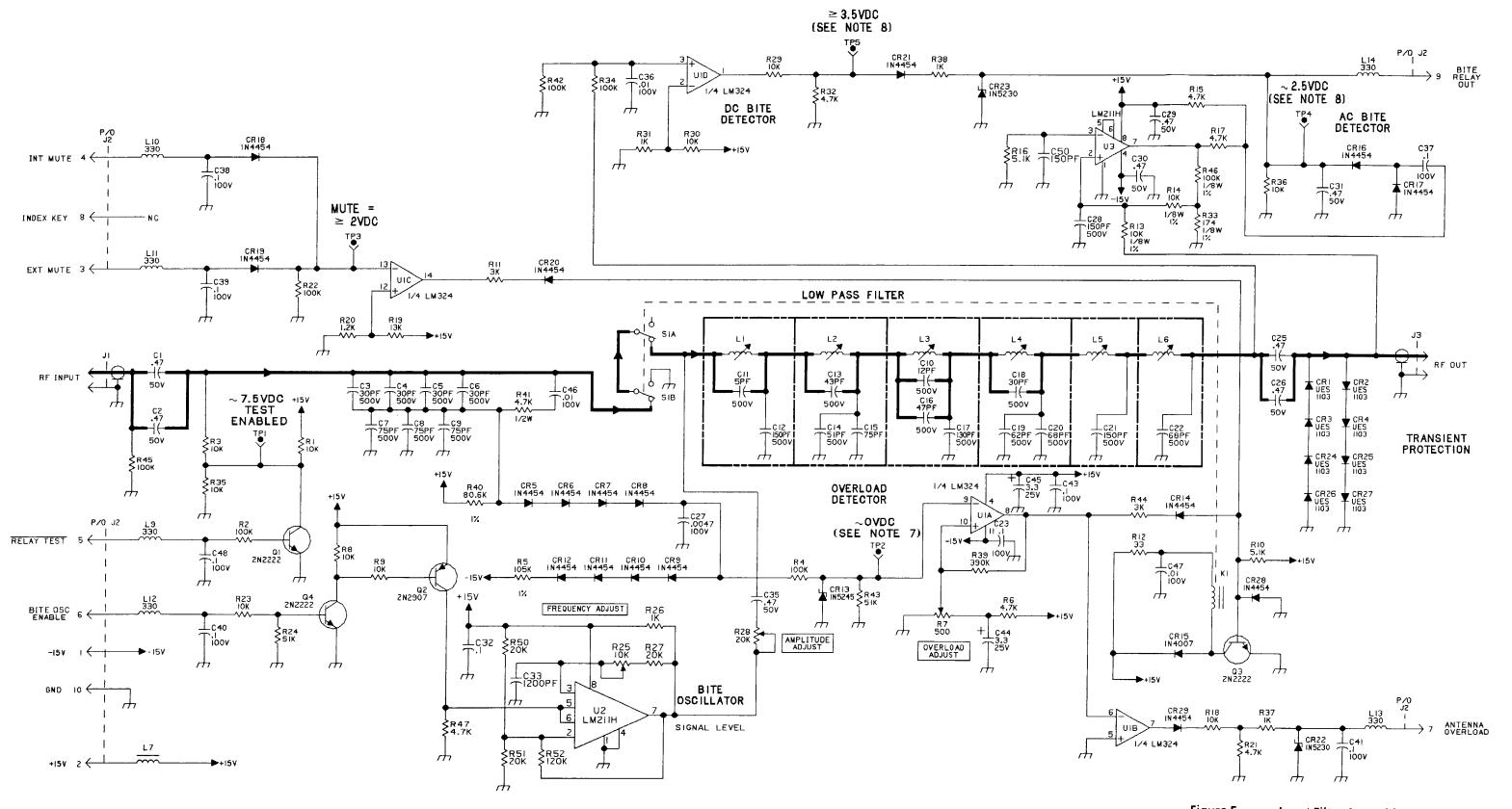

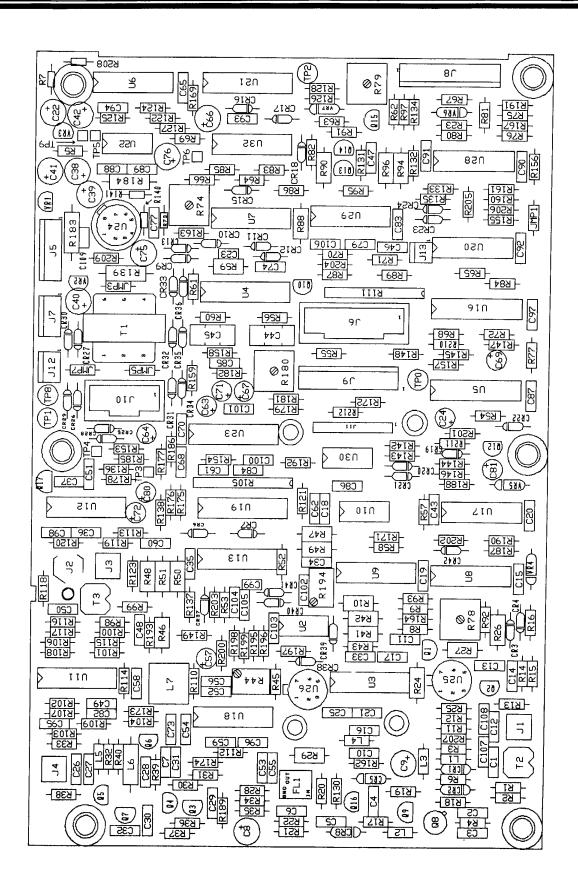

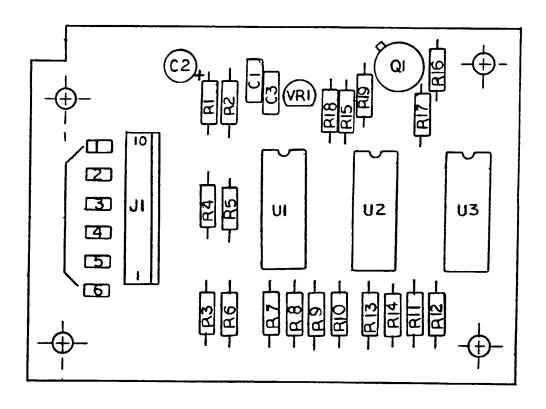

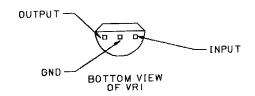

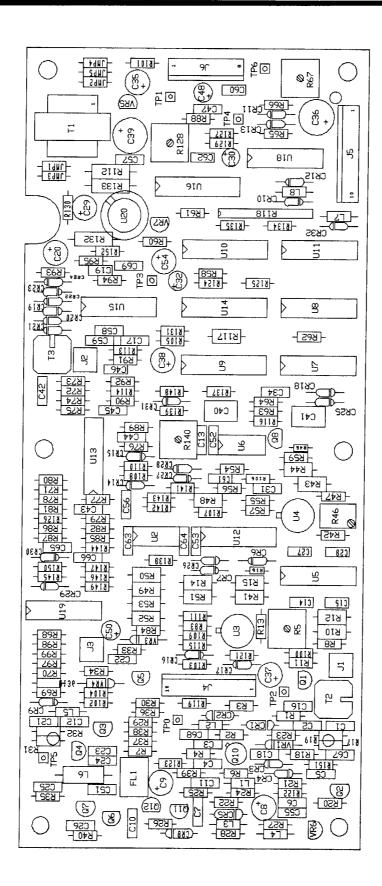

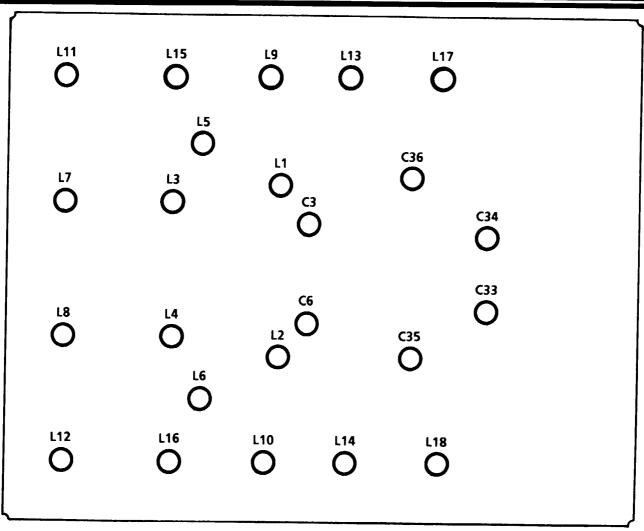

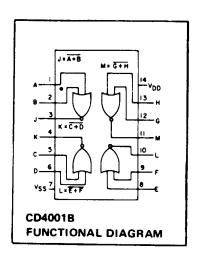

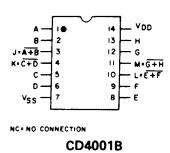

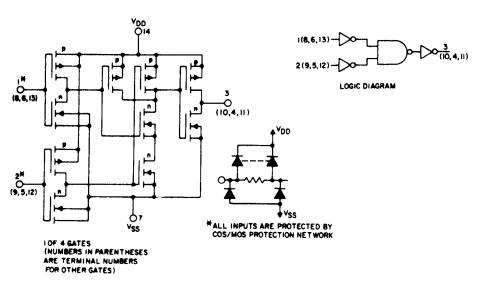

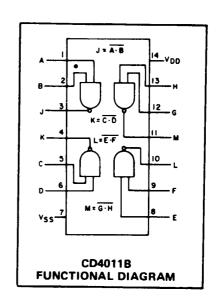

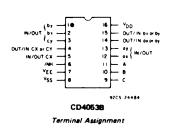

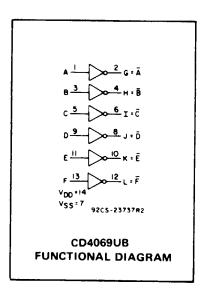

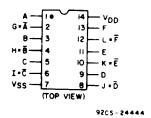

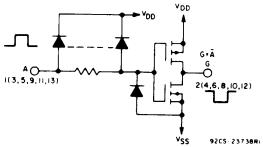

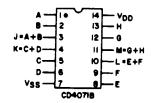

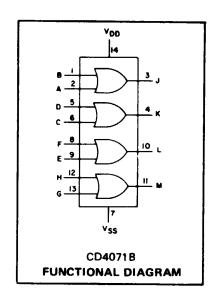

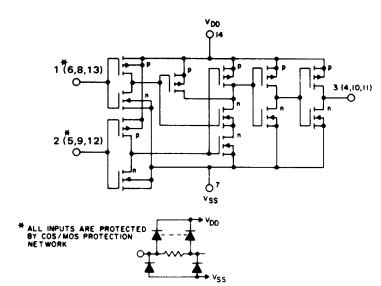

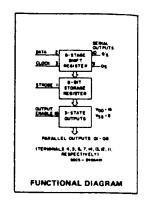

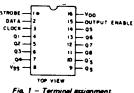

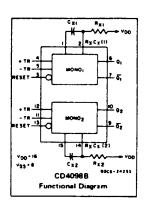

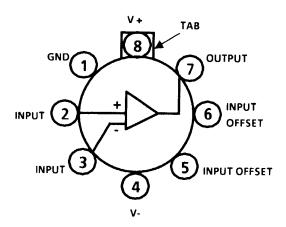

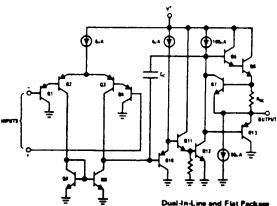

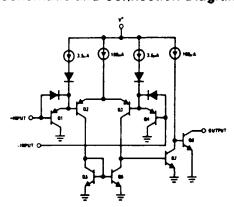

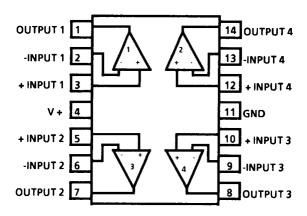

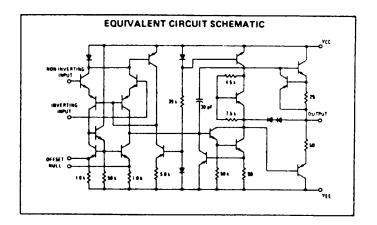

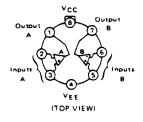

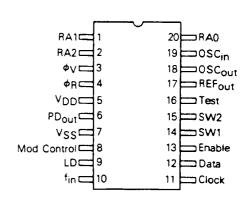

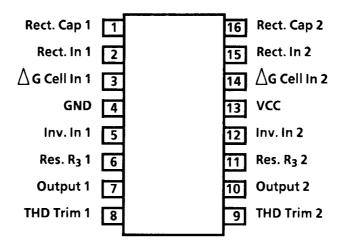

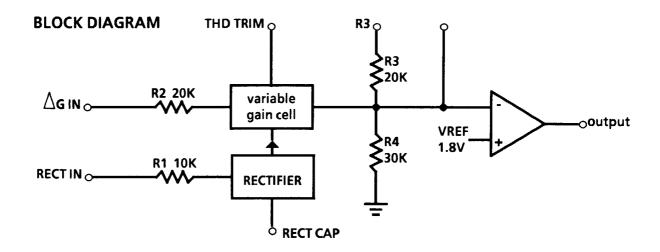

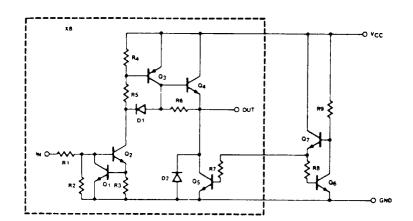

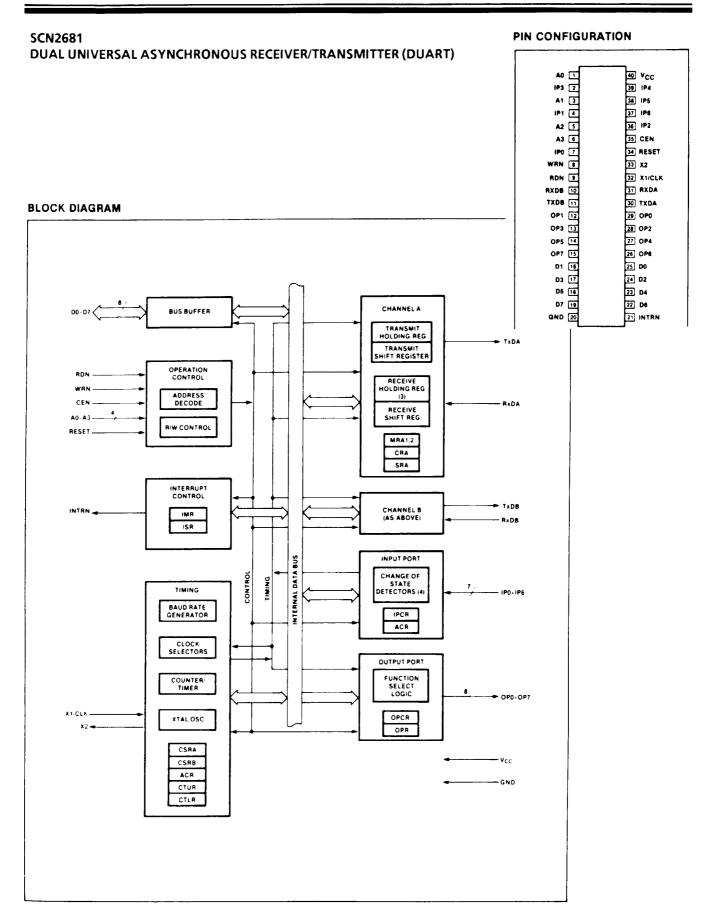

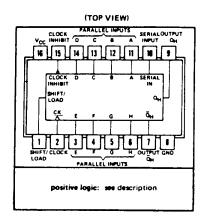

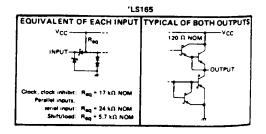

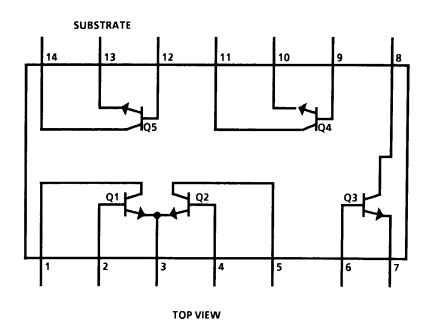

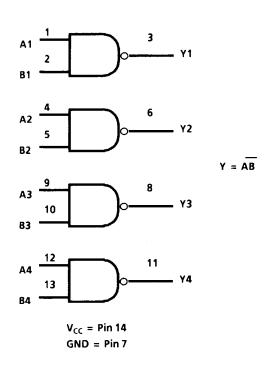

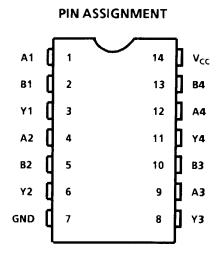

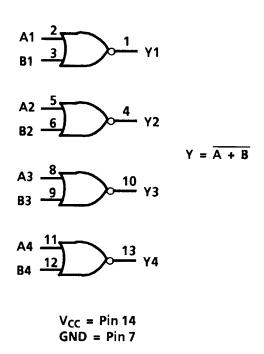

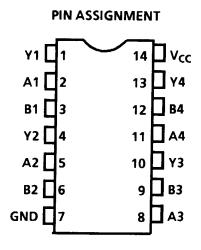

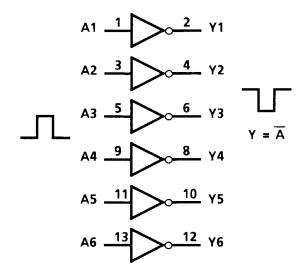

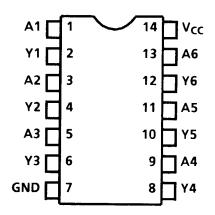

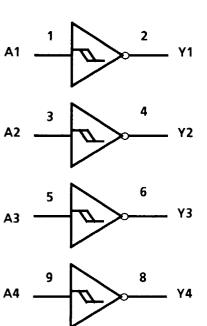

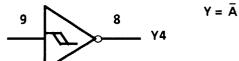

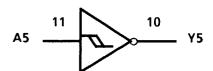

This instruction manual is divided into five general information sections (blue tabs), and 16 unit instruction sections (white tabs). Installation, operation, and maintenance procedures as well as a comprehensive technical description are included in the general information tab sections. The 16 unit instruction sections include detailed circuit descriptions, parts lists, component location drawings and schematic diagrams for the subassemblies of the Receiver. Data sheets for the integrated circuits used in this Receiver are included in the appendix for the user's convenience.

# R-2368/URR RADIO RECEIVER

INSTRUCTION MANUAL

URR-100P

R-2368/URR Receiver

#### **SECTION 1**

#### **INTRODUCTION**

#### 1.1 INTRODUCTION

1

This manual contains information necessary to install, operate, maintain, and repair the Receiver. This manual is subdivided into the following sections.

- Section 1: Introduction. Includes basic description, feature highlights, optional auxiliary equipment, etc.

- Section 2: Installation. Includes site selection, power requirements, mechanical installation, interconnect requirements, initial setup and power on, and functional checkout.

- Section 3: Operation. Includes general operating instructions, control, and indicator descriptions.

- Section 4: Technical Description. Contains general receiver characteristics, receiver block diagram, AGC-gain distribution chart, and signal path and synthesizer functional descriptions.

- Section 5: Maintenance: Contains general repair techniques, component handling techniques, self-test (BITE) descriptions and error code listings, receiver performance test procedures, and component data sheets.

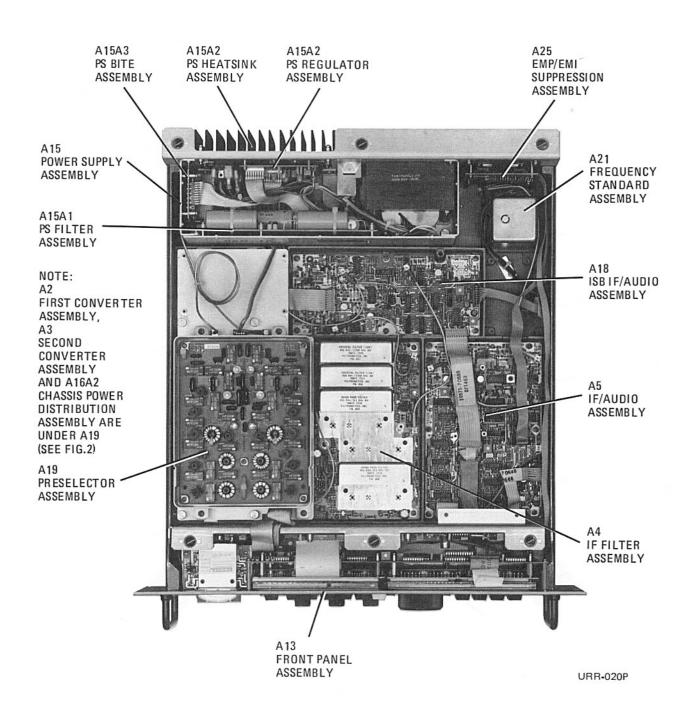

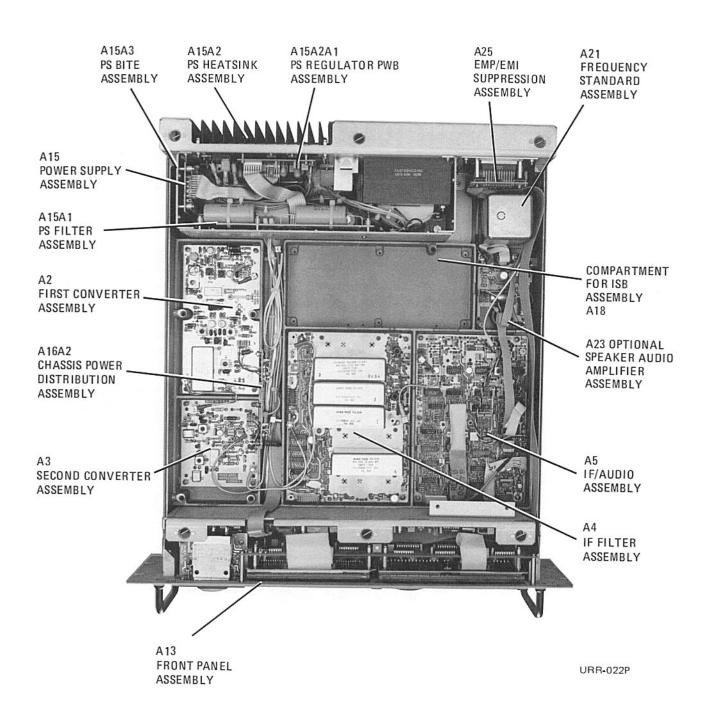

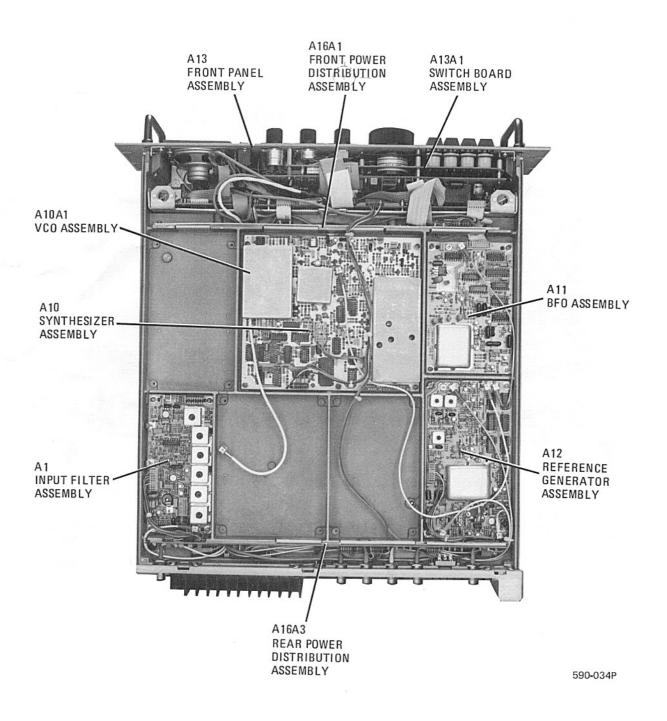

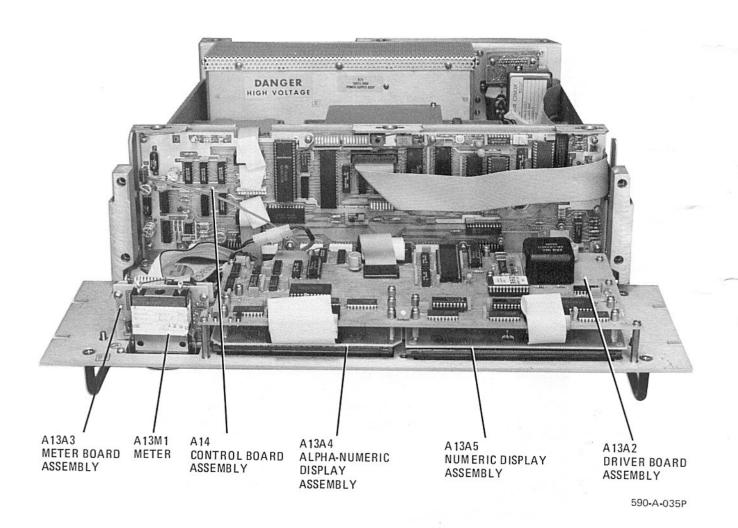

- Unit Main Chassis thru A25: These sections include detailed circuit descriptions, component location diagrams, parts lists and schematic diagrams for all subassemblies in the Receiver.

#### 1.2 GENERAL DESCRIPTION

The Receiver is designed to deliver high performance synthesized reception operating in the AM, CW, FM, USB, LSB, and ISB modes tuning to signals from 14 kHz to 29.99999 MHz (in 1 Hz increments) utilizing digital tuning techniques. Up to 100 channels can be programmed for frequency, detection mode, filter bandwidth, AGC mode, and BFO offset, and recalled individually, or scanned sequentially or in groups. The Receiver contains a comprehensive built-in test equipment (BITE) network which allows extensive microprocessor controlled self-testing to isolate faults at the modular level. Typical Receiver applications are illustrated in figure 1-1.

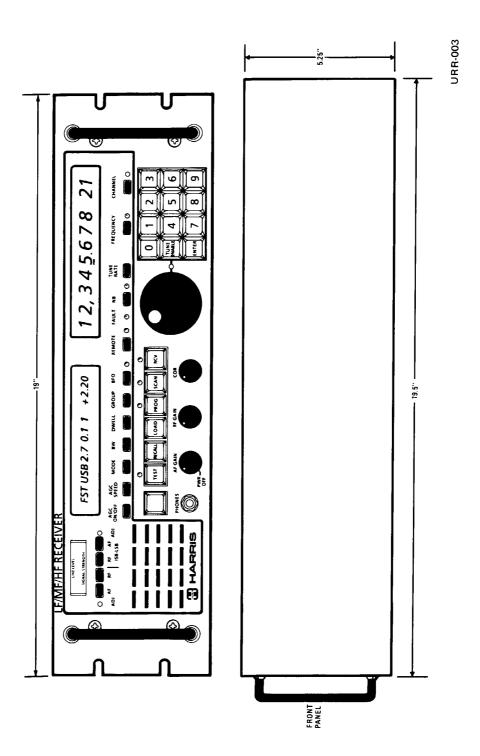

Manual tuning and channel selection is activated via a front panel touch pad or tuning wheel. Operating parameters such as detection mode and filter bandwidth (CW -.3 kHz; AM, 6 kHz; USB/LSB - 2.7 kHz; FM - 16 kHz) and AGC mode (slow, medium, fast, off) are pushbutton selectable. Receiver operating parameters and self-testing results are displayed on two front panel numeric and alphanumeric displays. Full remote control is built-in as a standard feature and is compatible with MIL-STD-188C.

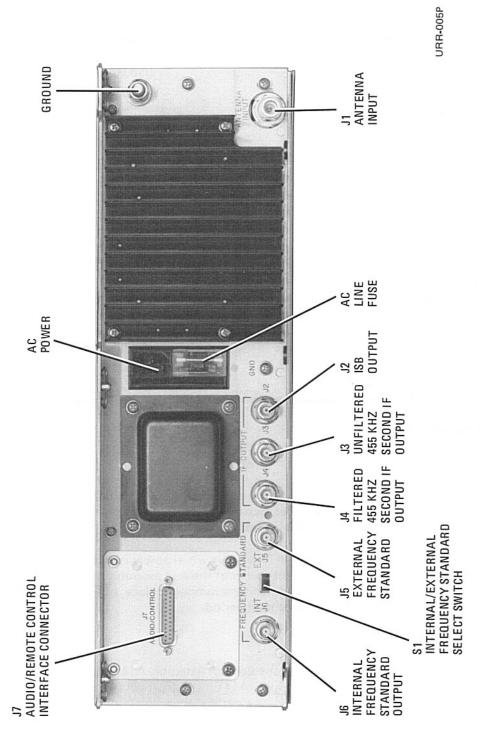

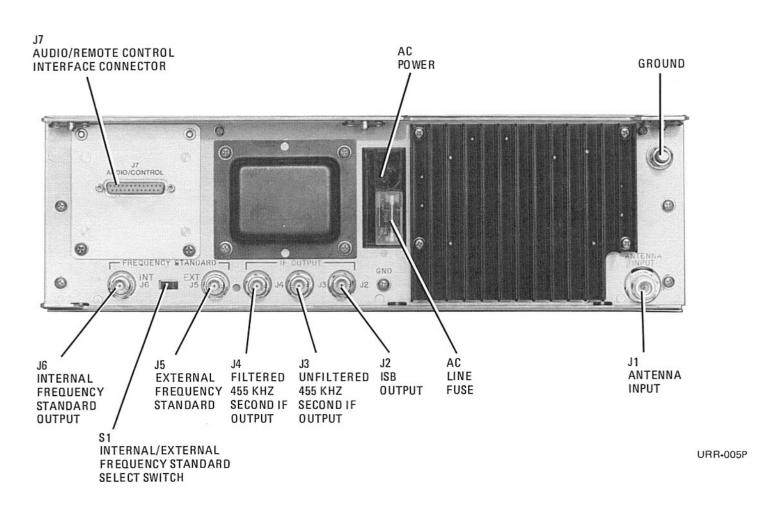

Rear panel connectors include an N type coaxial connector for the RF antenna input and BNC 50-ohm connectors for the following inputs/outputs: filtered 455 kHz IF output, unfiltered 455 kHz DSB output, ISB output, 1 MHz frequency standard input, and frequency standard output. Additionally, other connectors allow access to 600-ohm line audio outputs, remote control inputs and outputs, and other functions (see table 2-3).

590 A-079

Figure 1-1. Typical Receiver Applications

The Receiver is entirely modular in design to facilitate maintenance. The unit may be rack mounted with the following considerations.

- Dimension 5.25 H x 19.0 W x 19.5 D (less front panel projections) inches maximum (13.3 H x 48.3 W x 49.5 D cm)

- Weight 40 pounds (18.1 kg)

- Power requirements 115 Vac, 60 Hz, 90 watts

Note that a complete listing of all Receiver specifications is included at the front of this manual.

#### 1.3 RECEIVER FEATURES

This high performance Receiver utilizes the latest device technology and circuit design. The microprocessor based architecture allows for a cost effective design with the following versatile features.

- Synthesized digital tuning and readout in 1 Hz steps from 14 kHz to 29.99999 MHz.

- Keyboard control

- Continuous single knob tuning

- Full remote control by digital asynchronous commands with a wide variety of standards and rates.

- Built-in test equipment (BITE) fault isolation to replaceable module level.

- Preset channel memory Up to 100 front panel programmable channels can be stored in a nonvolatile memory. Frequency and mode are stored in memory for instant recall.

- Channel scanning Automatically searches programmed channels, with a selectable dwell time.

- Synthesized variable BFO offset ± 9.99 kHz in 10 Hz steps.

- Diversity capability With external RF-575 Diversity Combiner.

- Multimode operation Including USB, LSB, ISB, CW, AM, and FM. (FSK optional.)

- COR (Carrier Operated Relay) Operated from a front panel control.

- Plug in subassemblies All subassemblies can be replaced using common hand tools.

#### 1.4 COMPATIBILITY

This Receiver is compatible with the following RF products:

- RF-551A Preselector

- RF-575 Quad Diversity Combiner

- RF-130, RF-1130, RF-755 and RF-765 Transmitters

- RF-7110 Adaptive Controller

- RF-7405 Remote Control

- RF-777 Remote Control

#### 1.5 CUSTOMER OPTIONS

Table 1-1 is a list of optional equipment.

**Table 1-1. Optional Equipment**

| Number         | Name                                   | Part No.   | Description                                                                                                                                                                                               | Publication No.                         |

|----------------|----------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| RF-518         | Earphones                              | 724-0075   | For reduction of ambient noise levels or to utilize private listening.                                                                                                                                    | None                                    |

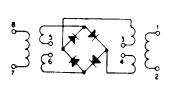

| RF-567         | High Impedance RF<br>Input Transformer | 1920-1450  | Improves reception when untuned antennas are used.                                                                                                                                                        | 1920-1452<br>(Instruction<br>Sheet)     |

| RF-575         | Diversity Combiner                     | 7634-0000  | Selects audio from the receiver with the strongest signal.                                                                                                                                                | 7634-1030                               |

| RF-593         | High Stability<br>Frequency Option     | 759-3906   | 1 MHz frequency standard with proportional temperature control. 1 part in 108 stability.                                                                                                                  | 10215-0022<br>A12/A21 section           |

| RF-594-01      | Rack Mount                             | 10073-0055 | Includes slides and related hardware for rack mounting applications                                                                                                                                       | 10215-0020<br>(installation<br>section) |

| RF-594-02      | Desk Top Case                          | 10073-0045 | Enclosed case for desk top installation.                                                                                                                                                                  | 10215-0020<br>(installation<br>section) |

| RF-594-03      | Stack Mount                            | 10073-0035 | Includes hardware for standard stack mounting applications.                                                                                                                                               | 10215-0020<br>(installation<br>section) |

| RF-595A-<br>02 | Delay Compensated<br>ISB Option        | 10215-6360 | Delay compensated filtering for critical data communications. Provides less than 500 u/sec. differential time delay from 400 Hz to 2900 Hz. Offers less than 2 dB ripple in the 300 Hz to 3 kHz passband. | 10215-0018<br>(supplement)              |

Table 1-1. Optional Equipment (Cont.)

| Number    | Name                              | Part No.   | Description                                                                                                                                               | Publication No.                 |

|-----------|-----------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| RF-596-01 | Half Octave Filter                | 10073-6410 | Offers filtering protection from 2<br>to 30 MHz in 8 half-octave band<br>filters. Also, for frequencies<br>below 2 MHz, Low Pass filtering<br>is provided | SU-10073-0019-1<br>(supplement) |

| RF-597A   | Noise Blanker                     | 10215-6800 | The Noise Blanker removes impulse type noise from received signals. Adjusts automatically to received signal level changes.                               | 10215-0019<br>(supplement)      |

| RF-598A   | 4ISB Option                       | N/A        | Provides simultaneous operation on four independent sidebands.                                                                                            | N/A                             |

| RF-651-02 | Receiver<br>Multicoupler (2 port) | RF-651-002 | Permits operation of two receivers from a common antenna. At the same time, it provides isolation between receivers.                                      | 7733-000                        |

| RF-651-04 | Receiver<br>Multicoupler (4 port) | RF-651-004 | Same as RF-651-002, but with 4 ports.                                                                                                                     | 7733-000                        |

| RF-651-08 | Receiver<br>Multicoupler (8 port) | RF-651-008 | Same as RF-651-002, but with 8 ports.                                                                                                                     | 7733-000                        |

#### 1.6 SPECIALIZED REQUIREMENTS

Harris/RF Communications Group Systems Division specializes in translating exacting customer needs into complete systems packages. Contact the following for specialized requirements.

> Harris Corporation/RF Communications Group 1680 University Avenue Rochester, New York 14610 U.S.A.

Phone: (716) 244-5830

Cable: RFCOM; Rochester, New York

Telex: 978464

#### **SECTION 2**

#### **INSTALLATION**

#### 2.1 INTRODUCTION

This section provides unpacking and inspection information, equipment installation and mounting instructions, site selection, interconnection data, initial setup, and receiver functional test procedures.

#### 2.2 UNPACKING AND INSPECTION

Carefully open the shipping carton and check the contents against the packing list secured to the outside of the container. Inspect all items for signs of damage. Immediately notify the carrier if any damage is discovered. Save all packing material for possible reshipment.

#### 2.3 ANCILLARY KIT

Items that are supplied in the Receiver Ancillary Kit, (Part No. 10215-0021) are listed in table 2-1.

| Quantity | Part No.     | Description               |

|----------|--------------|---------------------------|

| 1        | J22-0001-001 | Connector, Type D, 25 pin |

| 1        | J55-0015-025 | Hood, D-Connector, 25 pin |

| 1        | W-0023       | Cord, Line, 6 feet        |

Table 2-1. Ancillary Kit (P/N 10215-0021)

#### 2.4 SITE SELECTION

The Receiver provides specified performance in any environment within the temperature range of 0°C to +50°C and up to 95 percent humidity. Consider the following factors when determining the operating location for the Receiver.

- Avoid sites which will subject the receiver to conditions exceeding those mentioned above. If this is not possible, provide an environmentally controlled site (adequate ventilation, temperature control, etc.) to maintain the stated operating limits.

- Avoid nearby obstructions such as hills, trees, buildings, and power lines which absorb and reflect radio signals. In particular, avoid obstructions that are in a direct line with the desired directions of reception.

- Some antennas, especially the doublet, are directional and should be oriented for maximum signal gain. Therefore allow enough land area around the site to orient the antenna as necessary.

- Reception is generally best at the top of a hill, over level ground, or over water.

Once the operating site has been chosen, consider the following factors when positioning the Receiver at the site.

- Ease of operation and visibility of controls

- Relation to other units

- Power, control, and output interfaces

- Environmental considerations for unit and operator (temperature control, adequate ventilation, etc.).

#### WARNING

Always operate the Receiver with a heavy gauge ground strap connected from a solid earth ground to the rear panel ground. Failure to do so could result in serious injury or death to the operator if the receiver should ever fail in such a manner as to make the chassis electrically hot.

#### 2.4.1 Antennas

Maximum receiver sensitivity is achieved when the antenna impedance presented at antenna input connector, J1, is 50 ohms. The use of coaxial cables, such as type RG-58/U terminated with an N type connector, prevents feed-line noise pickup and provides the proper impedance match.

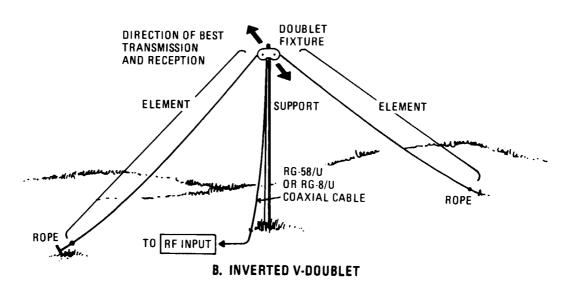

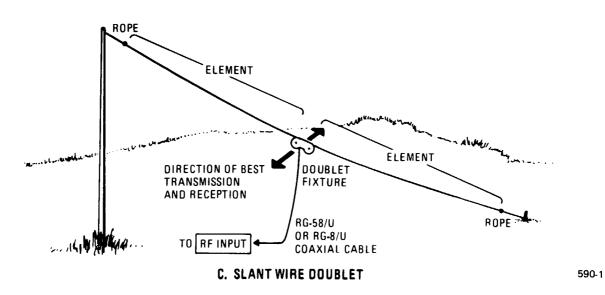

Doublet antenna kits, such as the RF-334 and SB-AD, are available from Harris Corporation/RF Communications. Three basic types of antennas, the horizontal doublet, the inverted V, and the slant wire can be constructed with these kits. Figure 2-1 shows these three antenna types used in typical installations. Each type of doublet antenna has two legs of equal length, one connected to the center conductor of the coaxial cable and the other connected to the shield. The two legs have a combined electrical length of one-half wavelength (one-quarter wavelength for each leg).

The inverted V and slant wire doublets are useful if the antenna site prohibits the use of the two supports required for a horizontal doublet, or if the supports cannot be located so that the doublet is perpendicular to the direction of the desired transmitted signal. All doublet antennas are directional and provide best response to signals received from directions perpendicular to their lengths. The length of each element of a doublet can be determined from one of the formulas given in table 2-2.

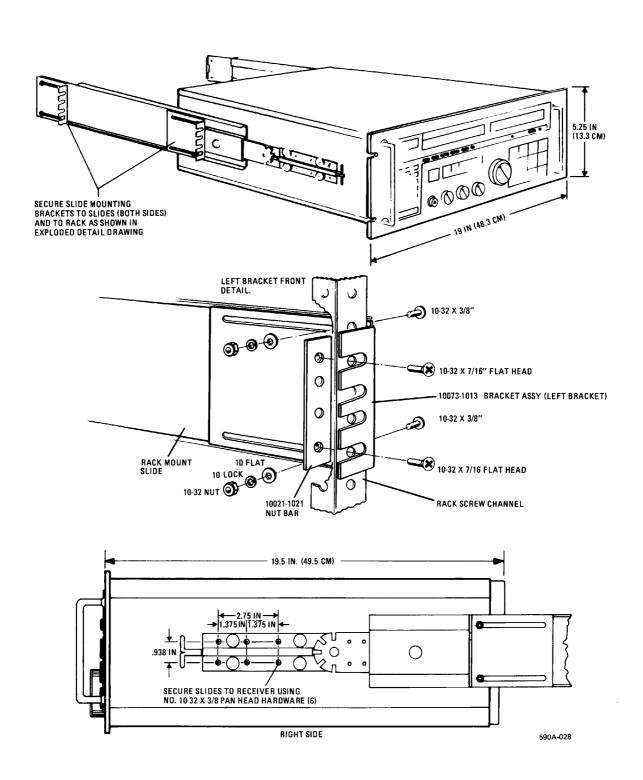

#### 2.5 MECHANICAL INSTALLATION

The Receiver may be desk mounted (RF-594-02 option), see figure 2-2, stack mounted (RF-594-03 option) or rack mounted (RF-594-01 option) into a standard 19-inch equipment rack. See figure 2-3 for rack mounting information. Note that two different mounting brackets are supplied for rack mounting. PN 10073-1010 fits the left side of the Receiver and PN 10073-1014 fits the right side. The detail drawing in figure 2-3 shows the left side bracket.

#### 2.6 POWER REQUIREMENTS

The Receiver requires 115 Vac, 60 Hz single-phase power at 90 watts, nominally. Ac power selection is factory set to 115 Vac. The receiver can be configured for other line voltages including 100, 220, or 240 Vac. To select a different range, first turn the front panel power switch off, then remove the ac power cord at the rear panel. Slide the plastic cover out of the way to expose the fuseholder and remove the fuse by pulling on the lever labeled FUSE PULL. Grasp the small PC card (located to the left of the fuseholder) with needlenose pliers

Figure 2-1. Typical Doublet Antenna Installation

Table 2-2. Calculation of Doublet Antenna Element Lengths

| Antenna Type                    | Length of Each<br>Element (Feet) | Length of Each<br>Element (Meters) |

|---------------------------------|----------------------------------|------------------------------------|

| Doublet, horizontal, or slanted | <u>234</u><br>f (MHz)            | 71.3<br>f (MHz)                    |

| Inverted V doublet              | <u>245</u><br>f (MHz)            | <u>74.5</u><br>F (MHz)             |

and pull the card straight out. This card will be labeled with the numbers 100, 120, 220, and 240 Vac. Orient this card so that the desired range faces the fuseholder, and is the only number visible once the card has been reinserted. Insert the fuse for the selected voltage and reconnect the power cord to the radio and the ac source. Turn the power on.

#### 2.7 INPUT/OUTPUT CONNECTIONS

The Receiver is complete and can be operated without other equipment. It requires only the appropriate power, antenna connections, and a headset. All other input/output connectors are used to expand and integrate features of the receiver or the system. Input and output connectors are shown and their uses explained in figure 2-4.

All RF type connectors are standard BNC, 50-ohm connections except the antenna connector which is an N type coaxial connector. Table 2-3 details the signal functions available at J7.

#### 2.8 INITIAL SETUP AND ADJUSTMENTS

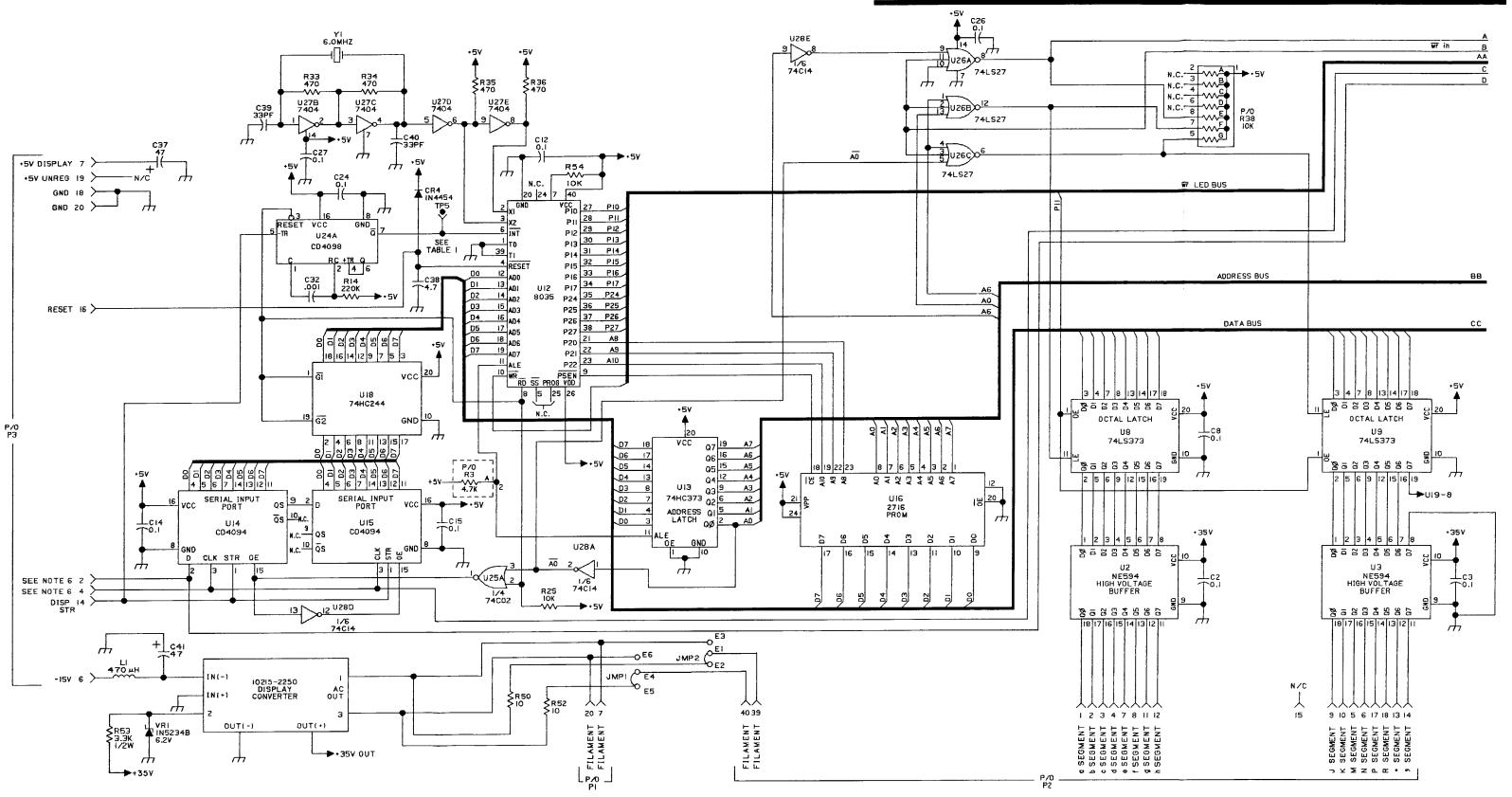

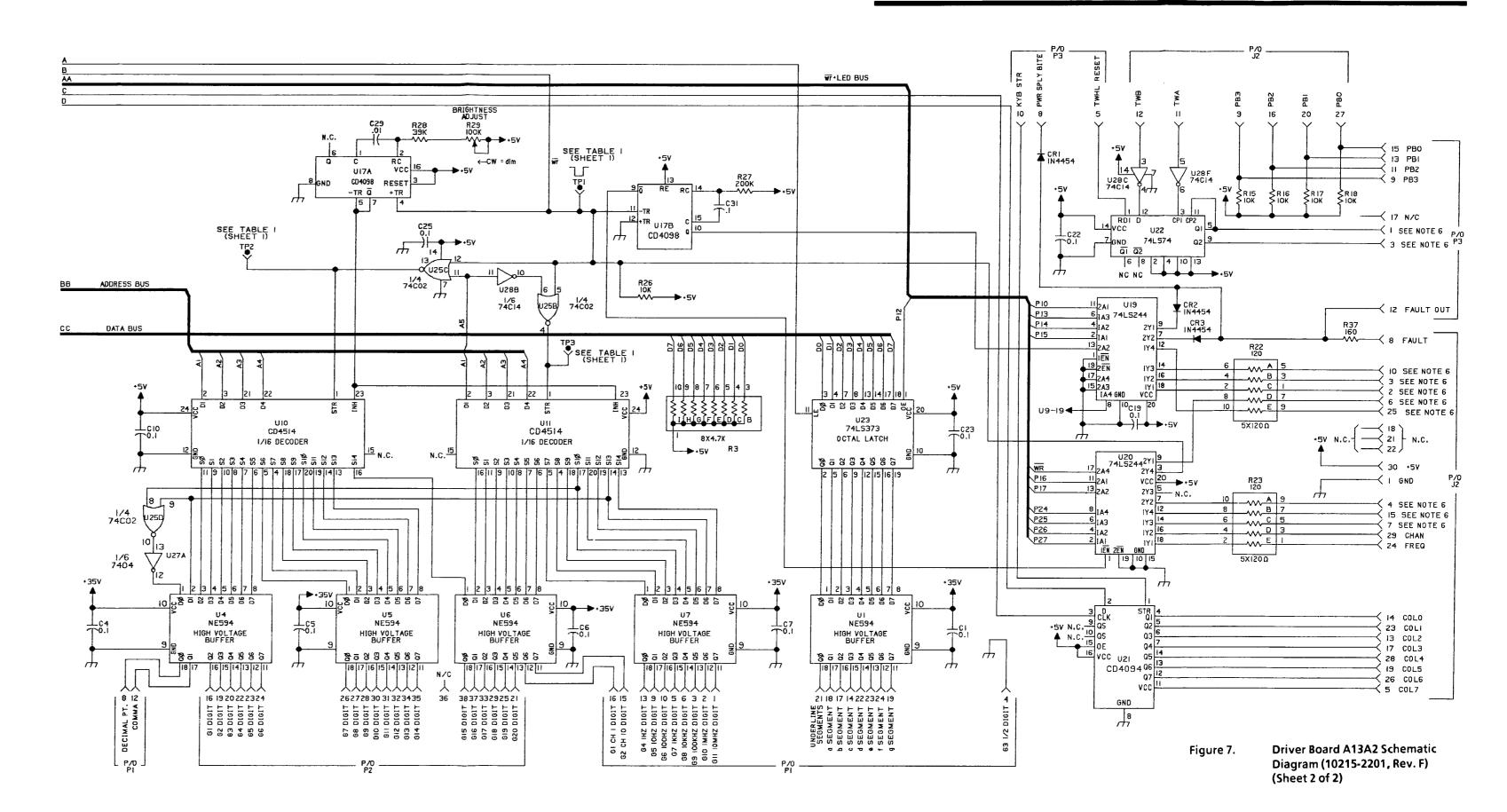

To set up the remote control interface, the Control Assembly A14 must be accessed. The A14 assembly is located behind the front panel. To access the assembly, remove the top and bottom covers, then the four phillips head screws on the front panel and tilt the panel forward. The front panel is hinged at the bottom. After the Control Assembly is configured, the front panel can be returned to its original position and power can be applied to the unit. Brightness of the displays can be adjusted at this point, if desired, by turning A13A2R29.

#### WARNING

High voltages are present inside the front panel when the receiver is turned on.

After the brightness has been adjusted, the top and bottom covers can be replaced. The line audio adjustments can be made when an appropriate signal is present using the adjustment screws adjacent to the front panel meter.

Figure 2-2. Desk Mount Dimensions

Figure 2-3. Rack Mounting Details

Figure 2-4. Rear Panel

Table 2-3. Rear Panel Connector J7

| Pin              | Function                  |

|------------------|---------------------------|

| J7-1             | USB Line Out              |

| J <b>7-2</b>     | USB Line Ret              |

| J7-3             | GND                       |

| J7-4 thru J7-9   | Spare                     |

| J <b>7</b> -10   | COR (Contact)             |

| J <b>7</b> -11   | RS-232 Out/RS-422 Out -   |

| J7-12            | GND                       |

| J <b>7-13</b>    | MIL-188C Out/RS-422 Out + |

| J7-14 thru J7-16 | Spare                     |

| J7-17            | ISB Line Out              |

| J7-18            | ISB Line Ret.             |

| J7-19            | GND                       |

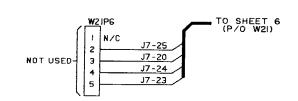

| J7-20, J7-21     | Spare                     |

| J7-22            | COR (N.C.)                |

| J7-23            | COR (N.O.)                |

| J <b>7-24</b>    | RS-232 ln/RS-422 ln -     |

| J7-25            | MIL-188C ln/RS-422 ln +   |

#### 2.8.1 Memory Backup Battery

#### **CAUTION**

DO NOT short backup battery terminals. A shorted battery can overheat, destroying the battery and damaging the PWB assembly.

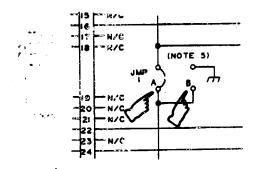

A rechargeable Ni-Cad battery is used to keep the RAM alive when power is interrupted or the receiver is turned off. Jumper J17, located in the upper right corner of the A14 assembly, must be in place to activate the keep alive circuit. Receivers are normally shipped with the jumper in place, however, the jumper should be removed if the receiver is to be stored for an extended period.

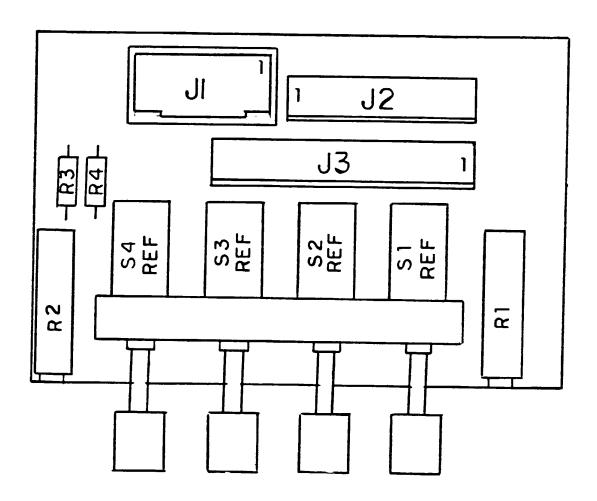

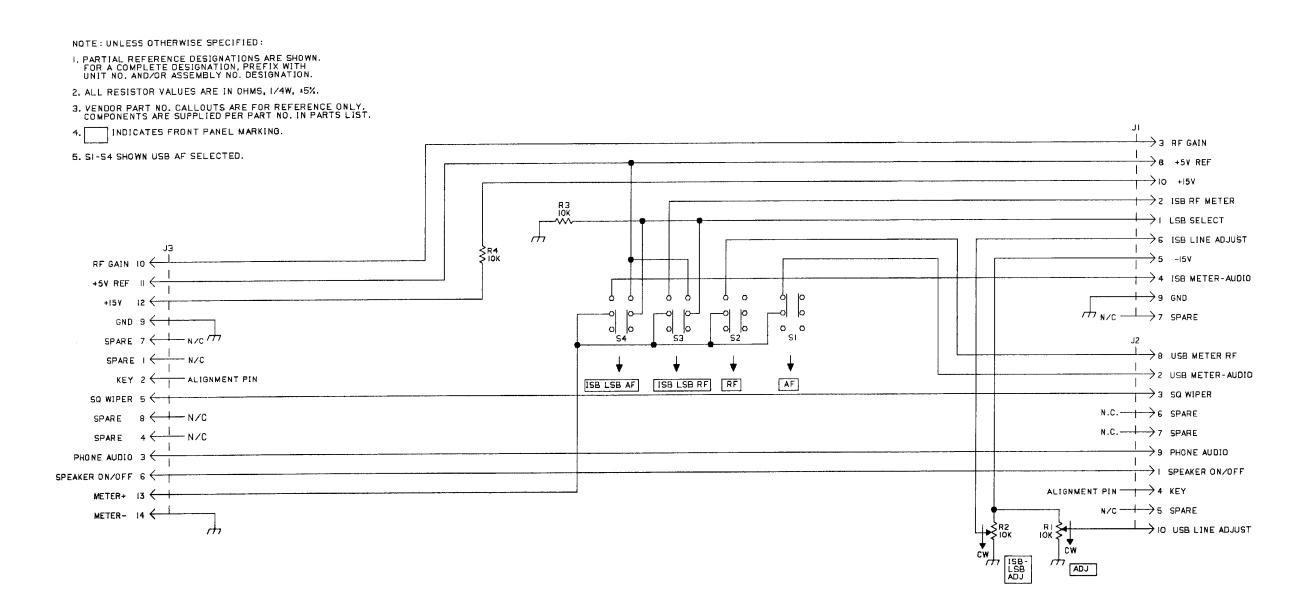

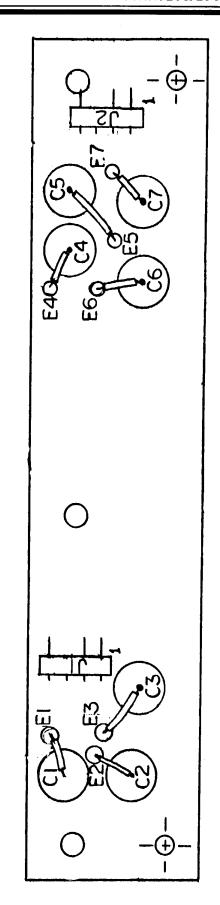

#### 2.8.2 Remote Control Interface Setup

The remote control interface circuit is located on the Control Assembly A14 and can be accessed when the front panel is folded down. See the Control Assembly A14 unit instruction section for locations of switches and jumpers. The interface must be configured for the particular application of the Receiver. The setup procedure includes:

- Enabling or disabling the interface

- Setting the baud rate

- Setting the unit ID

- Selecting the serial interface type

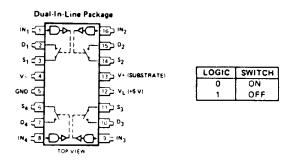

The control assembly has one serial interface that can be configured for a variety of standard interface types. For this application the interface must be configured for MIL-188. DIP switch S5 is used to enable the interface and configure the serial port. To enable or disable the remote control interface set switch S5-1 as follows:

Remote Control Enabled: S5-1 Closed

Remote Control Disabled: S5-1 Open

Note that when the remote control interface is disabled the REMOTE switch on the front panel will be disabled.

The serial interface is configured for MIL-188 using switches S5-2, and S5-4 thru S5-8, and jumper J19 on the A14 assembly. Switch S5-3 is not used for Remote Control configuration and should be closed. Switch settings and jumper positions for selecting the interface type are listed in table 2-4.

Table 2-4. Remote Control Interface Configuration Switch Setting

| Switch or<br>Jumper    | S5-2 | \$5-4 | <b>S5-5</b> | S <b>5-6</b> | S5-7 | S5-8 | A14J19 |

|------------------------|------|-------|-------------|--------------|------|------|--------|

| Setting or<br>Position | Open | Open  | Closed      | Closed       | Open | Open | 2 to 3 |

The serial interface baud rate is selected by a 16-position rotary switch, S4. Most popular baud rates between 50 and 19200 are selectable. All selectable baud rates and their corresponding switch settings are listed in table 2-5.

For systems that use multiple, remotely controlled receivers, each receiver must have its own ID number. The ID number is selected as an 8 bit binary number by setting the switches of DIP switch S3 Table 2-6 lists the eight switches and their weights.

The bit is high when the corresponding switch is open. A bit is low when the switch is closed. Decimal numbers between 0 and 255 are selectable. The decimal equivalent of the switch settings can be calculated by adding the weights assigned to each closed switch. Note that the ID and the baud rate are read into the memory only at power up or when the microprocessor is reset.

The unit ID and the baud rate can be displayed on the front panel when the receiver is in the remote mode. To display them on the alphanumeric display, simply press and hold the ENTER pushbutton for about 10 seconds.

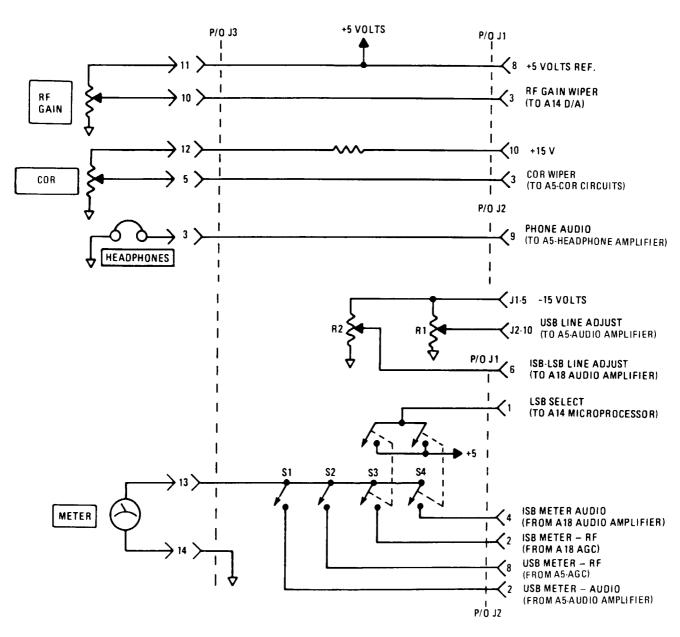

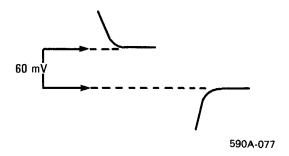

#### 2.8.3 USB, LSB and ISB Line Audio Output Level Adjust

USB and LSB line audio output levels are adjustable from the front panel. Multiturn adjustment potentiometers are accessed through holes located next to the USB and LSB meter select pushbutton switches on the front panel.

Table 2-5. Serial Interface Baud Rate Switch Settings

| S4 Position | Baud Rate |

|-------------|-----------|

| 0           | 50        |

| 1           | 75        |

| 2           | 110       |

| 3           | 134.5     |

| 4           | 150       |

| 5           | 300       |

| 6           | 600       |

| 7           | 1200      |

| 8           | 1800      |

| 9           | 2000      |

| Α           | 2400      |

| В           | Not Used  |

| С           | 4800      |

| D           | 7200      |

| Ε           | 9600      |

| F           | 19200     |

Table 2-6. ID Number Switch Weights

| Switch       | Weight |

|--------------|--------|

| <b>S3-1</b>  | 1      |

| S3-2         | 2      |

| \$3-3        | 4      |

| 53-4         | 8      |

| <b>S3-</b> 5 | 16     |

| \$3-6        | 32     |

| 53-7         | 64     |

| \$3-8        | 128    |

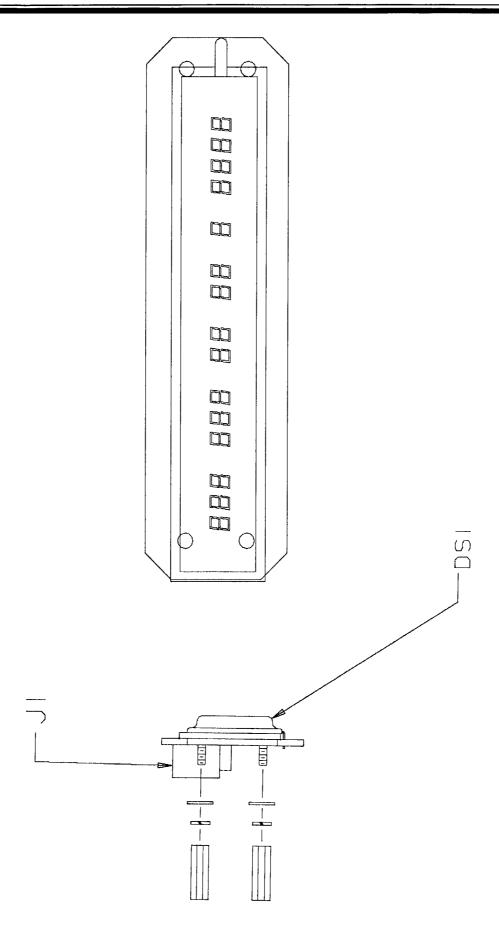

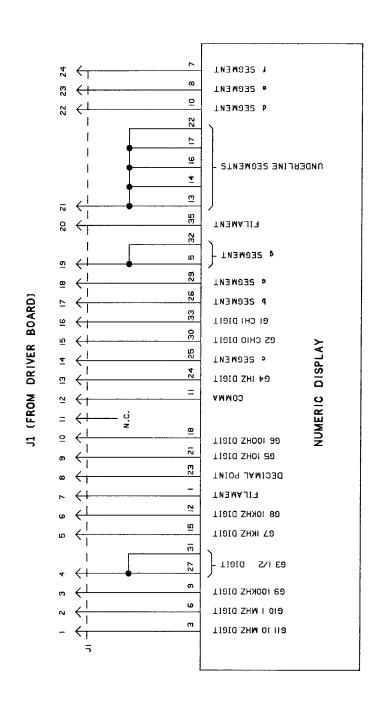

#### 2.8.4 Adjusting Front Panel Display Brightness

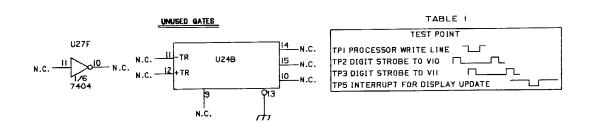

Potentiometer R29 on Front Panel Driver Board Assembly A13A2 is used to adjust the brightness of the vacuum fluorescent displays. R29 can be accessed by removing the top chassis cover. R29 can be adjusted with a small screwdriver and is identified in subsection A13.

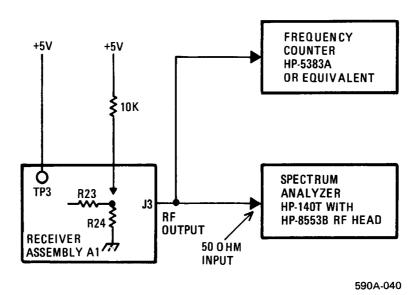

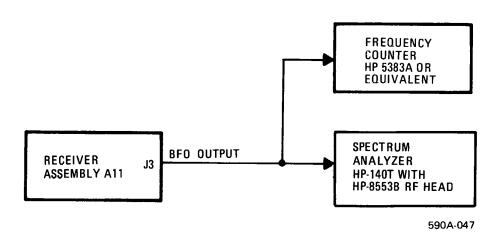

#### 2.9 FUNCTIONAL CHECKOUT PROCEDURE

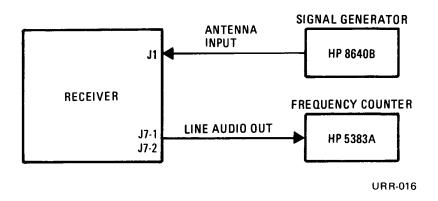

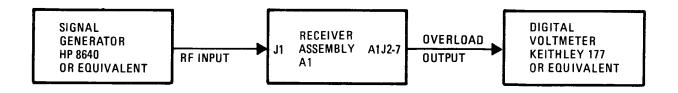

The following is a local control functional test to determine the satisfactory operation of the Receiver. The following equipment (or equivalent) is required.

- HP-8640B Signal Generator

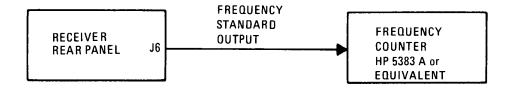

- HP-5383A Frequency Counter

The following paragraphs briefly describe and test Receiver operation. The operator may find it useful to read section 3, Operation, prior to or concurrently with this procedure. Connect the signal generator and frequency counter shown in figure 2-5.

Figure 2-5. Functional Test Setup

#### 2.9.1 Receive Mode Test

Apply the ac power and check that the receiver powers up with RCV (Receive), FREQUENCY, and TUNE LEDS lit. The receiver will run a self-test routine when turned on. The fault indicator will be lit during the test cycle but should go out shortly after that. If the unit fails, the fault indicator will remain lit and a fault code will be displayed. See the maintenance section for fault code definitions.

Set the receiver to the following initial conditions:

Mode: USB

RF Gain: Fully clockwise (cw)

AGC: MED

Connect the signal generator to the receiver's antenna input and set the generator for a level of -24 dBm (14.1  $mV_{rms}$ ) at any frequency.

#### 2.9.1.1 Frequency Entry

Press the FREQUENCY button and enter a frequency of 12.345678 MHz via the keypad. Press ENTER. Set the signal generator to a frequency 1 kHz above the receiver tuned frequency (12.346678) and note the 1-kHz

audible output tone. Connect the frequency counter to the line audio output and verify the audio frequency is 1 kHz.

#### 2.9.1.2 Tune Rate

Press TUNE RATE successively until the cursor is beneath the 1-kHz digit. Rotate the tuning wheel and use the signal generator to verify tuning in 1 kHz steps.

Press TUNE RATE to place the cursor beneath the 100-Hz digit and use the signal generator to verify tuning in 100 Hz steps.

Press TUNE RATE to place the cursor beneath the 10-Hz digit and use the signal generator to verify tuning in the 1 Hz steps.

#### 2.9.1.3 Mode Selection

Press the MODE button under the alphanumeric display and check that USB, LSB, ISB, FM, CW, and AM, are selectables as modes. Keeping the button pressed causes the display to scroll through the valid modes. Release the button and the receiver is placed into the selected mode.

#### 2.9.1.4 Bandwidth Selection

Press the BW button under the alphanumeric display and check that the bandwidth display scrolls through the filter selections that are valid for the selected mode. (Note that filter bandwidths are customer specified, and will vary depending on the requirements. A typical filter complement for different modes is shown in table 2-7.

Mode

Bandwidth

USB

2.7 kHz

LSB

2.7 kHz

CW

0.3 kHz

AM

6.0 kHz, 16.0 kHz

FM

16.0 kHz

Table 2-7. Typical Filter Complement

#### 2.9.1.5 AGC Selection

With the Receiver in the CW mode, press the AGC speed button beneath the alphanumeric display and check that the AGC speed selection scrolls from SLOW to FAST to MEDIUM until released.

#### 2.9.1.6 BFO Selection

Select the USB mode, and press the BFO button to enable BFO entries. Check that the BFO LED Lights and that keypad selections (followed by pressing ENTER) cause the BFO offset frequency to appear in the BFO display field.

Check that the tuning wheel varies the BFO selection when the TUNE LED is lit.

With the signal generator set for a frequency of 12.346678 and the receiver set at 12.345678, USB mode, tune the BFO via the tuning wheel to + 1 kHz and check that a zero beat is obtained.

Return the BFO frequency to 0.00 kHz.

#### 2.9.1.7 RF Gain

Set the front panel meter pushbuttons to measure USB RF level. Press the AGC ON/OFF button under the alphanumeric display to select AGC OFF. Verify that the AGC display changes to OFF and that the meter reading increases. Adjust the RF GAIN control and verify that the meter reading changes.

#### 2.9.1.8 AF Gain

Rotate the AF GAIN knob and check that the volume is adjustable.

#### 2.9.1.9 Load Memory Function

The channel programming memory allows up to 100 channels to be stored. Press the PROGRAM button to place the receiver in the Program mode, and check that the PROGRAM and CHANNEL LEDs light. Perform the following steps:

- a. Enter 01 via the keyboard.

- b. Press FREQUENCY and enter 01.111111 MHz via the keyboard. Press ENTER.

- c. Select AGC-SLO, MODE-USB.

- d. Press LOAD.

- e. Press CHANNEL and enter 02 via the keyboard.

- f. Press FREQUENCY and enter 02.222222 MHz via the keyboard. Press ENTER.

- g. Select AGC MED, MODE-LSB.

- h. Press LOAD.

- Press CHANNEL and enter 03.

- j. Push FREQUENCY and enter 03.333333 MHz. Press ENTER.

- k. Select AGC-FAST, MODE-CW, BW-0.3 kHz.

- Press LOAD.

- m. Press CHANNEL and enter 04.

- n. Press FREQUENCY and enter 04.444444 MHz. Press ENTER.

- Select AGC-MED, MODE-CW, BW-0.3 kHz.

- p. Press LOAD.

- q. Press RECEIVE to leave the Program mode.

#### 2.9.1.10 Channelized Reception

With the Receiver in the Receive Mode (RCV LED lit), press the CHANNEL button. (CHANNEL LED should light.) Select each channel number (followed by ENTER) listed in table 2-8. Check that the receiver front panel updates to number listed. Using the signal generator, check that the receiver has in fact tuned to the frequency listed.

Channel Frequency MHz AGC Mode Bandwidth kHz 01 01.111111 SLO USB 2.7 02 02.22222 MED LSB 2.7 03 03.333333 **FST** CW 0.3 04.44444 04 MED CW 0.3

**Table 2-8. Programmed Channels**

With the TUNE and CHANNEL LEDs lit, rotate the tuning wheel. Check that channels 1-4 are selected.

#### 2.9.1.11 Local/Remote Switch

The following test applies only if the remote control interface is enabled. If not, the REMOTE button will have no effect. With the Receiver under local control, press the REMOTE button and check that the REMOTE LED lights and that it is no longer possible to change Receiver parameters via the front panel. Make sure that by pressing the REMOTE button a second time, the Receiver is placed back under local control.

#### 2.9.1.12 Meter Switch

Set the Receiver in the following conditions:

• Frequency: 12.345678

Mode: USB

AGC: MED

• RF Gain: Fully clockwise (cw)

AF Gain: As desired

Set the signal generator to a frequency of 12.346678 MHz and a level of -24 dBm (14.1 mV $_{rms}$ ).

Press the USB/RF pushbutton under the meter. The meter indication should be approximately 14 mV<sub>rms</sub>.

Press the USB/AF pushbutton under the meter. The meter indication should be approximately 0 dBm unless the meter has been set to indicate some other level.

Note that the USB positions select USB information and the ISB-LSB positions select LSB information.

#### 2.9.1.13 COR Control

Set receiver as in paragraph 2.9.1.11. Verify COR operation as the COR control is varied. The COR should be energized and deenergized as the COR threshold is adjusted above and below the carrier levels. Check for continuity between J7-10 and J7-22, J7-23.

#### 2.9.2 Program Mode

#### **NOTE**

Channels 1 through 4 were previously programmed in step 2.9.1.9 of this procedure.

#### 2.9.2.1 Recall Memory Function

Place the receiver in the Program mode. Enter 02 via the keyboard and press RECALL. The display should update to 02.222222 MHz, CHANNEL-02, AGC-MED, MODE-LSB.

#### 2.9.2.2 Program Group Function

Group programming of channels allows the preprogramming of up to 10 channel groups (20 channels per group maximum). Channels may be programmed in any order and any channel can appear in more than one group.

To program a group, place the receiver in the Program mode and perform the following steps:

- a. Press GROUP.

- b. Enter the number 1 via the keyboard in response to the prompt GROUP NUMBER?. Press ENTER.

- c. Enter 03 via the keyboard in response to the prompt CHANNEL NUMBER?, and press ENTER and LOAD. The display will respond with 03 OK.

- d. Enter 02, followed by ENTER and LOAD.

- e. Enter 01, followed by ENTER and LOAD.

- f. Exit programming by pushing RECEIVE.

- g. Proceed to 2.9.3. Verification of Group programming will be done during the Group scan test.

#### 2.9.3 Scan Mode Test

The following two scan modes are available on the Receiver:

- Channel scan

- Group scan

Channel scan allows the automatic sequential scanning of up to 100 programmed channels. Group scan allows scanning of up to ten groups (20 channels per group, maximum). Follow the steps in paragraph 2.9.3.1 to perform a Channel scan and the steps in 2.9.3.2 to perform a Group scan.

#### 2.9.3.1 Channel Scan

- a. With the Receiver in RECEIVE MODE, press SCAN. SCAN LED should light.

- b. Press CHANNEL in response to GROUP or CHANNEL SCAN?.

- c. Enter 01 followed by ENTER in response to FIRST CHANNEL?.

- d. Enter 04 followed by ENTER in response to LAST CHANNEL?. The Receiver should commence to automatically scan channels 1-4. Press SCAN; verify that the scanning stops. Verify that pressing SCAN again restarts scanning. Verify that pushing the DWELL button affects the dwell speed accordingly.

#### 2.9.3.2 Group Scan

- a. Push the RECEIVE button, then SCAN.

- b. Press GROUP In response to the GROUP or CHANNEL SCAN? prompt.

- c. Enter 1 via the keyboard, followed by ENTER. The Receiver should now scan channels 3, 2, 1 in that order.

#### 2.9.4 Self-Test (BITE)

Press the TEST button to begin the Receiver's self-diagnostics. The Receiver will perform an automatic self-test, approximately 5 seconds in length. During this time, all front panel display segments and LEDs should light, and stay lit until the message --- TEST PASSED --- appears in the left-hand display.

In the event of a failure, a Receiver fault code will be displayed. If this occurs, consult the maintenance section of this manual, table 5-1, which lists the fault codes by assembly number.

#### 2.9.5 Reconnection

After the checkout is complete, disconnect the signal generator and the frequency counter. Reconnect the antenna and audio output lines, if used.

#### **SECTION 3**

#### **OPERATION**

#### 3.1 INTRODUCTION

The following paragraphs describe the function of the front panel controls and indicators and the basic operational modes of the Receiver. Operation of the Receiver is not difficult but should not be attempted before reading this section. This section begins with descriptions of the front panel controls and indicators. The controls and indicators have been broken up into functional groups for the purpose of discussion. Normal (non-programmed) operation is discussed immediately following the control and indicator descriptions. That discussion is followed by programming instructions and channelized operating procedures for a programmed receiver. Programmed operation includes channel and group scanning.

#### 3.2 CONTROLS AND INDICATORS

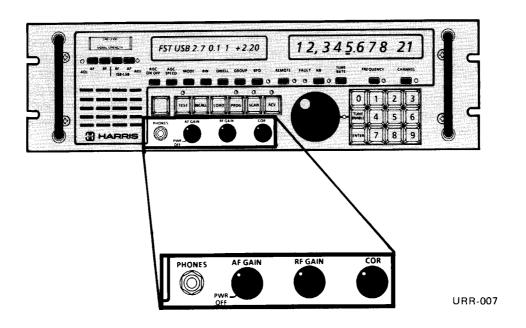

#### 3.2.1 Power, AF Gain, RF Gain, and COR

The power on/off, AF Gain, RF Gain, and COR controls are shown and described in figure 3-1. The receiver power control is combined with the audio gain (AF GAIN) control. The receiver is off when the knob is rotated fully counterclockwise. Rotate the knob clockwise past the click stop to turn the Receiver on. Rotate the knob clockwise to increase the audio amplifier gain and the volume level at the headphones. The RF GAIN control knob is used to manually control the radio frequency amplifier. The COR control sets the threshold at which the carrier operated relay is energized. Rotate the knob clockwise to raise the threshold.

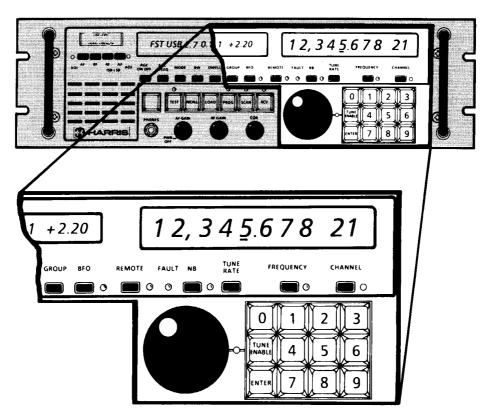

### 3.2.2 Tuning Wheel and Keypad Entries for Channel, Frequency, BFO, and Group

The operating frequency, channel, BFO, and group are displayed on the front panel as shown and described in figure 3-2. These displays can be changed using the keypad, or, except for the GROUP display, the tuning wheel. The keypad or tuning wheel is dedicated to one display at a time as selected by the switches under the displays. LEDs located next to the switches light to identify the active display. To use the tuning wheel, press and release the TUNE ENABLE button located in the keypad matrix. An LED located between the tuning wheel and the TUNE ENABLE button will be lit when the wheel is active.

When using the tuning wheel to scan or select frequencies, the operator can change the sensitivity of the wheel. The resolution is defined as total frequency change per turn of the wheel and is selected by using the TUNE RATE pushbutton located below the frequency display. This pushbutton changes the position of a cursor located below the digits in the frequency display. The cursor position selects the associated digit as the tuning unit. If the cursor is in the 1-kHz position, the tuning wheel will raise or lower the frequency in 1-kHz increments. With the cursor in the 10-kHz position, the wheel will raise or lower the frequency in 10-kHz increments. The 10-MHz cursor position is not allowed and will effectively disable the tuning wheel when selected.

Channel groups are used only in the Scan mode. Groups do not have to be entered for other modes of operation. See the operating procedures for proper entry of group numbers.

| CONTROL/<br>INDICATOR | FUNCTION                                                                                                                    | CONTROL/<br>INDICATOR | FUNCTION                                                                                                |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------|