#### **TECHNICAL MANUAL**

# OPERATOR'S, ORGANIZATIONAL, DIRECT SUPPORT, AND GENERAL SUPPORT MAINTENANCE MANUAL

## COUNTER, PULSE, ELECTRONIC TD-1338(V)1/USM

(NSN 6625-01-120-7832)

## SAFETY STEPS TO FOLLOW IF SOMEONE IS THE VICTIM OF ELECTRICAL SHOCK

- DO NOT TRY TO PULL OR GRAB THE INDI-VIDUAL

- (2) IF POSSIBLE, TURN OFF THE ELECTRICAL POWER

- IF YOU CANNOT TURN OFF THE ELECTRICAL POWER, PULL, PUSH, OR LIFT THE PERSON TO SAFETY USING A WOODEN POLE OR A ROPE OR SOME OTHER INSULATING MATERIAL

- 4 SEND FOR HELP AS SOON AS POSSIBLE

- 5 AFTER THE INJURED PERSON IS FREE OF CONTACT WITH THE SOURCE OF ELECTRICAL SHOCK, MOVE THE PERSON A SHORT DISTANCE AWAY AND IMMEDIATELY START ARTIFICIAL RESUSCITATION

TECHNICAL MANUAL

NO. 11-6625-3031-14

HEADQUARTERS

DEPARTMENT OF THE ARMY

WASHINGTON, D.C. 6 May 1983

#### OPERATOR'S, ORGANIZATIONAL, DIRECT SUPPORT AND GENERAL SUPPORT MAINTENANCE MANUAL

**FOR**

#### COUNTER, PULSE, ELECTRONIC TD-1338(V)1/USM

(NSN 6625-01-120-7832)

#### REPORTING ERRORS AND RECOMMENDING IMPROVEMENTS

You can help improve this manual. If you find any mistakes or if you know of a way to improve the procedures, please let us know. Mail your letter, DA Form 2028 (Recommended Changes to Publications and Blank Forms), or DA Form 2028-2 located in the back of this manual direct to: Commander, US Army Communications-Electronics Command and Fort Monmouth, ATTN: DRSEL-ME-MP, Fort Monmouth, NJ 07703.

In either case, a reply will be furnished direct to you.

#### **TABLE OF CONTENTS**

|           |                                                 | Para  | Page |

|-----------|-------------------------------------------------|-------|------|

| Chapter 1 | . INTRODUCTION                                  |       |      |

| Section I | . General Information                           |       | 1-1  |

|           | Scope                                           | . 1-1 | 1-1  |

|           | reports                                         | . 1-2 | 1-1  |

|           | Administrative storage                          | . 1-3 | 1-1  |

|           | Destruction of Army electronics materiel        | . 1-4 | 1-1  |

|           | Reporting equipment improvement recommendations |       |      |

|           | (EIR's)                                         | . 1-5 | 1-1  |

|           | Warranty information                            | . 1-6 | 1-1  |

| II        | Equipment Description                           | •     | 1-2  |

|           | Equipment characteristics, capabilities and     |       |      |

|           | features                                        | . 1-7 | 1-2  |

|           | Equipment data                                  | . 1-8 | 1-2  |

| III       | . Technical Principles of Operation             | •     | 1-4  |

|           | Counter functional operation                    | . 1-9 | 1-4  |

#### TABLE OF CONTENTS - Continued

| Para       | Page                                                                                                                                                  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | 1-6<br>1-8                                                                                                                                            |

|            |                                                                                                                                                       |

|            | 2-1                                                                                                                                                   |

|            | 2-1<br>2-1                                                                                                                                            |

|            | 2-5<br>2-5                                                                                                                                            |

|            | 2-5<br>2-6<br>2-7                                                                                                                                     |

|            | 2-7<br>2-7<br>2-8                                                                                                                                     |

| 2-8<br>2-9 | 2-10<br>2-10                                                                                                                                          |

| 2-11       | 2-11<br>2-11                                                                                                                                          |

| 2-13       | 2-11<br>2-12<br>2-13                                                                                                                                  |

|            | 2-13                                                                                                                                                  |

|            | 3-1<br>3-1                                                                                                                                            |

| 3-4        | 3-3<br>3-3                                                                                                                                            |

| 3-6        | 3-3<br>3-3<br>3-3                                                                                                                                     |

|            | 3-3                                                                                                                                                   |

|            |                                                                                                                                                       |

|            | 4-1                                                                                                                                                   |

| 4-2        | 4-1<br>4-1                                                                                                                                            |

| 4-3        | 4-1<br>4-1                                                                                                                                            |

|            | 4-1<br>4-1                                                                                                                                            |

|            | 4-2<br>4-17<br>4-17                                                                                                                                   |

| 4-8        | 4-17<br>4-20<br>4-28                                                                                                                                  |

|            | 2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>2-9<br>2-10<br>2-11<br>2-12<br>2-13<br>2-14<br>2-15<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>4-1<br>4-2<br>4-3 |

#### TABLE OF CONTENTS - Continued

|             |                                                    | Para | Page                 |

|-------------|----------------------------------------------------|------|----------------------|

| Section V.  | Preparation for Storage or Shipment                |      | 4-33<br>4-33<br>4-33 |

| Appendix A. | . REFERENCES                                       |      | A-1                  |

| Appendix B. | . MAINTENANCE ALLOCATION                           |      | B-1                  |

| Appendix C. | COMPONENTS OF END ITEM AND BASIC ISSUE ITEMS LISTS |      | C-1                  |

| Appendix D. | . ADDITIONAL AUTHORIZATION LIST                    |      | D-1                  |

| Appendix E. | . EXPENDABLE SUPPLIES AND MATERIALS LIST           |      | E-1                  |

#### LIST OF ILLUSTRATIONS

| Figure | Title                                                                            | Page   |

|--------|----------------------------------------------------------------------------------|--------|

| 1-1    | Counter, Pulse, Electronic TD-1338(V)1/USM                                       |        |

| 1-2    | Counter, Functional Block Diagram                                                |        |

| 1-3    | Basic Counter Al, Functional Block Diagram                                       |        |

| 1-4    | Converter A2, Functional Block Diagram                                           | 1-9    |

| 2-1    | Counter Front Panel                                                              |        |

| 2-2    | Counter Rear Panel                                                               |        |

| 2-3    | Pulse Profile Measurement Test Setup                                             |        |

| 2-4    | Pulse Profile Measurement                                                        |        |

| 2-5    | Time Varying Signal Measurement Test Setup                                       |        |

| 2-6    | Internal Timing Delays                                                           |        |

| 2-7    | GPIB Capabilities and Structure                                                  |        |

| 2-8    | GPIB IEEE STD 488/1975 ADDRESS SWITCH Positions                                  | 2-16   |

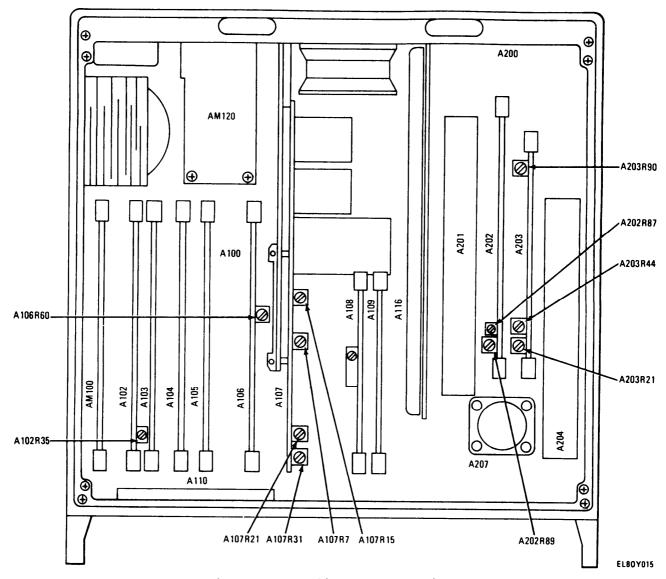

| 4-1    | Subassembly and Cable Locations                                                  |        |

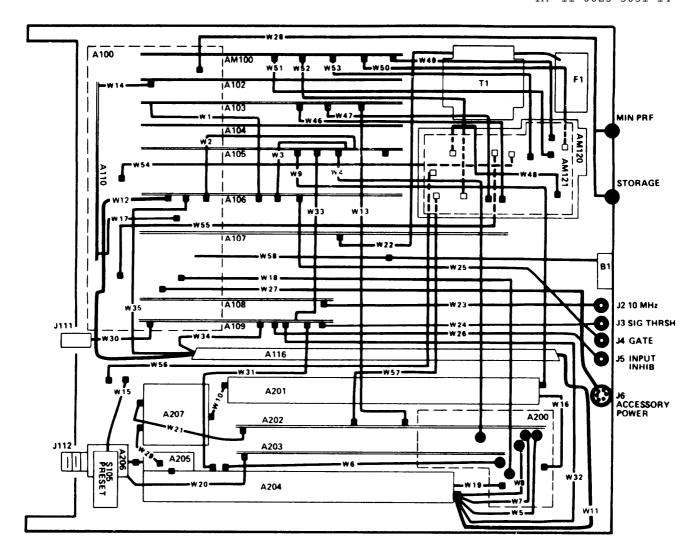

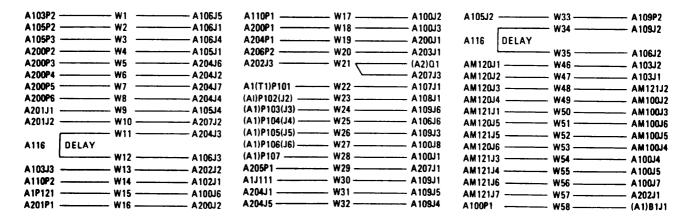

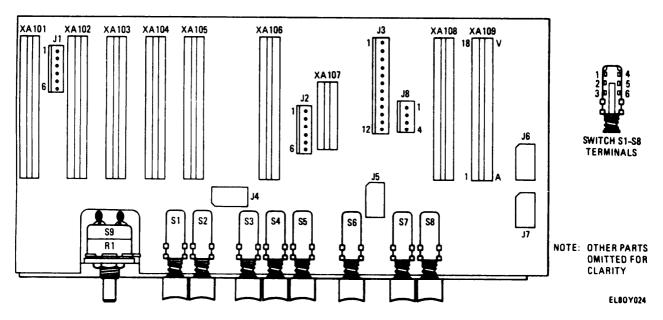

| 4-2    | Counter Interconnect A100, Connector and Switch Locations                        |        |

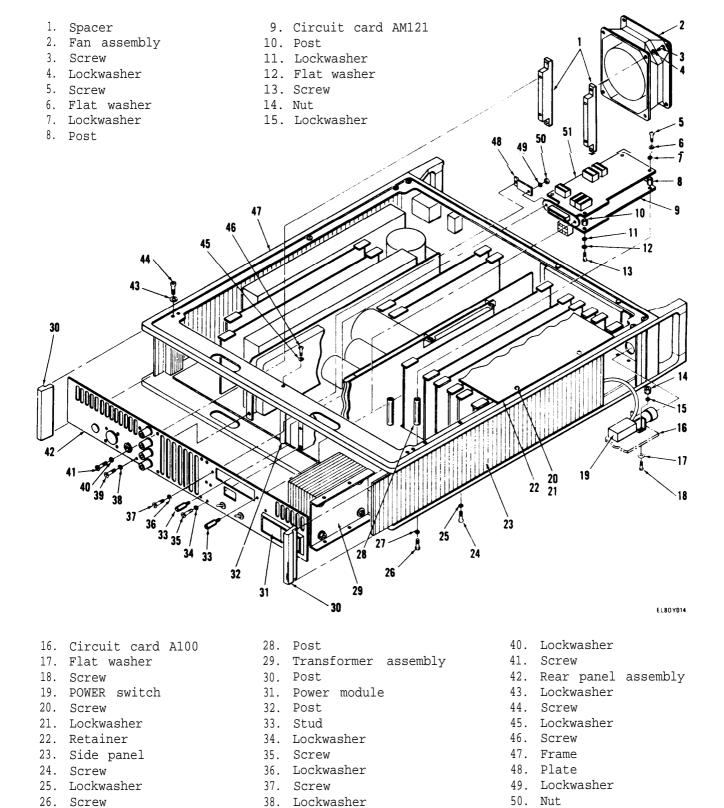

| 4-3    | Counter, Partial Exploded View                                                   |        |

| 4-4    | Adjustment Locations                                                             |        |

| 4-5    | Pulse Generator Output                                                           |        |

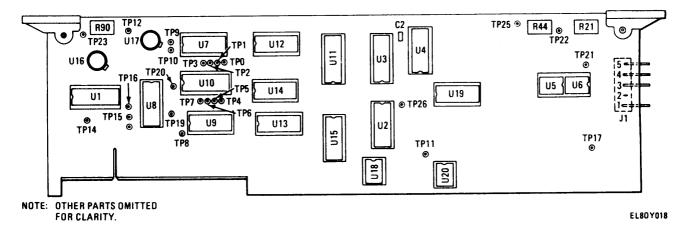

| 4-6    | YIG Control A202, Adjustment and Test Point Locations                            |        |

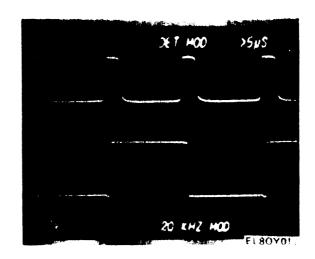

| 4-7    | Detected Modulation and 20 kHz Reference Pulse Timing                            | 4-24   |

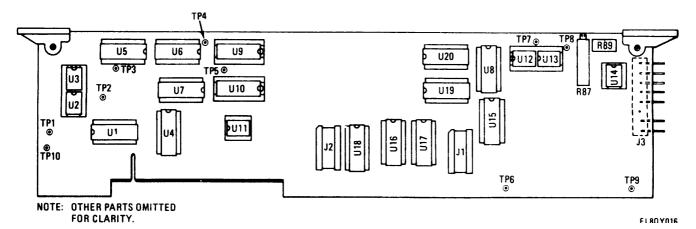

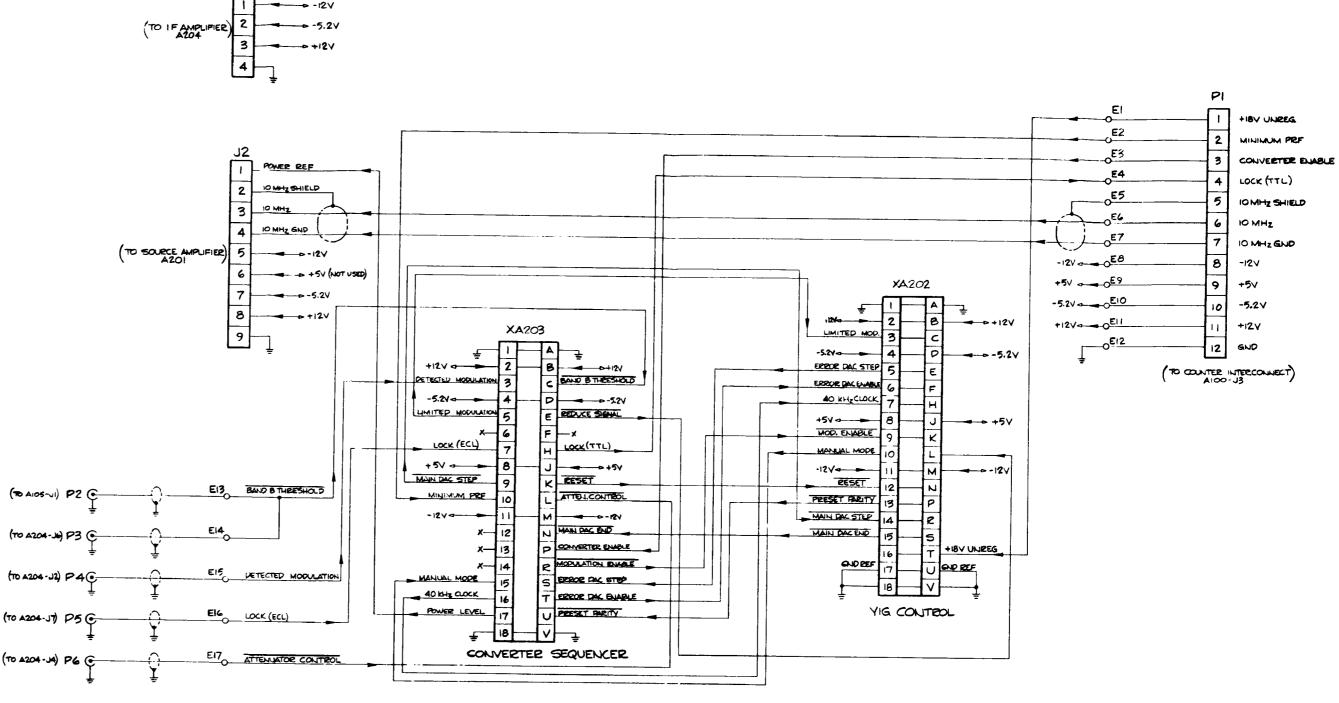

| 4-8    | Converter Sequencer A203, Adjustment and Test Point Locations                    | 1-26   |

| 4-9    | Return Loss Measurement Setup                                                    |        |

| 4-10   | Return Loss Measurement Waveform                                                 |        |

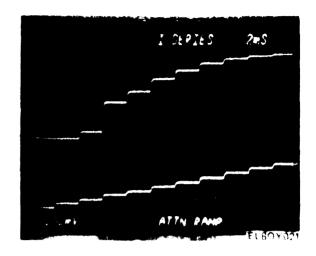

| 4-11   | Typical Attenuator Control Ramp Offset                                           |        |

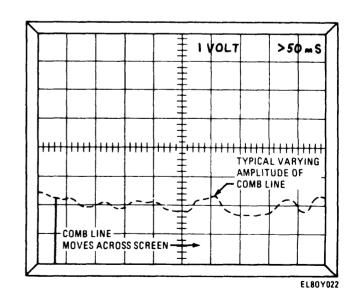

| 4-12   | Comb Line                                                                        |        |

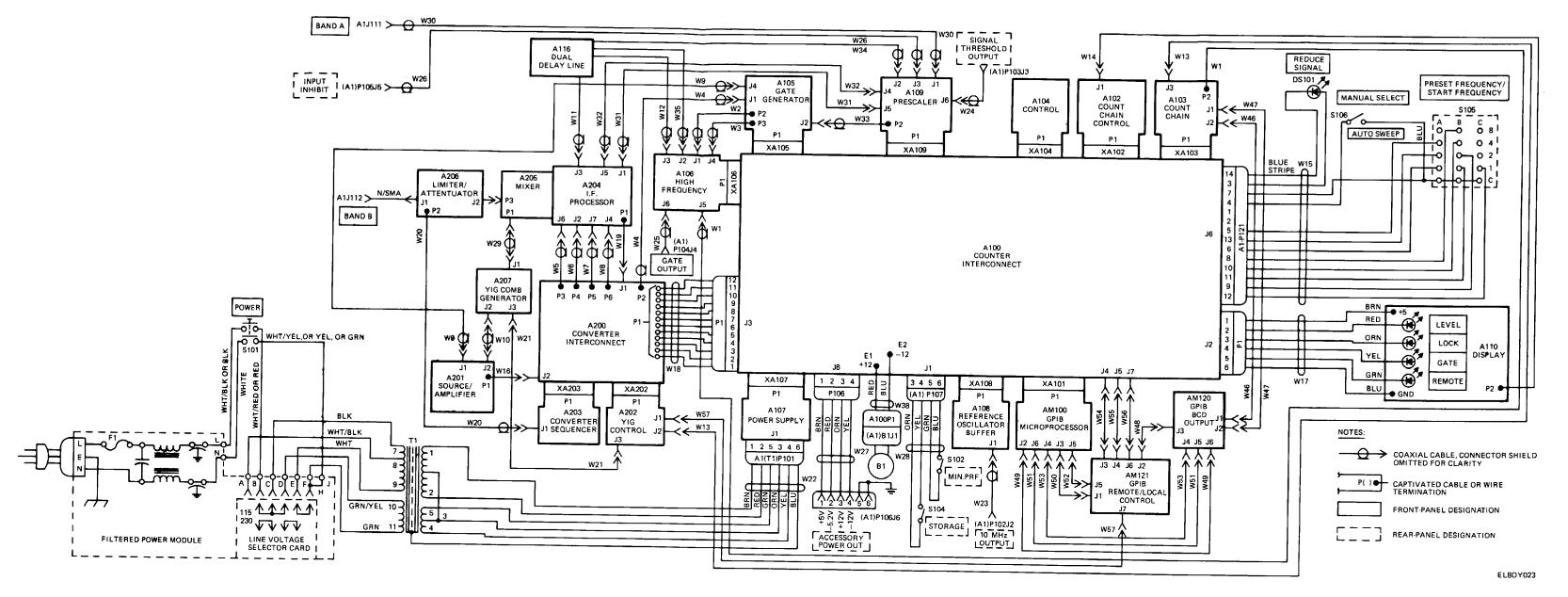

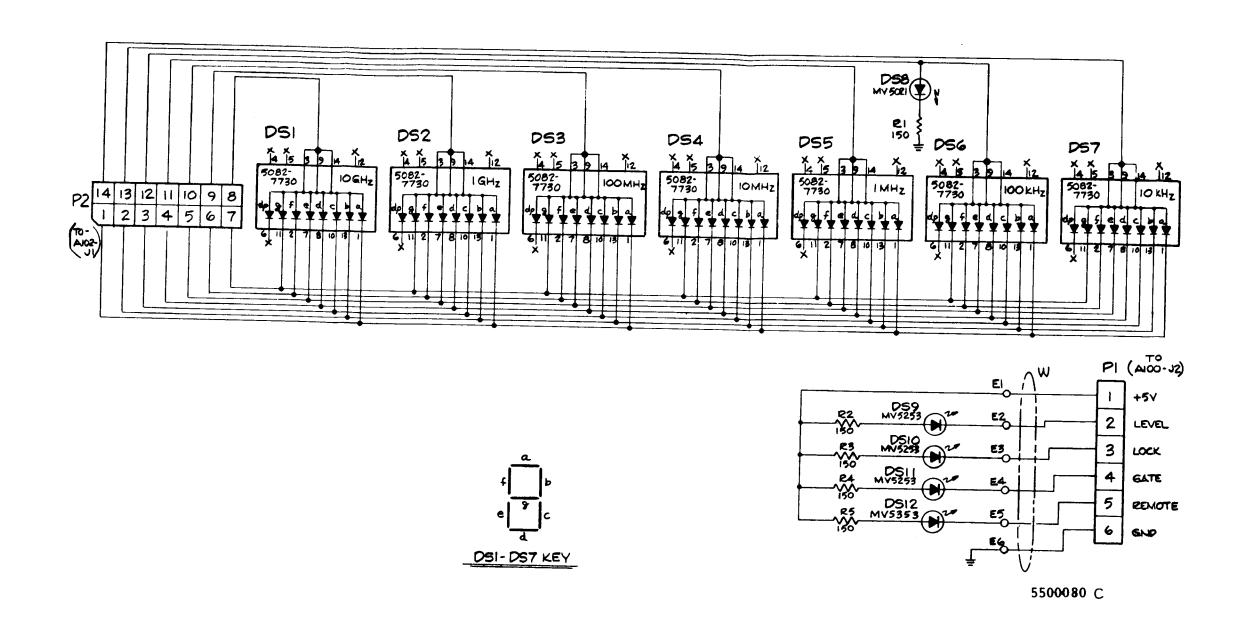

| FO-1   | Counter Interconnection Schematic Diagram                                        |        |

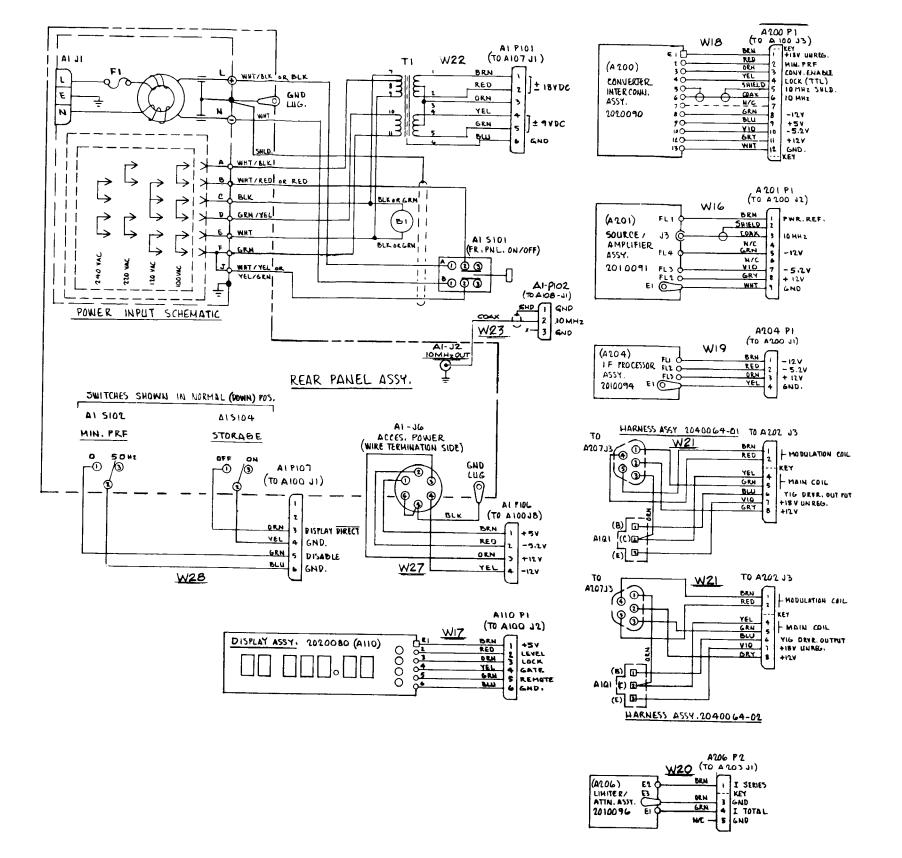

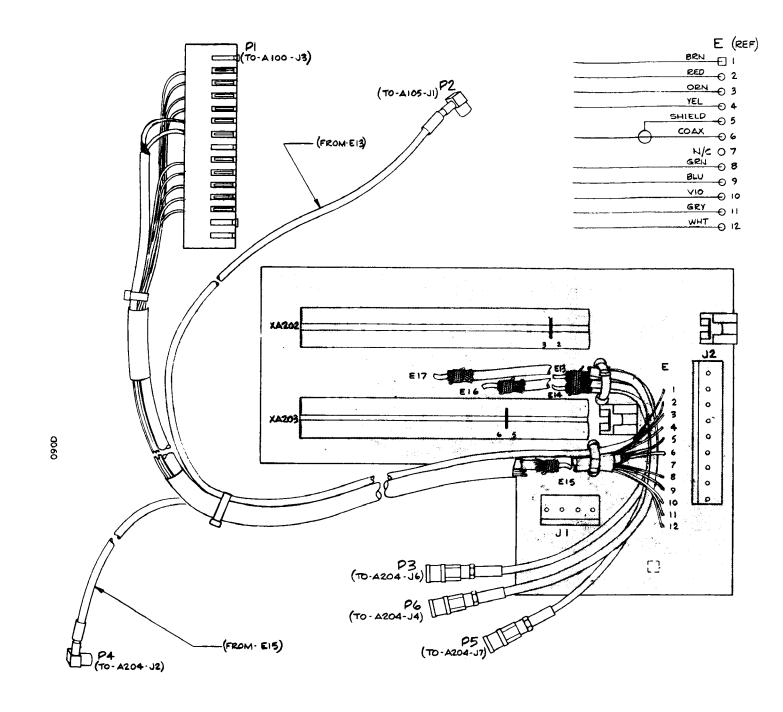

| FO-2   | Interconnection Diagram, Detailed Technical Schematic                            |        |

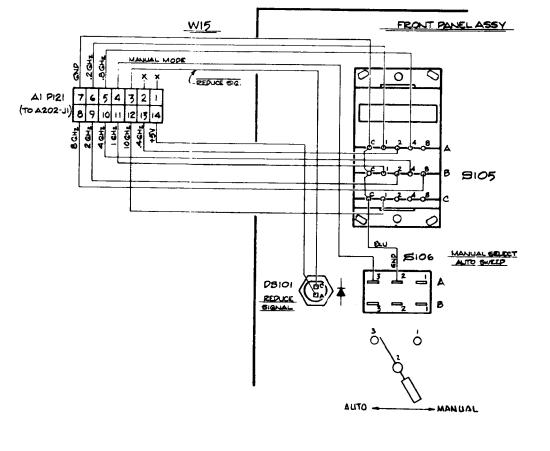

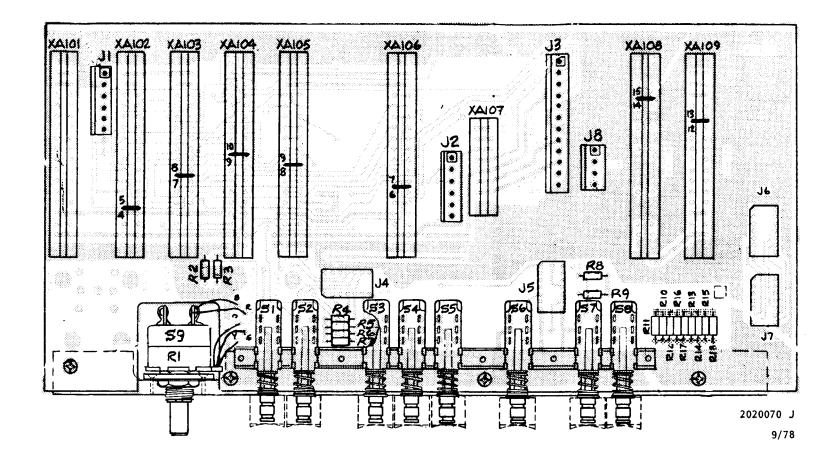

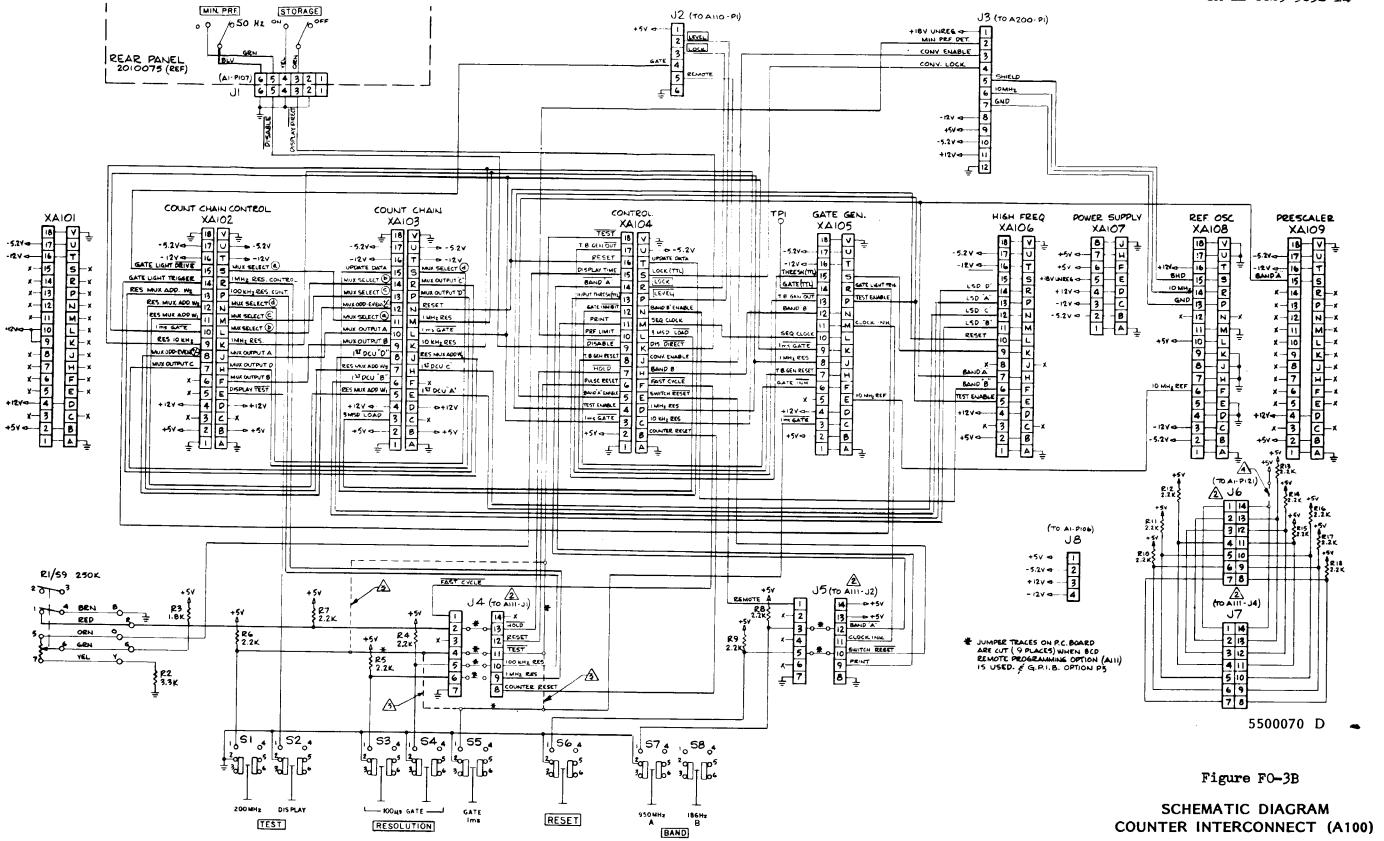

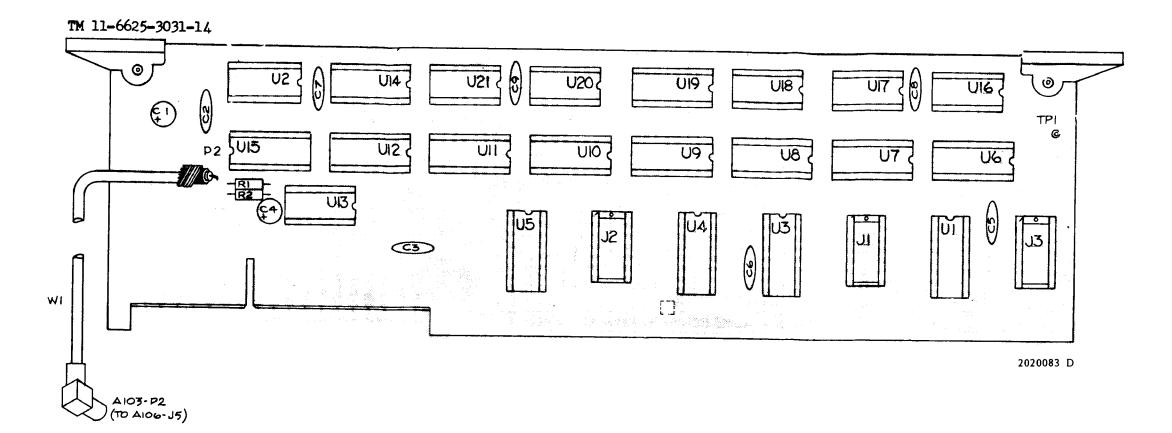

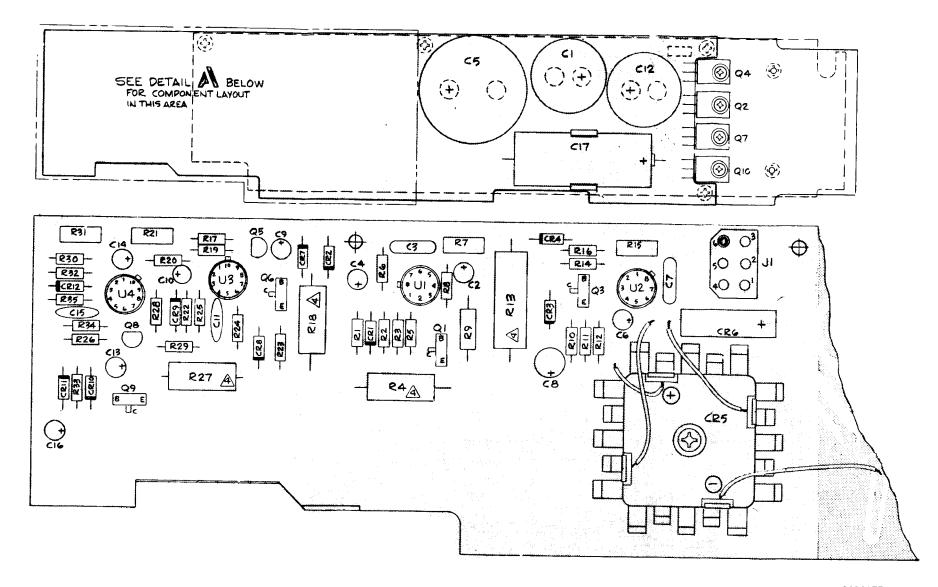

| FO-3A  | Component Locator Counter Interconnect (A100)                                    |        |

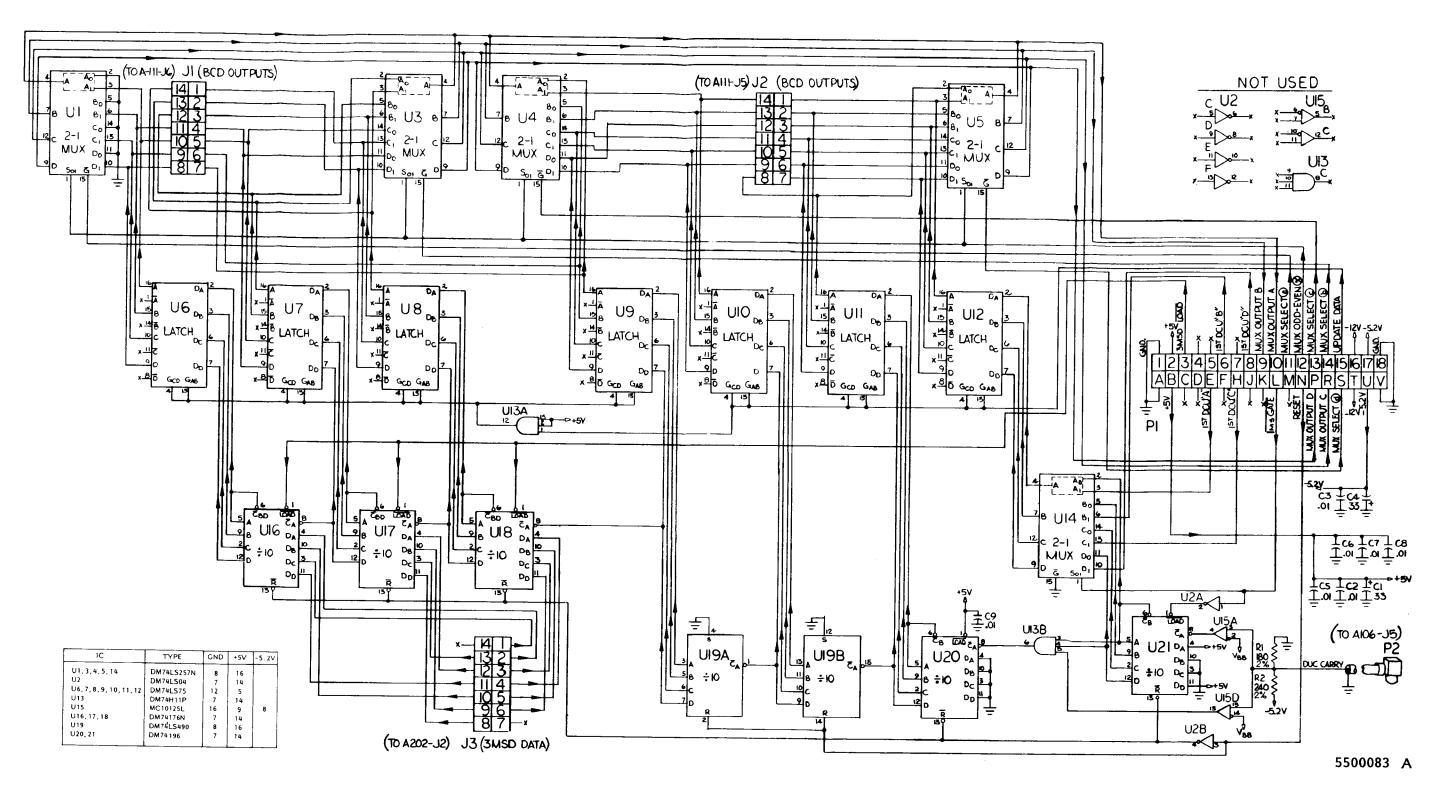

| FO-3B  | Schematic Diagram Counter Interconnect (A100)                                    |        |

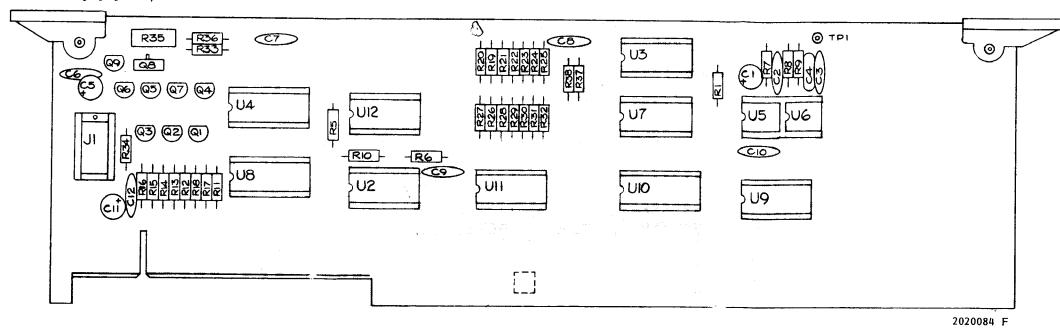

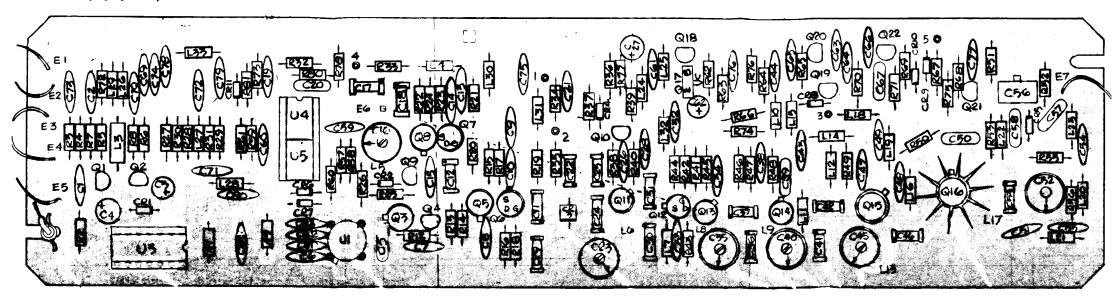

| FO-4A  | Component Locator and Descriptive Information Count Chain Control                | (A102) |

| FO-4B  | Schematic Diagram Count Chain Control (A102)                                     |        |

| FO-5A  | Component Locator and Descriptive Information Count Chain (A103)                 |        |

| FO-5B  | Schematic Diagram Count Chain (A103)                                             |        |

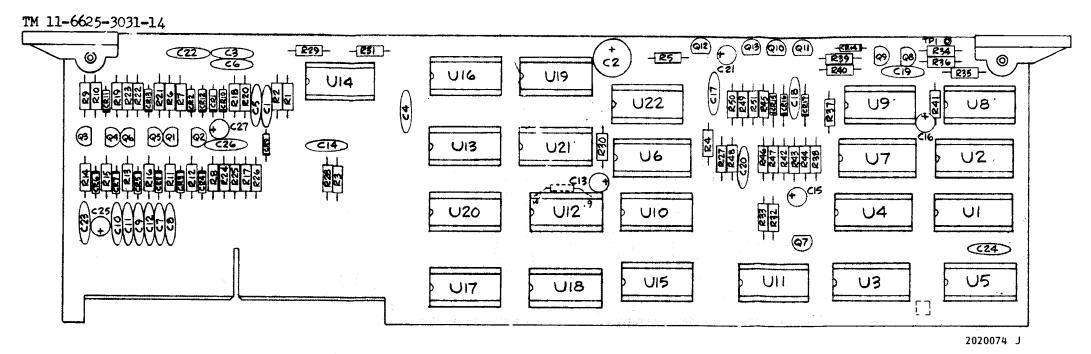

| FO-6A  | Component Locator and Descriptive Information Control (A104)                     |        |

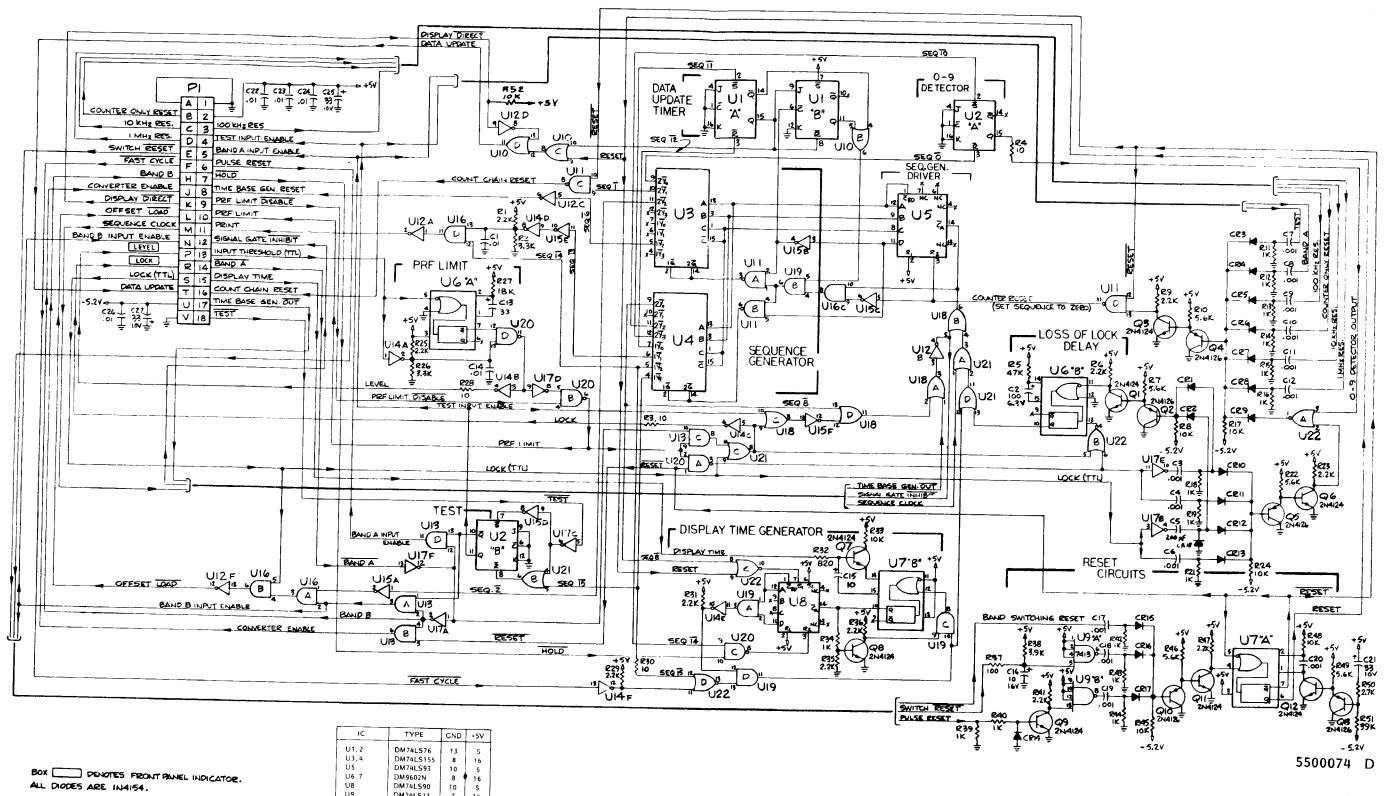

| FO-6B  | Schematic Diagram Control (A104)                                                 |        |

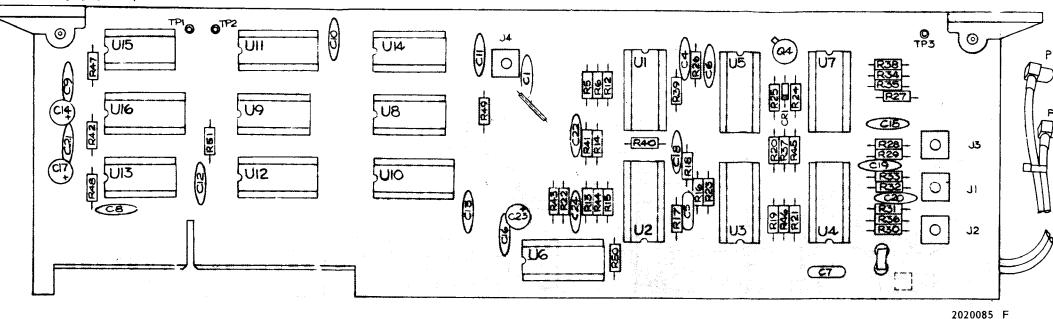

| FO-7A  | Component Locator and Descriptive Information Gate Generator (A105)              | )      |

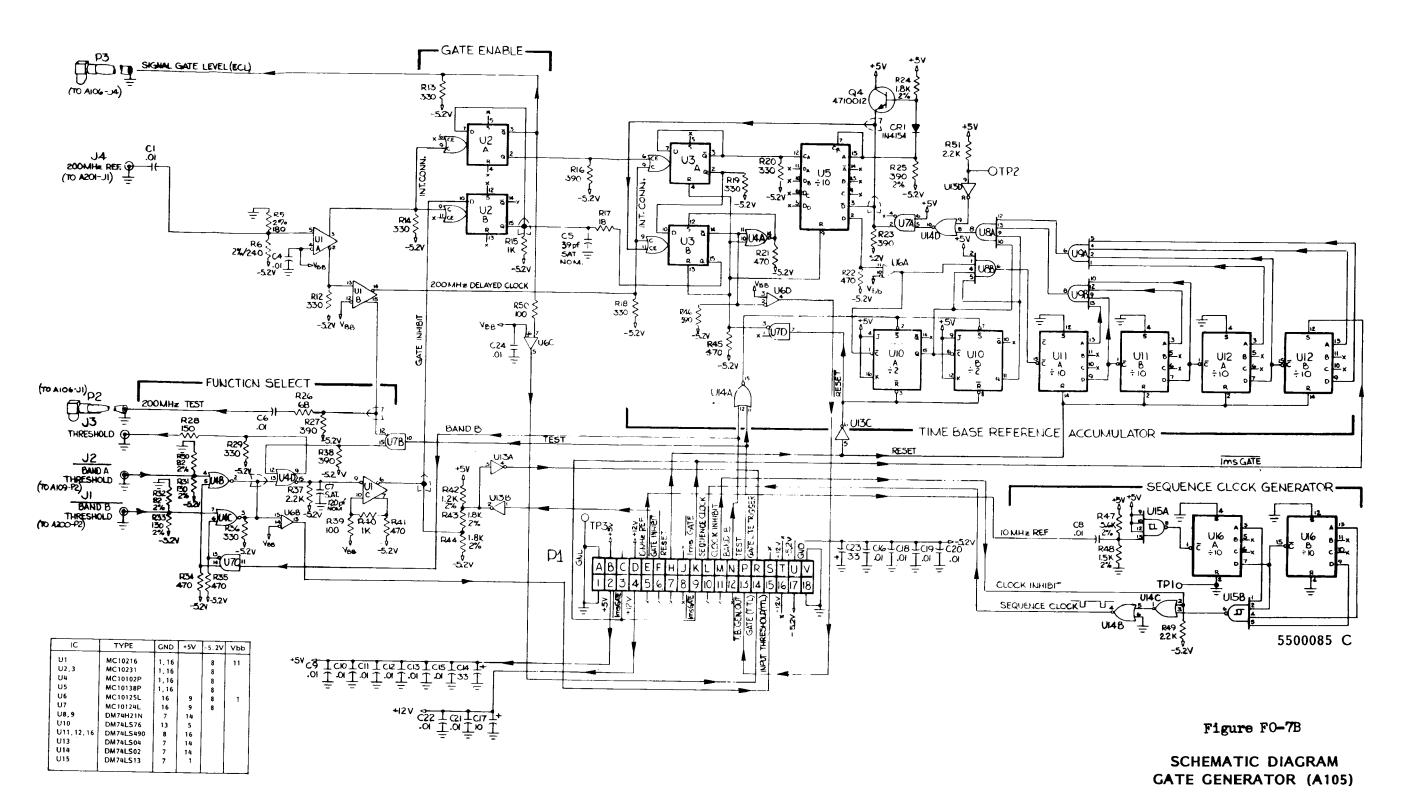

| FO-7B  | Schematic Diagram Gate Generator (A105)                                          |        |

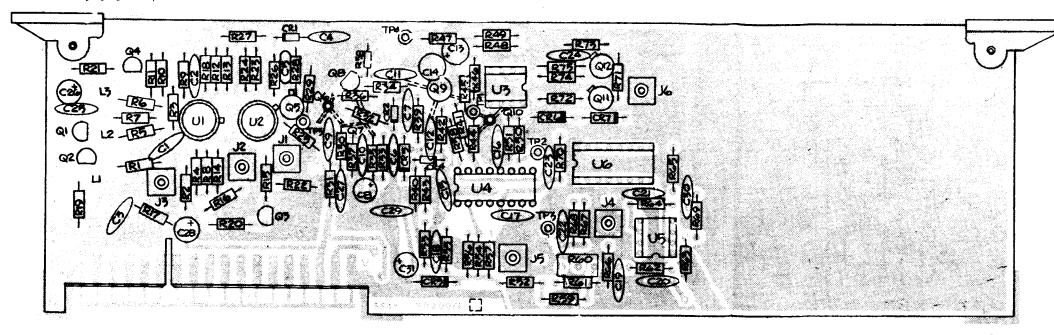

| FO-8A  | Component Locator and Descriptive Information High Frequency (A106)              | )      |

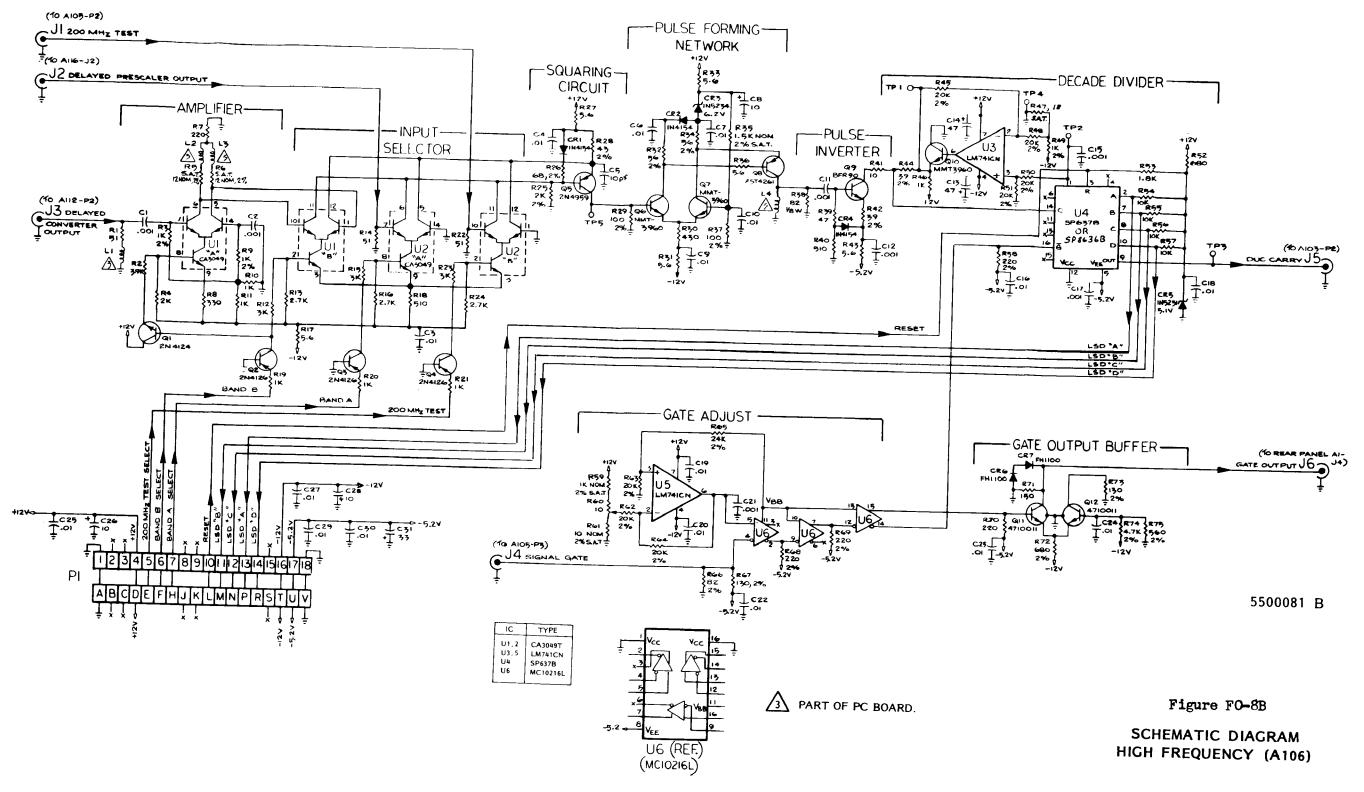

| FO-8B  | Schematic Diagram High Frequency (A106)                                          |        |

| FO-9A  | Component Locator and Descriptive Information Power Supply (A107)                |        |

| FO-9B  | Schematic Diagram Power Supply (A107)                                            |        |

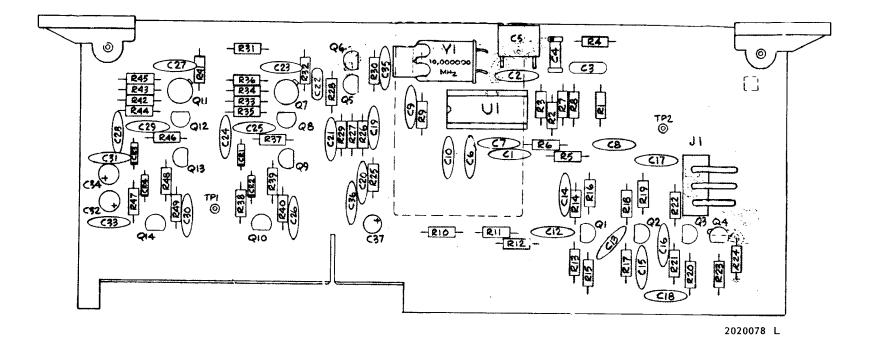

| FO-10A | Component Locator and Descriptive Information Reference Oscillator Buffer (A108) |        |

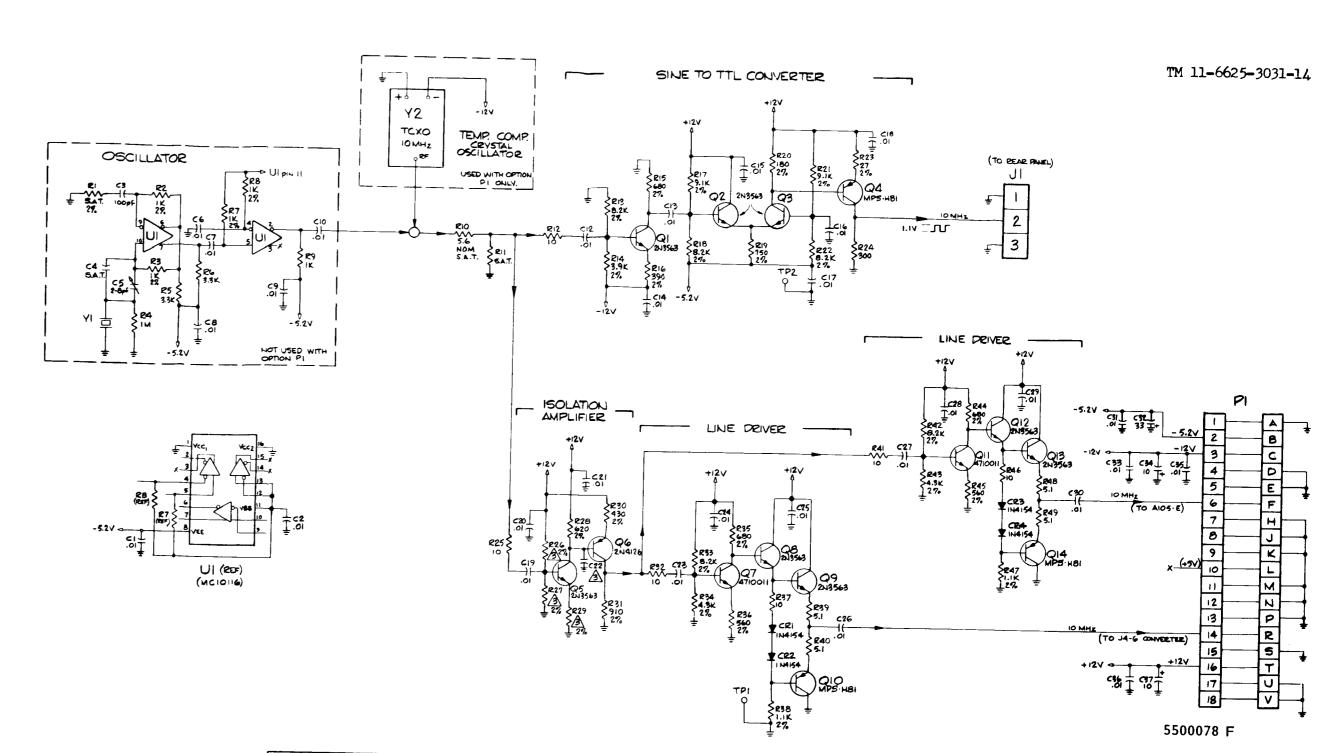

| FO-10B | Schematic Diagram Reference Oscillator Buffer (A108)                             |        |

#### LIST OF ILLUSTRATIONS (Continued)

| Figure |           |         | Title                                                 |

|--------|-----------|---------|-------------------------------------------------------|

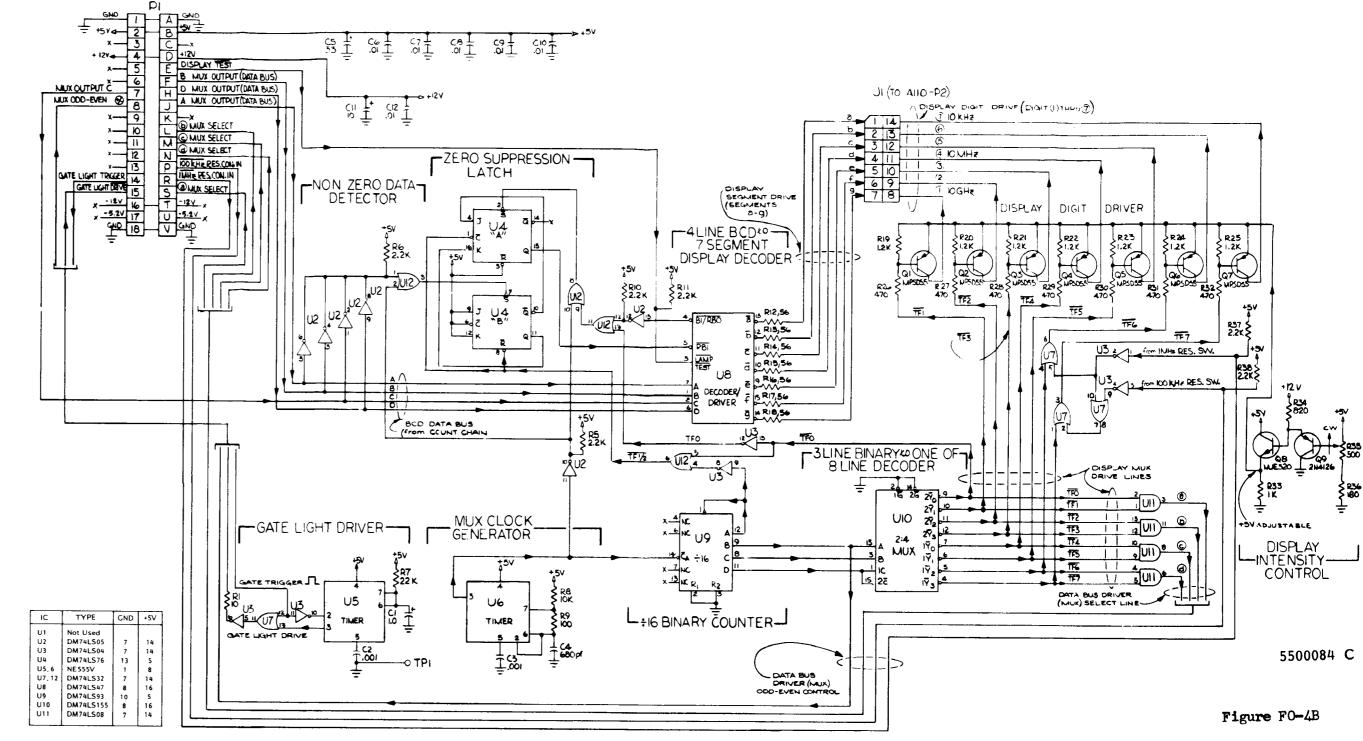

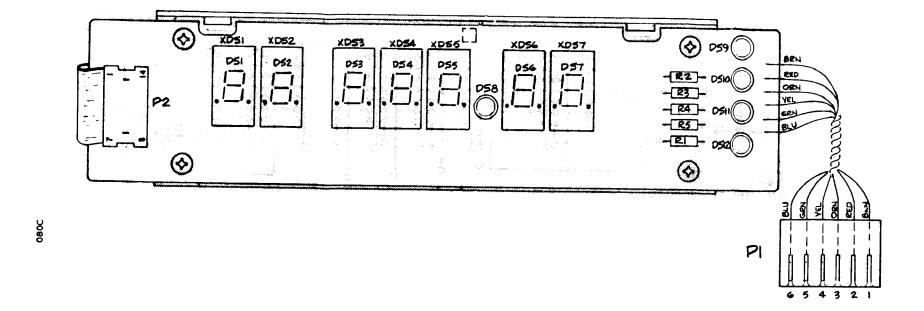

| FO-11A | Component | Locator | and Descriptive Information Display (Al10)            |

| FO-11B | Schematic | Diagram | Display (A110)                                        |

| FO-12A | Component | Locator | Converter Interconnect (A200)                         |

| FO-12B | Schematic | Diagram | Converter Interconnect (A200)                         |

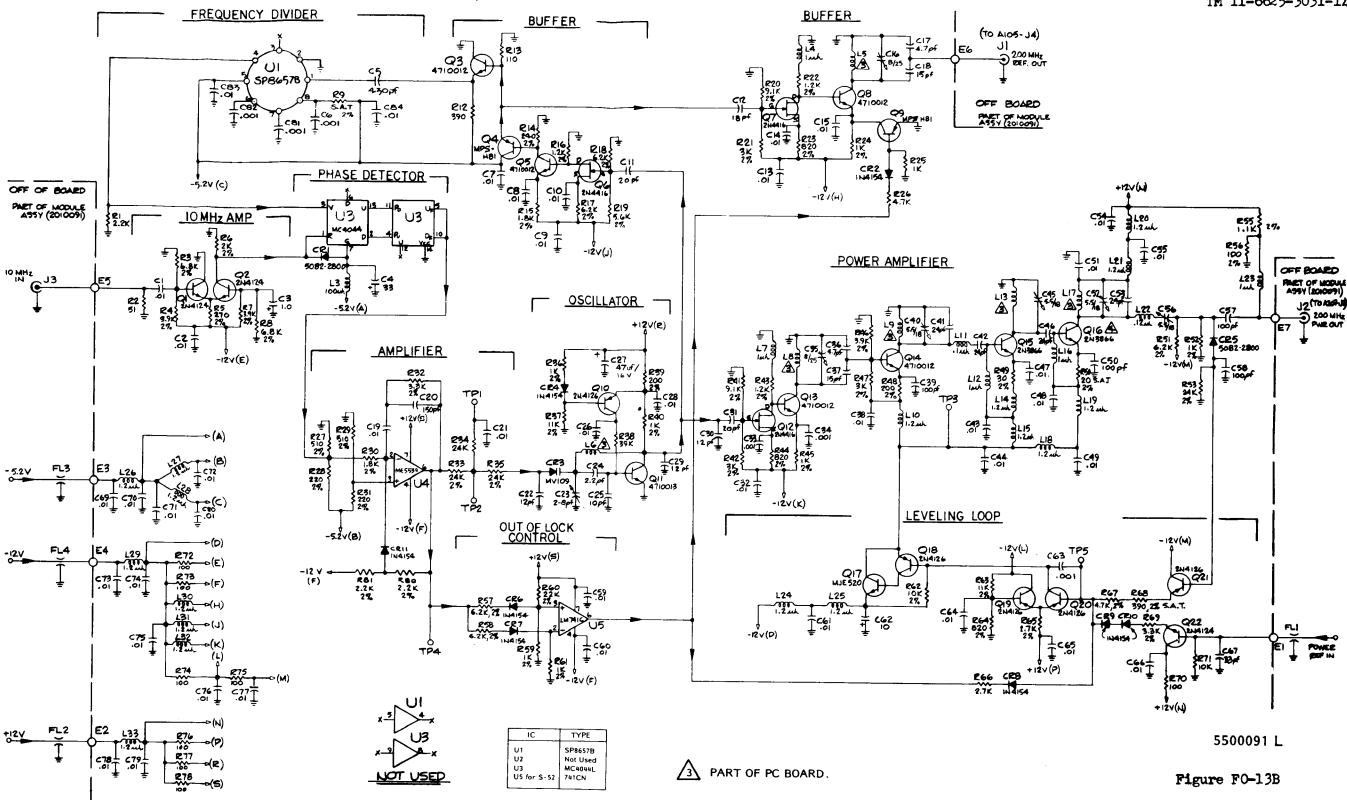

| FO-13A | Component | Locator | and Descriptive Information Source/Amplifier (A201)   |

| FO-13B | Schematic | Diagram | Source/Amplifier (A201)                               |

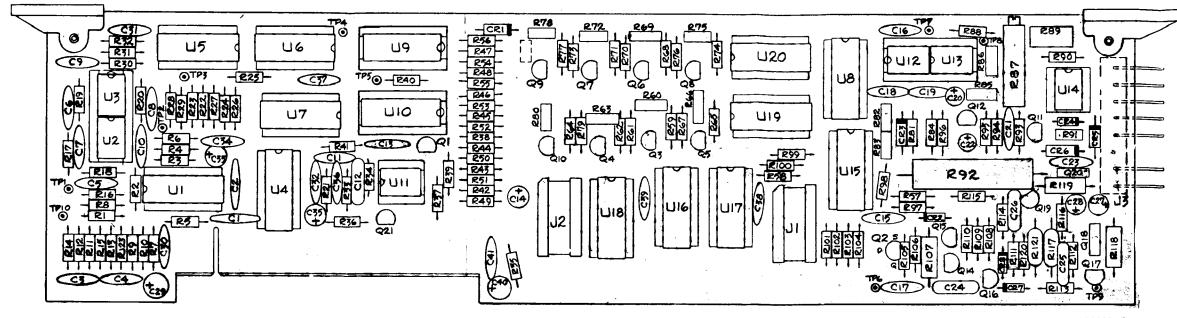

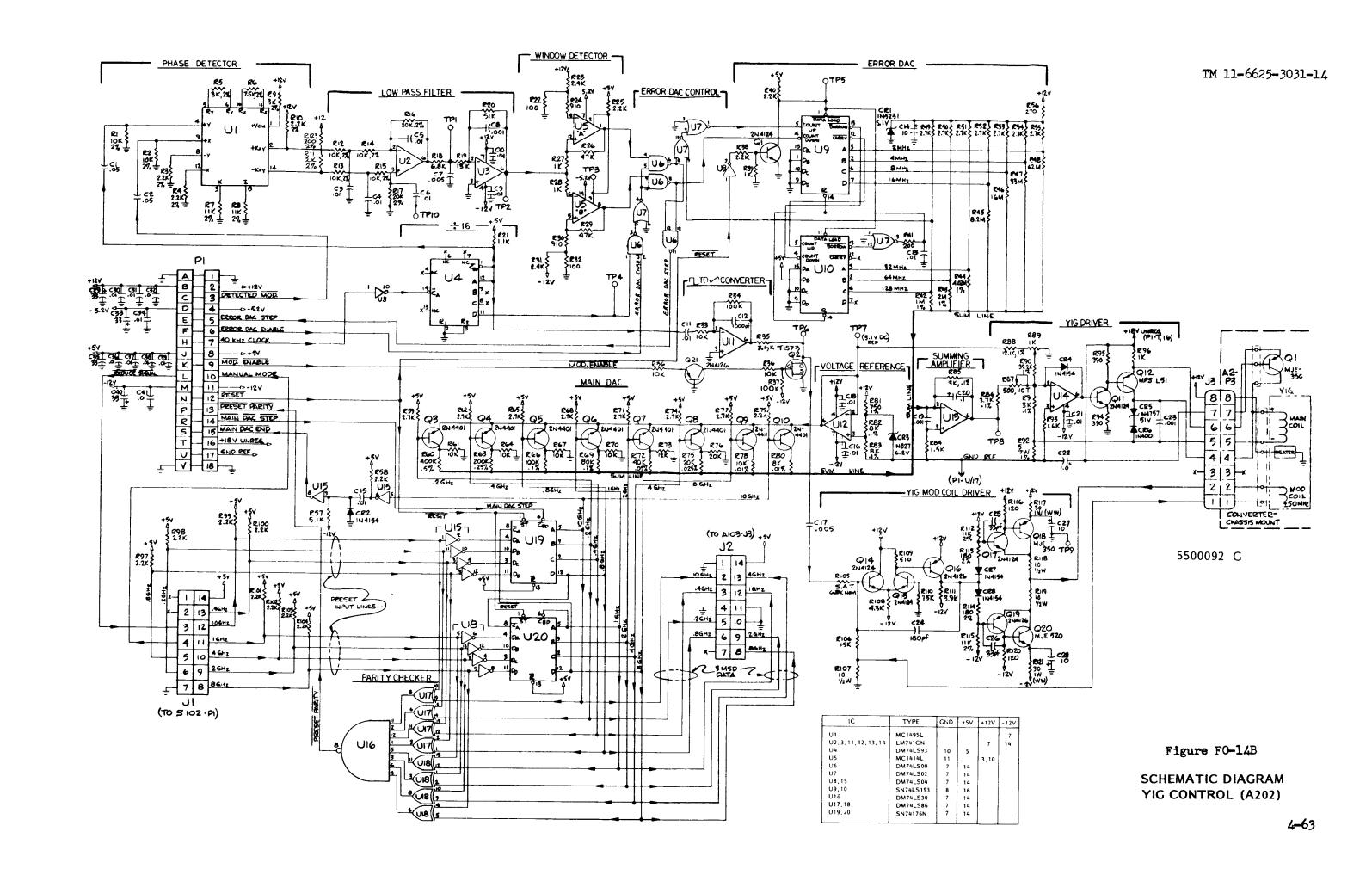

| FO-14A | Component | Locator | and Descriptive Information Yig Control (A202)        |

| FO-14B | Schematic | Diagram | Yig Control (A202)                                    |

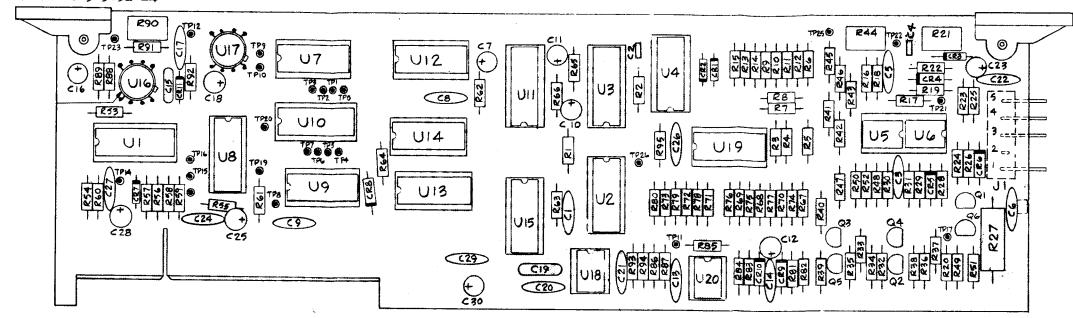

| FO-15A | Component | Locator | and Descriptive Information Converter Sequencer (A203 |

| FO-15B | Schematic | Diagram | Converter Sequencer (A203)                            |

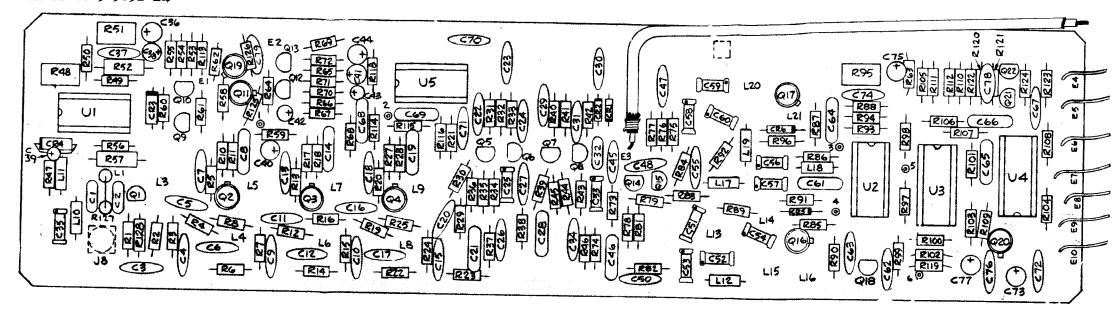

| FO-16A | Component | Locator | and Descriptive Information IF Processor (A204)       |

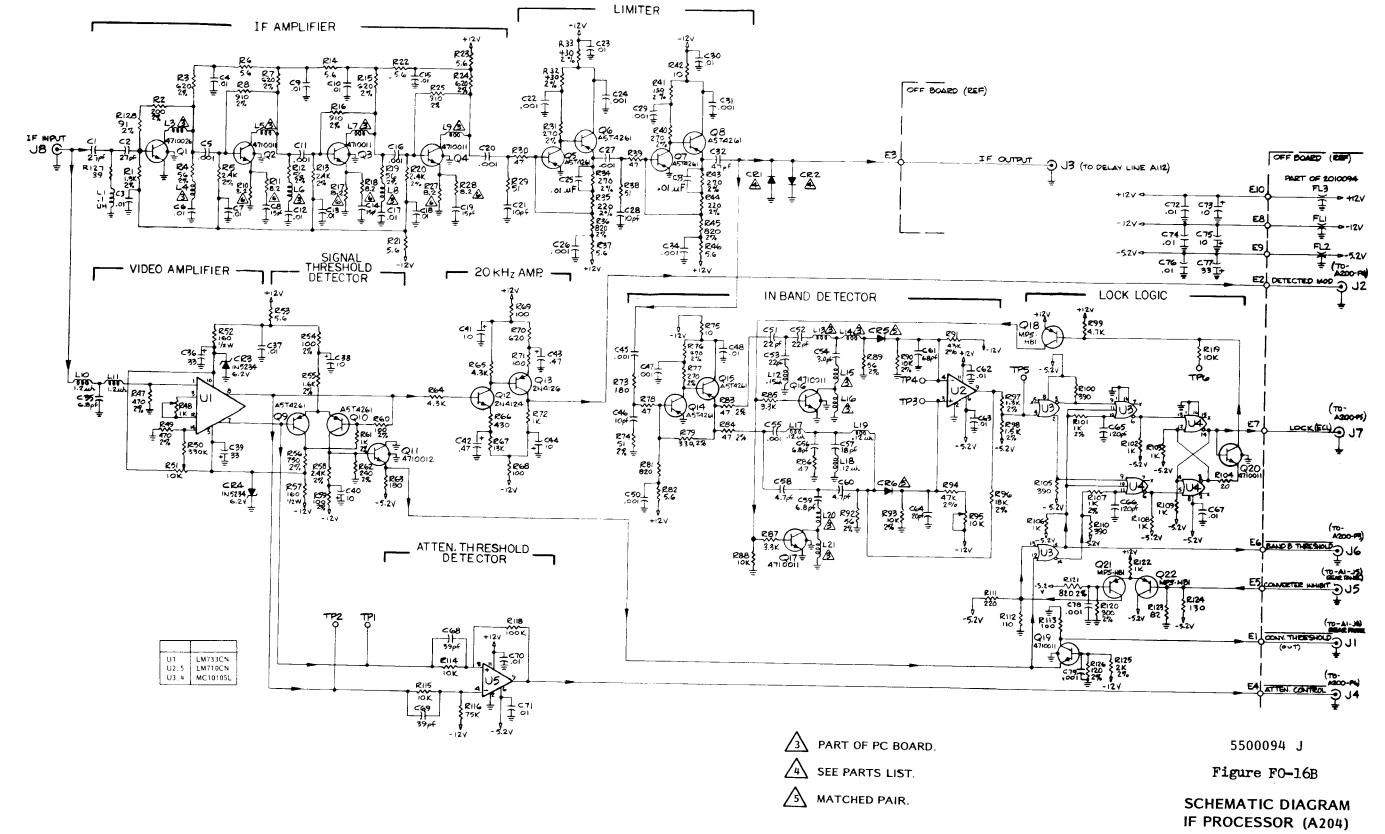

| FO-16B | Schematic | Diagram | IF Processor (A204)                                   |

#### **LIST OF TABLES**

| Table | Title                                                    | Page |

|-------|----------------------------------------------------------|------|

| 1-1   | Specifications                                           | 1-1  |

| 2-1   | Front-panel Controls, Connectors and Indicators          | 2-1  |

| 2-2   | Rear-panel Controls and Connectors                       | 2-5  |

| 2-3   | Operator Preventive Maintenance Checks and Services      | 2-6  |

| 2-4   | Counter GPIB Capability Identification Codes             | 2-14 |

| 2-5   | GPIB IEEE STD 488/1975 Connector Pin Assignments         |      |

| 2-6   | On Line and Off Line ADDRESS SWITCH Settings             |      |

| 2-7   | ADDRESS SWITCH Settings vs ASCII Characters              |      |

| 2-8   | Programming Summary                                      |      |

| 2-9   | Typical Program Using Hewlett-Packard 9815 Calculator as |      |

|       | Controller                                               | 2-26 |

| 3-1   | Operator and Organizational Troubleshooting              |      |

| 4-1   | Symptom Index                                            |      |

| 4-2   | Direct Support and General Support Troubleshooting       |      |

| 4-3   | Power Supply Voltages and Adjustments                    |      |

| 4-4   | Band B Response Tests                                    |      |

| 4-5   | Preset Frequency Tests                                   |      |

| 4-6   | Control Sequence                                         |      |

| 4-7   | Converter Sequence Functions                             | 4-65 |

| 1 /   | converser bedrence rancerous                             | 4-65 |

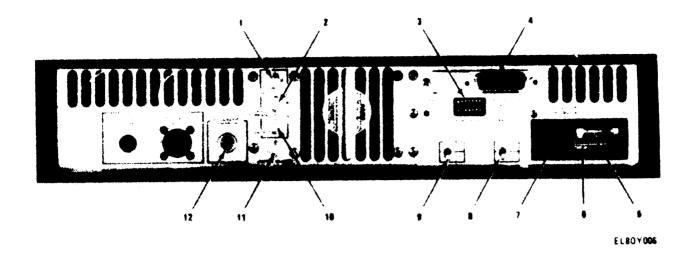

Figure 1-1. Counter, Pulse, Electronic TD-1338(V)1/USM

### CHAPTER 1 INTRODUCTION

#### Section I. GENERAL INFORMATION

#### 1-1. Scope.

<u>a.</u> This technical manual covers operation and maintenance of Counter, Pulse, Electronic TD-1338(V)1/USM. Throughout this manual it is referred to as the counter.

<u>b.</u> The counter (fig. 1-1) is used to measure the frequency of cw, pulse-modulated, or frequency-modulated microwave signals between 300 MHz and 18 GHz. Pulse widths can be as narrow as 100 nanoseconds, with a maximum pulse repetition frequency of 2.5 MHz. Peak-to-peak deviation of FM signals may be as great as 40 MHz at 10 MHz modulation rates.

- 1-2. Reports of Maintenance Forms, Records and Reports.

- a. Reports of Maintenance and Unsatisfactory Equipment. Department of the Army forms and procedures used for equipment maintenance will be those prescribed by TM 38-750, The Army Maintenance Management System (Army). Air Force personnel will use AFM 66-1 for maintenance reporting and TO 00-35D54 for unsatisfactory equipment reporting.

<u>b. Report of Packaging and Handling Deficiencies.</u> Fill out and forward SF 364 (Report of Discrepancy (ROD)) as prescribed in AR 735-11-2/DLAR 4140.55/NAVMATINST 4355.73/AFR 400-54/MCO 4430.3E.

c. Discrepancy in Shipment Record (DISREP) (SF 361). Fill out and forward Discrepancy in Shipment Report (DISREP) (SF 361) as prescribed in AR 55-38/NAVSUPINST 4610.33B/AFR 75-18/MCO P4610.19C/DLAR 4500.15.

#### 1-3. Administrative Storage.

Administrative storage of equipment issued to and used by Army activities will have preventive maintenance performed in accordance with the PMCS charts before storing. When removing the equipment from administrative storage, the PMCS should be performed to assure operational readiness.

1-4. Destruction of Army Electronics Materiel.

Destruction of Army electronics materiel to prevent enemy use shall be in accordance with TM 750-244-2.

1-5. Reporting Equipment Improvement Recommendations (EIR's).

If your counter needs improvement, let us know. Send us an EIR. You, the user, are the only one who can tell us what you don't like about your equipment. Let us know why you don't like the design or performance. Put it on an SF 368 (Quality Deficiency Report). Mail it to: Commander, US Army Communications-Electronics Command and Fort Monmouth, ATTN: DRSEL-ME-MP, Fort Monmouth, New Jersey 07703. We'll send you a reply.

#### 1-6. Warranty Information.

The counter is warranted by EIP Microwave, Inc. for 12 months. It starts on the date, found in block 23, DA Form 2408-9, in the logbook. Report all defects in material or workmanship to your supervisor, who will take appropriate action through your organizational maintenance shop.

#### Section II. EQUIPMENT DESCRIPTION

1-7. Equipment Characteristics, Capabilities and Features.

The counter is a portable test instrument usable as either self-contained frequency measurement or monitoring indicator, or as part of a programmable automatic test equipment (ATE) system. It provides a direct readout of frequency from 300 MHz through 18 MHz. Capabilities and features include:

- <u>a.</u> Measures pulse-modulated microwave signals.

- <u>b.</u> Measures frequency-modulated microwave signals.

- c. Measures cw microwave signals.

- <u>d.</u> Front panel self-test of digital display.

- $\underline{e.}$  Front panel self-test of internal circuits.

- <u>f.</u> Automatic and selectable resolution of-readout display.

- g. Overload protection built in at input connector.

- <u>h.</u> Simple change to cover different power line voltages.

- <u>i.</u> Front-panel selection of frequency scanning limits.

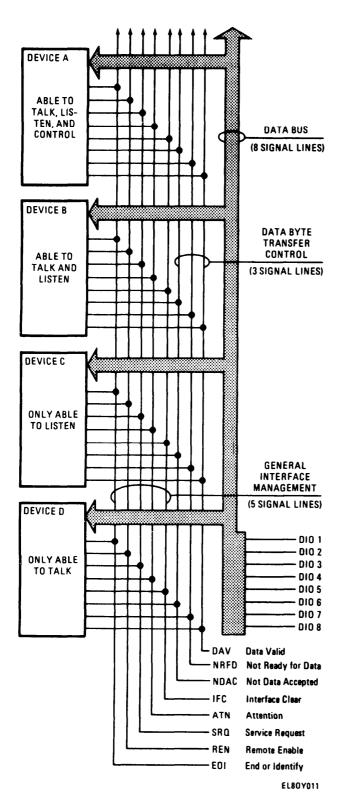

- j. Comparable with IEEE STD 488

General Purpose Interface Bus (GPIB).

- 1-8. Equipment Data.

Table 1-1 lists the electrical and physical characteristics of the counter.

Table 1-1. Specifications

Frequency Range:

Band A

Band B

Pulse Characteristics:

Pulse width

Pulse repetition frequency

Accuracy:

CW or pulse > 100 µsec

Pulse < 100 usec

Averaging Error (kHz rms):

100 µsec gate

1 msec gate

Gate error (max)

300 MHz to 950 MHz 925 MHz to 18 GHz

100 nsec min, measured at 3-dB points Minimum 50 Hz or 0 Hz, rear panel selectable. Maximum 2.5 MHz. Minimum time between pulses 300 nsec.

Time base accuracy  $\pm$  1 count

Time base accuracy ± averaging error

± gate error

NOTE

PW = pulse width in µsec

Table 1-1. Specifications - Continued

| Time Base:                                     | Temperature compens oscillator (TCXO)            | ated crystal                      |

|------------------------------------------------|--------------------------------------------------|-----------------------------------|

| Crystal frequency<br>Stability:                | 10 MHz                                           |                                   |

| Aging rate                                     | < 3 X 10 <sup>-7</sup>   per mor                 | nth                               |

| Temperature                                    | $<  2 \times 10^{-6} $ , 0 to 5                  | 0°C                               |

| Line voltage                                   | $<  1 \times 10^{-7} $ for ± 1                   |                                   |

| Sensitivity                                    | Band A                                           | Band B                            |

|                                                | 300 - 950 MHz:<br>-10 dBm peak                   | 925 MHz - 10 GHz:<br>-10 dBm peak |

|                                                |                                                  | 10 GHz - 18 GHz:<br>-5 dBm peak   |

| Input Impedance                                | 50 ohms nominal                                  | 50 ohms nominal                   |

| Connector Types                                | BNC                                              | N (precision)                     |

| Maximum Input Peak Level:                      |                                                  |                                   |

| Operating<br>Burnout level                     | +10 dBm<br>+27 dBm                               | +10 dBm<br>+30 dBm                |

| Reading Time (sec):                            | 127 Ubiii                                        | +30 QBIII                         |

| <i>y</i> , , , , , , , , , , , , , , , , , , , | 400                                              | 100                               |

| 100 μsec gate                                  | (PW) (PRF)                                       | (PW) (PRF)                        |

| 1 msec gate                                    | 4000<br>(PW)(PRF)                                | 1000<br>(PW) (PRF)                |

|                                                | N                                                | OTE                               |

|                                                | PW = pulse wid                                   | th in µsec                        |

|                                                | PRF = pulse rep<br>in Hertz                      | etition frequency                 |

| Display                                        | 7-digit light emitt:                             | ing diode (LED)                   |

|                                                | Fixed decimal point                              |                                   |

|                                                | Leading zero suppre                              | ssion                             |

| Band B Minimum FM Tolerance:                   |                                                  |                                   |

| CW                                             | 40 MHz p-p deviation rates dc to 10 MHz          | n for modulation                  |

| Pulse                                          | Without input inhibiting frequency shift acro    |                                   |

| Frequency profile                              | With input inhibit: frequency shift during pulse |                                   |

Table 1-1. Specifications - Continued

| Band B Acquisition Time:                        |                                                                                              |

|-------------------------------------------------|----------------------------------------------------------------------------------------------|

| PRF > 100 Hz                                    | 100 msec + 50 msec/GHz                                                                       |

| PRF < 100 Hz                                    | 100 msec + $\frac{5}{PRF}$ sec/GHz                                                           |

| Resolution                                      | 10 kHz, 100 kHz, 1 MHz                                                                       |

| General Purpose Interface Bus (GPIB)            | IEEE Standard Digital Interface for Programmable Instrumentation, IEEE STD 488-1975          |

| Power                                           | 115 or 230 Vac ± 10%, 50/60 Hz;<br>115 Vac ± 10%, 400 Hz; single phase;<br>100 watts nominal |

| Operating Temperature<br>Warm up Time<br>Weight | 0 - 50°C<br>None Required<br>30 lb                                                           |

| Dimensions (inches)                             | 3.5 H x 16.75 W x 19.0 D                                                                     |

#### Section III. TECHNICAL PRINCIPLES OF OPERATION

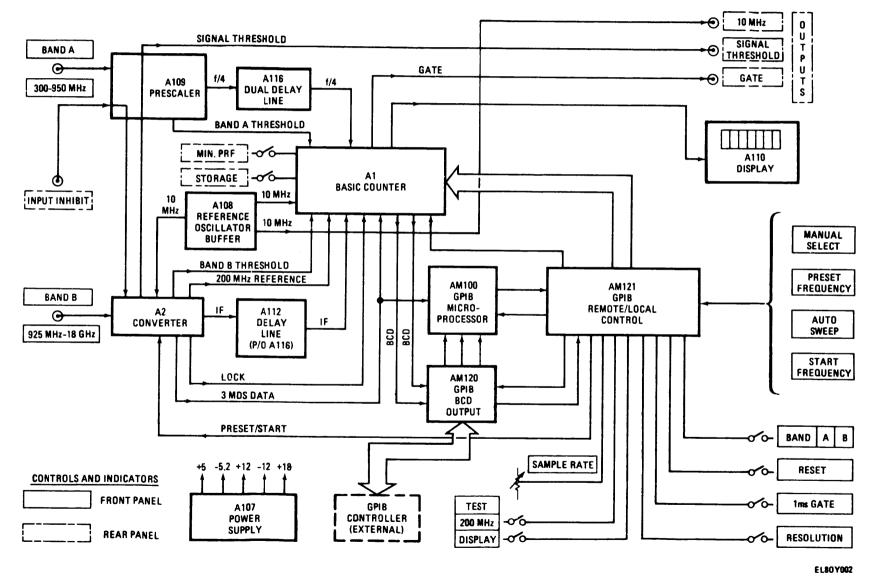

1-9. Counter Functional Operation. (Fig. 1-2.)

a. The counter automatically measures and displays the frequency of cw or pulse-modulated signals from 300 MHz through 18 GHz. With accessory equipment, the counter can make dynamic frequency measurements; measurement windows as narrow as 20 nanoseconds are possible. Two primary input connectors on the front panel, BAND A 300 - 950 MHz and BAND B 925 MHz - 18 GHz, are used to connect the counter to the external frequency source. An auxiliary INPUT INHIBIT connector on the rear panel can be used to control the time during which an actual reading is made. Control of the counter can be accomplished by front-panel switches or by a General Purpose Interface Bus (GPIB) from an external GPIB controller. The output of the counter is displayed on a 7digit, fixed decimal, light emitting diode (LED) display and can be transmitted through the GPIB for other

purposes. Accuracy of the counter is controlled by Reference Oscillator Buffer Al08 with outputs to Basic Counter Al and Converter A2; a third output is connected to a rear-panel 10 MHz OUTPUT connector.

b. Band A signals are fed into a divide-by-four circuit in Prescaler A109, whose output is directed to Basic Counter A1 through Dual Delay Line A116. The divide-by-four frequency is counted in the basic counter for either a 400 microsecond or 4 millisecond period to obtain 10 kHz resolution readout on Display A110. The counter gate in A1 is enabled by the input signal and is open only when a signal is present.

c. Band B signals are fed into Converter A2, converted to an IF signal by heterodyning the input signal against a 200 MHz harmonic, and directed to A1 through Delay Line A112. The counter gate in A1 is enabled by the Input signal and is open only when a signal is present. In A1, resolution is inversely proportional to the measurement

Figure 1-2. Counter, Functional Block Diagram

time. For example: a 1 microsecond gate time will give 1 MHz resolution. To get 10 kHz resolution, the counter automatically averages as many input pulses as necessary to obtain a total gate time of 100 microseconds or 1 millisecond. The required number of pulses is a function of input pulse width. The intermediate frequency from A2 is processed and counted in A1 and displayed on A110.

d. Three rear-panel connectors provide 10-MHz, SIGNAL THRESHOLD, and GATE OUT-PUTS. The 10 MHz OUTPUT is a service convenience for adjusting the temperature compensated crystal oscillator (TCXO) on Reference Oscillator Buffer A108. The other two signal outputs may be used for dynamic frequency measurements such as pulse profile measurements or time varying signal measurements.

e. Power Supply A107 provides +5, -5.2, +12, -12, and +18 volts dc for the counter circuits. The +18 Vdc output is unregulated; the other four voltages are regulated.

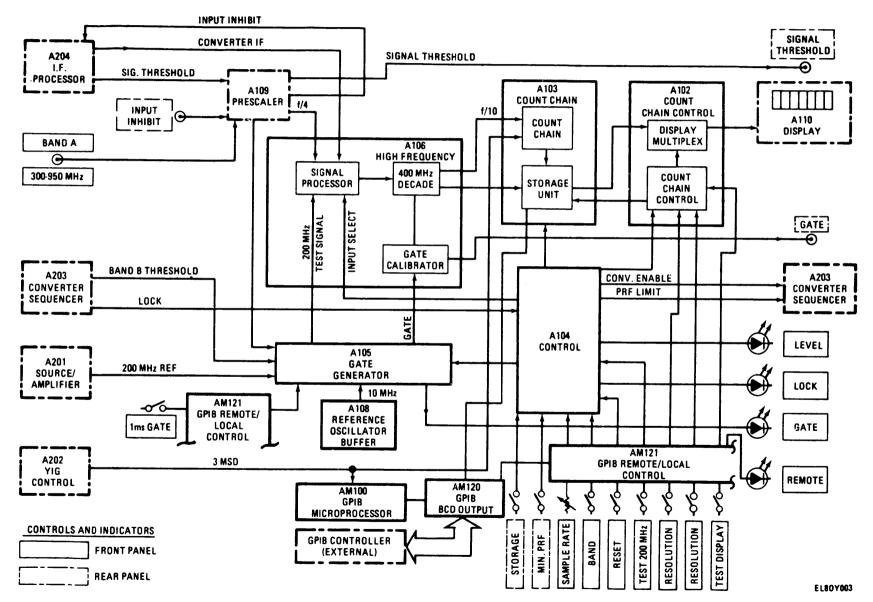

#### 1-10. Basic Counter Al. (Fig. 1-3.)

a. Input signals from either the low range (300 - 950 MHz) or high range (925 MHz - 18 GHz) sources, or both, are applied to the signal processor circuits on High Frequency Circuit Card A106. The signal from Prescaler Al09 is the BAND A input frequency, divided by four (f/4). The signal from I.F. Processor A204 is the BAND B input frequency minus the reference frequency identified as the converter IF signal. Selection of which signal to display is controlled by the front panel BAND selection switches or by GPIB selection. Only one of the signal inputs can be displayed even though both may be connected to the counter. The f/4 and the IF signal inputs are 360 MHz or lower and are directed to the 400 MHz decade circuits on A106.

<u>b.</u> Two threshold (Band A and/or Band B) control levels are applied to Gate Generator A105 to provide a gate output to the 400 MHz decade through the gate calibrator. The Band A

threshold comes from Prescaler A109 while the Band B threshold comes from I.F. Processor A204 in Converter A2.

c. When an input signal has been processed into the range below 360 MHz and applied to the 400 MHz decade, the frequency of the signal is determined by accumulating the number of signal cycles occurring within a precisely determined time interval (gate). The gate period is dependent on the 200 MHz reference frequency. Total time intervals of the gates are 100 microseconds and 1 millisecond for Band B, or 400 microseconds and 4 milliseconds for Band A. In order to measure narrow pulses to a resolution of 10 kHz, it is necessary to add the number of cycles counted in each of a large number of pulses until the required total time interval is obtained.

d. Gate Generator A105 provides a precision interval gate. This function is considerably more difficult for pulsed signals than it is for cw signals, and it is on this function that the overall accuracy of the counter depends. A105 performs two functions; it supplies a gate to A106 only when an input signal is present, and it accumulates the total time of gate application for periods of either 100 microseconds or 1 millisecond for Band B, or either 400 microseconds or 4 milliseconds for Band A.

e. The first function or operation requires that the gate begin after the signal is present at A106 and to end before the end of signal. This is done by generating a gate approximately 30 nanoseconds shorter than the RF signal start as determined by the associated Band A or Band B threshold level. The arrival time at A106 of the converter IF or the prescaler f/4 signal is controlled by delay lines in A116, in series with the signals, so that the gate will fall entirely within the signal pulse application.

<u>f.</u> The second function is done by counting clock pulses when the gate is open until a total period of 100 microseconds or 1 millisecond for Band B, or 400 microseconds or 4 milliseconds for

Figure 1-3. Basic Counter Al, Functional Block Diagram

Band A, is accumulated. This requires that each gate opening is for an exact integral number of clock pulses. A 200 MHz clock is used, causing the gate width to increase in 5 nanosecond steps until a total of 20,000 steps for 100 microseconds, 80,000 steps for 400 microseconds, 200,000 steps for 1 millisecond, or 800,000 steps for 4 milliseconds is accumulated.

g. The signal passes through the counter gate and is accumulated in the counting-chain first decade, the 400 MHz decade on A106. The signal output (f/10) of the 400 MHz decade is fed to the storage unit through the 6-decade count chain of A103. The storage unit on A103 holds all of the digital information from the previous reading. Output from the storage unit is fed to the display multiplexer which is controlled by count chain control circuits on the Count Chain Control A102.

h. Output of the display multiplexer on A102 is fed to Display A110. A110 is mounted on the front panel along with LEVEL, LOCK, and GATE status indicators. The front-panel REMOTE indicator is used with GPIB controller operations. all control of the counter is performed by Control Circuit Card A104. Frontpanel selection switching is routed to A104 through GPIB Remote/Local Circuit Card AM121. When the counter is in the REMOTE mode of operation, front-panel controls and switches are inoperative except for the SAMPLE RATE control, and then only under certain programming instructions from the GPIB controller.

#### 1-11. Converter A2. (Fig. 1-4.)

a. Converter A2 translates the Band B input microwave frequencies down to frequencies between 100 and 360 MHz. Translation is done by mixing the input frequencies with a reference frequency to produce, by heterodyne action, an amplified intermediate frequency. The IF is then fed to A106 through Delay Line A112 for counting and processing in Basic Counter A1.

b. Generation of the heterodyning reference frequency starts by generating a

200 MHz reference signal in Source/

Amplifier A201. The 200 MHz reference

in A201 is generated by an L-C oscillator phase-locked to 10 MHz from Reference Oscillator Buffer A108. The 200

MHz outputs from A201 are directed to

YIG (Yttrium-Iron-Garnet) Comb Generator

A207 and to Gate Generator A105 in

Basic Counter A1. A power amplifier

section on A201 amplifies the 200 MHz

signal before it is applied to A207.

The 200 MHz output to A105 is used to

generate a Band B gate or may be used

for a TEST 200 MHz self-test.

c. The local oscillator, or reference harmonic, frequency is generated in YIG Comb Generator A207 by taking the 200 MHz signal from A201 and converting it to a train of narrow pulses containing all harmonics of 200 MHz up to 18 GHz. This conversion is done by the YIG comb generator and a two-stage YIG filter, which selects the desired 200 MHz harmonic. The YIG filter is tuned by varying the current through a pair of coils, which change magnetic fields in the assembly.

d. Band B input signals are applied to Limiter/Attenuator A206. A passive diode limiter protects Mixer A205 from power levels in excess of one watt peak (+30 dBm). A multistage matched PIN diode attenuator section controls the RF signal level to the mixer and switches off the input signal during portions of converter operation.

e. Mixer A205 is an integrated microwave circuit assembly consisting of a hybrid coupler, termination, mixer diode, and dc return. The mixer produces two output signals on a common line: an IF signal equal to the difference frequency between the incoming RF signal from A206 and the reference frequency harmonic from A207, and a video signal resulting from rectification (detection) of either the RF or reference inputs. The mixer output is fed to I.F. Processor A204.

$\underline{\text{f.}}$  The IF and video signals from Mixer A205 are separated in A204. The IF signal is amplified by the IF amplifier and sent on as the converter IF signal to A106, through Delay Line A112, for

Figure 1-4. Converter A2, Functional Block Diagram

ΜŢ

counting. The video signal is amplified in the video amplifier to produce three video outputs: (1) a threshold signal is directed to the rear-panel SIGNAL THRESHOLD connector through Prescaler A109; (2) a threshold signal, identified as attenuator control, is sent to an attenuator control circuit on Converter Sequencer A203; and (3) an analog output is applied to the power level control portion of A203.

g. On A203, inputs from the lock section of I.F. Processor A204 are sequenced and timed to produce a lock level signal for Control A104 and a Band B threshold signal for Gate Generator A105. The attenuator control threshold signal from the video section of A204 is combined with an input from the converter sequencer in the attenuator control to give two outputs: (1) an attenuator control signal, activated at a level approximately 7 dB above signal threshold, sent to the PIN attenuator of A206, to reduce signal level into Mixer A205; and (2) a reduce signal level sent to the front-panel

REDUCE SIGNAL indicator when the attenuator control is sending a signal to the PIN attenuator. The power level control circuit receives an analog input from the video section of A204 and a digital signal from the converter sequencer of A203, and provides a signal to the tuning circuits of A202 to set the comb line amplitude. The converter sequencer function is to control the sensing, leveling, and control of Converter A2.

h. YIG Control A202 contains circuits to step the YIG filter to the proper comb line, and is controlled by input lines from Converter Sequencer A204. On-board circuits include a YIG driver to supply the required current, a digital-to-analog converter (DAC) to set the approximate center frequency, and a centering circuit to precisely center the YIG filter passband on a comb line. The centering process is done by modulating the YIG center frequency by an auxiliary modulation coil in YIG Comb Generator A207. The modulation control circuit is on A202.

#### **CHAPTER 2 OPERATING INSTRUCTIONS**

#### Section I. DESCRIPTION AND USE OF OPERATORS CONTROLS AND INDICATORS

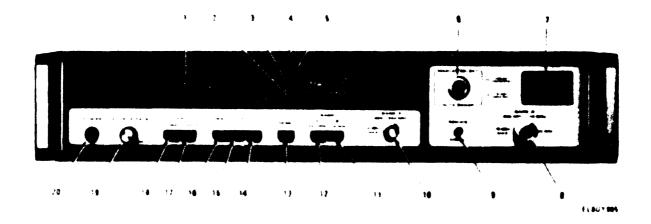

2-1. Front-Panel Controls, Connectors and Indicators.

Operator's front-panel controls, connectors and indicators are shown in fig- connectors are shown in figure 2-2 and ure 2-1 and are keyed to table 2-1, which describes their functions.

2-2. Rear-panel Controls and Connectors.

Operator's rear-panel controls and are keyed to table 2-2, which describes their functions.

Figure 2-1. Counter Front Panel

Table 2-1. Front-panel Controls, Connectors and Indicators

| Key | Control, connector<br>or indicator | Functional operation                                                                                                                                                                                                         |

|-----|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Display                            | Seven-digit LED display provides<br>direct numerical readout of input<br>frequency in GHz and MHz.                                                                                                                           |

| 2   | REMOTE indicator                   | When lighted, indicates that all front-panel controls are disabled except SAMPLE RATE. This indicator is controlled by digital programmed data on the General Purpose Interface Bus (GPIB) and by rear-panel ADDRESS SWITCH. |

Table 2-1. Front-panel Controls, Connectors and Indicators - Continued

| Кеу | Control, connector or indicator                    | Functional operation                                                                                                                                                                                                                                                                                                                                |

|-----|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | GATE indicator                                     | Lights when counter is in measure-<br>ment portion of cycle.                                                                                                                                                                                                                                                                                        |

| 4   | LEVEL indicator                                    | Lights when input signal level is high enough to be counted. Light will blink if signal pulse repetition frequency is too low.                                                                                                                                                                                                                      |

| 5   | LOCK indicator                                     | Lights when input signal has been acquired.                                                                                                                                                                                                                                                                                                         |

| 6   | MANUAL SELECT/AUTO SWEEP switch                    | Selects either manual or automatic operation of counter for BAND B.                                                                                                                                                                                                                                                                                 |

| 7   | PRESET FREQUENCY/START FREQUENCY thumbwheel switch | When MANUAL SELECT/AUTO SWEEP switch (6) is set to MANUAL SELECT, thumb-wheel switch sets PRESET FREQUENCY; input signal frequency must be 105 to 325 MHz higher. When MANUAL SELECT/AUTO SWEEP switch is set to AUTO SWEEP, thumbwheel switch sets sweep START FREQUENCY; input signal frequency must be at least 105 MHz higher than sweep start. |

| 8   | BAND B 925 MHz - 18 GHz<br>connector               | Type N precision input connector for Band B operation.                                                                                                                                                                                                                                                                                              |

| 9   | REDUCE SIGNAL indicator                            | Lights when Band B input power approaches maximum safe operating level.                                                                                                                                                                                                                                                                             |

| 10  | BAND A 300 - 950 MHz<br>connector                  | Type BNC input connector for Band A operation.                                                                                                                                                                                                                                                                                                      |

| 11  | BAND B pushbutton switch                           | Selects Band B operation for frequen-<br>cies between 925 MHz and 18 GHz.                                                                                                                                                                                                                                                                           |

| 12  | BAND A pushbutton switch                           | Selects Band A operation for frequen-<br>cies between 300 and 950 MHz.                                                                                                                                                                                                                                                                              |

| 13  | RESET pushbutton switch                            | When pushed and released, overrides SAMPLE RATE control, resets display to zeros, and initiates a new reading.                                                                                                                                                                                                                                      |

| 14  | 1 ms GATE pushbutton switch                        | When pushed in, provides 10 kHz resolution with 1 millisecond gate time on Band B or 4 millisecond gate time on Band A for reduced pulse averaging error.                                                                                                                                                                                           |

Table 2-1. Front-panel Controls, Connectors and Indicators - Continued

| Key | Control, connector<br>or indicator    | Functional operation                                                                                                                                                                                                                       |

|-----|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | Right RESOLUTION pushbutton<br>switch | Provides blanking of least significant digit for resolution of 100 kHz with 100 microsecond gate time on Band B or 400 microsecond gate time on Band A.                                                                                    |

| 16  | Left RESOLUTION pushbutton<br>switch  | Provides blanking of two least significant digits for resolution of 1 MHz with 100 microsecond gate time on Band B or 400 microsecond gate time on Band A.                                                                                 |

| 17  | TEST DISPLAY pushbutton<br>switch     | When pushed and held in, provides test of all segments of display LEDS. Display should read 88 888.88.                                                                                                                                     |

| 18  | TEST 200 MHz pushbutton<br>switch     | When pushed and held in, provides check of counting circuits. Display should indicate 200.00 MHz.                                                                                                                                          |

| 19  | SAMPLE RATE control                   | Continuously variable control which varies display time from 0.1 to 10 seconds per reading. Rotating control to its switched HOLD position will cause display to hold last reading without an update until RESET switch (13) is pushed in. |

| 20  | POWER pushbutton switch               | When pushed in and released, power counter is turned on or off. When power is on, a green indicator is visible in switch.                                                                                                                  |

Figure 2-2. Counter Rear Panel

Table 2-2. Rear-panel Controls and Connectors

| Table 2-2. Real-panel Conclus and Connectors |                                          |                                                                                                                                                                                                                                                              |  |

|----------------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Кеу                                          | Control or connector                     | Functional operation                                                                                                                                                                                                                                         |  |

| 1                                            | 10 MHz OUTPUT connector                  | Provides output of internal 10 MHz clock; 1 Vp-p minimum into 50 ohms.                                                                                                                                                                                       |  |

| 2                                            | SIGNAL THRESHOLD OUTPUT<br>connector     | Provides pulse output representing signal threshold level of input pulse. Output pulse typically delayed 20 nanoseconds from input pulse. Used for frequency profile measurements.                                                                           |  |

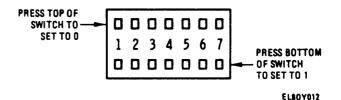

| 3                                            | GPIB IEEE STD 488/1975<br>ADDRESS SWITCH | Address switches of counter when General Purpose Interface Bus (GPIB) is used. Setting of various combinations of seven switches permits the counter to be operated in Talk, Listen, or Monitor modes when external GPIB controller is connected to counter. |  |

| 4                                            | GPIB IEEE STD 488/1975 connector         | Provides connection to external GPIB controller.                                                                                                                                                                                                             |  |

| 5                                            | Fuse                                     | Slow-blow line fuse; 1.5 A at 115 Vac or 0.75 A at 230 Vac.                                                                                                                                                                                                  |  |

| 6                                            | Line voltage selector card               | Selects either 115 or 230 Vac line voltage. Selected voltage printed on card is visible when card is installed.                                                                                                                                              |  |

| Table 2-2. | Rear-panel | Controls | and | Connectors | - | Continued |

|------------|------------|----------|-----|------------|---|-----------|

|            |            |          |     |            |   |           |

| Key | Control or connector          | Functional operation                                                                                                                                                           |

|-----|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | AC power connector            | Three-prong male connector for ac power cable. Third conductor grounding meets NEC and UL requirements.                                                                        |

| 8   | MIN. PRF switch               | Selects minimum prf. Normally set to 50 Hz position. In 0 position, counter will measure very low prf signals but reading will not automatically reset when signal is removed. |

| 9   | STORAGE switch                | Controls display update. Normally ON; in OFF position front-panel display updates continuously during measurement cycle.                                                       |

| 10  | GATE OUTPUT connector         | Provides gate pulse representing actual time at which measurement is being made. Used in frequency profile measurements.                                                       |

| 11  | INPUT INHIBIT connector       | Connector for external pulse input for use in frequency profile measurements.                                                                                                  |

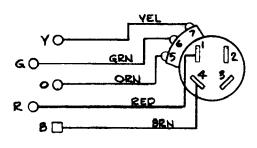

| 12  | ACCESSORY POWER OUT connector | Provides +5, -5.2, +12, and -12 Vdc<br>for accessories used with counter,<br>such as EIP Model 400 Delay<br>Generator.                                                         |

#### Section II. PREVENTIVE MAINTENANCE CHECKS AND SERVICES

#### 2-3. General Instructions.

- <u>a.</u> <u>Before you operate.</u> Always keep in mind the CAUTIONS and WARNINGS. Perform your before (B) PMCS.

- <u>b.</u> <u>While you operate.</u> Always keep in mind the CAUTIONS and WARNINGS. Perform your during (D) PMCS.

- c. After you operate. Be sure to perform your after (A) PMCS.

- d. If your equipment fails to operate. Troubleshoot with proper equipment. Report any deficiencies using the proper forms. See TM 38-750.

#### 2-4. PMCS Procedures.

Table 2-3 outlines the functions to be performed at specific intervals. These checks and services are to maintain Army electronic equipment in a combat serviceable condition; that is, in good general (physical) condition and in good operating condition. To assist operators in maintaining combat serviceability, the chart indicates what to check. If any entry appears in the "Equipment is not ready/available if:" column, appropriate corrective

maintenance action must be taken to restore the counter to an operational condition.

#### 2-5. Cleaning Instructions.

a. At the interval specified in table 2-3, remove dust and loose dirt with a clean soft cloth.

#### CAUTION

Do not use any solvent except water or a mild detergent to clean the plastic front panel of the counter. Other solvents may damage the panel.

<u>b.</u> Clean external surfaces with a clean soft cloth moistened with clean water. A mild detergent may be used for more effective cleaning.

Table 2-3. Operator Preventive Maintenance Checks and Services

#### NOTE

Within designated interval, these checks are to be performed in the order listed.

B - Before

W - Weekly

D - During

M - Monthly

A - After

| Item |   | Interval |   | Item to be | Procedures - check for and have | Equipment<br>is not ready/ |                                                             |                                      |  |

|------|---|----------|---|------------|---------------------------------|----------------------------|-------------------------------------------------------------|--------------------------------------|--|

| No.  | В | D        | A | W          | М                               | inspected                  | repaired or adjusted<br>as necessary                        | available if:                        |  |

| 1    | Х |          |   |            |                                 | Completeness               | Power cable connected to counter.                           | Power cable is missing.              |  |

| 2    |   | х        |   |            |                                 | Power cable                | Cuts or cracks in outside jacket; damage to connector pins. | Power cable is defective.            |  |

| 3    |   |          |   | х          |                                 | Controls and hardware      | Missing or loose<br>knobs or hardware                       |                                      |  |

| 4    |   |          |   |            | х                               | Exterior<br>surfaces       | Clean exterior surfaces.                                    |                                      |  |

| 5    |   |          |   |            | х                               | Nameplate                  | Legibility.                                                 |                                      |  |

| 6    | х |          |   |            |                                 | Operational capability     | Perform self-test,<br>para 2-7 <u>b</u> (2).                | Self-test indications are incorrect. |  |

#### Section III. OPERATION UNDER USUAL CONDITIONS

2-6. Assembly and Preparation for Use.

#### a. Unpacking.

- (1) Visually inspect the shipping carton for signs of damage before opening. If there is any apparent damage, request that the shipper's agent be present when the counter is unpacked. Visible and concealed damage claims against the carrier or shipper can only be filed if the agent is present or waives his rights.

- (2) Open the carton, removing instrument supports and packing materials. Carefully lift out the counter. Inspect the counter for damage. Without applying power, check the mechanical operation of all controls and switches.

#### b. Assembly

(1) The only assembly requirements are selection of either 115 Vac or 230 Vac line voltage and connecting the power cable to the instrument.

#### WARNING

Be sure only the specified power cable is used. The instrument is provided with a 3-wire cable which grounds the instrument cabinet. This cable should only be inserted in a socket outlet provided with a protective ground contact. This protective action should not be negated by the use of an extension cord without a protective ground conductor.

(2) The counter is normally shipped ready for operation from a 115 Vac power line, with a 1.5 ampere slow-blow fuse installed. Check the marking on the line voltage selector card (6, fig. 2-2), visible through the window in the fuse cover, to be certain that it reads 115 volts.

#### CAUTION

The FUSE FULL lever attached to the body of the power module housing does not come off. Firm but careful rotation of the fuse puller will lift up one end of the fuse so that finger force can remove the fuse. Failure to heed this caution by exerting too much force may damage the plastic pivot of the built-in fuse puller.

- (3) Remove the installed fuse by lifting up on the FUSE PULL lever and check that it is a  $1.5\ \text{ampere}$  fuse.

- (4) Reinstall or replace the fuse with one of the correct value and connect the power cable to the ac power connector.

- (5) To change the line voltage operation, proceed as follows:

- (a) On the rear of the counter, slide the fuse cover to the left and remove the fuse by lifting up on the FUSE PULL lever; see CAUTION above.

- (b) Extract the line voltage selector card.

- (c) Rotate the card so that the appropriate marking (115 or 230 volts) will be visible when the card is inserted into the card slot. Carefully but firmly insert the card into the slot, being careful not to cant or tilt the card while inserting. Check the seating by sliding the fuse cover from left to right. After checking the card seating, slide the fuse cover back to the left to gain access to the fuse clip.

- (d) Insert a slow-blow fuse of the correct value (1.5 amperes for 115 Vat, 0.75 ampere for 230 Vac) in the fuse clip; check that built-in fuse puller does not obstruct the fuse cover by sliding the fuse cover to the right.

- $\underline{\mbox{(e)}}$  Connect the power cable to the ac power connector.

#### c. Preparation for Use.

(1) Stand-alone Operation. No special procedures are necessary if the counter is used as a stand-alone test instrument. Applying power and connecting the signal to the selected connector and selecting the desired switches and controls is all that is required.

(2) GPIB Operation. Installation of the counter in a GPIB-controlled system will vary with console or rack hardware. Therefore only general procedures can be suggested.

(a) The dimensions of the counter are 3.5 inches high by 16.75 inches wide by 19 inches deep. Rack mounting kits are available from the manufacturer of the counter to mount the instrument in a standard 19 inch width rack-mount cabinet or console. Ventilation of the counter is through the rear panel so it is not necessary or desirable to remove the top and bottom covers for cooling. Top and bottom covers should remain in place secured by screws to retain RFI integrity.

(b) Access to the rear panel is required to control selector switches and the GPIB address switches. The rear panel ventilating louvers and blower should not be blocked off from free air flow.

(c) Leads from frequency sources to—the counter front—panel connectors should be as short as possible. A common ground bus should tie the counter to other instruments and the GPIB controller. The length of power cable is not critical but the supplied cable should be retained and plugged into a powerline strip.

(d) The length of the GPIB interface cable should be as short as feasible and should be shielded against RFI to reduce data transmission contamination. Any keyboarding or fixed program controller may be connected, provided that the controller meets IEEE Standard 488/1975.

#### 2-7. Operation as Stand-alone Instrument.

a. Operating Modes. The counter has three principal modes of operation: automatic, manual, and externally enabled. Operation on Band A (300 - 950 MHz) is automatic; operation on Band B (925 MHz - 18 GHz) may be either automatic or manual. Externally enabled operation covers specific measurement techniques. Signals may be connected to

both the BAND A and BAND B inputs at the same time, but the counter will display only the input frequency selected by the appropriate BAND pushbutton switch on the front panel.

#### <u>b</u>. Preliminary Procedures.

(1) Rear-panel Switches. Set rear-panel switches as follows.

$\underline{\text{(a)}}$  GPIB IEEE STD 488/1975 ADDRESS SWITCH 7 to 0 (top of switch depressed).

(b) MIN. PRF switch to 50 Hz. (c) STORAGE switch to ON.

#### (2) Self-test.

(a) Press the POWER switch to turn on the counter. The display should light and the internal cooling fan should operate.

(b) Partially depress either of the two RESOLUTION switches and release it, so that neither switch remains in a depressed position. All digits in the display should indicate zero.

(c) Press the TEST DISPLAY switch. The display should indicate 88 888.88 while the switch is held in. Release the switch.

(d) Press the TEST 200 MHz switch. The display should indicate 200.00, with the two leading zeros blanked (unlighted), while the switch is held in. Release the switch.

(e) Press the right RESOLUTION switch and again hold the TEST 200 MHz switch in. The display should indicate 200.0, with the two leading zeros blanked. Release the switch.

$\begin{tabular}{ll} $(f)$ Press each RESOLUTION \\ switch in turn and note that the display \\ digit immediately above the switch \\ which has been depressed, and any digit \\ to the right, is blanked. \\ \end{tabular}$

(g) Unblank all display digits by repeating step (b).

c. Band A (300 - 950 MHz) Operation.

#### CAUTION

Peak power applied to the BAND A input connector should be between -10 and +10 dBm for normal operation. Peak input must not

exceed +27 dBm or damage to the counter may result, even if the counter is turned off.

- (1) Perform the preliminary procedures of step <u>b.</u>, above.

- (2) Connect the signal source to the BAND A input connector.

- (3) Depress the BAND A switch.

- (4) Depress the desired RESOLUTION switch.

- (5) If the input signal level is high enough for counting, both the LEVEL and LOCK indicators will light, and the measured frequency will be displayed.

#### NOTE

The REDUCE SIGNAL indicator is inoperative on Band A.

(6) Turn the SAMPLE RATE control to provide the desired display update rate. The GATE indicator will flash in accordance with the sample rate. If the control is set to its switched HOLD position, the display will retain the last reading. If a new reading is desired, press and release the RESET switch.

$\underline{d}$ . Band B (925 MHz - 18 GHz) Operation.

#### CAUTION

Peak power applied to the BAND B input connector should be within the following ranges for normal operation:

925 MHz - 10 GHz: -10 to +10 dBm 10 - 18 GHz: -5 to +10 dBm.

The peak input power must not exceed +30 dBm or damage to the counter may result, even if the counter is turned off.

(1) <u>Initial Procedures.</u>

(a) Perform the preliminary procedures of step b above.

$\underline{\mbox{(b)}}$  Connect the signal source to the BAND B input connector.

(c) Depress the BAND B switch.

(d) Depress the desired RESOLUTION switch.

(e) If the input signal level is high enough for counting, both the LEVEL and LOCK indicators will light. If the REDUCE SIGNAL indicator lights, the input signal power is approaching the maximum safe operating level and should be reduced.

(2) <u>Automatic Mode</u>. In the automatic mode, the counter searches for the input signal by sweeping from a start frequency which is 105 MHz above a preset frequency.

(a) Set the MANUAL SELECT/AUTO SWEEP switch to AUTO SWEEP. For full search, set the START SWEEP thumbwheel switches to 00.0 GHz.

(b) To improve acquisition speed, the sweep start frequency may be set by means of the START SWEEP thumb-wheel switches. The lowest frequency which can then be acquired and displayed will be 105 MHz above the switch settings; erroneous readings may be displayed if the frequency of the applied signal is less than 105 MHz above the switch settings.

$\underline{\text{(c)}}$  Adjust the SAMPLE RATE control as described in paragraph 2-7  $\underline{\text{c}}$  (6).

(3) Manual Mode. In the manual mode, the search sweep is inhibited, reducing the acquisition time. However, the signal frequency to be measured must be between 105 and 325 MHz above a preset frequency.

(a) Set the MANUAL SELECT/AUTO SWEEP switch to MANUAL SELECT.

(b) Set the PRESET FREQUENCY thumbwheel switches so that they indicate a frequency 105 to 325 MHz lower than the signal frequency. For example, if the frequency to be measured is expected to be 12.35 GHz, the thumbwheel switches should be set to indicate 12.2 GHz, which places the input frequency 105 to 325 MHz above the preset frequency. Erroneous readings may be displayed if the frequency of the applied signal is outside the preset range.

$\underline{\text{(c)}}$  Adjust the SAMPLE RATE control as described in paragraph 2-7  $\underline{\text{c}}$  (6).

#### 2-8. Externally Enabled Operation.

The use of the reara. Function. panel INPUT INHIBIT connector makes possible a class of measurements known as dynamic frequency measurements measurements made at a specified point in time on a signal whose frequency is some repetitive function of time. When a high emitter-coupled-logic (ECL) level is applied, the counter is inhibited from making a measurement. Thus a signal at the INPUT INHIBIT connector can be used as an enable signal to make a measurement at a desired time. width of the enable signal determines the duration of the measurement, typically 30 nanoseconds less than the applied pulse.

b. INPUT INHIBIT Requirements. INPUT INHIBIT circuit is designed to be compatible with either a 50 ohm impedance pulse generator or ECL devices. An internal termination of 50 ohms returned to -2 volts makes this dual compatibility possible. An ECL high level signal (-0.8 to -1.1 V) will inhibit measurement, while an ECL low level signal (-1.5 to -2.0 V) will enable measurement. ECL devices are designed to drive 50 ohm lines without reflections when the lines are terminated with 50 ohms returned to -2 V. The direct compatibility with a 50 ohm pulse generator results from the fact that zero volts from a 50 ohm source will produce -1 V at the INPUT INHIBIT (inhibiting the counter), while a -1 V signal into 50 ohms will produce -1.5 V at the INPUT INHIBIT thus enabling the counter.

#### 2-9. Pulse Profile Measurements

<u>a. Purpose.</u> Automatic pulse measurements can determine the average frequency of a pulse. In some cases, however, additional information may be necessary. For example, a pulse magnetron may exhibit substantial frequency shift near the leading and trailing edges of the pulse, or a pulsed Gunn diode oscillator may exhibit frequency shift during a pulse due to peak power thermal effects.

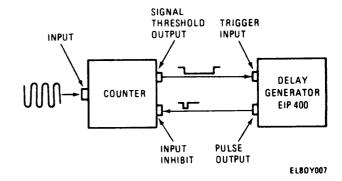

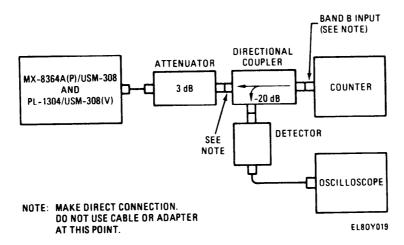

<u>b.</u> <u>Measurement Technique</u>. Measurements of these characteristics are easily made with the counter and a delaying pulse generator (see fig. 2-3).

Figure 2-3. Pulse Profile Measurement Test Setup

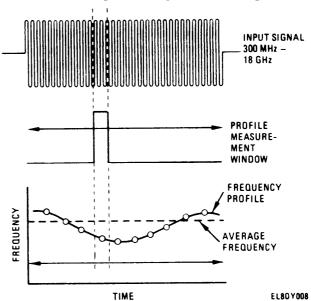

The SIGNAL THRESHOLD OUTPUT of the counter is used to trigger the pulse generator. The generator's output pulse is used as an enable input to the counter. As the pulse delay is varied, the measurement window can be "walked" through the pulse. A plot of frequency versus delay gives the frequency-versus-time profile of the pulse directly as shown in fig. 2-4. The width of the measurement window is determined by the width of the pulse generator output. Measurement windows of 50 nanoseconds or less can be used, although wider windows yield higher accuracy.

Figure 2-4. Pulse Profile Measurement

2-10. Dynamic Characteristics of Time Varying Signals.

a. Purpose. Many complex signals are not pulses at all but simply continuous signals whose frequency varies repetitively with time. One example is the measurement of the response of a device such as a voltage-controlled oscillator (VCO). A square wave applied to the tuning voltage will produce a response curve of frequency versus time, allowing measurement of various settling times such as post-tuning drift. Another possible application would be the measurement of linearity and amplitude for frequency-modulated radar altimeter signals.

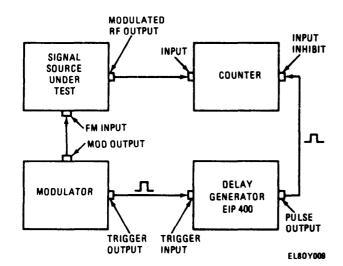

<u>b.</u> Measurement Technique. Fig. 2-5 shows a test setup designed to make measurements on time varying signals. It is similar to the pulse profile test setup, except that in this case, since there is always a signal present, a trigger must be obtained from the modulating source. This will trigger the pulse generator which controls the measurement.

#### 2-11. Multiple Pulse Signal Measurements.

<u>a. Purpose.</u> Another type of measurement is that of a repetitive sequence of pulses differing in frequency. In this

Figure 2-5. Time Varying Signal Measurement Test Setup

case, it is desirable to measure the frequency of each pulse in the sequence separately.

b. Measurement Technique. The same test setup as shown in fig. 2-5 is required, with the trigger pulse synchronous with the sequence. In this measurement, the INPUT INHIBIT is used simply to discriminate between pulses. The enabling pulse can be slightly wider than the pulse to be measured. The counter will automatically restrict the measurement window entirely within the pulse. By shifting the delay time of the enabling pulse, each input pulse of the sequence can be separately measured.

#### 2-12. Timing Considerations.

<u>a. General.</u> Under most circumstances, internal timing within the counter is of no concern to the user. However, in applications where a few nanoseconds are significant, some details of internal operation are important. These involve two areas: measurement window width and internal timing delays.

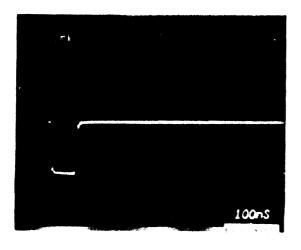

b. Measurement Window Width. The measurement window is the period during which the gate is actually open to enable the counting of a signal. gate width will typically be 30 nanoseconds narrower than the pulse applied to the INPUT INHIBIT connector. width of the gate is always an integral number of clock periods (5 nanoseconds). For applications where the measurement window needs to be known to an accuracy better than 20 nanoseconds, it is recommended that the GATE OUTPUT on the rear panel be observed directly on a high speed oscilloscope. The desired gate width may then be set by varying the INPUT INHIBIT pulse width. accurate pulse representation, the oscilloscope input should be terminated in a 50 ohm load.

c. Internal Timing Delays. When it is necessary to measure the signal frequency at a precise point in time, the internal delays of the measuring instrument can be significant. The total delay between the time a signal is applied to the counter input connector, and the time it is available to be

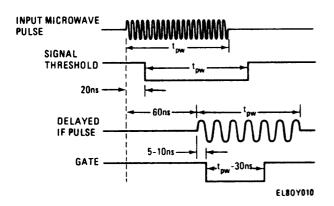

counted, is nominally 60 nanoseconds. The SIGNAL THRESHOLD OUTPUT on the rear panel typically occurs 20 nanoseconds after the signal is applied. The GATE OUTPUT at the rear panel occurs at the measurement time with virtually no delay. In other words, when absolute time positioning of a signal is required, it is necessary to consider that the GATE OUTPUT signal, which represents the measurement period, is actually making a measurement of the signal which appeared at the input connector 60 nanoseconds earlier. If the SIGNAL THRESH-OLD OUTPUT is used as an indication of input signal, then it occurs 40 nanoseconds prior to measurement. Fig. 2-6 shows the relative timing of these signals for a pulsed input signal. Timing, however, is not a function of input signal characteristics.

#### 2-13. Accuracy.

#### <u>a</u>. General Considerations.

- (1) In a cw frequency counter, measurement accuracy is generally specified as time base accuracy ±1 count. This means that the frequency measurement is in error by the same percentage as the time base reference oscillator. The maximum error in the time base is the sum of various possible errors, such as aging rate, temperature, etc.

- (2) The second type of error, ±1 count, is derived from the relative timing of gate and signal. Simply stated, if an event occurs every 400 milliseconds, a counter could measure

Figure 2-6. Internal Timing Delays

- either 2 or 3 events in a one second interval, since the processed input signal and the gate are asynchronous.

- (3) A third possible source of error in a cw counter is gate error. A gate is supposed to represent a precise number of reference oscillator cycles. Due primarily to differences in the rise and fall times of various circuits, the actual gate will usually be a fixed amount wider or narrower than desired. If this error is less than one period of the maximum input frequency, no counter error will occur. Thus a 300 MHz counter needs a gate accurate to about 3 nanoseconds.

- (4) Each of these three sources of error can contribute to the overall error In pulse frequency measurements. In fact for narrow pulses, the second and third sources of error, which are usually ignored in a cw counter, become the dominate sources of error in a pulse counter.

- <u>b. Time Base Errors.</u> A frequency error in the time base reference oscillator results in a proportional frequency measurement error. Two main sources of time base error are aging rate and temperature. The temperature compensated crystal oscillator (TCXO) reduces temperature instability to less than  $2 \times 10^{-6}$ . By calibration against a frequency standard, this error can be made less than one count, and thus becomes insignificant.

- <u>c.</u>Averaging Error. In order to obtain high resolution, the frequency of a number of measurements is averaged. Each individual measurement has a ±1 count uncertainty as previously noted. If N measurements are made, then an uncertainty of ±N counts is possible, but very unlikely. The resultant averaged measurement will follow the rules of statistics, in that successive measurements will vary randomly to a certain degree. In fact, most of the readings (63 percent) will fall between  $\pm \sqrt{N}$  counts; this is called the rms averaging error. N is the number of gates required to accumulate 100 microseconds or 1 millisecond of gate time. The gate is typically

30 nanoseconds narrower than the input pulse, so that

Averaging Error (rms) =

$$\frac{F}{\sqrt{PW - 0.03}}$$

where PW = pulse width in microseconds

F = 200 kHz with 100 μsec gate, Band A; or 60 kHz with 1 msec gate, Band A; or 100 kHz with 100 μsec gate, Band B; or 30 kHz with 1 msec gate, Band B.

#### <u>d.</u> Gate Error.

(1) When narrow pulses are counted, the gate is opened many times in order to obtain a high resolution measurement. Each time the gate opens and closes, there will be a small but finite error. The total error is proportional to the number of times the gate is cycled during a measurement, and is thus inversely proportional to the gate width. This error is also related to both temperature and input frequency. The worst case error, including all variables, is specified for the counter as:

$$\frac{\pm 100 \text{ kHz}}{PW - 0.03}$$

for Band A, and

$$\frac{\pm 40 \text{ kHz}}{\text{PW} - 0.03} \quad \text{for Band B}$$

where PW = pulse width in microseconds.

- (2) Unlike averaging error, which is random, gate error is systematic, and is not reduced by frequency averaging.

- 2-14. Techniques for Improving Accuracy.

- a. Time Base Calibration. A frequency error in the time base oscillator results in the same percentage error in the frequency reading for either cw or pulsed signals. By directly measuring the 10 MHz time base frequency at the 10 MHz OUTPUT connector with a standard of known accuracy, this error can be

determined and corrected. As an example, the measured time base output is  $10.0001~\mathrm{MHz}$ . The time base is thus  $1~\mathrm{x}~10^{-6}~\mathrm{high}$  in frequency, and all readings will be  $1~\mathrm{x}~10^{-6}~\mathrm{low}$  in frequency. Thus, a reading at 10 GHz will be 10 kHz low. Although the reading can be corrected for this error, the counter should be recalibrated as soon as possible.

#### <u>b</u>. Gate Error.

- (1) Gate error at any given frequency and pulse width can be virtually eliminated. This is accomplished by simulating a pulse input and determining the gate error. This calibration factor can then be added to, or subtracted from, the indicated measurement to obtain the correct frequency.