#### Errata

Title & Document Type: 71600 Series Installation and

Verification

Manual Part Number: 71600-90001

Revision Date: October 1990

#### **HP References in this Manual**

This manual may contain references to HP or Hewlett-Packard. Please note that Hewlett-Packard's former test and measurement, semiconductor products and chemical analysis businesses are now part of Agilent Technologies. We have made no changes to this manual copy. The HP XXXX referred to in this document is now the Agilent XXXX. For example, model number HP8648A is now model number Agilent 8648A.

#### **About this Manual**

We've added this manual to the Agilent website in an effort to help you support your product. This manual provides the best information we could find. It may be incomplete or contain dated information, and the scan quality may not be ideal. If we find a better copy in the future, we will add it to the Agilent website.

## **Support for Your Product**

Agilent no longer sells or supports this product. You will find any other available product information on the Agilent Test & Measurement website:

## www.tm.agilent.com

Search for the model number of this product, and the resulting product page will guide you to any available information. Our service centers may be able to perform calibration if no repair parts are needed, but no other support from Agilent is available.

# HP 71600 Series of Gbit/s Testers

# Installation and Verification Manual

#### **SERIAL NUMBERS**

This manual applies directly to:

HP 70841A 0.1-3 Gbit/s Pattern Generator with serial number(s) prefixed 3017U.

HP 70842A 0.1-3 Gbit/s Error Detector with serial number(s) prefixed 3017U.

HP 70845A 0.05-1 Gbit/s Pattern Generator with serial number(s) prefixed 3027U.

HP 70846A 0.05-1 Gbit/s Error Detector with serial number(s) prefixed 3027U.

For additional important information about serial numbers, see SERIAL NUMBER INFORMATION in Chapter 1.

Serial number information for other elements in the system is contained in the following manuals:

Display Mainframe see HP 70004A Installation and Verification Manual

see HP 70001A Installation and Verification Manual

Clock Source

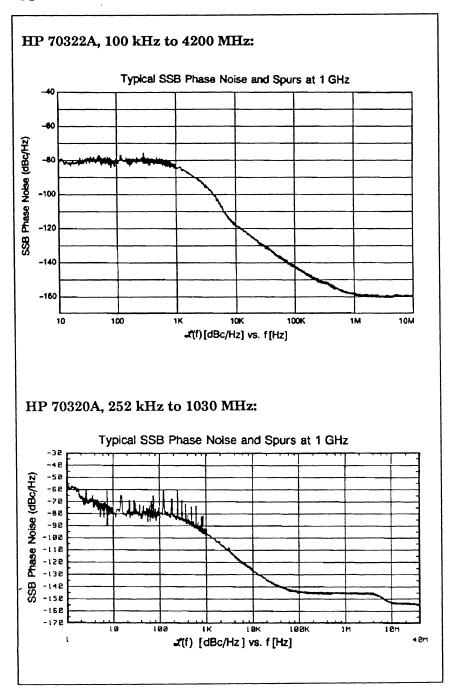

- see HP  $70320\mathrm{A}/70322\mathrm{A}$  Operating/Programming/Calibration

Manuals

© Copyright (1990), Hewlett-Packard Company

HP Part No. 71600-90001 Microfiche Part No. 71600-90026 Printed in U.K. October 1990

## CERTIFICATION

Hewlett-Packard Company certifies that this product met its published specifications at the time of shipment from the factory. Hewlett-Packard further certifies that its calibration measurements are traceable to the United States National Bureau of Standards, to the extent allowed by the Bureau's calibration facility and to the calibration facilities of other International Standards Organization members.

## WARRANTY

This Hewlett-Packard product is warranted against defects in materials and workmanship for a period of one year from date of shipment. During the warranty period, Hewlett-Packard Company will, at its option either repair or replace products which prove to be defective.

For warranty service or repair, this product must be returned to a service facility designated by HP. Buyer shall prepay shipping charges to HP and HP shall pay shipping charges to return the product to Buyer However, Buyer shall pay all shipping charges, duties, and taxes for products returned to HP from another country.

HP warrants that its software and firmware designated by HP for use with an instrument will execute its programming instuctions when properly installed on that instrument. HP does not warrant that the operation of the instrument, or software, or firmware will be uninterrupted or error free.

#### LIMITATION OF WARRANTY

The foregoing warranty shall not apply to defects resulting from improper or inadequate maintenance by Buyer. Buyer-supplied software or interfacing, unauthorized modification or misuse, operation outside of the environment specifications for the products, or improper site preparation or maintenance.

NO OTHER WARRANTY IS EXPRESSED OR IMPLIED. HP SPECIFICALLY DISCLAIMS THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

#### **EXCLUSIVE REMEDIES**

THE REMEDIES PROVIDED HEREIN ARE BUYER'S SOLE AND EXCLUSIVE REMEDIES. HE SHALL NOT BE LIABLE FOR ANY DIRECT, INDIRECT, SPECIAL INCIDENTAL, OR CONSEQUENTIAL DAMAGES, WHETHER BASED ON CONTRACT, TORT, OR ANY OTHER LEGAL THEORY.

# **ASSISTANCE**

Product maintenance agreements and other customer assistance agreements are available for Hewlett-Packara products.

For any assistance, contact your Hewlett-Packard Sales and Service Office. Addresses are provided at the back of this manual.

# **WARNING**

READ THE FOLLOWING NOTES BEFORE INSTALLING OR SERVICING ANY INSTRUMENT.

- 1. IF THIS INSTRUMENT IS TO BE ENERGISED VIA AN AUTO-TRANSFORMER MAKE SURE THAT THE COMMON TERMINAL OF THE AUTO-TRANSFORMER IS CONNECTED TO THE NEUTRAL POLE OF THE POWER SOURCE.

- 2. THE INSTRUMENT MUST ONLY BE USED WITH THE MAINS CABLE PROVIDED. IF THIS IS NOT SUITABLE, CONTACT YOUR NEAREST HP SERVICE OFFICE. THE MAINS PLUG SHALL ONLY BE INSERTED IN A SOCKET OUTLET PROVIDED WITH A PROTECTIVE EARTH CONTACT. THE PROTECTIVE ACTION MUST NOT BE NEGATED BY THE USE OF AN EXTENSION CORD (POWER CABLE) WITHOUT A PROTECTIVE CONDUCTOR (GROUNDING).

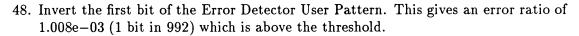

- 3. THE SERVICE INFORMATION FOUND IN THIS MANUAL IS OFTEN USED WITH POWER SUPPLIED TO AND PROTECTIVE COVERS REMOVED FROM THE INSTRUMENT. ENERGY AVAILABLE AT MANY POINTS MAY, IF CONTACTED, RESULT IN PERSONAL INJURY.

- 4. BEFORE SWITCHING ON THIS INSTRUMENT:

- (a) Make sure the instrument input voltage selector is set to the voltage of the power source.

- (b) Ensure that all devices connected to this instrument are connected to the protective (earth) ground.

- (c) Ensure that the line power (mains) plug is connected to a three-conductor line power outlet that has a protective (earth) ground. (Grounding one conductor of a two-conductor outlet is not sufficient).

- (d) Check correct type and rating of the instrument fuse(s).

#### 5. SERVICING INFORMATION:

- (a) This manual contains information, cautions and warnings which must be followed to ensure safe operation and to retain the instrument in safe condition. Service and adjustments should be performed only by qualified service personnel.

- (b) Any adjustment, maintenance and repair of the opened instrument under voltage should be avoided as much as possible and, when unavoidable, should be carried out only by a skilled person who is aware of the hazard involved.

- (c) Capacitors inside the instrument may still be charged even if the instrument has been disconnected from its source of supply.

- (d) Whenever it is likely that the protection has been impaired, the instrument must be made inoperative and be secured against any unintended operation.

## HP 71600 Series Overview

## Introduction

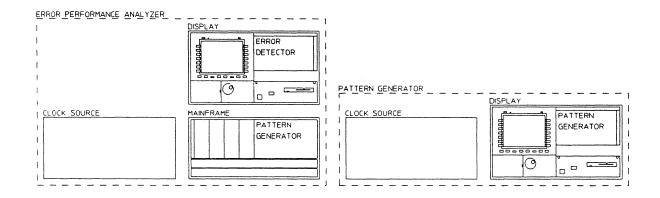

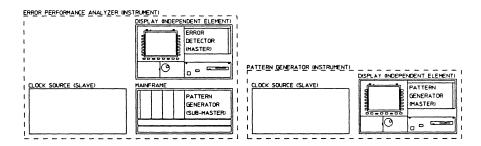

The HP 71600 Series can be configured into one of the following:

HP 71601A 0.05-1 Gbit/s Error Performance Analyzer

HP 71602A 0.05-1 Gbit/s Pattern Generator

HP 71603A 0.1-3 Gbit/s Error Performance Analyzer

HP 71604A 0.1-3 Gbit/s Pattern Generator

## **Systems Overview**

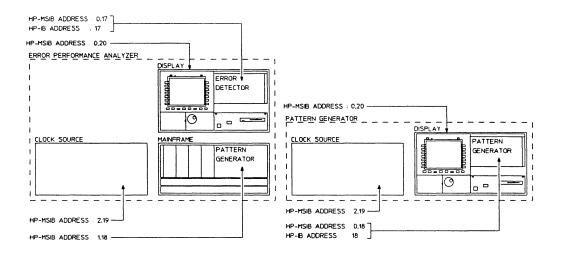

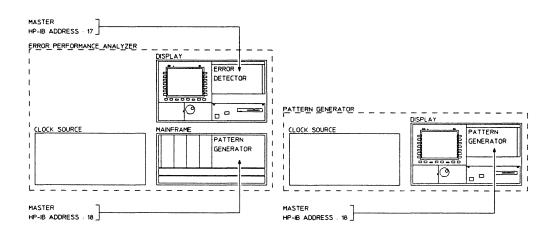

The basic systems are shown in the following illustrations:

The elements which make up your system are identified by product number in the following table:

| Element           | Error Performance Analyzer |                | Pattern Generator |                |

|-------------------|----------------------------|----------------|-------------------|----------------|

|                   | HP 71601A                  | HP 71603A      | HP 71602A         | HP 71604A      |

|                   | (.05-1 Gbit/s)             | (0.1-3 Gbit/s) | (.05-1 Gbit/s)    | (0.1-3 Gbit/s) |

| Display           | HP 70004A                  | HP 70004A      | HP 70004A         | HP 70004A      |

| Mainframe         | HP 70001A                  | HP 70001A      | -                 | -              |

| Pattern Generator | HP 70845A                  | HP 70841A      | HP 70845A         | HP 70841A      |

| Error Detector    | HP 70846A                  | HP 70842A      | -                 | -              |

| *Clock Source     | HP 70320A                  | HP 70322A      | HP 70320A         | HP 70322A      |

<sup>\*</sup> Clock Source is not supplied if Option 100 is ordered with your system.

# **Documentation Overview**

The manuals which are supplied with each system are listed in the following table:

| Element                   | ent Product Manual<br>Number |                                       | HP Part<br>Number | Comments                                                                           |  |

|---------------------------|------------------------------|---------------------------------------|-------------------|------------------------------------------------------------------------------------|--|

| System HP 71601A          |                              | Installation/Verification             | 71600-90001       | These manuals are                                                                  |  |

|                           | HP 71602A                    | Operating                             | 71600-90000       | supplied with all systems.                                                         |  |

|                           | HP 71603A                    | Programming                           | 71600-90003       |                                                                                    |  |

|                           | HP 71604A                    |                                       |                   |                                                                                    |  |

| Display                   | HP 70004A                    | Operation                             | 70004-90007       | These manuals are supplied                                                         |  |

|                           |                              | Installation/Verification 70004-90005 |                   | with all systems.                                                                  |  |

| Mainframe HP 70001A       |                              | Installation/Verification             | 70001-90021       | This manual is supplied with all systems operating as Error Performance Analyzers. |  |

| *Clock Source   HP 70320A |                              | Operating/Programming/<br>Calibrating | 08644-90047       | This manual is supplied with systems operating at 0.05-1 Gbit/s.                   |  |

|                           | HP 70322A                    | Operating/Programming/<br>Calibrating | 08665-90001       | This manual is supplied with systems operating at                                  |  |

|                           |                              |                                       |                   | 0.1-3 Gbit/s.                                                                      |  |

Service manuals covering the elements in your system are listed in the following table:

| Element       | Product<br>Number | Service Manual<br>HP Part Number | Comments                                 |

|---------------|-------------------|----------------------------------|------------------------------------------|

| System        | HP 71601A         | 71600-90002                      | This manual is required for all systems. |

|               | HP 71602A         |                                  |                                          |

|               | HP 71603A         |                                  |                                          |

|               | HP 71604A         |                                  |                                          |

|               |                   |                                  |                                          |

| Display       | HP 70004A         | 70004-90009                      | This manual is required for all systems. |

|               |                   |                                  |                                          |

| Mainframe     | HP 70001A         | 70001-90044                      | This is manual required for systems      |

|               |                   |                                  | operating as an Error Performance        |

|               |                   |                                  | Analyzer.                                |

| *01 1 0       | HD 700004         | 00045 00104                      |                                          |

| *Clock Source | HP 70320A         | 08645-90104                      | This manual is required for all systems. |

|               | HP 70322A         |                                  |                                          |

<sup>\*</sup> Clock Source documentation is not supplied if Option 100 is ordered with your system.

## **HP 71600 Series Installation and Verification Manual**

This manual is shipped from the factory with only the system installation and verification information.

When the Display and Mainframe Installation and Verification Manuals are unpacked they should be inserted into the *HP 71600 Series Installation and Verification Manual*, (all installation and verification information is then contained within the one binder).

## **User Tasks**

Listed below are typical user tasks and chapter references:

| Task                                                      | Chapter                 |

|-----------------------------------------------------------|-------------------------|

| Getting the system ready for use.                         | Installation 2          |

| Identifying error conditions and messages                 | Troubleshooting 5       |

| Verifying the system meets specification.                 | Performance Tests 4     |

| Understanding a master/slave Modular Measurement System.  | HP 71600 Series (MMS) 6 |

| Understanding a master/master Modular Measurement System. | Appendix A              |

| Controlling the system remotely through HP-IB             | HP-IB 7                 |

# **Contents**

| 1. | General Information                                                 |      |

|----|---------------------------------------------------------------------|------|

|    | Introduction                                                        | 1-1  |

|    | Options                                                             | 1-2  |

|    | Accessories Supplied                                                | 1-2  |

|    | Serial Number Information                                           | 1-2  |

|    | Returning Modules for Service                                       | 1-3  |

|    | Packaging Requirements                                              | 1-3  |

|    | Preparing a Module for Shipping                                     | 1-3  |

|    | Precautions                                                         | 1-5  |

|    | ESD Precautions                                                     | 1-5  |

|    | Static-safe Workstation                                             | 1-5  |

|    | Static-safe Accessories                                             | 1-6  |

|    | Display Cleaning                                                    | 1-6  |

|    | Display Cleaning                                                    | 10   |

| 2. | Installation                                                        |      |

|    | Preparation for Use                                                 | 2-2  |

|    | Initial Inspection                                                  | 2-2  |

|    | Operating Requirements                                              | 2-2  |

|    | Operating and Storage Environment                                   | 2-2  |

|    | Physical Specifications                                             | 2-3  |

|    | Power Requirements                                                  | 2-3  |

|    | Power Cables                                                        | 2-4  |

|    | Line Voltage Selection                                              | 2-4  |

|    | Display (HP 70004A) Line Voltage Selector                           | 2-4  |

|    | Clock Source (HP 70320A or HP 70322A) Line Voltage Selector         | 2-5  |

|    | Mainframe (HP 70001A) Line Voltage Selector                         | 2-6  |

|    | Line Fuses                                                          | 2-7  |

|    | Accessing the Display (HP 70004A) and Mainframe (HP 70001A) Fuses . | 2-7  |

|    | Accessing the Clock Source (HP 70320A or HP 70322A) Fuse            | 2-7  |

|    | Fuse Ratings                                                        | 2-7  |

|    | HP-MSIB Address Switches                                            | 2-8  |

|    | Factory Preset HP-MSIB Addresses                                    | 2-8  |

|    | Error Detector Module Address Switches                              | 2-8  |

|    | Pattern Generator Module Address Switches                           | 2-9  |

|    |                                                                     | 2-10 |

|    |                                                                     | 2-10 |

|    | - ·                                                                 | 2-11 |

|    |                                                                     | 2-11 |

|    |                                                                     | 2-11 |

|    |                                                                     | 2-11 |

|    |                                                                     | 2-13 |

|    | ·                                                                   | 2-14 |

|    | System Verification                                                                  | 2-16         |

|----|--------------------------------------------------------------------------------------|--------------|

|    | Error Performance Analyzer System Verification                                       | 2-16         |

|    | Pattern Generator System Verification                                                | 2-10         |

|    | Selftest at Power-on                                                                 | 2-18         |

|    | Installing/Removing Modules                                                          | 2-20<br>2-21 |

|    | Installing a Module into a Display                                                   |              |

|    | Installing a Module into a Display                                                   | 2-21         |

|    | Installing a Module into a Mainframe                                                 | 2-22         |

| 3. | Specification                                                                        |              |

|    | Introduction                                                                         | 3-1          |

| 4. | Performance Tests                                                                    |              |

|    | Introduction                                                                         | 4-1          |

|    | Module Verification                                                                  | 4-1          |

|    | System Verification                                                                  | 4-1          |

|    | Test Levels                                                                          |              |

|    | Test Levels                                                                          | 4-1          |

|    | Calibration Cycle                                                                    | 4-2          |

|    | Warm-up Time                                                                         | 4-2          |

|    | Recommended Test Equipment                                                           | 4-3          |

|    | Operational Verification                                                             | 4-4          |

|    | Pattern Generator Performance Tests                                                  | 4-4          |

|    | Test Frequencies                                                                     | 4-4          |

|    | Clock Source                                                                         | 4-5          |

|    | Pattern Generator Module Preliminary Setup                                           | 4-5          |

|    | Clock Input Levels                                                                   | 4-6          |

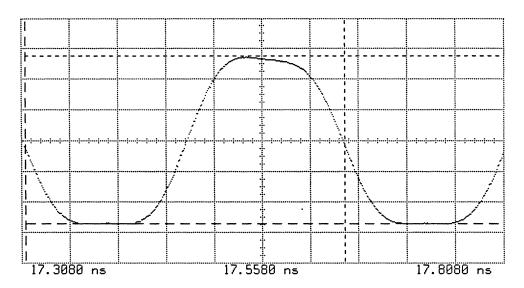

|    | Clock Output Waveforms                                                               | 4-10         |

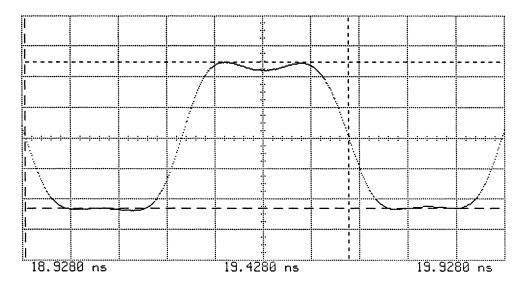

|    | Data Output Waveforms                                                                | 4-16         |

|    | Trigger Output Waveform and Data Output Intrinsic Jitter                             | 4-22         |

|    | PRBS 2 <sup>n</sup> -1 Pattern Length                                                | 4-22         |

|    | PRBS 2 <sup>n</sup> Variable Mark Density                                            |              |

|    | DDDC 2° n Zone Cubetitution                                                          | 4-30         |

|    | PRBS 2^n Zero Substitution                                                           | 4-34         |

|    | Error Add                                                                            | 4-38         |

|    | User Selectable Patterns and Memory Backup                                           | 4-40         |

|    | Auxiliary Input Test                                                                 | 4-46         |

|    | Error Detector Performance Tests                                                     | 4-50         |

|    | Test Frequencies                                                                     | 4-50         |

|    | Error Detector Module Preliminary Setup (Master/Slave)                               | 4-51         |

|    | Preliminary Setup (Master/Master)                                                    | 4-52         |

|    | Clock Input Levels                                                                   | 4-54         |

|    | PRBS 2 <sup>n</sup> -1 Pattern Synchronization, Error Detect and Audible Indicator . | 4-57         |

|    | PRBS 2 <sup>n</sup> Pattern Synchronization, Error Detect and Memory Back up         | 4-61         |

|    | PRBS 2 <sup>n</sup> with Variable Mark Density                                       | 4-65         |

|    | PRBS 2 n Pattern with Zero Substitution                                              |              |

|    |                                                                                      | 4-68         |

|    | User Selectable Pattern Synchronization and Error Detect                             | 4-71         |

|    | Data Input Range (Automatic 0/1 Threshold)                                           | 4-74         |

|    | Error Output Waveform and Data Input Delay                                           | 4-78         |

|    | Data Input Invert                                                                    | 4-82         |

|    | Pattern Synchronization Threshold                                                    | 4-85         |

| <b>5.</b> | Troubleshooting                                  |                |

|-----------|--------------------------------------------------|----------------|

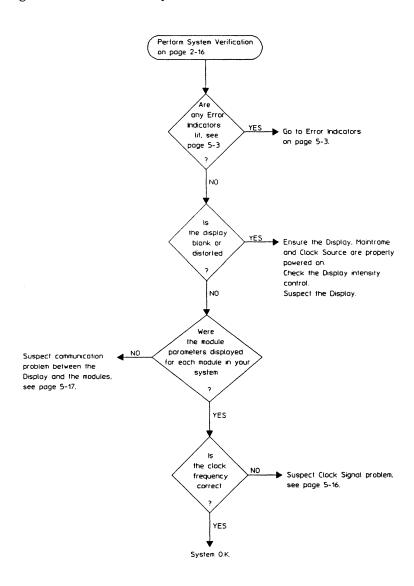

|           | Entry Chart                                      | 5-1            |

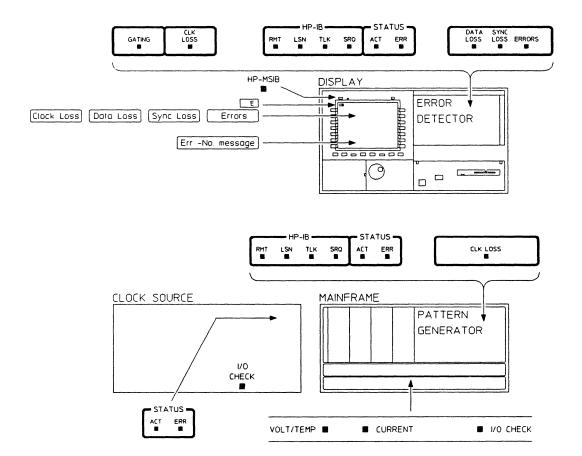

|           | System Indicators                                | 5-2            |

|           | Error Indicators                                 | 5-3            |

|           | VOLT/TEMP Troubleshooting                        | 5-4            |

|           | CURRENT Troubleshooting                          | 5-5            |

|           |                                                  | 5-6            |

|           |                                                  | 5-8            |

|           |                                                  | 5-8            |

|           |                                                  | 16             |

|           |                                                  | 16             |

|           |                                                  | 16             |

|           | 211211 2000 210111111111111111111111111          | 17             |

| c         | HP 71600 Series Modular Measurement System       |                |

| 6.        |                                                  | 3-2            |

|           |                                                  | 3-2<br>3-2     |

|           |                                                  | 5-4<br>5-4     |

|           |                                                  | 5-4<br>5-4     |

|           |                                                  |                |

|           | <b></b>                                          | - <del>5</del> |

|           |                                                  | 3-5            |

|           | <del></del>                                      | 6-5            |

|           |                                                  | 6-6            |

|           | <del></del>                                      | 6-7            |

|           | 0                                                | 8-6            |

|           | HP 71600 Series HP-MSIB Cabling                  | 6-8            |

| 7.        | Hewlett-Packard Interface Bus (HP-IB)            |                |

|           | Preset Addresses                                 | 7-1            |

|           | Changing Addresses                               | 7-2            |

|           |                                                  | 7-2            |

|           | Cabling (HP-IB)                                  | 7-2            |

|           | Connecting Your System to an HP-IB Controller    | 7-3            |

|           |                                                  | 7-3            |

|           |                                                  |                |

| A.        | Master/Master Configuration                      |                |

|           |                                                  | <b>\</b> -1    |

|           |                                                  | <b>1</b> -1    |

|           | ,                                                | 1-2            |

|           |                                                  | <b>1-</b> 3    |

|           | HP 71600 Series in a Master/Master Configuration | <b>1-3</b>     |

| В.        | Instrument Operation                             |                |

|           | Introduction                                     | 3-:            |

|           |                                                  | B-2            |

|           |                                                  | B-2            |

|           |                                                  | B-2            |

|           |                                                  | 3-;            |

|           | 1 0                                              | 3-3            |

|           |                                                  | •              |

# **General Information**

## Introduction

This chapter contains general information about the HP 71600 Series System and is divided into the following sections:

**Options** Lists all the options available with your system.

**Accessories Supplied** Lists the accessories supplied with your system.

Serial Number Explains the Hewlett-Packard serial numbering system.

Information

Returning Modules for Contains information on how to return a module to

Service Hewlett-Packard for service.

Precautions Highlights electrostatic discharge procedures and accessories

available. This section also contains information on cleaning the

display.

## **Options**

The options which may have been ordered with your system are listed below:

Option 100 Delete the Clock Source.

Option 200 Delete the HP 15680A RF Accessory Kit.

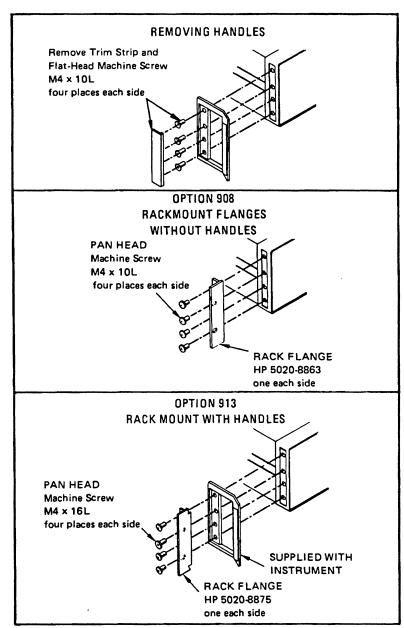

Option 908 Rack mount flanges for systems without handles fitted.

Option 910 Extra set of manuals - provides an additional set of installation/verification

and operating manuals for your system.

Option 913 Rack mount flanges for systems with handles fitted.

Option + W30 Two years additional hardware support beyond the standard one-year warranty.

# **Accessories Supplied**

The accessories supplied with your system are listed below:

- HP 15680A RF Accessory Kit

- HP-MSIB cables:

Three cables supplied with the Error Performance Analyzer system Two cables supplied with the Pattern Generator system

■ Line power cables:

Three cables supplied with the Error Performance Analyzer system Two cables supplied with the Pattern Generator system

- 8 mm hex-ball driver

- Four 1/8 cosmetic panels (HP 5061-9006) required for the Mainframe in the Error Performance Analyzer system

- HP 11500B N-type cable (not supplied when Option 100 is ordered)

- Front Handles for the Clock Source (HP 70320A/22A)

#### Serial Number Information

Attached to each element in your system is a serial number plate. A typical serial number is in the form XXXXUXXXXX. It is in two parts; the first four digits and the letter are the serial prefix and the last five are the suffix, the letter designates the country of origin - U is the United Kingdom. The prefix is the same for identical elements, it only changes when a change is made to an element in your system. The suffix however, is assigned sequentially and is different for each element. The contents of this manual apply to the elements with the serial number prefix(es) listed under SERIAL NUMBERS on the title page.

A system manufactured after the printing of this manual may have a number prefix that is not listed on the title page. The unlisted serial number prefix indicates the system is different from those described in this manual. The manual for this new element is accompanied by a *Manual Changes* supplement. This supplement contains *change information* that explains how to adapt the manual to the new element.

In addition to change information, the supplement may contain information for correcting errors in the manual. To keep this manual as current and accurate as possible, Hewlett-Packard recommends that you periodically request the latest Manual Changes supplement. The supplement for this manual is identified with the manual print date and part number, both of which appear on the manual title page. Complementary copies of the supplement are available from Hewlett-Packard. For information concerning a serial number prefix that is not listed on the Manual Changes supplement, contact your nearest Hewlett-Packard office.

# **Returning Modules for Service**

This section explains how you return a module to Hewlett-Packard for servicing.

## **Packaging Requirements**

Instruments and modules can be damaged as a result of using packaging materials other than those specified. Never use styrene pellets as packaging material. They do not adequately cushion the instrument nor prevent it from shifting in the carton. They also cause instrument damage by generating static electricity.

## Preparing a Module for Shipping

- 1. Fill out a blue repair tag (located at the end of this manual) and attach it to the instrument or module. Include any error messages or specific performance data related to the problem. If a blue tag is not available, the following information should be noted and sent with the module or instrument:

- Type of service required.

- Description of the problem.

- Whether problem is constant or intermittent.

- Name and phone number of technical contact person.

- Return address.

- Model number of returned module or instrument.

- Full serial number or returned module or instrument.

- List of any accessories returned with the module or instrument.

- 2. Pack the module or instrument in the appropriate packaging materials. Original shipping or equivalent materials should be used. If the original or equivalent material cannot be obtained, follow the instructions below:

#### Caution

Inappropriate packaging of the instrument may result in damage to the instrument during transit.

- Wrap the instrument in anti-static plastic to reduce the possibility of damage caused by

- Use a double-walled, corrugated cardboard carton of 159 kg (350 lb) test strength.

## Caution

If you are shipping a complete system, remove the module(s) from Display and Mainframe, individually pack each element, then ship them to Hewlett-Packard.

- The carton must be large enough to allow 3- to 4-inches on all sides of the instrument for packing material and strong enough to accommodate the weight of the instrument.

- Surround the instrument with 3- to 4-inches of packing material, to protect the instrument and prevent it from moving in the carton.

- If packing foam is not available, the best alternative is S.D.-240 Air Cap<sup>TM</sup> from Sealed Air Corporation (Commerce, California 90001). Air Cap<sup>TM</sup> looks like a plastic sheet filled with air bubbles.

- Use the pink (anti-static) Air Cap<sup>TM</sup> to reduce static electricity. Wrapping the instrument several times in this material will protect the instrument and prevent it from moving in the carton.

- 3. Seal the carton with strong nylon adhesive tape.

- 4. Mark the carton FRAGILE, HANDLE WITH CARE.

- 5. Retain copies of all shipping papers.

## **Precautions**

#### **ESD Precautions**

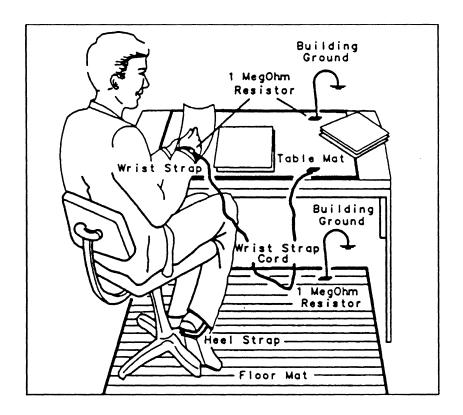

Electrostatic discharge (ESD) can damage or destroy electronic components. All work on electronic assemblies should be performed at a static-safe workstation.

#### Static-safe Workstation

A typical static-safe workstation is illustrated in the following diagram. There are two types of ESD protection:

- Wrist-strap (with > 1 M $\Omega$  isolation to ground) with table-mat.

- Heel-strap (with > 1 M $\Omega$  isolation to ground) with conductive floor-mat.

These two types must be used together to ensure adequate ESD protection. Isolation to ground must be provided for personnel protection.

#### **Static-safe Accessories**

The following table lists the accessories that may be ordered through any Hewlett-Packard sales and service office.

| HP Part<br>Number | Description                                                                                                                                                                   |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 9300-0797         | 3M static control mat 0.6 m x 1.2 m (2 ft x 4 ft) and 4.6 m (15 ft) of ground wire. (The wrist-strap and wrist-strap cord are not included. They must be ordered separately.) |  |

| 9300-0980         | Wrist-strap cord 1.5 m (5 ft).                                                                                                                                                |  |

| 9300-1383         | Wrist-strap, color black, stainless steel, has four adjustable links and a 7 mm post-type connection.                                                                         |  |

| 9300-1169         | ESD heel-strap (reusable 6- to 12- months).                                                                                                                                   |  |

| *92175A           | Black, hard surface, static control mat, 1.2 m x 1.5 m (4 ft x 5 ft)                                                                                                          |  |

| *92175B           | Brown, soft surface, static control mat, 1.2 m x 2.4 m (4 ft x 8 ft)                                                                                                          |  |

| *92175C           | Small, black, hard surface, static control mat, 0.9 m x 1.2 m (3 ft x 4 ft)                                                                                                   |  |

| *92175T           | Table-top static control mat, 58 cm x 76 cm (23 in x 30 in)                                                                                                                   |  |

| *92176A           | Natural color anti-static carpet, 1.2 m x 1.8 m (4 ft x 6 ft)                                                                                                                 |  |

| *92176B           | Natural color anti-static carpet, 1.2 m x 2.4 m (4 ft x 8 ft)                                                                                                                 |  |

| *92176C           | Russet color anti-static carpet, 1.2 m x 1.8 m (4 ft x 6 ft)                                                                                                                  |  |

| *92176D           | Russet color anti-static carpet, 1.2 m x 2.4 m (4 ft x 8 ft)                                                                                                                  |  |

<sup>\*</sup>Can also be ordered by calling HP DIRECT Phone (800) 538 8787.

# **Display Cleaning**

To avoid damaging the coating on the display, use a thin-film cleaner such as Hewlett-Packard Video Clean Kit (HP part number 92193). The kit includes an non-abrasive cleaning cloth.

Hand and laboratory paper towels are abrasive, if these are used they may Caution damage the coating on the display.

# 2. Installation

# Installation

Modules

This chapter enables you to install your system ready for use. The information is presented under the following headings:

| Preparation for Use  | Provides information you should read before you install your system. It contains information on initial inspection, power requirements, address switches and rack mount kits. |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System Installation  | Shows you how to install your system. As you progress through<br>the procedure, you will be directed to other relevant information.                                           |

| System Verification  | Describes how you power-on and verify correct system installation, and directs you to troubleshooting (if there are any problems).                                            |

| Selftest at Power-on | Details the instrument status during selftest at power-on.                                                                                                                    |

| Installing/Removing  | Describes how you install modules into a Display and Mainframe.                                                                                                               |

## **Preparation for Use**

This section should be read before you install your system. It contains the following:

- Initial Inspection

- Operating Requirements

- Line Voltage Selection

- Line Fuses

- Power Cables

- HP-MSIB Address Switches

- HP-IB Address Switches

- Bench Operation

- Rack Mount Kits

## **Initial Inspection**

## Warning

To avoid hazardous electrical shock, do not perform electrical tests when there are signs of shipping damage to any portion of the outer enclosure (covers, panels, meters).

Inspect the shipping container for damage. If the shipping container or cushioning material is damaged, it should be kept until the contents of the shipment have been checked for completeness and the elements in your system have been checked both mechanically and electrically. Procedures for checking the electrical operation are given in chapter 4 of this manual.

If any element in your system appears damaged or is defective, contact the nearest Hewlett-Packard service office. Hewlett-Packard will arrange for repair or replacement of the equipment without waiting for a claim settlement. Retain the shipping materials for the carrier to inspect.

Mainframes and stand-alone instruments such as the HP 70004A Display, are shipped with the front handles attached.

Undamaged shipping materials should be kept. Original HP or equivalent shipping materials are required for system or module re-shipment, as substandard packaging may result in damage. Refer to *Returning Modules for Service* in chapter 1 for information on re-shipment.

## **Operating Requirements**

#### **Operating and Storage Environment**

The system may be operated in temperatures from 0 °C to +45 °C. For storage, the temperature range is -40 °C to +65 °C.

The system should be protected against temperature extremes which may cause condensation within the elements in your system.

#### **Physical Specifications**

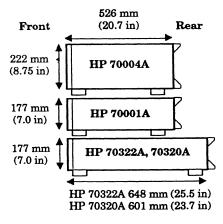

The physical dimensions and weight of each element in your system are contained in chapter 3 Specifications.

#### **Power Requirements**

The line voltage requirements for the Display, Mainframe and Clock Source are as follows:

115 V line operation: 90 to 132 V ac, 47 to 66 Hz 230 V line operation: 198 to 264 V ac, 47 to 66 Hz

The maximum power consumption is as follows:

Display

260 W maximum, 350 VA maximum

Mainframe

310 W maximum, 570 VA maximum

Clock Source

Refer to the Operating/Programming/Calibrating manual.

## Warning

Before turning the system on, make sure it is grounded through the protective conductor of the power cable to a socket outlet with protective earth contact. Any interruption of the protective (grounding) conductor inside or outside the instrument, or disconnection of the protective earth terminal, can result in personal injury.

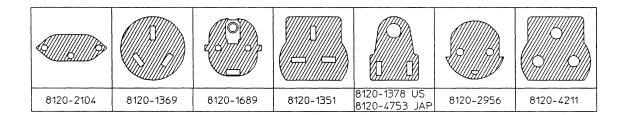

#### **Power Cables**

The Display, Mainframe and Clock Source are equipped with a three-wire power cable. When connected to a properly grounded power outlet, this cable grounds the instrument case. The power cable shipped with each instrument depends on the country of destination. The plug configuration and the power cable part numbers are listed below. If the appropriate power cable(s) are not supplied with your system or are damaged, notify the nearest Hewlett-Packard sales and service office and replacement(s) will be provided.

The color code used in each power cable is given below:

Line Brown

Neutral Blue

Ground Green/yellow

## Line Voltage Selection

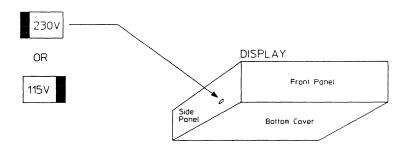

#### Display (HP 70004A) Line Voltage Selector

#### Caution

Before you connect the power cable to the Display, check that the LINE VOLTAGE SELECTOR switch is set for the correct line voltage source.

If the wrong voltage is selected, one of the following may happen:

If 115 V line operation is selected and you connect to a 230 V ac line power source, the fuse may blow.

If 230 V line operation is selected and you connect to a 115 V ac line power source, the instrument will not power-on correctly.

The LINE VOLTAGE SELECTOR slide switch is located through a slot in the left side-panel.

#### Clock Source (HP 70320A or HP 70322A) Line Voltage Selector

#### Caution

Before you connect the power cable to the Clock Source, check that the LINE VOLTAGE SELECTOR is set for the correct line voltage source.

If the wrong voltage is selected, one of the following may happen:

If 115 V line operation is selected and you connect to a 230 V ac line power source, the fuse may blow.

If 230 V line operation is selected and you connect to a 115 V ac line power source, the instrument will not power-on correctly.

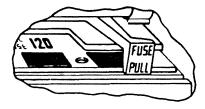

The LINE VOLTAGE SELECTOR switch is located in the line-module housing on the rear panel. To change the voltage, use the following procedure:

- 1. Open cover door, pull the FUSE PULL lever and rotate to the left. Remove the fuse.

- 2. Remove the LINE VOLTAGE SELECTOR card. Position the card so that the required line voltage is visible when the card is firmly pushed into the slot.

- 3. Rotate the fuse pull lever to its normal position. Insert a fuse of the correct rating into the holder. Close the cover door.

Operating voltage is shown in module window.

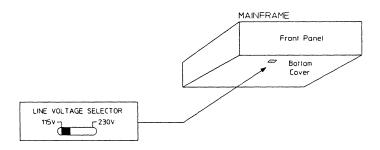

#### Mainframe (HP 70001A) Line Voltage Selector

#### Caution

Before you connect the power cable to the Mainframe, check that the LINE VOLTAGE SELECTOR switch is set for the correct line voltage source.

If the wrong voltage is selected, one of the following may happen:

If 115 V line operation is selected and you connect to a 230 V ac line power source, the fuse may blow.

If 230 V line operation is selected and you connect to a 115 V ac line power source, the instrument will not power-on correctly.

The LINE VOLTAGE SELECTOR slide switch is located through a slot in the bottom panel (the switch is set for 115 V operation in the above diagram).

## **Line Fuses**

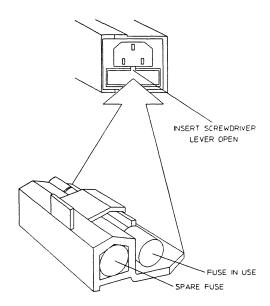

The line fuses of the Display, Mainframe and Clock Source are located in the line-module housings on the rear panel.

#### Accessing the Display (HP 70004A) and Mainframe (HP 70001A) Fuses

The Display and Mainframe use similar line-module housings (see the following diagram). To access the fuses:

- 1. Ensure no power cable is connected to the line-module housing.

- 2. Use a screwdriver to lever open the fuse holder. A spare line fuse is located inside the fuse holder.

#### Accessing the Clock Source (HP 70320A or HP 70322A) Fuse

The line fuse is located in the line-module housing. To access the fuse, refer to step 1 and the diagram in the Clock Source LINE VOLTAGE SELECTOR procedure on page 1-6.

## **Fuse Ratings**

The fuse ratings and the part numbers for 115 V ac and 230 V ac operation are listed below:

The Display and Mainframe fuse rating are 6.3 A, 250 V (HP 2110-0703) for both 115 and 230 V ac operation.

The Clock Source fuse ratings are 4 A, 250 V (HP 2110-0055) for 115 V ac operation and 2.5 A, 250 V (HP 2110-0083) for 230 V ac operation.

#### **HP-MSIB Address Switches**

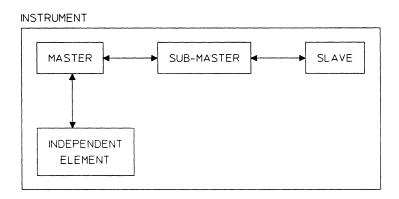

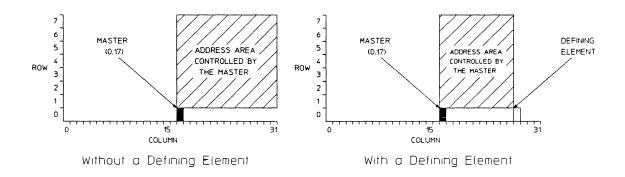

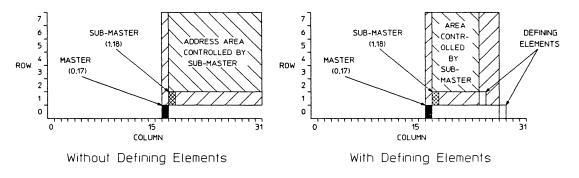

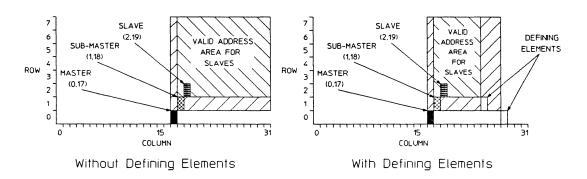

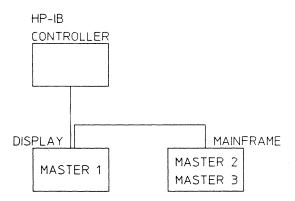

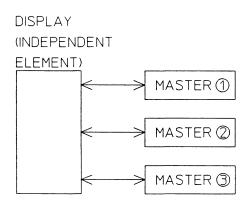

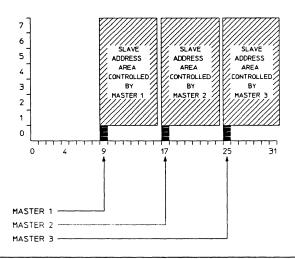

The HP-MSIB address switches are factory preset to configure your Error Performance Analyzer or Pattern Generator as a master/slave Modular Measurement System (MMS).

If you want to change the master/slave addressing or want to change to master/master configuration, ensure you are fully aware of the HP-MSIB address protocol, see chapter 6.

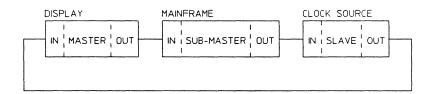

In an Error Performance Analyzer system the Error Detector master module controls the slave Pattern Generator module and the Clock Source. The Pattern Generator module (a slave to the Error Detector) is a sub-master to the Clock Source. The Clock Source is controlled directly by the Pattern Generator, and indirectly by the Error Detector (through the Pattern Generator).

In a Pattern Generator system the master module is the Pattern Generator, it controls the slave Clock Source.

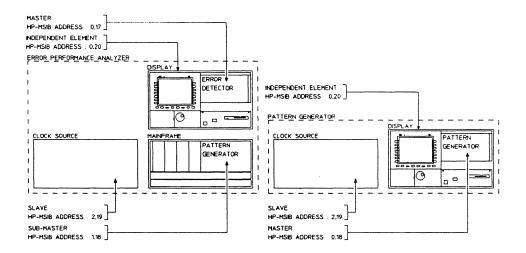

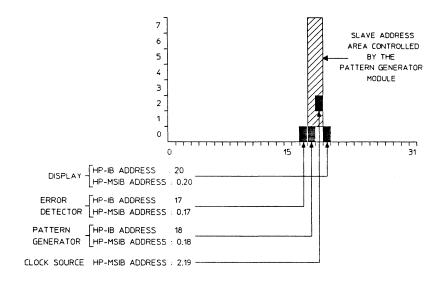

## Factory Preset HP-MSIB Addresses

The factory preset HP-MSIB addresses (row,column) are listed below:

Display : 0, 20 Error Detector : 0, 17\*

Pattern Generator: 1, 18\* (for the Error Performance Analyzer)

: 0, 18\* (for the Pattern Generator system)

Clock Source : 2, 19

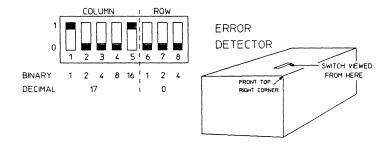

#### **Error Detector Module Address Switches**

These are accessed through a slot on top of the module. The factory preset settings are shown in the following diagram:

<sup>\*</sup> Column value defines the factory preset HP-IB addresses.

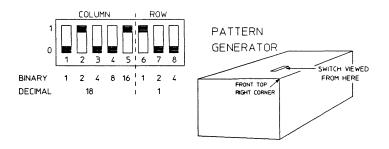

## Pattern Generator Module Address Switches

These are accessed through a slot on top of the module. The factory preset settings for a Pattern Generator module in an Error Performance Analyzer system are shown in the following diagram:

Note

The factory preset settings for a Pattern Generator module in a Pattern Generator system are (0, 18).

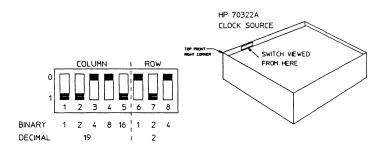

#### Clock Source Address Switches

The factory preset switch settings are shown in the following diagram:

The above switch refers to the HP 70322A Clock Source.

To access the HP-MSIB switches:

- 1. Remove the two side handles, using a large posi-driver.

- 2. Remove the two top rear feet, using a small posi-driver.

- 3. Remove the two top roundhead screws, using a size T-15 torque-driver (part number HP 8710-1625 which is part of the Torque-driver Kit HP 8710-1543).

- 4. Remove the 5 countersunk screws and metal strip on each side of the top cover, using a size T-10 torque-driver (part number HP 8710-1624).

- 5. Unscrew the rear central countersunk screw, using a large posi-driver.

- 6. Slide the top cover to the rear to access the address switches.

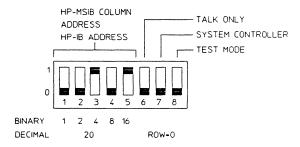

#### **Display Address Switches**

These are located on the rear panel of the HP 70004A Display, it has no row switches (it defaults to row 0) - only column switches (the factory preset settings are shown in the following diagram):

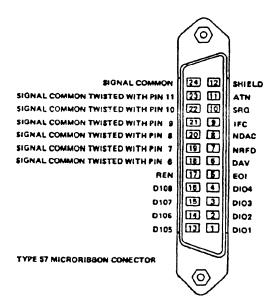

#### **HP-IB Address Switches**

The HP-MSIB address switches in the Error Detector and Pattern Generator modules also act as HP-IB switches. If you want your system to communicate over the HP-IB:

The row switches must be set to  $\theta$ .

The column switches define the HP-IB address.

If you want to change an HP-IB address (ie, use an address that is different from that defined by the *column* switch settings), it is recommended that you use the Display *HP-IB Address* function, see the *HP 71600 Series Operating Manual*.

#### Caution

It is not recommended that you change the HP-IB address using the HP-MSIB/HP-IB switches, as these also change the HP-MSIB address. If the HP-MSIB address protocol is violated your system will fail to operate.

## Factory Preset HP-IB Addresses

The Error Detector HP-IB address is factory preset to 17 (column part of HP-MSIB switch setting).

The Pattern Generator HP-IB address is factory preset to 18.

## **Bench Operation**

Plastic feet are included with Mainframes and stand-alone instruments to provide bench operation convenience. The plastic feet are self-aligning when systems are to be stacked.

#### **Rack Mount Installation**

Front handles must be removed when fitting the system rack mount options.

The rack mounts that are available are illustrated in the diagram on the page opposite. Angled brackets (HP 12679C) may be ordered to provide additional rear or side support for the rack mounted instruments. The table below lists the rack mount kit part numbers.

| Device       | Rack Mount Kit |              |  |

|--------------|----------------|--------------|--|

|              | Option 908     | Option 913   |  |

| Display      | HP 5062-3979   | HP 5062-3985 |  |

| Mainframe    | HP 5062-3978   | HP 5062-3984 |  |

| Clock Source | HP 5062-3978   | HP 5062-3984 |  |

NOTE: LEFT FRONT IS SHOWN IN EACH EXAMPLE.

# **System Installation**

Your HP 71600 Series can be installed to operate as an Error Performance Analyzer or as a Pattern Generator system.

Use the following table to identify the elements (by product number) which make up your system:

| Element           | Error Performance Analyzer |                | Pattern Generator |                |

|-------------------|----------------------------|----------------|-------------------|----------------|

|                   | HP 71601A                  | HP 71603A      | HP 71602A         | HP 71604A      |

|                   | (.05-1 Gbit/s)             | (0.1-3 Gbit/s) | (.05-1 Gbit/s)    | (0.1-3 Gbit/s) |

| Display           | HP 70004A                  | HP 70004A      | HP 70004A         | HP 70004A      |

| Mainframe         | HP 70001A                  | HP 70001A      | -                 | -              |

| Pattern Generator | HP 70845A                  | HP 70841A      | HP 70845A         | HP 70841A      |

| Error Detector    | HP 70846A                  | HP 70842A      | -                 | _              |

| *Clock Source     | HP 70320A                  | HP 70322A      | HP 70320A         | HP 70322A      |

<sup>\*</sup> Clock Source is not supplied if Option 100 is ordered with your system.

Caution

Ensure that no power cables are connected. Also check that the LINE power switches are set to off.

#### **Procedure**

#### Caution

Ensure that the Display, Mainframe and Clock Source line voltage selector switches are set for the line voltage being used, also check that the ratings of the fuses, see pages 2-4 and 2-7.

- 1. Use the factory preset HP-MSIB and HP-IB addresses to install the Display, Module(s) and Clock Source as a master/slave system, see the diagram on the previous page and pages 2-8 to 2-11.

- 2. Install your module (the *Error Detector* for Error Performance Analyzers and the *Pattern Generator* for Pattern Generators) into the Display, see page 2-21.

- 3. If your system is an Error Performance Analyzer, install your Pattern Generator module into your Mainframe, see page 2-22.

- 4. Locate and secure the four 1/8 width cosmetic panels into the Mainframe.

- 5. Arrange the elements which make up your system for bench operation. The plastic feet on the Display, Mainframe and Clock Source are self aligning when systems are stacked. To rack mount your system, refer to *Rack Mount Installation*, see page 2-11.

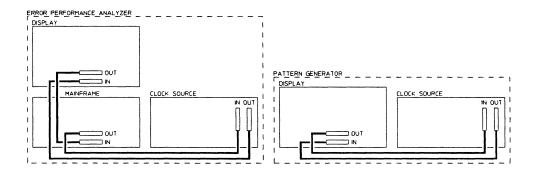

- 6. Connect the HP-MSIB cables (to suit your system) as follows:

#### Caution

Your system must be powered down when connecting or disconnecting HP-MSIB cables.

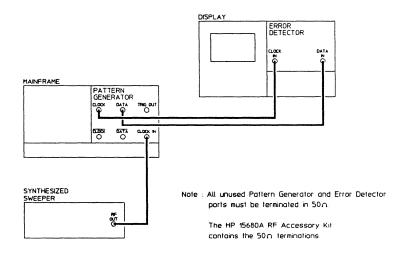

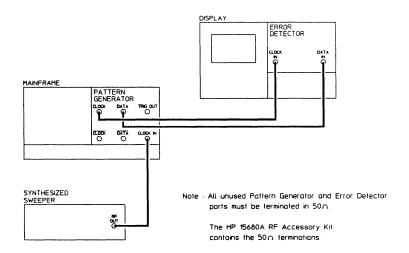

The diagram shows the systems viewed from the rear.

#### Note

If the Clock Source is not supplied (Option 100), HP-MSIB cabling is between the Display and the Mainframe in an *Error Performance Analyzer* system, in a *Pattern Generator* system no external HP-MSIB cables are required.

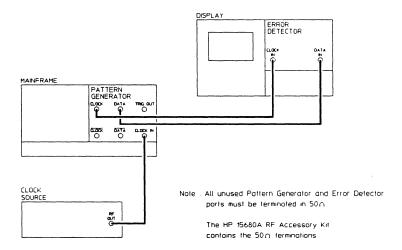

7. Connect the CLOCK IN port of the Pattern Generator module to the RF OUTPUT of the Clock Source, using the accessory cable HP 11500B.

#### Note

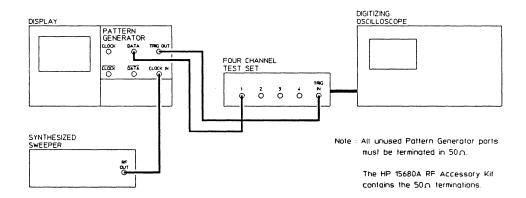

The other front panel ports on the Pattern Generator and Error Detector modules are interconnected according to the application you want to undertake. Accessory Kit HP 15680A contains the necessary cables, adapters and  $50\Omega$  terminations. Unused ports must be terminated in  $50\Omega$ .

8. Connect the power cables to your system then connect the cables to the power outlets.

Three cables for Error Performance Analyzers. Two cables for Pattern Generators.

## Caution

Check the power cables for damage before powering on your system, see the *Power Cables* on page 2-4.

Your system is now ready for System Verification, see page 2-16.

# **System Verification**

This section contains procedures which will enable you to verify that your *Error Performance Analyzer* (see this page) or *Pattern Generator* system (see page 2-18) has been correctly installed.

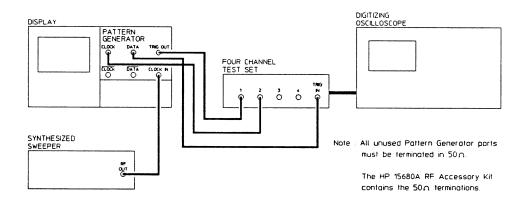

## **Error Performance Analyzer System Verification**

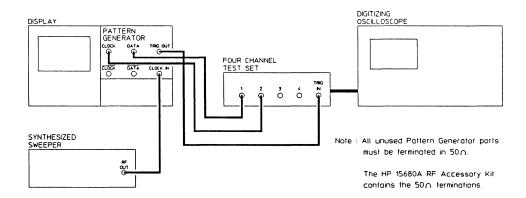

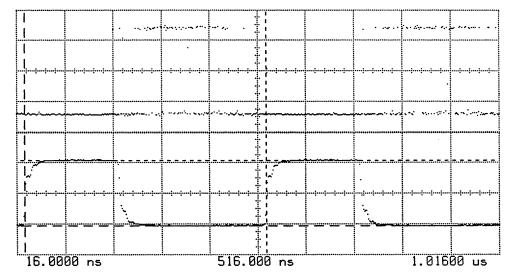

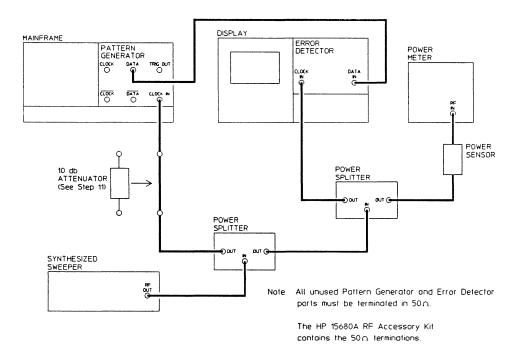

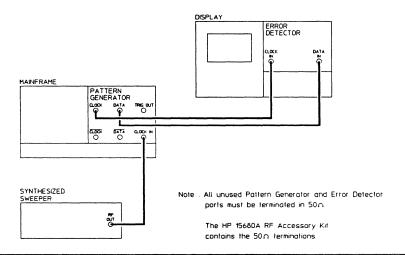

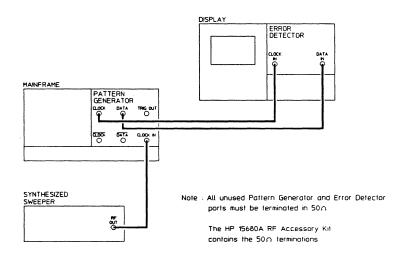

The Error Detector and Pattern Generator modules are connected back-to-back, then the system selftest and instrument preset parameters are used to verify correct installation. A description of what you will see during selftest is given in *System Selftest at Power-on*, see page 2-20 (since selftest takes only 15 seconds approximately to complete, you should read the description before powering on your system).

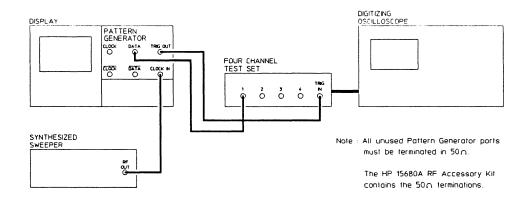

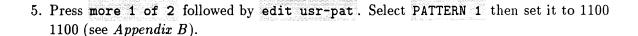

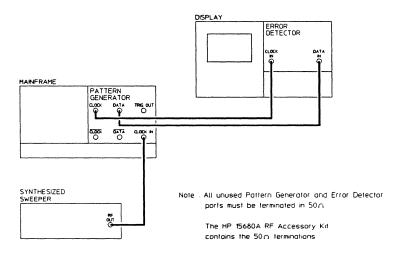

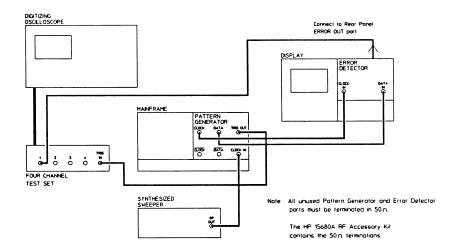

1. Interconnect the front panel ports as shown below, then prior to switching on your system, read Selftest at Power-on on page 2-20.

2. Switch on the three *Line* power switches (in any order) - wait approximately 15 seconds for selftest to end.

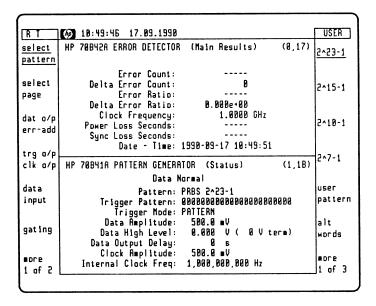

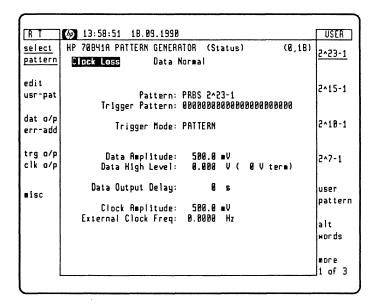

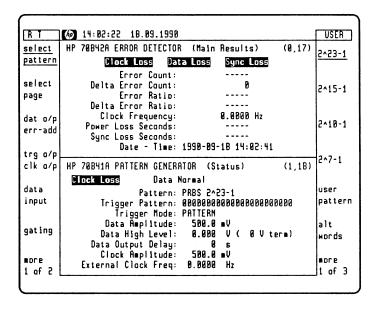

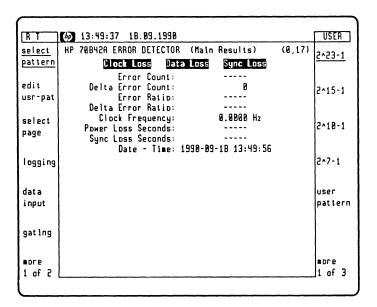

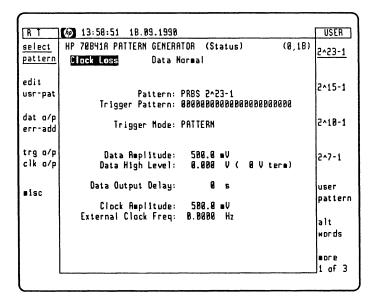

3. Press the Display (INST PRESET) key to set up the instrument preset parameters. The display should be as follows:

- 4. Check that the displayed clock frequency is 1 GHz and that both modules and the Clock Source ACT indicators are lit.

- 5. Press the Display DISPLAY key, the ACT indicators should extinguish and an A should appear at the top left of the display.

- 6. Press the Display MENU key, the A should disappear and the ACT indicators should light.

- 7. Press data input then more 1 of 2 (right menu). Press CLK-DAT ALIGN then wait a few seconds for the clock and data signals to align (see HP 71600 Series System Operating manual).

- 8. Press gating followed by RUN GATING. The GATING indicator on the Error Detector should light.

- 9. Check that the displayed error count is 0.

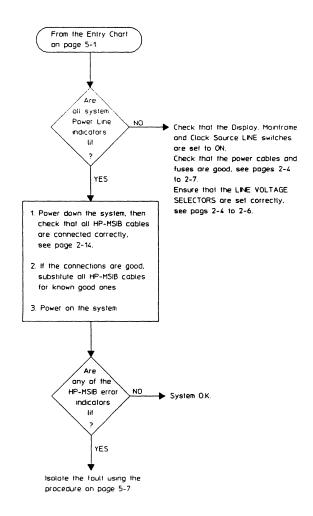

If the system does not operate as described (ie, selftest fails or error indicators are lit after selftest), go to the troubleshooting in chapter 5.

If there are no errors, the system is ready for use.

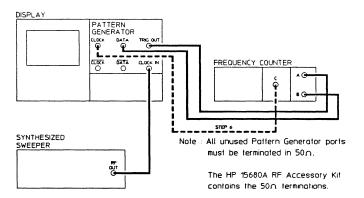

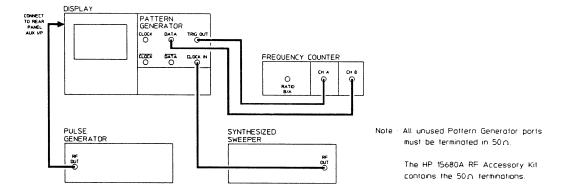

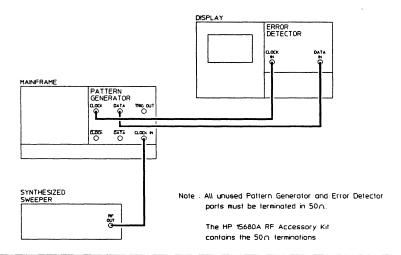

# **Pattern Generator System Verification**

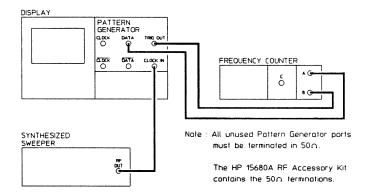

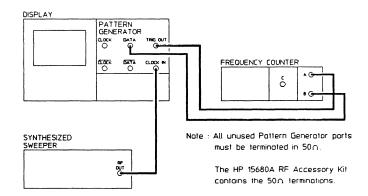

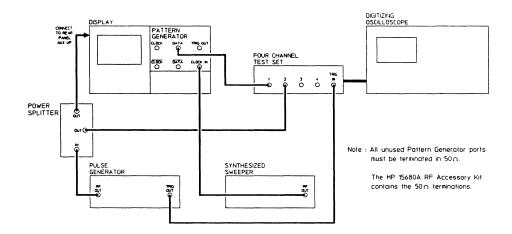

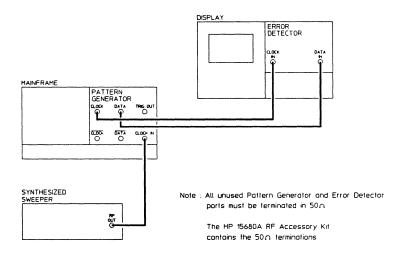

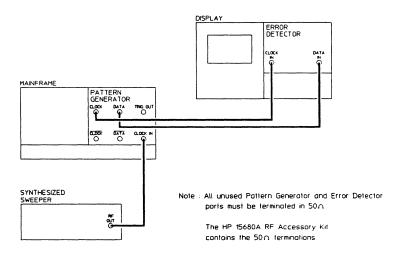

The Pattern Generator is connected to a counter, then the system selftest and instrument preset parameters are used to verify correct installation. A description of what you will see during selftest is given in *System Selftest at Power-on*, see page 2-20 (since selftest takes only 15 seconds approximately to complete, you should read the description before powering on your system).

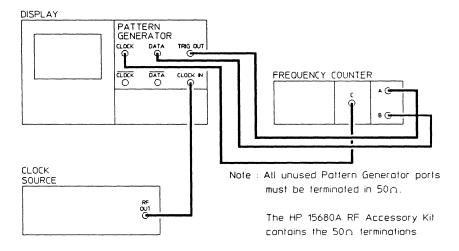

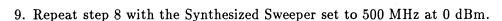

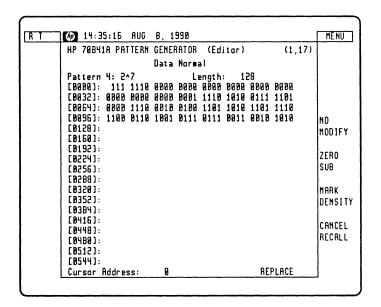

1. Interconnect the front panel ports as shown below, then prior to switching on your system, read Selftest at Power-on on page 2-20.

2. Switch on the two *Line* power switches (in any order) - wait approximately 15 seconds for selftest to end.

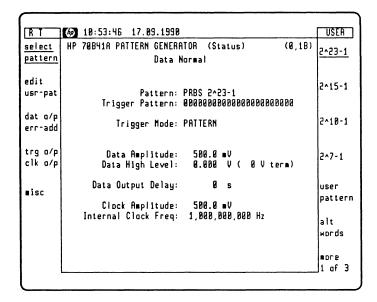

3. Press the Display (INST PRESET) key to set up the instrument preset parameters. The display should be as follows:

- 4. Check that the displayed clock frequency is 1 GHz and that the module ACT indicator is lit.

- 5. Set the clock frequency to 100 MHz (see HP 71600 System Operating Manual).

- 6. Press the Display DISPLAY key, the module ACT indicator should extinguish and an A should appear at the top left of the display.

- 7. Press the Display (MENU) key, the A should disappear and the ACT indicator should light.

- 8. Set the Frequency Counter Scale to Ratio B/A.

- 9. Check that the reading on Frequency Counter is  $33554432 \pm 0.1$ . The Frequency Counter sensitivity may require adjustment to obtain a stable reading.

- 10. Set the Frequency Counter to Ratio C/A.

- 11. Press 2<sup>7</sup>-1.

- 12. Check that the reading on the Frequency Counter is  $4064 \pm 0.1$ . The Frequency Counter sensitivity may require adjustment to obtain a stable reading.

If the system does not operate as described (ie, selftest fails or error indicators are lit after selftest), go to the troubleshooting in chapter 5.

If there are no errors, the system is ready for use.

## Selftest at Power-on

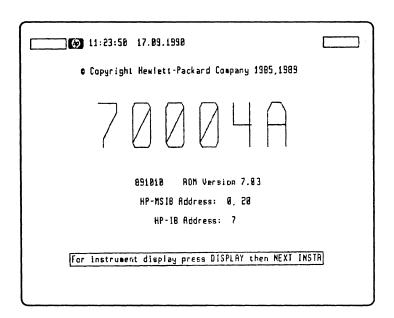

At power on the Error Performance Analyzer system or Pattern Generator system performs a selftest (this takes approximately 15 seconds to complete), during this time the Display, Mainframe, Error Detector and Pattern Generator modules and Clock Source operate as follows:

Display

The display is blank for the first few seconds of the selftest, it then shows a multi-colored raster. The raster sweeps to the right, to show a blue back-ground. For the remainder of the selftest the display is as follows:

After selftest the Display may continue to display the above, or will display the module parameters present prior to the last power down.

Mainframe

All front panel indicators extinguish except for LINE.

Error Detector Module All front panel indicators are lit for approximately eight seconds then

extinguished for the remainder of the selftest.

After selftest the ACT indicator should light.

Pattern Generator Module All front panel indicators are lit for approximately five seconds then

extinguished for the remainder of the selftest.

After selftest the ACT indicator should light.

**Clock Source**

All HP-IB indicators are lit for the duration of the selftest.

# Installing/Removing Modules

Use the following procedures to install your module into the Display or Mainframe. To remove a module, perform the steps in the reverse order.

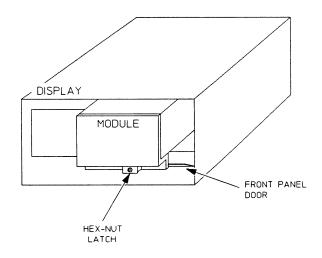

# Installing a Module into a Display

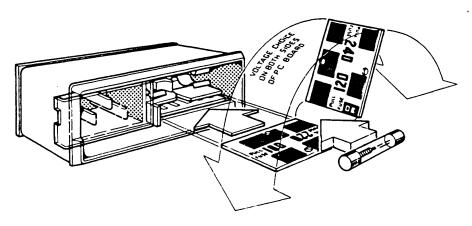

- 1. Open the front panel door then insert the module.

- 2. Secure the module by pressing against its front panel while tightening the hex-nut latch with an 8 mm hex-ball driver.

When removing an Error Detector module, disconnect any cable that may be connected to the rear panel ERROR OUT port.

When removing a Pattern Generator module, disconnect any cable that may be connected to the rear panel AUX IN port.

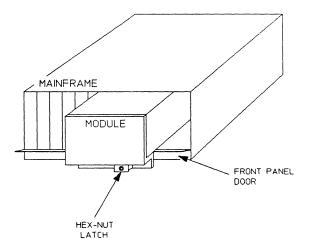

# Installing a Module into a Mainframe

1. Open the front panel door, then insert the module into the mainframe (the module can operate in any location).

# Caution

The Mainframe LINE power switch must be set to off before the front panel door will open.

2. Secure the module by pressing against its front panel while tightening the hex-nut latch with an 8 mm hex-ball driver.

When removing a Pattern Generator module, disconnect any cable that may be connected to the rear panel AUX IN port.

# **Specification**

# Introduction

Except where otherwise stated, the following parameters are the warranted performance specifications. Parameters described as typical or nominal are supplemental characteristics which provide a useful indication of typical, but non-warranted, performance characterstics. All soecifications ar for 0°C to 45°C after 30 minutes.

#### Pattern Generator Modules

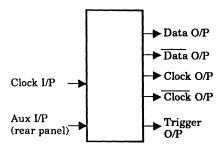

The HP 70841A and 70845A are two pattern generator modules in Hewlett-Packard's Modular Measurement System (MMS). Each occupies 4/8 module slots and has seven I/O ports, six on the front panel and one on the rear:

Operating Frequency Range: HP 70841A: 100 Mbit/s to 3 Gbit/s. HP 70845A: 50 Mbit/s to 1 Gbit/s.

All data refers to 1 and 3 Gbit/s modules, unless otherwise noted.

#### **Patterns**

#### PRBS Test Patterns:

$2^{23}$ -1, polynomial  $D^{23} + D^{18} + 1 = 0$ , inverted (as in CCITT Rec 0.151).  $2^{16}$ -1, polynomial  $D^{16} + D^{14} + 1 = 0$ , inverted (as in CCITT Rec 0.151).  $2^{10}$ -1, polynomial  $D^{10} + D^{7} + 1 = 0$ , inverted.

$2^{7}$ -1, polynomial  $D^{7} + D^{6} + 1 = 0$ , inverted. Zero Substitution/Variable Mark Density Test Patterns:

Density Test Patterns:

8192 bits, based on 2<sup>13</sup>-1 PRBS;

2048 bits, based on 2<sup>14</sup>-1 PRBS;

1024 bits, based on 2<sup>16</sup>-1 PRBS;

128 bits, based on 2<sup>7</sup>-1 PRBS.

Zero Substitution: Zeros can be substituted for data to extend the longest run of zeros in the above patterns. The longest run can be extended to the pattern length, minus one. The bit after

the substituted zeros is set to 1. Variable Mark Density: The ratio of 1s to total bits in the above patterns can be set to 1/8, 1/4, 1/2, 3/4 and 7/8.

Word Test Patterns: Variable length user patterns from 1 to 8192 bits.

Resolution: From 1 to 255 bits in 1-bit steps; 256 to 8192 bits in 32-bit steps.

Four stores are provided for user patterns. Each store can hold one pattern up to 8192 bits long.

Alternating Word Test Patterns: Alternate between two userprogrammable 16-bit words under the control of the auxiliary input; changeover is synchronous with the end of a word.

| A word 16 bits  |     | B word 16 bits |   |   |   |

|-----------------|-----|----------------|---|---|---|

| A               | Α   | A              | В | В | A |

| Auxili<br>Input | ary | ٦              |   |   |   |

Data Output Inhibit: The data output can be inhibited under the control of the auxiliary input. The output is forced to zero for a multiple of 16 bits from the start of a 16-bit block in the pattern. Error Add: There are two modes of operation:

Single errors on demand;

Single errors on demand; Fixed error ratio of 1 error in 10<sup>6</sup> bits. **Data Polarity:** Selectable normal or inverted data.

#### **Clock Input**

Waveform: Sinewave from the HP 70322A or 70320A signal generator modules.

Amplitude Range: ± 4 dBm.

Return Loss: Over operating frequency range: > 10 dB typical.

Impedance: 50Ω nominal.

Interface: ac coupled.

Connector: N-type female.

Alternative Clock Sources: The

HP 8665A and 8644A synthesized signal

generators are compatible. Other clock

sources can be used provided they meet

the following criteria:

Noise: SSB broadband noise floor, offsets >10 MHz from the carrier in the range 10 MHz to 4 GHz:

|                                                                    | Noise Floor<br>in dBc/Hz         |                  |  |

|--------------------------------------------------------------------|----------------------------------|------------------|--|

| Carrier<br>Frequency                                               | HP<br>70841A                     | HP<br>70845A     |  |

| < 300 MHz<br>300 MHz to 1.0 GHz<br>1.0 GHz to 2.0 GHz<br>> 2.0 GHz | <-140<br><-130<br><-130<br><-140 | < -140<br>< -130 |  |

#### **Data and Data Outputs**

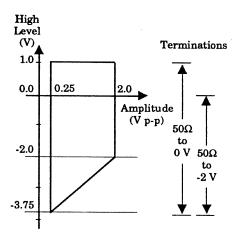

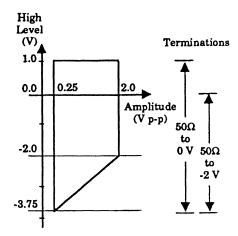

Except where stated, all specifications are with the outputs terminated  $50\Omega$  to 0 V.

Format: NRZ.

Levels: Selectable amplitude and offset or nominal ECL, into  $50\Omega$  to 0 V or  $50\Omega$  to -2 V.

Amplitude:

Range: 0.25 to 2 V p-p nominal. Resolution: 10 mV nominal.

Offset: The output amplitude and offset (high level) can be set as shown below:

High Level Resolution: 10 mV nominal.

High Level: -0.90 V nominal. Low Level: -1.75 V nominal.

Delay: Data delay variation vs clock

output transitions: Range: ± 1 ns nominal. Resolution: 5 ps nominal.

Jitter: Specified for 223-1 PRBS, 2 V p-p output amplitude, 0 V high level and measured relative to clock/32 trigger pulse.

| HP 70841A   | HP 70845A   |

|-------------|-------------|

| at 3 GHz    | at 1 GHz    |

| < 15 ps rms | < 30 ps rms |

Transition Times and Overshoot: Specified for 0101 pattern, 1 V p-p output amplitude and 0 V high level at

Transition Times:

|            | HP 70841A<br>at 3 GHz | HP 70845A<br>at 1 GHz |

|------------|-----------------------|-----------------------|

| 20% to 80% | < 90 ps               | < 180 ps              |

| 10% to 90% | < 120 ps              | < 250 ps              |

Specified over full operating frequency range for 0101 pattern, 0.5 to 2 V p-p output amplitude and 0 V high level. Transition Times (typical):

|            | HP 70841A | HP 70845A |

|------------|-----------|-----------|

| 10% to 90% | < 150 ps  | < 300 ps  |

Preshoot/Overshoot: < 15% typical. Impedance:  $50\Omega$  nominal.

Interface: dc coupled. Connectors: N-type female.

# **Clock and Clock Outputs**

All specifications are for the output terminated  $50\Omega$  to 0 V.

Amplitude:

Range: 0.5 to 2 V p-p nominal. Resolution: 10 mV nominal. Transition Times and Overshoot: Transition Times: 10% to 90% at 25°C (typical).

|         | HP 70841A | HP 70845A |

|---------|-----------|-----------|

| 3 GHz   | < 120 ps  | -         |

| 1 GHz   | < 130 ps  | < 300 ps  |

| 100 MHz | < 1.3 ns  | < 2 ns    |

Preshoot/Overshoot: < 15% typical at

25°C.

Impedance:  $50\Omega$  nominal. Interface: ac coupled. Connectors: N-type female.

#### **Trigger Output**

Provides a trigger pulse synchronous with the pattern or clock. There are two modes of operation: pattern mode and clock/32 mode.

Pattern Mode: For all patterns except alternate word, the output is a 16-clockperiod trigger pulse synchronized to repetitions of the pattern. The pulse repetition rate depends on the pattern length (with the exception of alternate word patterns) and occurs at least every 32 repetitions of the pattern. The rising edge of the trigger pulse is active. PRBS Test Patterns (2n-1): Pulse synchronized to a selectable trigger pattern n-bits long in the PRBS. Word Test Patterns: The trigger pulse can be synchronized to any bit in the pattern.

Alternate Word Test Patterns: Trigger output changes as the word alternates under control of the auxiliary input.

Clock/32 Mode: The trigger pulse output is the input clock divided by 32.

Pulse Amplitude: Output terminated 50Ω to 0 V. High: 0 V nominal. Low: -0.75 V nominal. Impedance:  $50\Omega$  nominal. Interface: dc coupled. Connector: N-type female.

#### **Auxiliary Input**

Provides a means of controlling the alternate word changeover or forcing the data output to zero.

Alternate Word Selected: The input signal forces a change between the two 16-bit patterns at the end of either pattern.

Alternate Word Not Selected: The input signal forces the data output to zero.

Levels: TTL compatible, active low. Pulse Width:

| Clock     | Minimum<br>Pulse Width |  |  |

|-----------|------------------------|--|--|

| ≥ 500 MHz | 100 ns                 |  |  |

| < 500 MHz | 250 ns                 |  |  |

Interface: dc coupled. Connector: BNC female.

## **Frequency Measurement**

Measures the incoming clock frequency to five significant digits.

#### **Status Indicators**

#### Front Panel LEDs:

Clock Loss: Indicates nominal low clock power or overload at Clock Input. HP-IB and HP-MSIB: Six LEDs indicate status.

## **Error Detector Modules**

The HP 70842A and the HP 70846A error detector modules complement the pattern generator modules.

Each occupies 4/8 MMS module slots and has three I/O ports, two on the front panel and one on the rear.

Operating Frequency Range: HP 70842A: 100 Mbit/s to 3 Gbit/s. HP 70846A: 50 Mbit/s to 1 Gbit/s.

To avoid duplication, reference will be made to the pattern generator section where appropriate.

All data refers to 1 and 3 Gbit/s error detector modules unless otherwise stated.

#### **Patterns**

PRBS, with or without zero substitution/ variable mark density, and word test patterns are as specified for pattern generator modules.

Data Polarity: Selectable normal or inverted data.

#### **Clock Input**

Waveform: Compatible with the output of the following: Signal Generator Modules: HP 70322A,

70320A.

Signal Generators: HP 8665A, 8644A. Pattern Generator Modules: HP 70841A, 70845A.

Amplitude Range: ±4 dBm.

Return Loss: Over operating frequency

range: > 10 dB typical. Impedance:  $50\Omega$  nominal. Interface: ac coupled. Connector: N-type female. Alternative Clock Sources: Other clock sources offering a similar performance to those listed under Waveform above can be used provided they meet the following criteria: Noise: SSB broadband noise floor, offsets > 10 MHz from the carrier in the range 10 MHz to 4 GHz:

| Carrier<br>Frequency | Noise Floor   |  |  |

|----------------------|---------------|--|--|

| < 300 MHz            | < -140 dBc/Hz |  |  |

| > 300 MHz            | < -130 dBc/Hz |  |  |

#### **Data Input**

Data Sampling Clock Edge: Selectable rising or falling edge. Termination Voltage: Selectable 0 V or -2 V nominal. Levels: Amplitude: Min, 0.5 V p-p; Max, 2.0 V p-p nominal. Offset (nominal):

|                          | Terminations  |                |

|--------------------------|---------------|----------------|

|                          | 50Ω to<br>0 V | 50Ω to<br>-2 V |

| Maximum Input<br>Voltage | +1 V          | 0 V            |

| Minimum Input<br>Voltage | -4 V          | -4 V           |

0/1 Threshold: The electrical interface allows for a range of input amplitudes and dc offsets. The 0/1 threshold is set using one of three modes:

Automatic Track: Tracks the mean dc level of the input signal. The measured threshold is displayed.

Automatic Center: The error detector sets the 0/1 threshold midway between two points, top and bottom of the "eye", where the bit error ratio is equal to a selectable threshold. The "eye" height is calculated and displayed.

Manual: Sets the 0/1 threshold manually.

Range: +1 to -4 V nominal. Resolution: 10 mV nominal.

#### Delay:

The data sampling point can be set automatically to the center of the "eye". The error detector sets the data/clock delay midway between two points either side of the "eye" where the bit error ratio is equal to a selectable threshold. The "eye" width is calculated and displayed. The sampling point can also be set manually by altering the data/clock

Data delay variation vs selected clock

Range: ± 1 ns nominal. Resolution: 5 ps nominal. Automatic Data/Clock Alignment and 0/1 Threshold Center: Selectable error-ratio thresholds from 0 to 1 x 10-1. Return Loss: 300 kHz to 3 GHz: > 10 dB typical. Impedance:  $50\Omega$  nominal. Interface: dc coupled.

Connector: N-type female.

#### **Error Output**

Provides an electrical signal to indicate received errors. The error output pulse is the logical "OR" of all errors in a 16-bit period.

All specifications are for the output terminated  $50\Omega$  to 0 V.

Format: NRZ, active high. Amplitude: High: 0 V nominal. Low: -800 mV nominal. Pulse Width:

For 1-bit error: 16 clock periods nominal.

Impedance:  $50\Omega$ . Interface: dc coupled. Connector: BNC female.

#### **Audible Error Indicator**

There is a selectable, audible beep on error. Single errors produce a beep. For error ratios above 1 x 10°, beep repetition rate increases with error ratio in five steps:  $1 \times 10^{-6}$ ,  $10^{-7}$ ,  $10^{-5}$ ,  $10^{-3}$ ,  $10^{-1}$ . Requires an MMS display.

#### **Measurement Period**

Real-time Clock: Provides time and date information for event logging. Battery back-up allows clock to continue running when the instrument is switched off or power fails. Elapsed Time Indication: Shows

elapsed time from the start of a gating period; resets to zero at the start of each gating period; holds value when measurement stopped.

Gating Periods: There are three gating (measurement timing) modes: Manual, Timed Single and Timed Repeat. Manual: Gating period is controlled by the Run/Stop Gating keys. Accumulating results are displayed throughout the measurement and the end of measurement results are held until a new gating period is started. Timed Single: Gating period is started

by pressing the Run Gating key and terminates at the end of the gating period set by the user. Accumulating results are displayed throughout the gating period and the end of gating results are held until a new gating period

Timed Repeat: Similar to Timed Single but when one timed gating period ends, a new identical period starts. This continues until the measurement is terminated by pressing the Stop Gating key. The measurement results displayed during any period can be the final results of the previous period or the accumulating results for the current period. There is no "deadtime" between consecutive periods.

Minimum Gating Period: 1 second. Maximum Gating Period: 99 days, 23 hours, 59 minutes, 59 seconds. Resolution: 1 second.

The gating period excludes any periods when the instrument is not powered.

#### **Error Measurements**

The error detector counts bit errors by comparing the incoming data bit-by-bit with the internally-generated reference pattern. All measurements run during the gating periods as described with the exception of Delta Error Count and Delta Error Ratio. These measurements run continuously to facilitate user adjustments for minimizing errors. Error Count: The total number of errors during the gating period. Delta Error Count: The number of errors in successive decisecond intervals. Error Ratio: The ratio of counted errors to the number of bits in the selected gating period. Delta Error Ratio: The ratio of counted errors to the number of bits in successive decisecond intervals. Errored Intervals: Time intervals during which one or more errors occurred. These intervals are errored seconds, deciseconds, centiseconds or milliseconds.

#### **Error Analysis**

occurred

The error analysis is based on CCITT Rec G.821 and is derived from the bit error results.

Error Free Intervals: Time intervals of seconds, deciseconds, centiseconds or

milliseconds, during which no errors

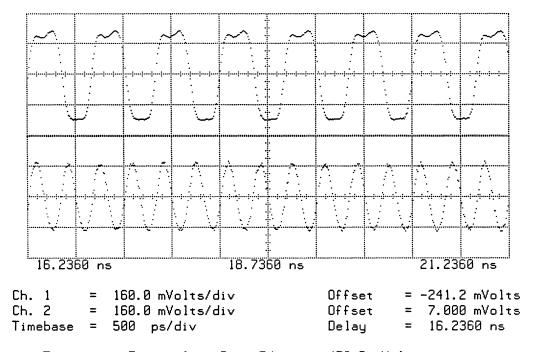

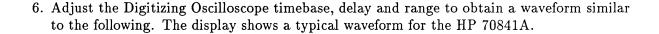

% Unavailability: The error ratio is calculated over 1 second timed intervals during the gating period. An unavailable period begins when the error ratio is worse than 1 x 10<sup>3</sup> for 10 consecutive seconds. These 10 seconds are considered part of the unavailable time. The unavailable period ends when the error ratio is better than 1 x 10-3 for 10 consecutive seconds. These 10 seconds are considered part of the available time. % Unavailability is the ratio of the unavailable seconds to the total gating period expressed as a percentage. % Availability: The ratio of the available seconds to the total gating period expressed as a percentage.