# **VOLUME 2 TABLE OF CONTENTS**

| Service Sheet | 1—A53 RF Power Assembly (Sensor Input Circuits)                 | . 8F-1 |

|---------------|-----------------------------------------------------------------|--------|

|               | 2—A53 RF Power Assembly (Control Circuits)                      |        |

| Service Sheet | 3—A32 Power Reference Oscillator Assembly                       | 8F-15  |

| Service Sheet | 4-A15 RF Input Control, A16 RF Detector, A70 Amplifier/Switch   | 8F-17  |

|               | 5—A17 Input Mixer and A18 IF Amplifier Assemblies               |        |

| Service Sheet | 6—A55 IF Amplifier/Filter Assembly                              | 8F-37  |

| Service Sheet | 7—A54 IF Synchronous Detector Assembly                          | 8F-43  |

| Service Sheet | 8—A6 AM Demodulator Assembly (ALC Loop)                         | 8F-53  |

| Service Sheet | 9—A6 AM Demodulator Assembly (Control Circuits)                 | 8F-63  |

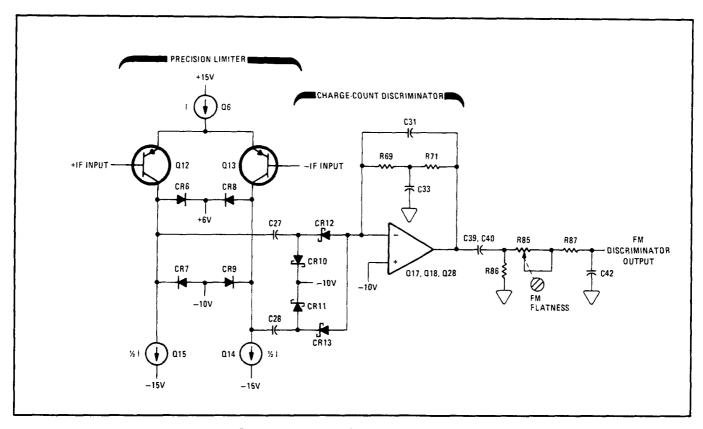

| Service Sheet | 10—A4 FM Demodulator Assembly (Limiters)                        | 8F-67  |

| Service Sheet | 11—A4 FM Demodulator Assembly (Discriminator)                   | 8F-69  |

| Service Sheet | 12—A2 Audio Filters Assembly                                    | 8F-75  |

| Service Sheet | 13-A3 Audio De-emphasis and Output Assembly                     | 8F-81  |

| Service Sheet | 14—A5 Voltmeter Assembly (Audio Detectors)                      | 8F-89  |

| Service Sheet | 15—A5 Voltmeter Assembly (Voltmeter)                            | 8F-97  |

| Service Sheet | 16—A52 Audio Counter and Distortion Analyzer Assembly           | 8F-103 |

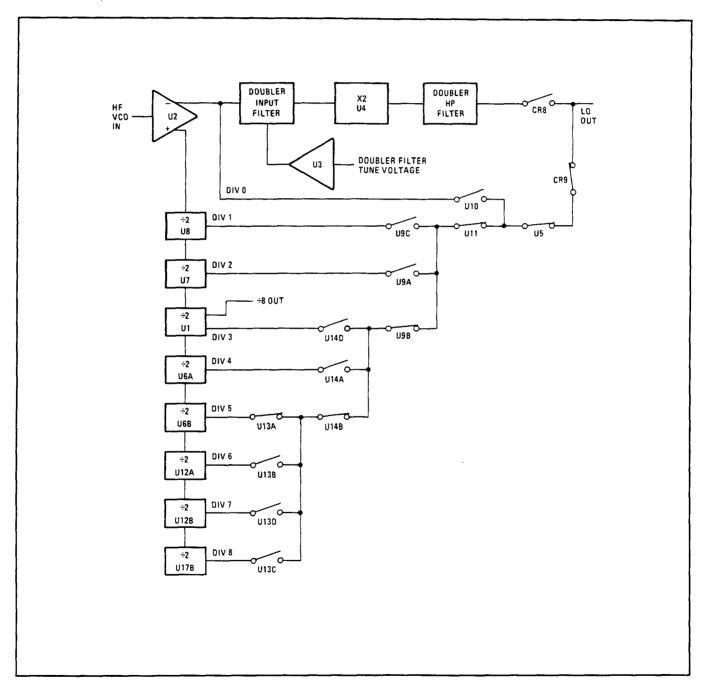

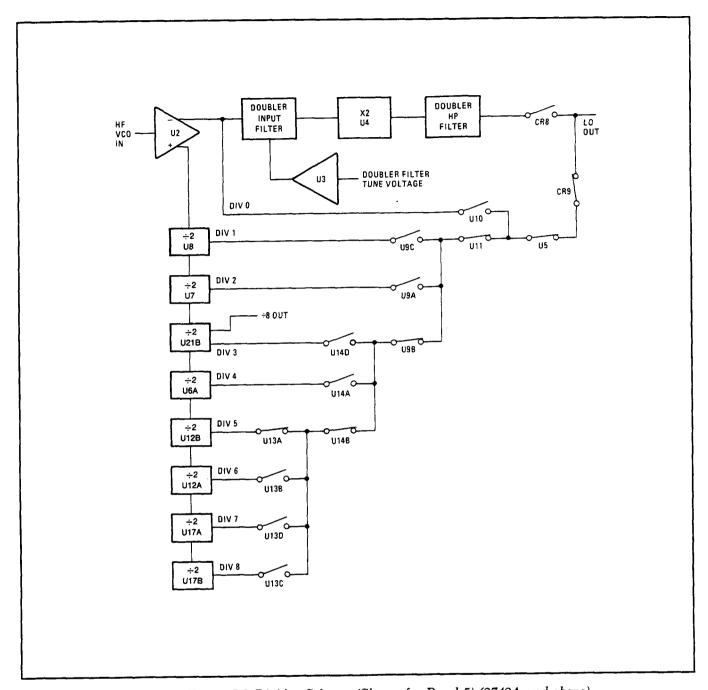

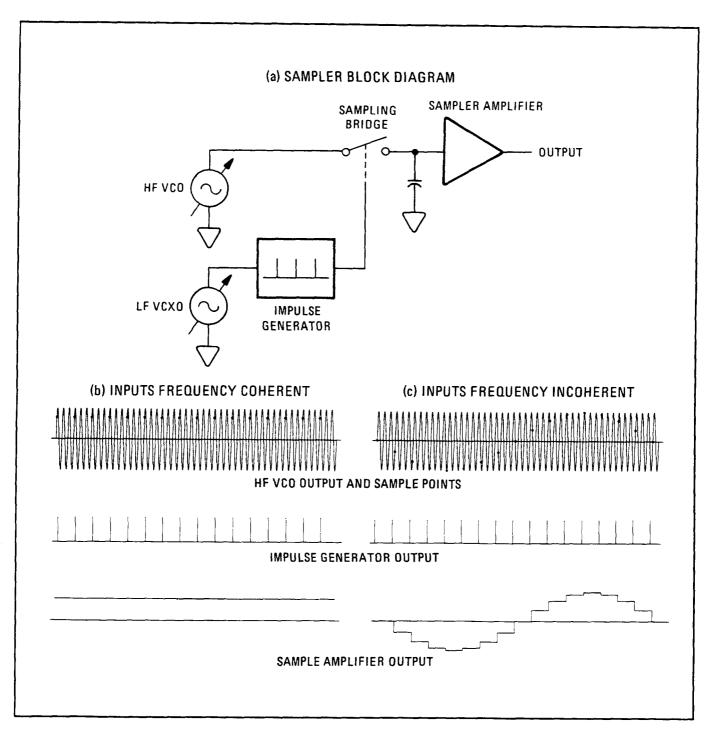

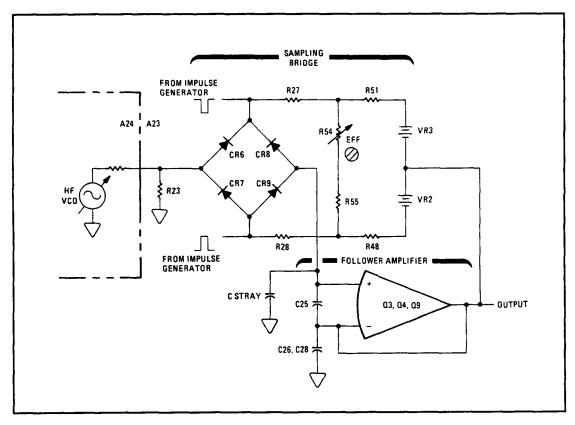

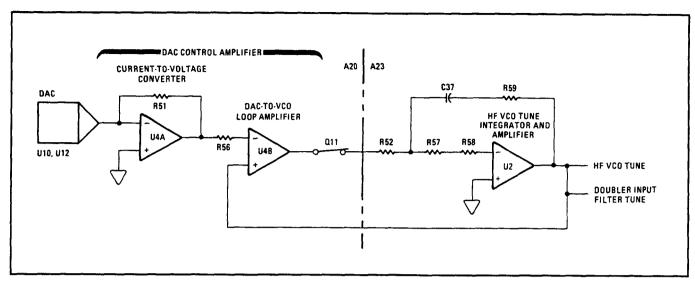

| Service Sheet | 17—A19 LO Divider Assembly                                      | 8F-111 |

| Service Sheet | 18—A23 Sampler and A24 High Frequency VCO Assemblies            | 8F-117 |

|               |                                                                 | 8F-129 |

| Filter As     | semblies                                                        |        |

| Service Sheet | 20—A20 LO Control Assembly (Analog Circuits) (2305A to 2530A)   | 8F-133 |

|               |                                                                 | 8F-139 |

| Service Sheet | 21—A20 LO Control Assembly (Digital Circuits) (2305A to 2530A)  | 8F-145 |

| Service Sheet | 21—A20 LO Control Assembly (Digital Circuits) (2535A and Above) | 8F-149 |

| Service Sheet | 22—A11 Counter Assembly (Time Base)                             | 8F-153 |

| Service Sheet | 23—A11 Counter Assembly (Counter)                               | 8F-157 |

| Service Sheet | 24—A13 Controller Assembly                                      | 8F-167 |

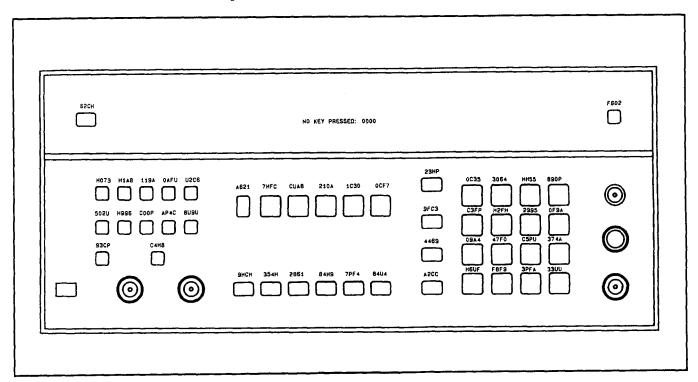

| Service Sheet | 25—A1 Keyboard Assembly (Keyboard)                              | 8F-177 |

| Service Sheet | 26—A1 Keyboard Assembly (Displays)                              | 8F-183 |

| Service Sheet | 27—A1 Keyboard and Display Assembly (Annunciators)              | 8F-187 |

|               | 28—A14 Remote Interface Assembly                                | 8F-191 |

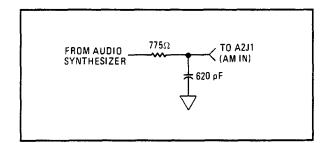

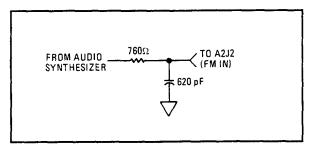

| Service Sheet | 29—A51 FM Calibrator Assembly                                   | 8F-207 |

| Service Sheet | 30—A50 AM Calibrator Assembly                                   | 8F-215 |

| Service Sheet | 31—A10 Power Supply Regulators, A26 Power Supply Motherboard,   | 8F-223 |

| and A29       | Series Regulator Heat Sink Assemblies                           |        |

| Service Sheet | 32—A10 Power Supply Regulators, A26 Power Supply,               | 8F-227 |

|               | Series Regulator Heat Sink Assemblies                           |        |

|               | 33—A72 IF Channel Filter Assembly (Option Series 030)           | 8F-231 |

|               | 34—A71 IF Amplifier Detector Assembly (Option Series 030)       |        |

## **SERVICE SHEET 1**

### **Assembly**

• A53 RF Power (Sensor Input Circuits)

#### **Principles of Operation**

#### General

The load impedance of the power-sensing element dissipates the RF input power applied to the external power sensor (in the Sensor Module). A sampling gate (chopper) in the power sensor converts the dc output of the power-sensing element to a 220 Hz ac signal. The RF Power circuits amplify the ac signal and convert the signal back to dc for measurement by the Voltmeter.

### **Amplifier 1**

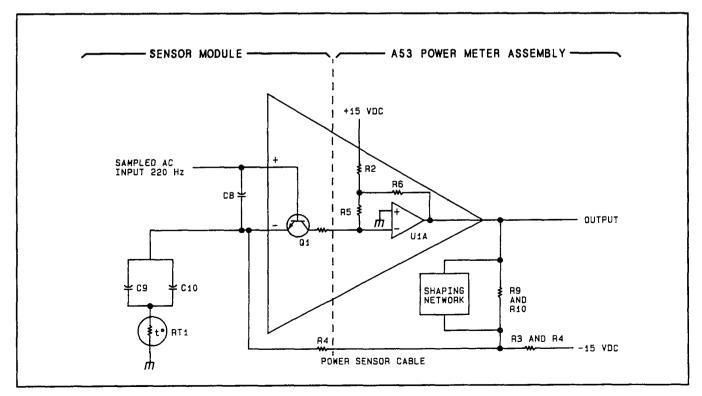

The ac signal, which is proportional to the RF input power, is amplified by tuned ac amplifier stages in the external power sensor and the RF Power circuits. Amplifier 1 and the output amplifier of the external power sensor form a low-noise, high-gain operational amplifier. See Figure 8F-1. The ac gain of the amplifier is approximately 700. DC bias is set by R2, R3, R4, R5, and R6. Diodes CR1, CR2, VR1, and VR2 and associated components are part of a shaping network which compensates for the non-linear output of the power sensor's power sensing element. (The efficiency of the power-sensing element is slightly impaired when the RF input to the power sensor is near maximum power.) The shaping network reduces the gain of Amplifier 1 to give a linear overall response. R13 (RNG 4) and R16 (RNG 5) permit fine adjustment of the gain of the shaping circuit for high levels.

Figure 8F-1. First Amplifier Stage of the RF Power Meter

The combination of C10, R9, and R10 determines, in part, the upper cutoff frequency (240 Hz) of the bandpass response of the ac amplifiers; C14, R19, and R20 determine, in part, the lower cutoff frequency (200 Hz). C1, C5, and C13 filter line noise.

### **Ground Regulator**

U17 and U1B are connected as a voltage follower between the GND REGULATOR line from the Sensor Module and ANALOG GND 1 of the RF Power circuits. This circuit ensures that a minimum voltage difference exists between the grounds to eliminate error-creating voltage difference between measurement ground and instrument ground.

### Attenuators 1 and 2 and Amplifiers 2 and 3

Attenuators 1 and 2 operate as shown in Table 8F-1. (The attenuation indicated is voltage attenuation.)

| <b>D</b> | Attenuation (dB)          |    |       |  |  |  |  |  |  |

|----------|---------------------------|----|-------|--|--|--|--|--|--|

| Range    | Attenuator 1 Attenuator 2 |    | Total |  |  |  |  |  |  |

| 1        | 0                         | 0  | 0     |  |  |  |  |  |  |

| 2        | ] o                       | 20 | 20    |  |  |  |  |  |  |

| 3        | 0                         | 40 | 40    |  |  |  |  |  |  |

| 4        | 40                        | 20 | 60    |  |  |  |  |  |  |

| 5        | 40                        | 40 | 80    |  |  |  |  |  |  |

Table 8F-1. Attenuation vs. Range of Attenuators 1 and 2

Amplifier 2 has a gain of 21. Amplifier 3 has a gain of 19. The two combinations of C18 and R21 and of C27 and R31 determine, in part, the upper cutoff frequency (240 Hz) of the bandpass response of the ac amplifiers; C19, R24, R25, and R26 and C22 and R27 determine, in part, the lower cutoff frequency (200 Hz).

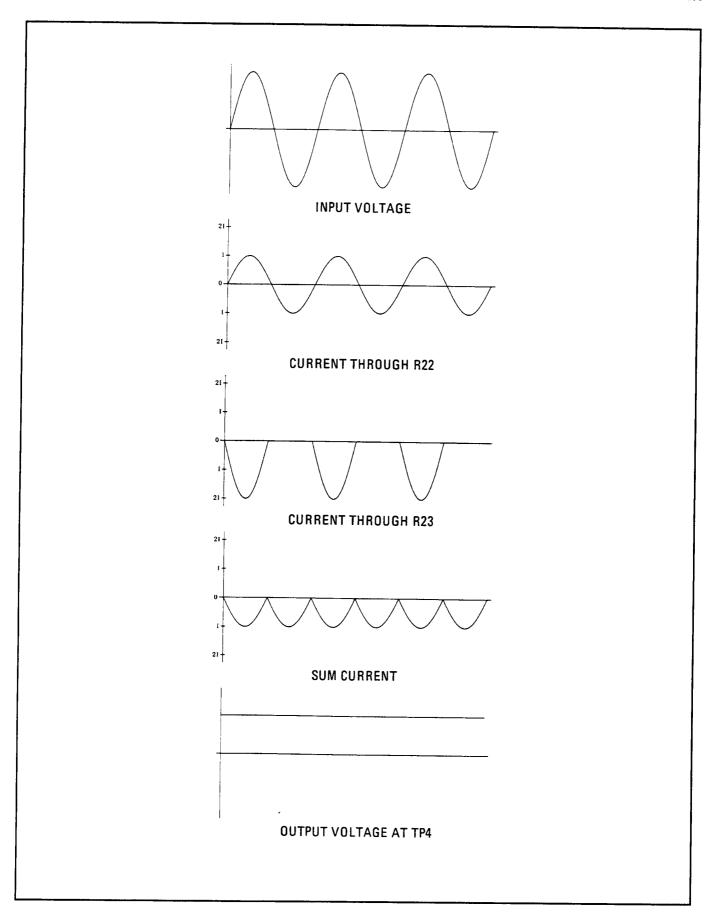

#### **Synchronous Detector**

The 220 Hz Multivibrator drives the Synchronous Detector in the same way it drives the sampling gate (chopper) in the external power sensor. The 220 Hz switching signal is applied through Q5 and Q6 to the gate of FET Q4 which causes Q4 to turn on and off. When Q4 is on, the gain of amplifier U3 is -1. When Q4 is off, the gain of U3 is +1. Since the 220 Hz drive signal is in synchronism with the ac signal originating in the power sensor's chopper, the output of U3 is full-wave rectified. The average dc level of the signal from U3 is proportional to the power dissipated in the power-sensing element of the external power sensor.

#### 220 Hz Multivibrator

The 220 Hz Multivibrator drives both the chopper in the external power sensor and the gain switch (Q4) of the Synchronous Detector. Q8, Q9, and associated components form an astable multivibrator. Q11 and Q12 are drivers. R40 (FREQ) allows fine adjustment of the multivibrator's frequency. R40 is adjusted for minimum phase shift through the bandpass filter response of the ac amplifiers. The point of minimum phase shift gives the maximum and most drift-immune power indication.

### **Troubleshooting**

#### General

Procedures for checking the RF Power Assembly are given below. The circuits to check are marked on the schematic diagram by a hexagon with a check mark and a number inside, for example,  $\sqrt{3}$ . In addition, any points outside the labeled circuit area that must be checked are also identified. Fixed signals are also shown on the schematic inside a hexagon, for example,  $\langle +1.9 \text{ TO} +2.1 \text{ VDC} \rangle$ .

Extend the board assembly where necessary to make measurements. Extending the assembly will require freeing the two multi-conductor cables atop the assembly so that they may be reconnected. Freeing the cables will require disconnecting several RF cables. The RF cables need not be reconnected while troubleshooting the assembly.

CAUTION

Tighten SMC connectors to 0.6 N·m (5 in·lb). Hand tightening of connectors is insufficient. Hand-tightened connectors can work loose and cause reduced performance or malfunctions.

### Equipment

| Oscilloscope     | HP 1740A  |

|------------------|-----------|

| Range Calibrator | HP 11683A |

### Amplifier 1 and Ground Regulator Check

#### NOTE

Failure of the Ground Regulator may make Amplifier 1 appear to fail.

- 1. Remove any connection to the SENSOR connector.

- 2. Connect one channel of a high-impedance, dc coupled oscilloscope to pin 6 of U17. Connect the other channel to pin 7 of U1B. Connect pin 3 of U17 through a 100 kΩ resistor to the supply indicated in the table below. After connecting the resistor to the supply, briefly short pin 2 of U17 to chassis ground and observe the oscilloscope display. The voltages should be as indicated in Table 8F-2.

#### NOTE

U17 and U1B will be operating with nearly short-circuited outputs, which they should be able to withstand indefinitely. It is a good practice, however, to be as brief as possible. The +15V Supply is easily accessed at the + end of C2, the -15V Supply at the - end of C4.

**Table 8F-2.** Voltage Limits for  $\langle \sqrt{1} \rangle$  Step 2

| Supply<br>Connection | Limits (Vdc)<br>on U17 Pin 6 | Limits (Vdc)<br>on U1B Pin 7 |

|----------------------|------------------------------|------------------------------|

| +15V                 | +0.2 to +1.0                 | +0.1 to +0.3                 |

| -15V                 | −1.0 to −0.2                 | -0.3 to -0.1                 |

Hint: If the short on pin 2 of U17 is removed, the outputs of U17 and U1B will normally drift towards the corresponding supply and, for the +15V Supply, will begin pulsing. If this change

does not occur, the Ground Regulator is working properly but its load (the devices connected to Analog Ground 1) requires more current than the regulator is able to supply.

- 3. Remove the short from pin 2 of U17. Connect the oscilloscope to A53TP6 (A GND). Connect the 100 k $\Omega$  resistor to chassis ground. The level at A53TP6 should slowly drift to between -50 and +50 mVdc.

- 4. Ground pin 3 of U1A. (Shorting R1 with a cliplead may be the simplest way to do this.)

- 5. Connect the oscilloscope to pin 1 of U1A. The voltage should be between −15 and −12 Vdc.

Hint: U1A, R2, and R6 form an inverting amplifier with the +15V Supply as the input. The gain is high enough to drive U1A into limiting by the −15V Supply.

- 6. Connect a 42.2 k $\Omega$  resistor between the + end of C5 and the -15V Supply. The voltage should be between -0.5 and +0.5 Vdc. (Ignore any ac ripple.)

- 7. Remove all jumpers. Leave the oscilloscope connected to pin 1 of U1A.

- 8. Connect the range calibrator to the SENSOR input. Set the calibrator's range to 1 mW, function to calibrate, and polarity to normal.

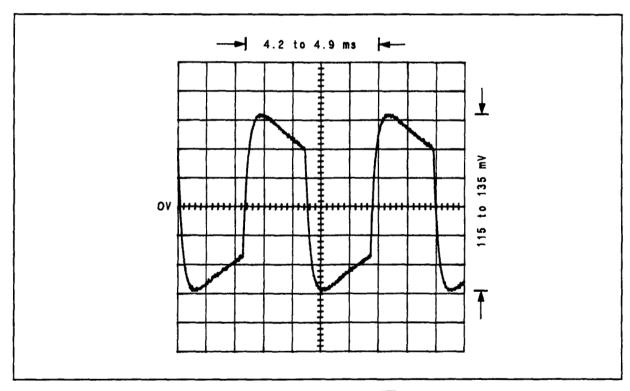

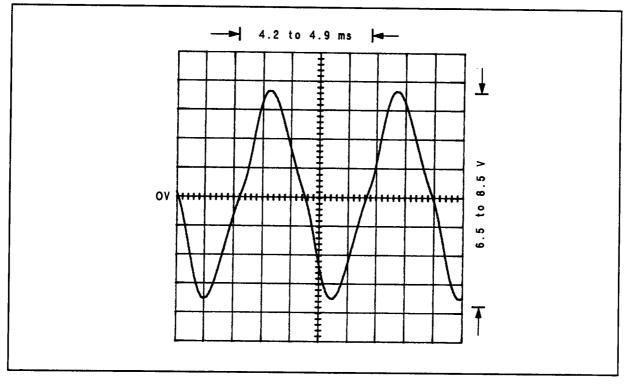

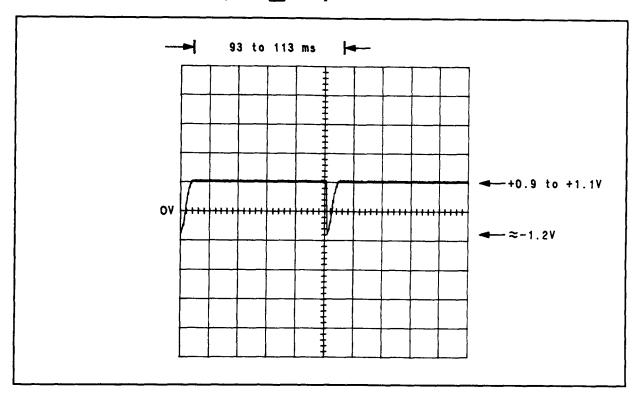

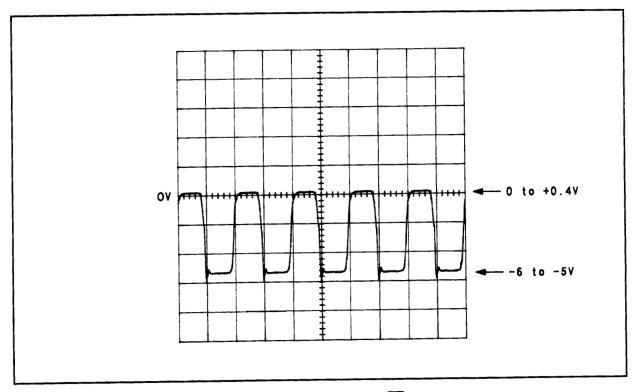

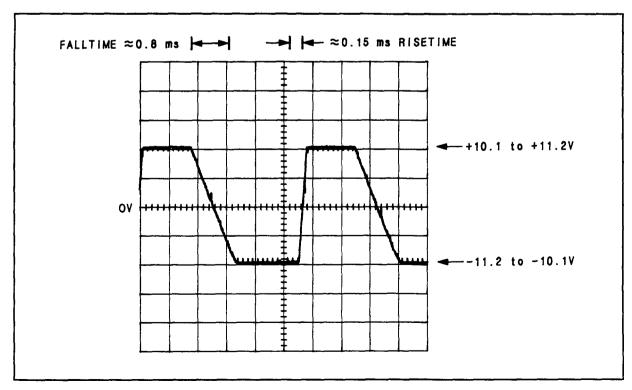

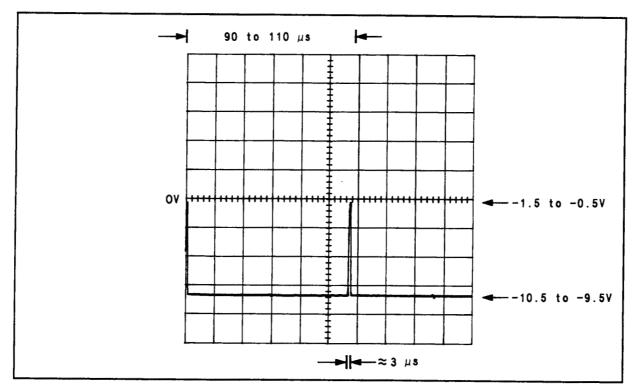

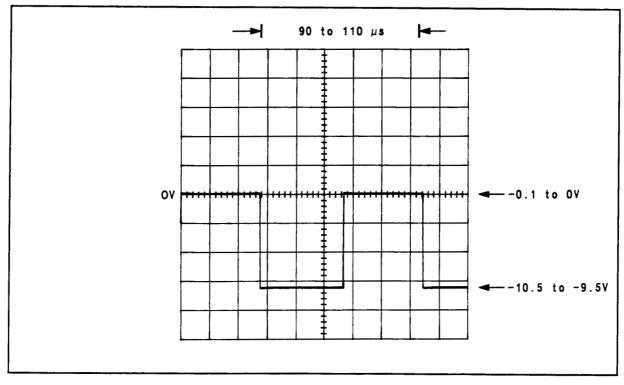

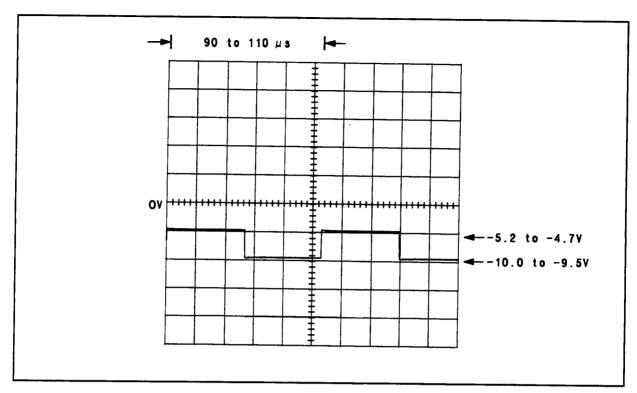

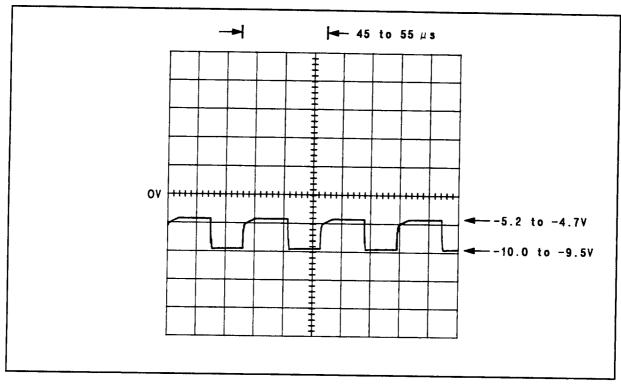

- 9. Press RF POWER. The waveform on the oscilloscope display should appear as shown in Figure 8F-2.

**Figure 8F-2.** Waveform for  $\langle \sqrt{1} \rangle$  Step 9

Hint: If the period is out of limits, see  $\sqrt{4}$  220 Hz Multivibrator Check. Improper operation of the Zeroing Control circuit can alter the input to Amplifier 1 and cause an erroneous output. If this is suspected, short R65 (see Service Sheet 2) and recheck the waveform.

10. Set the calibrator's range to 10 mW. Reduce the oscilloscope's vertical gain by a factor of 10. The waveform should appear as in the figure for step 9 with the voltage limits multiplied by 10.

Hint: If faulty, check the components associated with the Range 4 shaping circuit (R13, CR1, CR2, etc.).

11. Set the calibrator's range to 100 mW. Reduce the oscilloscope's vertical gain by a factor of 10. The waveform should appear as in the figure for step 9 with the voltage limits multiplied by 100. Hint: If faulty, check the components associated with the Range 5 shaping circuit (R16, VR1, VR2, etc.).

## √2 Attenuator 1, Amplifier 2, Attenuator 2, and Amplifier 3 Check

- 1. Connect the range calibrator to the SENSOR input. Set the calibrator's range to 1 mW, function to calibrate, and polarity to normal.

- 2. Connect a high-impedance, ac coupled oscilloscope to pin 1 of U1A. The display should be as shown in the figure for step 9 of the  $\langle \sqrt{1} \rangle$  Amplifier 1 and Ground Regulator Check.

*Hint:* If faulty, perform  $\langle \sqrt{1} \rangle$  above.

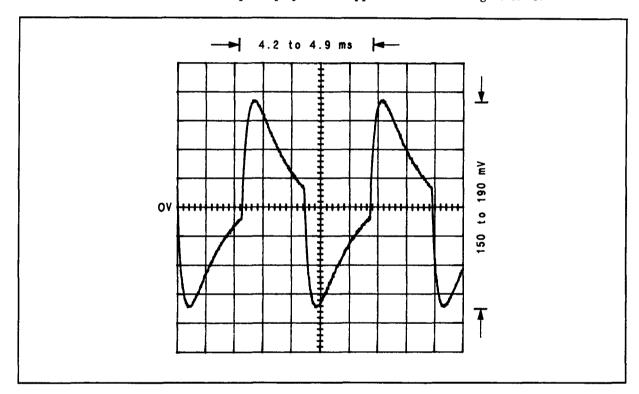

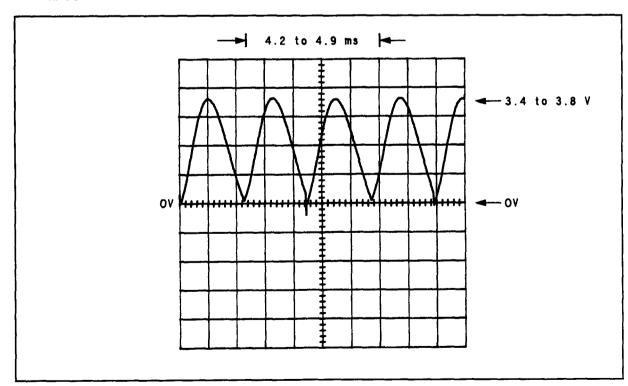

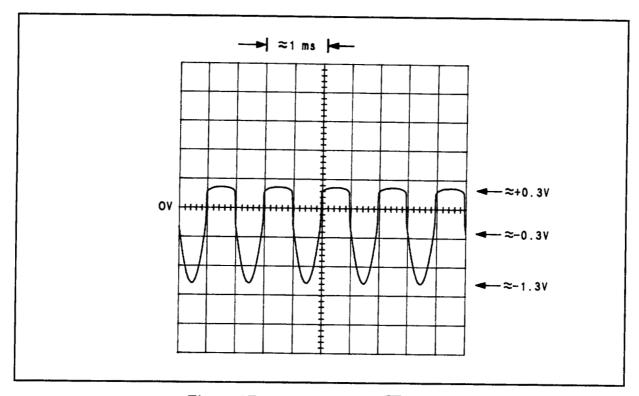

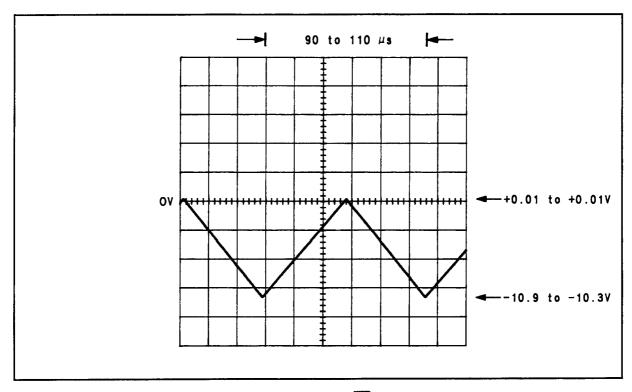

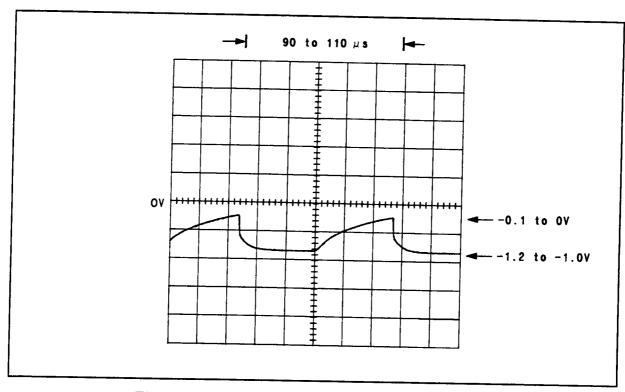

3. Connect the oscilloscope to pin 2 of U4A. Key in 0.209 SPCL to switch U4A on and U4B off. The waveform on the oscilloscope display should appear as shown in Figure 8F-3.

**Figure 8F-3.** Waveform for  $(\sqrt{2})$  Step 3

Hint: Pin 1 of U4A should be a TTL low. Pin 8 of U4B should be high.

4. Key in 0.208 SPCL to switch U4A off and U4B on. Switch the calibrator's range to 100 mW. The waveform should appear as in the figure for step 3.

Hint: Pin 1 of U4A should be high. Pin 8 of U4B should be low.

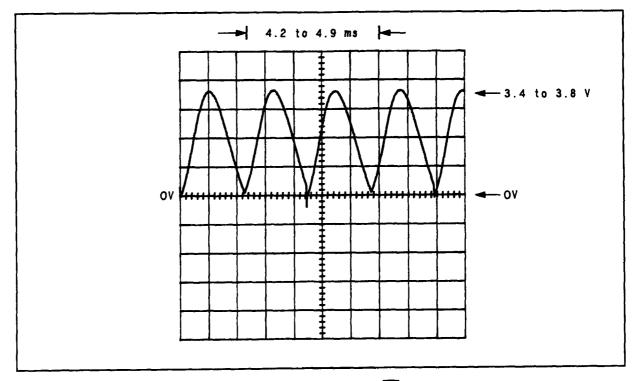

5. Connect the oscilloscope to pin 11 of U4C. Switch the calibrator's range to 1 mW. Key in 0.202 SPCL to switch U4C on and U4D and U8A off. The waveform should appear as shown in Figure 8F-4.

Hint: Pin 9 of U4C should be low. Pin 16 of U4D and pin 1 of U8A should be high.

**Figure 8F-4.** Waveform for  $\sqrt{2}$  Step 5

**Figure 8F-5.** Waveform for  $\sqrt{2}$  Step 8

6. Key in 0.204 SPCL to switch U4D on and U4C and U8A off. Switch the calibrator's range to 10 mW. The waveform should appear as in the figure for step 5.

Hint: Pin 16 of U4D should be low. Pin 9 of U4C and pin 1 of U8A should be high.

- 7. Key in 0.208 SPCL to switch U8A on and U4C and U4D off. Switch the calibrator's range to 100 mW. The waveform should appear as in the figure for step 5.

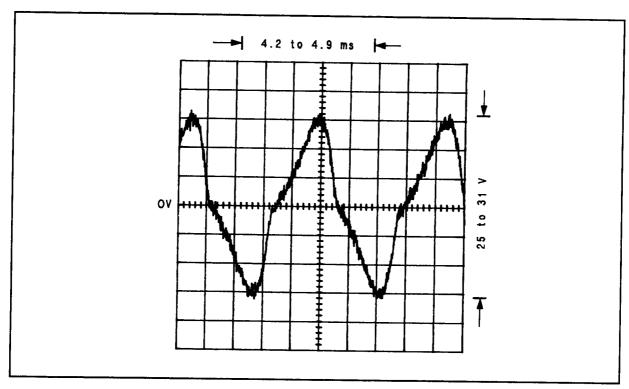

- 8. Connect the oscilloscope to A53TP1 (AC). The waveform should appear as shown in Figure 8F-5. Hint: The waveform at pin 7 of U2B should have a similar shape and an amplitude of approximately 600 mVpp.

### √3 Synchronous Detector Check

- 1. Connect the range calibrator to the SENSOR input. Set the calibrator's range to 1 mW, function to calibrate, and polarity to normal. Press RF POWER.

- 2. Connect a high-impedance, ac coupled oscilloscope to A53TP1 (AC). The display should be as shown in the figure for step 8 of the  $\bigcirc$  Amplifier 1, Attenuator 2, Amplifier 2, and Amplifier 3 Check.

Hint: If faulty, perform  $\langle \sqrt{2} \rangle$  above.

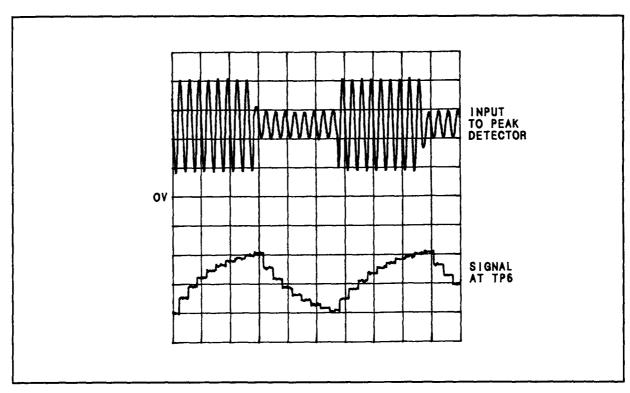

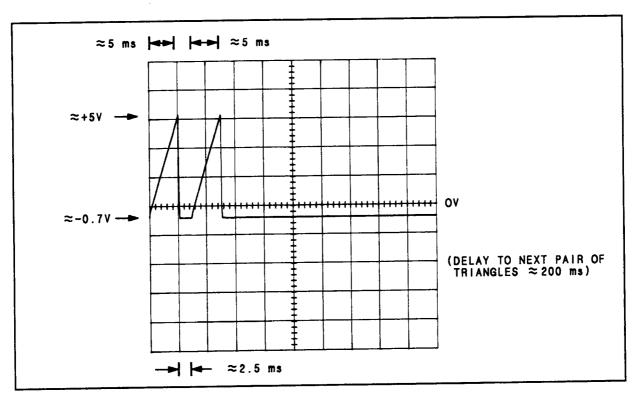

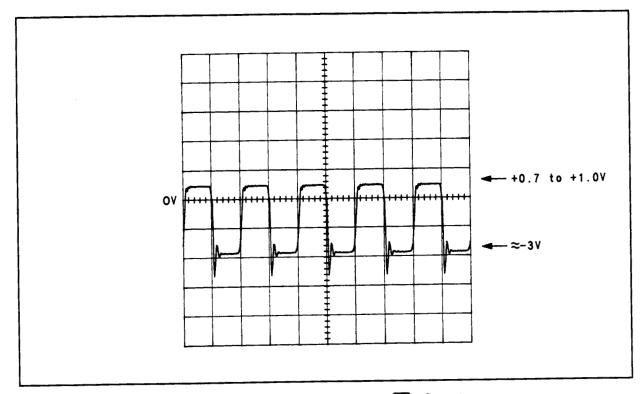

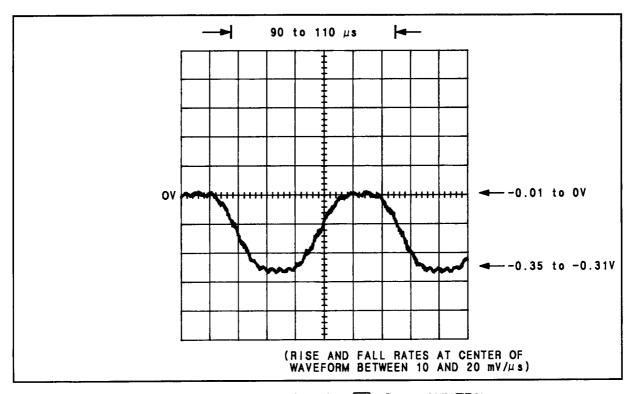

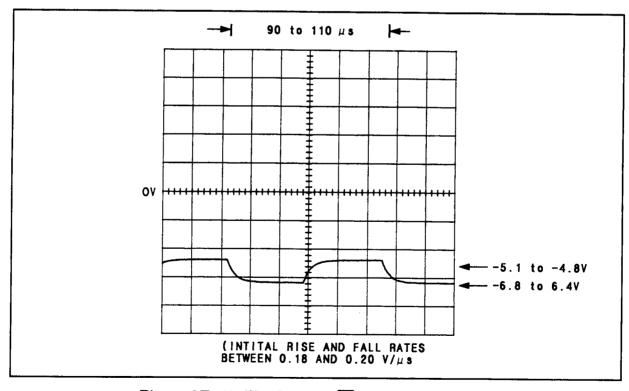

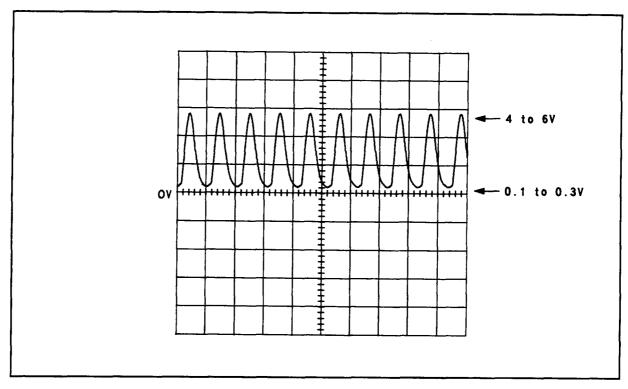

3. DC couple the oscilloscope and connect it to A53TP2 ( $\Phi$  DET). The waveform should appear as shown in Figure 8F-6.

Hint: The collector of Q6 should be switching between 0 and approximately -15V with a period between 4.2 and 4.9 ms. The gain of operational amplifier based on U3 switches from +1 to -1 as Q4 switches from off to on. Non-uniform half-cycles indicates unequal gain for the two states of U3.

Figure 8F-6. Waveform for  $\sqrt{3}$  Step 3

## 220 Hz Multivibrator Check

1. Connect a high-impedance, dc coupled oscilloscope to A53TP4 (MULTVIB or MV1). The waveform should be a square wave switching between 0V and 10 to 11V with a period between 4.2 and 4.9 ms.

Hint: A more accurate way of measuring the multivibrator's frequency and adjusting it if necessary is found in Adjustment 20—Power Meter.

2. Connect the oscilloscope to A53TP5 (MV2) and repeat step 1.

# **SERVICE SHEET 2**

### **Assembly**

• A53 RF Power (Control Circuits)

### **Principles of Operation**

#### General

This Service Sheet documents the circuits that filter the signal from the Synchronous Detector, zero the Power Sensor, and control the Power Meter and external Sensor Module.

#### **Noise Filter**

The dc voltage from the Synchronous Detector (see Service Sheet 1) is filtered to remove noise and improve measurement readability. U13 and associated components form an active, three-pole, low-pass filter. The noise bandwidth is 10 Hz with switch U8B closed and 1 Hz with U8B open. The 10 Hz bandwidth is used in ranges 5, 4, and 3 (refer to Table 8F-1); the 1 Hz bandwidth is used in ranges 2 and 1. (In addition, in range 1, the Controller effectively increases filtering by averaging several successive readings.)

The Voltmeter reads the Noise Filter output (RF PWR/SENSOR TYPE) via switch U8C to display RF power. The Voltmeter also reads the Noise Filter output via U8D to identify the type of sensor connected to the front-panel SENSOR input connector. By reading the voltage developed at the junction of R68, R69, and the SENSOR-TYPE READBACK line the type of sensor is determined. Each sensor type has a unique resistor value with one end of the resistor connected to ground. (In the HP 11722A Sensor Module, the resistor is  $1.62~\mathrm{k}\Omega$ .)

# **Zeroing Control**

Power offsets (positive or negative readings from the Power Meter when no power is actually applied) come primarily from the Power Sensing Element in the external Power Sensor. The offset is cancelled by the Zeroing Control DAC (U10) when the Power Meter is zeroed. To zero the Power Meter, the Controller removes the power from the external Power Sensor using the Input Switch in the Sensor Module. (If a sensor is used which is not part of a Sensor Module, the RF power source must be manually removed before zeroing is attempted.) With no power into the Power Sensor, the Controller takes an RF power reading and adjusts the Zeroing Control DAC to cancel the reading; more than one attempt may be required to bring the reading within limits.

The Zeroing Control DAC outputs a current proportional to the binary-weighted input. This output current, flowing through R65 develops a negative voltage. Another current, originating from Q15, flows through R67 to develop a constant positive voltage across R65. The combination of the currents from the DAC and Q15 thus permits a positive or negative offset. The offsetting voltage is fed to the Power Sensing Element of the external Power Sensor. To minimize drift of the offset, reference diodes VR3, VR4, and VR5 are biased by thermally compensated current sources (Q14 and Q15) to produce the reference voltage to the DAC and R67.

#### **Sensor Module Switch Control**

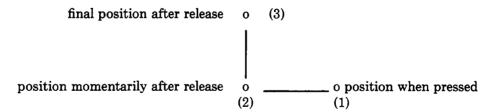

The Switch Drive One-Shot permits control of latching-type RF switches in the Sensor Module which can have either automatic breaking or non-breaking solenoid drive contacts. For either case, one-shot U16 provides an energizing pulse for 30 ms which is sufficient to throw the switch's plunger.

Switch Q3 actually energizes the RF switch solenoid. The collector resistor (R77) of Q3 provides sufficient drive current for the types of RF switches commonly used in the external Sensor Module.

CR3 suppresses the emf generated by the RF switch solenoid when the drive current is interrupted. Q3 is driven from U16 via Q13.

Relays K1 and K2, activated by U14A and U14B, route the switch drive to the proper solenoid contacts. The Controller then activates the RF switch via the Switch Drive One-Shot.

#### **Power Reference Oscillator Control**

The RF Power Reference Oscillator (see Service Sheet 3) is activated by the Controller via Q7 and Q2. When Q2 is on, -15V is supplied to the reference circuitry.

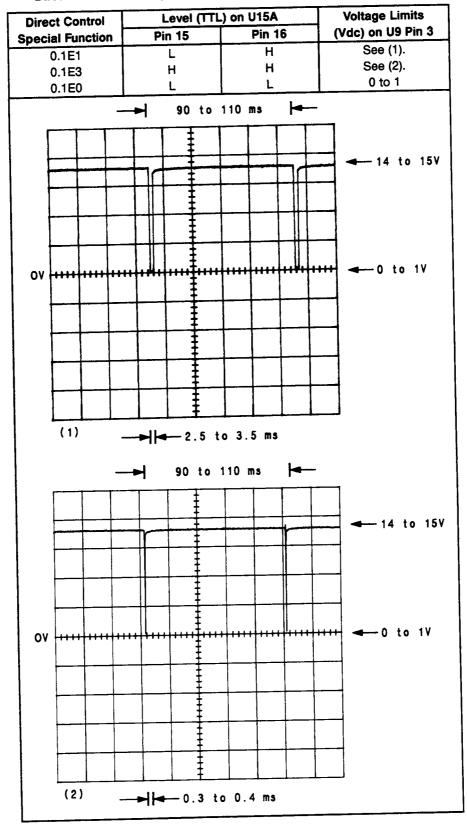

### **Frequency Offset Control**

Gates U15A and U15B provide a three-level (0, +3, and +5V) output to indicate to an external down-converter the status and frequency range of frequency offset. (See Table 8D-4 for status information.)

#### **Select Decoder and Data Latches**

Refer to the general discussion under *Instrument Bus* in Service Sheet BD5. R53 and C35 for the Power-Up Reset circuit that sets the front-end components of the instrument to the most-protected state at power-up; that is, input attenuation is set to maximum and the external Power Sensor is switched out.

### **Troubleshooting**

#### General

Procedures for checking the RF Power Assembly are given below. The circuits to check are marked on the schematic diagram by a hexagon with a check mark and a number inside, for example,  $\sqrt{3}$ . In addition, any points outside the labeled circuit area that must be checked are also identified. Fixed signals are also shown on the schematic inside a hexagon, for example,  $\sqrt{+1.9 \text{ TO} + 2.1 \text{ VDC}}$ .

Extend the board assembly where necessary to make measurements. Extending the assembly will require freeing the two multi-conductor cables atop the assembly so that they may be reconnected. Freeing the cables will require disconnecting several RF cables. The RF cables need not be reconnected while troubleshooting the assembly.

Tighten SMC connectors to 0.6 N·m (5 in·lb). Hand tightening of connectors is insufficient. Hand-tightened connectors can work loose and cause reduced performance or malfunctions.

## **Equipment**

# (V1) Noise Filters Check

- 1. Connect the range calibrator to the SENSOR input. Set the calibrator's range to 1 mW, function to calibrate, and polarity to normal. On the Measuring Receiver, press RF POWER.

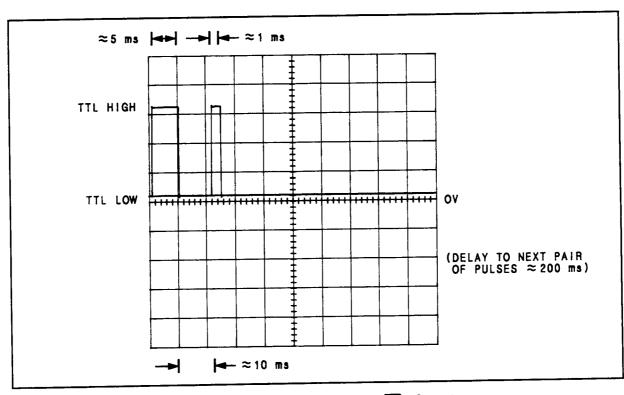

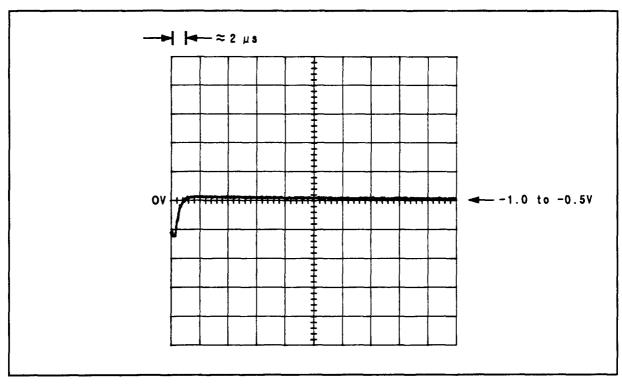

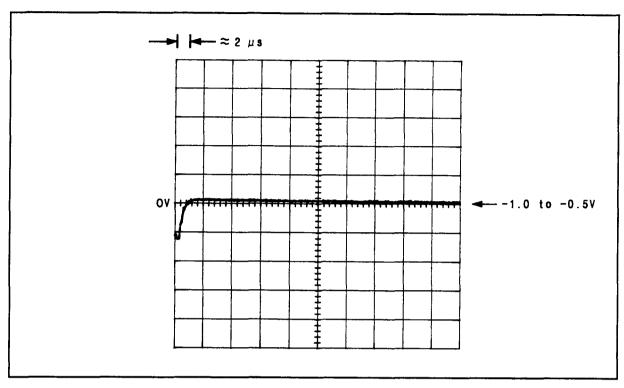

- 2. Connect a high-impedance, dc coupled oscilloscope to A53TP2 ( $\Phi$  DET). (See Service Sheet 1.) The waveform should appear as in Figure 8F-7.

Hint: If the waveform is faulty, see Service Sheet 1 and check the Synchronous Detector.

Figure 8F-7. Waveform for (V1) Step 2

3. Connect the oscilloscope to A53TP3 (FLTR). Key in 0.231 SPCL to set the Noise Filters to wide. The waveform should be dc at a level between 700 and 900 mV.

Hint: Pin 8 of U8B should be a TTL high.

4. Key in 0.230 SPCL to set the Noise Filters to narrow. The waveform should be between 700 and 900 mV.

Hint: Pin 8 of U8B should be a TTL low.

### √2 RF Power and Sensor-Type Readback Switches Check

- 1. Connect the range calibrator to the SENSOR input. Set the calibrator's range to 1 mW, function to calibrate, and polarity to normal. On the Measuring Receiver, press RF POWER.

- 2. Connect a high-impedance, dc coupled oscilloscope to A53TP3 (FLTR). The waveform should be dc at a level between 700 and 900 mV.

*Hint*: If the waveform is faulty, perform  $(\sqrt{1})$  above.

3. Key in 0.21A SPCL to enable the RF Power Readback Switch. Key in 49.F SPCL to read back the output of the switch. The display should read between 0.7 and 0.9.

Hint: Pin 9 of U8C should be a TTL low. Pin 16 of U8D should be a TTL high.

4. Key in 0.219 SPCL to enable the Sensor-Type Readback Switch. Key in 49.F SPCL. The display should read between -0.01 and +0.01. (The sensor-type resistor in the range calibrator is a short circuit.)

Hint: Pin 9 of U8C should be a TTL high. Pin 16 of U8D should be a TTL low.

### **⊘** Power Reference Oscillator Control Check

- 1. Connect a high-impedance, dc coupled oscilloscope to the collector of Q2.

- 2. Key in 0.21E SPCL to switch Q2 on. The dc waveform should be between -15 and -14 Vdc.

Hint: Pin 10 of U6 should be a TTL high.

- 3. Key in 0.21A SPCL to switch Q2 off. The dc waveform should be between +1 and +2 Vdc. *Hint:* Pin 10 of U6 should be a TTL low.

#### √4 Sensor Module Switch Control Check

- 1. Disconnect any connection to the SENSOR input.

- 2. Connect a high-impedance, dc coupled oscilloscope to pin 6 of U16.

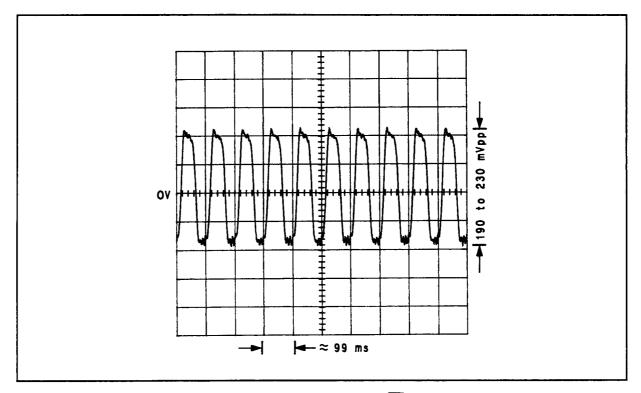

- 3. Key in 0.24 SPCL to trigger the Switch Drive One-Shot. The waveform on the oscilloscope should be a square wave with a period of approximately 60 ms and a level alternating between a TTL high and a TTL low.

Hint: Pin 1 of U16 should be low-going TTL pulses with a width of approximately 30 ms and a period of approximately 60 ms.

- 4. Connect the oscilloscope to pin 14 of K1. Connect a 10 k $\Omega$  resistor between pin 14 of K1 and ground. The waveform should be a square wave with a period of approximately 60 ms and a level alternating between approximately -15 and 0V.

- 5. Move the oscilloscope and resistor to pin 8 of the relay indicated in Table 8F-3. Key in the Direct Control Special Functions indicated in the table. For each step, the waveform should be as described. If faulty, also check the logic level on the pin on U14 indicated.

| Dalaw | Direct Control    | Mountain     | Level (TTL) at U14 |       |  |  |

|-------|-------------------|--------------|--------------------|-------|--|--|

| Relay | Special Functions | Waveform     | Pin 2              | Pin 7 |  |  |

| K1    | 0.212, 0.24       | as in step 4 | L                  | Н     |  |  |

| K1    | 0.21A, 0.24       | 0 Vdc        | Н                  | L     |  |  |

| K2    | 0.21A, 0.24       | as in step 4 | н                  | L     |  |  |

| K2    | 0.212, 0.24       | 0 Vdc        | <b>└</b>           | Н     |  |  |

**Table 8F-3.** Levels at Relays,  $\langle \sqrt{4} \rangle$  Step 5

# √5 Zeroing Control Check

- 1. Connect the range calibrator to the SENSOR input. Set the calibrator's function to standby.

- 2. On the Measuring Receiver, press RF POWER.

- 3. Connect a high-impedance, dc coupled oscilloscope to the collectors of Q14 then Q15. The dc voltage should be between +6.0 and +6.4 Vdc. (The two voltages may differ from each other.)

Hint: If the voltage at the collector of Q15 is faulty, check the anode of VR5; if the voltage is not 0V, there may be a fault in the Ground Regulator. (See Service Sheet 1.)

5. Connect the oscilloscope to pin 4 of U10. Successively key in the following Direct Control Special Functions to clear the latches of U11: 0.220 SPCL, 0.222 SPCL, 0.224 SPCL, 0.226 SPCL, 0.228 SPCL, 0.22A SPCL, 0.22C SPCL, and 0.22E SPCL. (Note that each suffix is even.) The oscilloscope should read approximately 15 mVdc.

Hint: Pins 4, 5, 6, 7, 9, 10, 11, and 12 of U11 should be TTL low.

6. Successively key in 0.221 SPCL, 0.223 SPCL, 0.225 SPCL, 0.227 SPCL, 0.229 SPCL, 0.22B SPCL, 0.22D SPCL, and 0.22F SPCL. (Note that each suffix is odd.) As each Direct Control Special Function is entered, the voltage should drop is successively larger steps until the voltage is approximately -15 mVdc.

Hint: As each Special Function is entered, the pins of U11 mentioned in the previous hint should successively go to a TTL high.

### √6 Select Decoder and Data Latches Check

1. Key in the Direct Control Special Functions indicated in Table 8F-4. For each setting, check the pins on U12 indicated.

**Table 8F-4.** Levels at U12,  $\sqrt{6}$  Step 1

| Direct Control      | Level (TTL) at U12 Pin |           |        |         |     |  |  |  |  |

|---------------------|------------------------|-----------|--------|---------|-----|--|--|--|--|

| Special<br>Function | 11                     | 12        | 13     | 13 14   |     |  |  |  |  |

| 0.200               | Н                      | Н         | Н      | Н       | •   |  |  |  |  |

| 0.210               | Н                      | Н         | н,     | •       | Н   |  |  |  |  |

| 0.220               | Н                      | Н         | •      | н       | Н   |  |  |  |  |

| 0.230               | Н                      | •         | н      | н       | Н   |  |  |  |  |

| 0.240               | •                      | Н         | Н      | н       | _H_ |  |  |  |  |

| * Low-(             | going TTI              | _ pulses, | ≈60 ms | period. |     |  |  |  |  |

2. Key in the Direct Control Special Functions indicated in Table 8F-5. For each setting, check the pins on U9 and U15 indicated.

**Table 8F-5.** Levels at U9 and U15,  $\bigcirc$  Step 2

| Direct Control   | L | evel (TTL | ) at U9 F | Level at U15 Pin |                |      |

|------------------|---|-----------|-----------|------------------|----------------|------|

| Special Function | 2 | 7         | 10        | 15               | 3              | 5    |

| 0.230            | L | L         | L         | L                | TTLL           | TTLL |

| 0.23E            | Н | Н         | Н         | H                | TTLH           | TTLH |

| 0.232            | L | Н         | L         | ] L              | 2.6 to 3.2 Vdc | TTLL |

3. Key in the Direct Control Special Functions indicated in Table 8F-6. For each setting, check the pins on U5 indicated.

**Table 8F-6.** Levels at U5,  $\langle \sqrt{6} \rangle$  Step 3

| Direct Control      |   | Level (TTL) at U5 Pin |   |    |    |  |  |  |  |  |

|---------------------|---|-----------------------|---|----|----|--|--|--|--|--|

| Special<br>Function | 2 | 3                     | 6 | 11 | 14 |  |  |  |  |  |

| 0.200               | L | Н                     | Н | Н  | Н  |  |  |  |  |  |

| 0.20F               | н | L                     | L | L  | L  |  |  |  |  |  |

4. Key in the Direct Control Special Functions indicated in Table 8F-7. For each setting, check the pins on U6 indicated.

**Table 8F-7.** Levels at U6,  $(\sqrt{6})$  Step 4

| Direct Control   |   | Level (TTL) at U6 Pin |    |    |    |  |  |  |  |  |

|------------------|---|-----------------------|----|----|----|--|--|--|--|--|

| Special Function | 3 | 6                     | 10 | 14 | 15 |  |  |  |  |  |

| 0.210            | Н | Н                     | L  | Н  | L  |  |  |  |  |  |

| 0.21F            | L | L                     | н  | L  | Н  |  |  |  |  |  |

5. Key in 0.0 SPCL to disable the current Direct Control Special Function. Momentarily ground pin 1 of U9 to reset the latches. Measure all the IC pins in steps 2, 3, and 4. For each pin, the level should be the same as those given for the Direct Control Special Function code 0.230 in step 2, 0.200 in step 3, and 0.210 in step 4.

# **SERVICE SHEET 3**

### **Assembly**

• A32 Power Reference Oscillator

### **Principles of Operation**

#### General

The Power Reference Oscillator generates a 50 MHz signal which maintains a constant output level over a wide range of environmental conditions. The oscillator is adjusted to deliver 1 mW (0 dBm) into a  $50\Omega$  load.

#### 50 MHz Oscillator

The tank circuit of the 50 MHz Oscillator is a pi-network consisting of C11, L1, and the series combination of C13 and C14. (Since C13 has much less capacitance than C14, it predominates over C14 in determining the frequency of oscillation.) At 50 MHz, the tank circuit produces 180° phase shift. Another 180° phase shift is generated between the base and collector of Q1. The output of the tank circuit is fed to the base of Q1 through a capacitive voltage divider—C4 and varactor diode CR3. Thus, at 50 MHz, an in-phase signal fed back to the base of Q1 re-enforces the oscillation.

Voltage divider R12 and R13 sets the bias voltage at the base of Q1. Emitter resistors R14 and R15 establish the quiescent emitter current. The frequency of oscillation is adjusted by L1 (FREQ). The output of the oscillator is taken from the tap of capacitive divider C13 and C14. L2 is an RF choke which sets the dc collector voltage of Q1 at ground potential.

#### **ALC Loop**

The Automatic Leveling Control (ALC) Loop is a negative-feedback loop which assures that the oscillator output level remains constant. CR2 detects the positive peak of the signal at the output of the tank circuit. The detected peak voltage is stored in C7 and is compared to a dc reference voltage by comparator U2. If the detected signal level differs from the reference, U2 alters the reverse bias on varactor diode CR3 which changes the junction capacitance of the diode and thus the division ratio of the capacitive divider C9 and CR3. If the capacitance of CR3 decreases (due to an increase of reverse bias), the positive feedback to the base of Q1 is increased and the output level of the oscillator is increased.

#### DC Reference and Level Adjust

The reference to which the detected oscillator signal is compared in the ALC Loop originates with voltage reference diode VR1. VR1, when biased with a specified current, has a breakdown voltage that is constant with temperature. Q2 supplies a constant current to VR1. VR2 sets the emitter current of Q2 and has a temperature coefficient that tracks the base-emitter junction of Q2.

U1 inverts and slightly attenuates the reference voltage from VR1. R4 (LEVEL ADJ) permits fine adjustment of the reference and hence the output power of the oscillator. CR1 adds a temperature coefficient to the reference input of U2 which matches the temperature coefficient of the detector diode CR2. The Power Reference Oscillator is switched off by interrupting the -15V supply via the PWR REF OSC ON/OFF -15V line.

### **Troubleshooting**

#### General

Procedures for checking the Power Reference Oscillator Assembly are given below. The circuits to check are marked on the schematic diagram by a hexagon with a check mark and a number inside, for example,  $\sqrt{3}$ . Fixed signals are also shown on the schematic inside a hexagon, for example, (+1.9 TO + 2.1 VDC). Remove the assembly, the assembly cover, and RF cables where necessary to make measurements.

CAUTION

When removing the RF power calibrator assembly, take care that the power supply terminals do not short against the metal chassis parts.

Tighten SMC connectors to 0.6  $N \cdot m$  (5 in lb). Hand tightening of connectors is insufficient. Hand-tightened connectors can work loose and cause reduced performance or malfunctions.

If a fault in the Power Reference Oscillator is isolated and repaired, the correct output level (1 mW) must be set by a very accurate power measurement system. To see what this entails, review Adjustment 18 or 19—Power Reference in Section 5.

### **Equipment**

### (V1) Power Reference Oscillator Check

1. Connect a high-impedance, dc coupled oscilloscope to C3 (where the violet wire connects). Press RF POWER, and switch CALIBRATE on and off. The dc waveform should read between +1 and +2 Vdc when off and between -15 and -14 Vdc when on.

Hint: If faulty, see Service Sheet 2 and check the Power Reference Oscillator Control.

2. Switch CALIBRATE on. Connect the oscilloscope to A32TP1. The voltage should read between +3.5 and +5.5 Vdc.

Hint: The voltage at the collector of  $Q_2$  should be between -6.4 and -6.0 Vdc.

3. Connect the oscilloscope to A32TP2. The voltage should read between -5 and -1 Vdc.

Hint: If the oscillator does not oscillate and the voltage at A23TP2 is more negative than -5 Vdc, U2 is working properly. If the oscillator output is very large and the voltage at A23TP2 is more positive than -1 Vdc, U2 is working properly.

Hint: Modulation or spurious signals on the oscillator output may be caused by a fault in R9, R10, R11, or C8.

### Service Sheet 4

#### **ASSEMBLIES**

- A15 RF Input Control

- A16 RF Detector

- A70 Amplifier/Switch Interconnect

- AT1 Input Attenuator

#### PRINCIPLES OF OPERATION

#### General

The RF Input Control Assembly (A15) contains circuits that control and drive the Input Attenuator (AT1), a 10 dB fixed attenuator (AT2), and the RF Amplifier (U1). The RF Detector Assembly (A16) contains the RF Peak Detector and the 5.25 MHz High-Pass Filter. The Amplifier/Switch Interconnect Assembly (A70) filters the drive lines to the RF switches (S1 and S2) which insert or remove the 10 dB attenuator (AT2) and RF Amplifier (U1). A70 also contains the Amplifier Overpower Detector which senses overloads of the RF Amplifier (U1). The attenuators and amplifiers provide the proper drive levels for the Input Mixer (see Service Sheet 5).

#### NOTE

The RF Peak Detector also senses RF overloads and should not be confused with the Amplifier Overpower Detector on the A70 Amplifier/Switch Interconnect Assembly. The two detectors are independent.

### RF Input Control (A15)

The A20 LO Control Assembly (see Service Sheet 21) decodes the Instrument Bus to control the Input Attenuator (chassis part AT1), 10 dB attenuator AT2, and the RF Amplifier (chassis part AS1). The Attenuation Decoding logic (U6D, U8A, U10A, U10B, U11B, and U11C) further decodes the Input Attenuator and 10 dB attenuator control lines. U7 sums the fixed Q input (hexadecimal 7, binary 0111) with a variable P input and a variable CI (carry in) input. See Table 8F-8 for a partial listing of attenuation vs. logic states. The attenuator drive lines are decoded in such a way that whenever RF attenuation is required, the 10 dB attenuator is switched in ahead of the Input Attenuator to provide the lowest and most constant input SWR.

| Total                  | Sta        | tus of A   | ttenuat    | ors | State of Input Logic |              |              | Logic States of U7 |    |    |    |    |     | Logic |    |                     |

|------------------------|------------|------------|------------|-----|----------------------|--------------|--------------|--------------------|----|----|----|----|-----|-------|----|---------------------|

| Input Attenuation (dB) | Atten<br>1 | Atten<br>2 | Atten<br>3 | AT2 | 40 dB<br>(H)         | 20 dB<br>(H) | 10 dB<br>(H) | CI                 | P3 | P2 | P1 | P0 | Σ2  | Σ1    | Σ0 | State<br>of<br>U11C |

| 0                      | Out        | Out        | Out        | Out | L                    | L            | ۲            | H                  | L  | L  | L  | L  | L   | L     | L  | L                   |

| 10                     | Out        | Out        | Out        | In  | L                    | L            | Н            | L                  | L  | L  | L  | Н  | L   | L     | L  | Н                   |

| 20                     | in         | Out        | Out        | In  | Ł                    | Н            | L            | L                  | L  | L  | H  | L  | L   | L     | н  | Н                   |

| 30                     | Out        | ın         | Out        | in  | L                    | Н            | Н            | L                  | L  | L  | Н  | н  | L   | н     | L  | н                   |

| 40                     | In         | In         | Out        | in  | Н                    | L            | L            | L                  | L  | Н  | L  | L  | ] L | Н     | Н  | н                   |

| 50                     | Out        | Out        | (n         | in  | н                    | L            | Н            | L                  | L  | Н  | L  | Н  | ] н | L     | L  | н                   |

| 50*                    | ln i       | Out        | ín         | Out | н                    | <b>Н</b>     | L            | L                  | L  | н  | Н  | L  | Н   | L     | н  | L                   |

Table 8F-8. Attenuator Decoding

rev.28JAN87 Service Sheet 4 8F-17

The attenuation settings are monitored for any changes by the change detector circuit (U15, U16, and U17). The attenuator and switch are pulsed with the new information, the current attenuation settings are compared with the desired settings (U15) and if they don't match, the new data is latched in as the current data and the drivers pulse the switch and attenuator with the new information. The drivers for the attenuator (AT1) are on the A15 board (U14) and to minimize currents in the ribbon cable, the drivers for the attenuator/switch (AS1) are on the A70 board (U2).

The Overpower Latch (U9A) is clocked to a low (that is, the low at its J1 input is clocked into the non-inverting output) whenever the AMP OVERPOWER (L) line goes low (that is, whenever the RF Amplifier (chassis part U1) is overloaded). The overpower condition switches out the RF Amplifier (via U6C) independent of the Controller.

The AMP STATUS (L) line indicates to the Controller the status of the RF Amplifier to determine: (1) if, at power-up, the RF Input Control Assembly is present, and (2) for each measurement loop, if the amplifier has been overpowered. Since the Controller software is used in other HP instruments, the Controller must determine if the front-end hardware is that of the Measuring Receiver. Therefore, at power-up the AMP CONTROL (H) line is (1) set low, then (2) set high, and the AMP STATUS (L) line is monitored. If the A15 RF Input Control Assembly is not present, AMP STATUS (L) is high both times. (An open circuit is a TTL high.) If the RF Input Control Assembly is present, AMP STATUS (L) is high then low.

#### NOTE

If the RF Amplifier (chassis part U1) is overpowered during the second part of this test, a low on the AMP STATUS (L) line is still read by the Controller during power-up because the reading will have been completed before the amplifier can be switched in. (The overpower condition is discovered during the first measurement cycle.)

### Input Attenuator (AT1)

The Input Attenuator is a 10 dB step attenuator with steps from 0 to 70 dB. Only steps 0 to 40 dB are used in making measurements unless Special Function 35 (RF Level) or the RF Power measurement mode is used with no power sensor connected. For these two exceptions 50 dB is selected and the 10 dB attenuator (AT2) is not used. (60 and 70 dB are never selected.)

#### 5.25 MHz High-Pass Filter (A16)

The 5.25 MHz High-Pass Filter must be switched in manually by entering User Special Function 3.3, 3.4, 3.7 or 3.8. Its function is to prevent the IF from responding to low-frequency, spurious signals which may be present along with a higher-frequency input signal. The filter is a diplexer type which presents a  $50\Omega$  termination to signals of all frequencies present at its output (whether above or below the cutoff frequency). An example of such a signal is the IF itself which, if not properly terminated, can deteriorate the flatness of the Input Mixer (see Service Sheet 5) over the wide range of input frequencies. The filter is switched in by relay K2 via peripheral driver U6B.

#### RF Level Detector (A16)

The RF Peak Detector (CR2) is a Schottky diode that detects the positive peak of the input signal. The detected dc voltage is used primarily to give an indication of RF level for setting the input attenuators (chassis parts AT1 and AT2) when tuned-measurement modes (such as modulation) are selected. The detector also gives the RF power level for Special Function 35 (RF Level) and for the RF Power measurement mode when no power sensor is connected to the instrument. When the instrument's RF input is overpowered the RF Peak Detector output deactivates the Overpower Protection relay via the Overpower Detector and the LO Control Assembly (see Service Sheet 21).

Since the 10 dB attenuator (chassis part AT2) is inserted before the RF Peak Detector circuitry, the sensitivity of the circuits that follow the RF Peak Detector must be altered by 10 dB to compensate. This is done in various ways as explained in the discussions that follow.

8F-18 Service Sheet 4 rev.28JAN87

Because the RF Peak Detector can introduce a slight amount of clipping of the input signal, it is switched slightly off after the instrument is tuned to the input signal (except when measuring RF level). To turn the detector off, Q1 is switched on, which reverse biases the detector diode CR2 via R10 or R11, U1A, R5, and R3. The reverse bias, however, is low enough to permit the detector to trip the Overpower Detector when more than 1W is applied to the instrument's RF input. Switch U1A changes the detector's turn-off threshold to compensate for the presence or absence of the 10 dB attenuator. Switch 1 of U1A is on when the 10 dB attenuator is in; switch 2 is off.

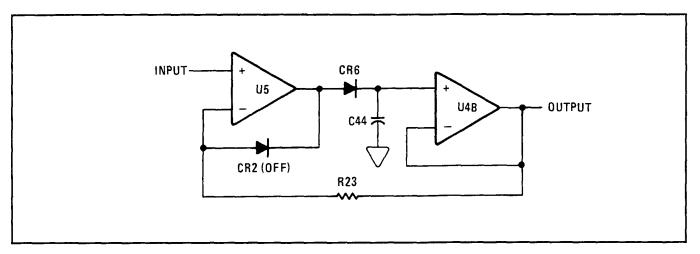

### **Detector Amplifier (A16)**

U2 forms a unity-gain amplifier and peak detector with offset. U2 detects the envelope peaks of the signal from the RF Peak Detector when AM is present on the RF input. Whenever the voltage at the non-inverting (+) input of U2 exceeds that of the inverting input (-), the output transistor of U2 (see Note 2 on the schematic) turns on and charges C26 from its emitter until the voltage across C26 equals the input voltage at the inverting input plus the constant drop across CR7, R34, and R27. When the input voltage drops, the output of U2 shuts off, and C26 remains charged to its previous level. R25 and R26 slowly discharge C26 when the input signal level is lowered or the signal is removed. U3B is activated (by the OVER POWER (L) input from the LO Control Assembly) to discharge C26 just prior to each level measurement from the RF Peak Detector; then C26 is allowed to recharge to the current, peak RF level.

CR7 is biased on by R18, which acts as a current source. CR7 is hot carrier diode whose offset voltage tracks CR2 with temperature. Fine adjustment of the offset is made with R27 (DET OFS), which is set for zero output from U4 when no input signal is present.

U4 is configured as a unity-gain amplifier when the 10 dB attenuator is not switched in—switch 1 of U5A is off, switch 2 is on; switch 2 of U5B is on. When the 10 dB attenuator is in (that is, line AT2 (H) is high), switches U5A and U5B toggle, and the gain of U4 is approximately 10 dB. R29 does not affect the gain of U4 but provides an input resistance at the non-inverting (+) input of U4 to match the input resistance (the combination of R30 and R31) at the inverting (-) input. Since the bias currents of the two inputs are nearly equal, the offset voltages created by the two input currents cancel. R33 (DET GAIN) adjusts the overall sensitivity of the RF Peak Detector.

### Overpower Detector (A16)

The Overpower Detector comparator U3 senses when the output from the RF Peak Detector (via voltage divider R5, R8, and R9) exceeds +3.4V (set by R14, R15, and hysteresis resistor R20). This reference corresponds to 1W of input power. Switch U1B selects which tap of the voltage divider is input to U3A. Switch 2 is closed when the 10 dB attenuator is out. When an overpower condition exists, the output of U3A then goes low and deactivates the Overpower Protection relay K1 via the LO Control circuits (see Service Sheet 21). K1 remains deactivated until reset by the operator pressing any front-panel key.

The OVERPOWER (L) output line from U3A is also an input line from the LO Control circuit which performs two other functions. First, the line is used to discharge the storage capacitor (C26) of the Detector Amplifier prior to an RF level measurement. Second, the line is used to turn off the RF Peak Detector as discussed previously. To accomplish these two tasks, a quasi-low is put on the line by the LO Control circuits. The low does not trip the overpower circuit but is low enough to set Detector Amplifier Discharge comparator U3B low which discharges C26. The quasi-low also turns off the RF Peak Detector by turning on Q3, Q2, and Q1.

### **Troubleshooting**

#### General

Procedures for checking the RF Input Control Assembly, the RF Detector Assembly, the Amplifier/Switch Interconnect Assembly, the Input Attenuator, and other RF input circuits are given below. The circuits to check are marked on the schematic diagram by a hexagon with a check mark and a number inside, for example,  $(\sqrt{3})$ . Fixed signals are also shown on the schematic inside a hexagon, for example, (+1.9 TO + 2.1 VDC). Extend the board assemblies where necessary to make measurements. Remove the front-panel assembly where necessary to make measurements on the RF input devices.

Tighten SMA connectors to 0.8 to 1.1  $N \cdot m$  (7 to 10 in lb). Tighten SMC connectors to 0.6  $N \cdot m$  (5 in lb). Hand tightening of connectors is insufficient. Hand-tightened connectors can work loose and cause reduced performance or malfunctions.

#### Equipment

| Oscilloscope     | HP 1740A |

|------------------|----------|

| Power Supply     | HP 6215A |

| Signal Generator |          |

| Voltmeter        |          |

### 10 dB Attenuator, RF Amplifier, and Amplifier/Switch Interconnect Check

- 1. Set the signal generator to 11 MHz CW at -30 dBm. Connect its RF output to the input of an ac coupled oscilloscope. Switch the input impedance of the oscilloscope to  $50\Omega$  or terminate the input in  $50\Omega$  using a tee.

- 2. Fine adjust the signal generator's level for an oscilloscope display of 4 divisions peak-to-peak.

- 3. Connect the oscilloscope's input to the end of W8 where it connects to A16J1 (RF IN) on the A16 RF Detector Assembly. Connect the signal generator's output to the Measuring Receiver's INPUT.

- 4. Key in the Direct Control Special Functions listed in Table 8F-9. For each setting, the waveform amplitude should be within the limits indicated. If faulty, also check the logic level at the pins indicated.

- Hint: Pin 7 of A70U1A (pin 2 of A70J1 or pin 2 of A15J1) should be a TTL high. A low on this pin will remove the RF Amplifier (pin 8 of A70J1 low, pin 6 of A70J1 high, AMP annunciator off).

- 5. Slowly increase the signal generator's level to -10 dBm. The RF waveform should be distorted and its level should be approximately 2 Vpp.

- Hint: The RF Amplifier (chassis part U1) is clipping at this level and not the limiter (chassis part U2).

| Direct<br>Control<br>Special | B.                                               | pe Display<br>liv pk-pk) | - |    | el (TTI<br>A15J1 | - | 1   | nciator<br>Itus |  |  |  |

|------------------------------|--------------------------------------------------|--------------------------|---|----|------------------|---|-----|-----------------|--|--|--|

| Function                     | Minimum                                          | Maximum                  | 9 | 10 | 8                | 6 | PAD | AMP             |  |  |  |

| 0.030, 0.047                 | 3.9                                              | 4.1                      | L | Н  | L                | Н | Off | Off             |  |  |  |

| 0.045                        | 1.1                                              | 1.4                      | Н | L  | L                | Н | On  | Off             |  |  |  |

| 0.032, 0.047*                | 5.7                                              | 7.0                      | L | Н  | Н                | L | Off | On              |  |  |  |

|                              | * Reduce the oscilloscope's vertical gain by 10. |                          |   |    |                  |   |     |                 |  |  |  |

**Table 8F-9.** Levels at W8,  $\langle \sqrt{1} \rangle$  Step 4

6. Slowly increase the signal generator's level to +3 dBm and observe the AMP annunciator. The AMP annunciator should remain on until the signal generator level is between -1 and +1 dBm. The RF waveform amplitude should be between 600 and 800 mVpp.

Hint: Pin 7 of A70U1A should be a TTL low. The logic levels on A15J1 should be the same as the first entry in the table of step 4.

### √2 Input Attenuator Check

- 1. Set the signal generator to 11 MHz CW at +10 dBm. Connect its RF output to the input of an ac coupled oscilloscope. Switch the input impedance of the oscilloscope to  $50\Omega$  or terminate the input in  $50\Omega$  using a tee.

- 2. Fine adjust the signal generator's level or an oscilloscope display of 5 divisions peak-to-peak.

- 3. Connect the oscilloscope's input to AT1J2 (RF OUT). Connect the signal generator's output to AT1J1 (RF IN).

- 4. Key in the Direct Control Special Functions listed in Table 8F-10. For each setting, the waveform amplitude should be within the limits indicated. If faulty, also check the logic level at the pins indicated.

Hint: A16TP5 should be a TTL high. A low on this pin will set AT1 to 50 dB (pins 13 and 3 high, pin 11 low).

| Direct<br>Control | Oscilloscope Display Limits (div pk-pk)  Logic Level (TTL) at A15J2 Pin |             |        | L) at  |        |       |    |   |

|-------------------|-------------------------------------------------------------------------|-------------|--------|--------|--------|-------|----|---|

| Special Function  | Minimum                                                                 | Maximum     | 13     | 2      | 11     | 5     | 3  | 9 |

| 0.047             | 4.9                                                                     | 5.1         | L      | Н      | L      | Н     | L  | Н |

| 0.043             | 1.3                                                                     | 1.9         | Н      | L      | L      | Н     | L  | Н |

| 0.041*            | 4.9                                                                     | 5.1         | L      | Н      | Н      | L     | L  | Н |

| 0.046             | 1.3                                                                     | 1.9         | Н      | L      | Н      | L     | L: | Н |

| 0.044*            | 4.9                                                                     | 4.9         | L      | Н      | L      | Н     | Н  | L |

| •                 | Reduce the                                                              | oscilloscop | e's ve | rtical | gain b | y 10. |    |   |

**Table 8F-10.** Levels at AT1J2,  $\langle \sqrt{2} \rangle$  Step 4

# √3 5.25 MHz High-Pass Filter Check

- 1. Set the signal generator to 5.25 MHz CW at +3 dBm. Connect its RF output the the input of an ac coupled oscilloscope. Switch the input impedance of the oscilloscope to  $50\Omega$  or terminate the input in  $50\Omega$  using a tee.

- 2. Fine adjust the signal generator's level for an oscilloscope display of 1 Vpp.

- 3. Connect the signal generator's output to the A16J1 (RF IN). Connect the oscilloscope's input to A16J2 (RF OUT).

4. Key in 0.024 SPCL to bypass the 5.25 MHz High-Pass Filter. The amplitude of the RF waveform should be between 0.76 and 1.00 Vpp.

Hint: Pins 5 and 6 of A16U6B should be TTL low. If the amplitude is very low, check the Overpower Protection.

5. Key in 0.02C SPCL to insert the 5.25 MHz High-Pass Filter. The amplitude of the RF waveform should be between 0.59 and 0.73 Vpp.

Hint: Pins 5 and 6 of A16U6B should be TTL high.

### (14) Overpower Protection Check

- 1. Set the power supply to 0 Vdc.

- 2. Connect the lead of the supply to chassis ground. Connect the + lead of the supply to A16J1 (RF IN). Remove the cable from A16J2 (RF OUT).

- 3. Connect a high-impedance, dc coupled oscilloscope to A16TP5.

- 4. Press the blue key then press INSTR PRESET (the AUTOMATIC OPERATION key) to preset the instrument. Key in 0.047 SPCL to bypass the 10 dB attenuator (chassis part AT2). The voltage level displayed on the oscilloscope should be a TTL high.

Hint: A16TP2, A16TP4, and the collector of A16Q1 should be at the same potential which should be a few tenths of a volt negative.

# CAUTION

In the next step monitor the supply current while turning up the supply. If current flow is observed, immediately turn the supply back to 0 Vdc. Current flow indicates that the 5.25 MHz High-Pass Filter is switched in; it should not be.

5. Slowly turn up the voltage on the power supply to +15 Vdc. At a voltage between +10 and +12 Vdc a click should occur and the voltage level on the oscilloscope should switch to a TTL low. As soon as observation is made, set the power supply back to 0 Vdc.

Hint: Pin 10 of A16U1B should be a TTL low at all times.

- 6. Key in 0.045 SPCL to insert the 10 dB attenuator.

- 7. Slowly turn up the voltage on the power supply to +5V. At a voltage between +3 and +4 Vdc a continuous clicking should occur and the voltage level on the display should oscillate between a TTL low and a TTL high. Do not allow the clicking to continue more than a few seconds. Set the power supply back to 0 Vdc.

Hint: Pin 10 of A16U1B should oscillate between a TTL low and a TTL high. (The line AT2 IN (H) controls A16U1B in such a way as to create a relaxation oscillator during this step.)

- 8. Disconnect the power supply. Press CLEAR. Measure the continuity of the contacts of A16K1 (pins 3 and 4). The contacts should be closed (a short circuit).

- 9. Switch POWER to STBY. The contacts should be open.

8F-22 Service Sheet 4 rev. 15JUN90

### (\sqrt{5}) Detector Amplifier Check

1. Set the signal generator to 11 MHz CW at +13 dBm. Connect its RF output to A16J1 (RF IN).

#### NOTE

A16J2 (RF OUT) should remain connected to AT1J1 (RF IN) or be terminated in  $50\Omega$ .

- 2. Disconnect any cable from the SENSOR input connector.

- 3. Press the blue key then press INSTR PRESET (the AUTOMATIC OPERATION key) to preset the instrument. Press RF POWER.

- 4. Key in 49.31 SPCL to connect the internal voltmeter to the output of the Detector Amplifier. Change the level of the signal generator as indicated in Table 8F-11 and note the display. Alternatively, measure A16TP1 with a dc voltmeter.

Hint: If the off condition above is slightly out of limit, perform Adjustment 1—RF Peak Detector Offset and Gain.

Hint: Pin 15 of A16U5A should be a TTL low.

Table 8F-11. Levels at A16J1, √5 Step 4

RF Level

Display

Voltage Limits

| RF Level<br>(dBm) | Display<br>Limits | Voltage Limits<br>at A16TP1 (Vdc) |

|-------------------|-------------------|-----------------------------------|

| +13               | 1.17 to 1.32      | +1.19 to +1.35                    |

| +3                | 0.30 to 0.38      | +0.31 to +0.39                    |

| Off               | -0.003 to 0.003   | -0.008 to +0.008                  |

- 5. Set the signal generator level back to +3 dBm.

- 6. Key in 0.045 SPCL to insert the 10 dB Attenuator (AT1). Key in 49.31 SPCL again. The display should read between 1.01 and 1.28, or the voltmeter should read between +1.04 and +1.31 Vdc.

Hint: Pin 15 of A16U5A should be a TTL high.

# (V6) Peak RF Detector Offset and On/Off Switch Check

1. Remove the cable (W8) from A16J1 (RF IN).

#### NOTE

A16J2 (RF OUT) should remain connected to AT1J1 (RF IN) or be terminated in  $50\Omega$ .

- 2. Disconnect any cable from the SENSOR input.

- 3. Press the blue key then press INSTR PRESET (the AUTOMATIC OPERATION key) to preset the instrument. Press RF POWER.

- 4. Measure the dc voltage at A16TP2. It should be between -0.3 and -0.1 Vdc. (The input impedance of the voltmeter must be at least 10 M $\Omega$ .)

Hint: A16Q1 should be off.

- 5. Measure the dc voltage at pin 2 of A16U2. It should be 15 to 35 mV more negative than the voltage in step 4.

- 6. Key in 0.020 SPCL to turn the detector off.

7. Measure the dc voltage at A16TP2. It should be between +9 and +11 Vdc.

Hint: A16Q1 should be on. Pin 15 of A16U1A should be a TTL low.

- 8. Measure the dc voltage at pin 2 of A16U2. It should be between +13 and +14.5 Vdc.

- 9. Key in 0.045 SPCL to switch in AT2.

- 10. Measure the dc voltage at A16TP2. It should be between +2 and +4 Vdc.

Hint: Pin 15 of A16U5A should be a TTL high.

# ✓ Detector Amplifier Discharge Check

1. Set the signal generator to 11 MHz CW at +13 dBm. Connect its RF output to the A16J1 (RF IN).

#### NOTE

A16J2 (RF OUT) should remain connected to AT1J1 (RF IN) or be terminated in  $50\Omega$ .

- 2. Disconnect any cable from the SENSOR input connector.

- 3. Press the blue key then press INSTR PRESET (the AUTOMATIC OPERATION key) to preset the instrument. Key in 0.020 SPCL to turn the RF Peak Detector off. Key in 49.31 SPCL to connect the internal voltmeter to display the output of the Detector Amplifier. The display should read between -0.0200 and 0.0200.

- 4. Key in 0.024 SPCL to turn the detector on. Again key in 49.31 SPCL. The display should read between 1.0000 and 1.3000.

- 5. Set the signal generator for 50% AM at a 20 Hz rate. The display should vary no more than  $\pm 0.4$  from its average value.

- 6. Press RF POWER. Switch the signal generator's AM off, then turn the RF off and note the Measuring Receiver's display as the reading decreases. The reading should decrease to less than 0.0100 -03 W by the second reading after the RF is switched off.

#### **⟨√8⟩** SWR Check

1. Perform Performance Test 9—SWR.

# Attenuator and RF Amplifier Decoding Check

1. Key in the Direct Control Special Functions indicated in Table 8-12. For each setting, check the pins on the ICs indicated.

Hint: Pins 3 and 5 of A15U2, U4, and U5 should be open when pins 2 and 6 respectively are high and TTL low when pins 2 and 6 are low. (The outputs of these ICs are open collector. The solenoids they drive switch to open circuits after the attenuator pad switches in.)

Hint: The last entry in the table (Direct Control Special Function 0.040) simulates an RF overload condition.

Table 8F-31. Levels on Various ICs, √9 Step 1

|                                    |                         |                        |                | Level          | (TTL) at      | Pin on A                | 15 IC                  |               |              |                       |

|------------------------------------|-------------------------|------------------------|----------------|----------------|---------------|-------------------------|------------------------|---------------|--------------|-----------------------|

| Direct Control<br>Special Function | U7-14<br>U10-1<br>U11-1 | U7-3<br>U10-2<br>U11-2 | U10-5<br>U11-4 | U10-3<br>U10-4 | U8-1<br>U11-3 | U8-2<br>U11-5<br>U11-10 | U8-3<br>U10-6<br>U11-9 | U7-5<br>U11-6 | U7-7<br>U8-4 | U2-2<br>U7-4<br>U8-13 |

| 0.047                              | L                       | L                      | L              | L              | L             | Н                       | L                      | L             | Н            | L                     |

| 0.045                              | L                       | L                      | Н              | L              | L             | н                       | Н                      | Н             | L            | L                     |

| 0.043                              | L                       | н                      | L              | Н              | L             | н                       | Н                      | L             | L            | Н                     |

| 0.041                              | L                       | н                      | Н              | ( н            | L             | Н                       | Н                      | H             | L            | L                     |

| 0.046                              | ( н                     | L                      | L              | Н              | L             | Н                       | н                      | L             | L            | Н                     |

| 0.044                              | Н                       | L                      | н              | н              | L             | Н                       | н.                     | н             | L            | L                     |

| 0.040                              | Н                       | Н                      | Н              | Н              | н             | L                       | Н                      | L.            | L            | Н                     |

|                                 |                       | L                     | evel (TTI             | L) at Pin     | on A15 (      | C            |              | Level (            | TTL) at            |

|---------------------------------|-----------------------|-----------------------|-----------------------|---------------|---------------|--------------|--------------|--------------------|--------------------|

| Direct Control Special Function | U4-2<br>U7-1<br>U8-11 | U5-2<br>U7-13<br>U8-9 | U1-2<br>U8-5<br>U11-8 | U2-6<br>U8-12 | U4-6<br>U8-10 | U5-6<br>U8-8 | U1-6<br>U8-6 | A15Q1<br>Collector | A15Q2<br>Collector |

| 0.047                           | L                     | L                     | L                     | Н             | Н             | Н            | Н            | Open               | L                  |

| 0.045                           | L                     | L                     | Н                     | Н             | н             | н            | L            | L                  | Open               |

| 0.043                           | L                     | L                     | н                     | L             | н             | Н            | L            | L                  | Open               |

| 0.041                           | н                     | L                     | Н                     | Н             | L             | Н            | L            | L                  | Open               |

| 0.046                           | н                     | L                     | Н                     | L             | L             | н            | L            | L                  | Open               |

| 0.044                           | L                     | н                     | Н                     | Н.            | Н             | L            | L            | L                  | Open               |

| 0.040                           | L                     | н                     | L                     | L             | н             | L            | Н            | Open               | L                  |

2. Key in the Direct Control Special Functions indicated in Table 8-13. For each setting, check the pins on the ICs listed.

Hint: Pins 3 and 5 of A15U3 should be open when pins 2 and 6 respectively are high and TTL low when pins 2 and 6 are low.

**Table 8F-13.** Levels at Various ICs, √9 Step 2

| Direct Control   |   | Level (TTL) at Pin on A15U6 |          |      |        |        |      |         | Level (TTL) at |  |  |

|------------------|---|-----------------------------|----------|------|--------|--------|------|---------|----------------|--|--|

| Special Function | 1 | 2                           | 3        | 6    | 10     | 8      | 11   | A15Q3-c | A15Q4-c        |  |  |

| 0.030            | L | Н                           | Н        | Ĺ    | Н      | Н      | L    | Open    | L              |  |  |

| 0.032            | Н | Н                           | L        | Н    | Н      | L      | Н    | j L     | Open           |  |  |

| •                | н | Н                           | L        | Н    | L      | Н      | L    | Open    | L              |  |  |

|                  | * | Mome                        | entarily | grou | nd pin | 2 of A | 1506 | A.      |                |  |  |

# **SERVICE SHEET 5**

#### **Assemblies**

- A17 Input Mixer

- A18 IF Amplifier

- S4 LO Input Switch (Option Series 030)

### **Principles of Operation**

#### General—A17 Input Mixer Assembly

The Input Mixer Assembly down-converts the input signal to an intermediate frequency (IF). For input signals above 2.5 MHz, the IF is equal to the LO frequency minus the signal frequency. The IF is normally 1.5 MHz for frequencies above 10 MHz and 455 kHz for frequencies between 2.5 and 10 MHz. Below 2.5 MHz the input signal passes directly through the Mixer into the IF Amplifier without down-conversion. For the Tuned RF Level measurement mode only, the 455 kHz IF is always used and measurements are not made below 2.5 MHz.

The Input Mixer Assembly contains the Mixer, LO Amplifier, and two IF filters (a 455 kHz Bandpass Filter and a 4 MHz Low-Pass Filter). The 4 MHz Low-Pass Filter is followed by a 2.5 MHz Low-Pass Filter in the AM Demodulator Assembly which determines the frequency response of the 1.5 MHz IF (see Service Sheet 8).

### **LO Amplifier**

The input to the LO Amplifier is a 1.25 to 1301.5 MHz signal which comes from the LO Divider Assembly (see Service Sheet 17). The amplifier has a gain of approximately 10 dB and drives the L port of the Mixer (U1) at about +10 dBm. The amplifier has two stages, stripline transistors Q4 and Q6, which are actively biased by Q5 and Q7 respectively. Using Q4 and Q5 to illustrate the biasing, notice that for dc levels the emitter of Q5 is connected directly to the collector of Q4. (L3 is an RF choke.) The base of Q5 is fixed at the voltage determined by voltage divider R1 and R2. The emitter of Q5 is normally a junction drop above this. The collector of Q5 is the source of dc base current for Q4. Changes in the collector voltage of Q4 alter the collector current of Q5, which regulates the collector voltage of Q4.

The gain of each stage is inversely proportional to the total emitter resistance and directly proportional to the collector load. C3 increases the gain slightly at high frequencies.

#### Mixer

Mixer U1 is a single-balanced type (that is, signals at the L port are balanced out at the R and I ports, but signals at the R port are not balanced at the I port). This permits low-frequency input signals to pass into the IF without down-conversion. The LO signal is coupled into the Mixer by U1T2. IF is coupled out from the center tap of the same transformer. U1C1 is the first element of the IF filters that follow. U1T1 optimizes the impedance seen by the IF Amplifier. The Input Pad ahead of the Mixer's R port improves the flatness over the wide range of input frequencies by presenting a constant impedance to the IF at the R port. The Limiter adds protection to the Mixer.

#### IF Filters (2305A to 2530A)

The 455 kHz Wide Bandpass Filter has seven poles and a 3 dB bandwidth of 200 kHz. L8 is adjusted for best passband flatness to minimize incidental AM (AM generated in the IF as the result of FM). L11 is adjusted primarily for best phase linearity vs. frequency to minimize FM distortion generated in the IF. The filter is switched in by Q3 and Q1 which forward-bias CR3 and CR6 when the output of U2B goes low. This also turns on DS1.

#### NOTE

In the Tuned RF Level measurement mode, a second 455 kHz IF bandpass filter is inserted into the IF path. This filter has a bandwidth of 30 kHz. (See Service Sheet 6.)

The 4 MHz Low-Pass Filter has three poles (2305A to 2326A) or five poles (2328A to 2530A). It is switched in by Q2 which forward-biases CR4 and CR5 when U2A goes low. Control of the filters is via the LO Control Assembly (see Service Sheet 21).

#### IF Filters (2535A and Above)

The down-converted (IF) signal from the Input Mixer is filtered by the three-pole, 4 MHz Low-Pass Filter 1. (U1C2 in the Input Mixer is the first reactive component of the filter.) When the 455 kHz IF is selected, C32 is switched in (by Q13 turning on CR8 and CR9) to improve the conversion efficiency of the Input Mixer for low-frequency input signals. The IF is then amplified by the First IF Amplifier. The amplifier has a gain of 5 to the input of Q9 (the input to the 455 kHz Wide Bandpass Filter) and 2.3 to the input of Q8 (the through-path). C18, R13, and L7 add a slight slope to the IF frequency response to compensate for slope in the 4 MHz Filters 1 and 2.

Transistor Q12B controls the routing of the IF to the 455 kHz Wide Bandpass Filter or the through path. When Q12B goes on, Q12C goes on and Q12D goes off. Q12C forward-biases CR3 and CR4, activates Q9 and Q1, and switches the 455 kHz Wide Bandpass Filter in. At the same time CR5 and Q8 go off and switch the through-path out. This also turns on DS1. Control of the filters is via the LO Control Assembly (see Service Sheet 21).

The seven-pole, 455 kHz Wide Bandpass Filter has 3 dB bandwidth of 200 kHz. L8 is adjusted for best passband flatness to minimize incidental AM (AM generated in the IF as the result of FM). L11 is adjusted primarily for best phase linearity vs. frequency to minimize FM distortion generated in the IF.

#### NOTE

In the Tuned RF Level and Selective Power (Option Series 030) measurement modes, a second 455 kHz IF bandpass filter is inserted into the IF path (a different filter for each mode). For Tuned RF Level, this filter has a bandwidth of 30 kHz. (See Service Sheet 6.) For Selective Power measurements, the filter bandwidth depends on the particular measurement mode and option installed.

The IF is routed to the A72 IF Channel Filter Assembly through the Second IF Amplifier, which has a gain of 2.8 at the output to J4 and unity gain at the output to Q1. The IF is also routed through 4 MHz Low-Pass Filter 2 on to the A18 IF Amplifier Assembly. The 4 MHz Low-Pass Filter 2 has three poles.

#### General—A18 IF Amplifier Assembly

The signal from the Input Mixer, whether down-converted or not, is amplified by the IF Amplifier. The amplifier is a low-noise type with 33 dB of gain and a phase compensation network to reduce FM distortion. The IF Amplifier has three stages.

#### IF Input Amplifier

The first stage, Q7 and Q5, is low noise and has 20 dB of gain. An active input impedance, the result of feeding signal back to the input through R6, generates a lower source noise than would be generated by a strictly passive resistance. The input impedance is essentially equal to R6 divided by the amplifier gain. The gain is approximately R9 divided by R7.

### **Inverting Amplifier**

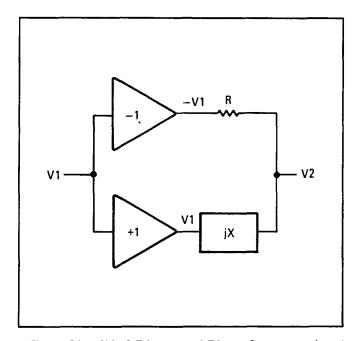

The second stage is a unity-gain amplifier with a phase-shift characteristic that can be adjusted to compensate for phase shifts generated in the 1.5 MHz IF system. This compensation improves FM distortion. The IF shape can also be adjusted to minimize incidental AM.

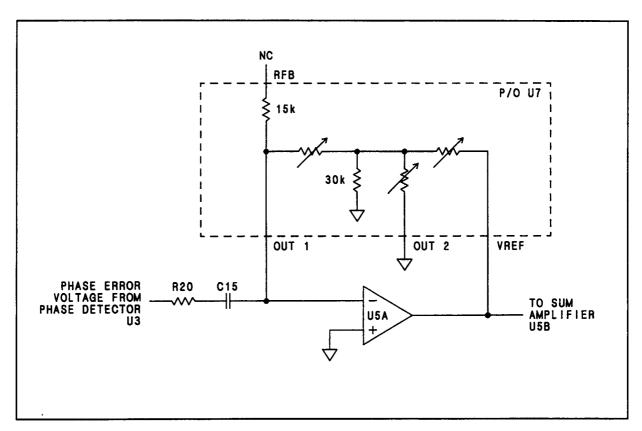

A simplified diagram of this stage is shown in Figure 8F-8. Q1 is shown as an amplifier with a gain of -1, Q2 with a gain of +1. The voltage gain for the circuit is

$$\frac{V_2}{V_1} = \frac{R - jX}{R + jX}.$$

which has a constant magnitude (+1) and a variable phase shift. The impedance jX is formed by L1, L2, C15, and C16. R is formed by the combination of R17, R23, and R24. R is fine adjusted by R23 for optimum phase shift (minimum FM distortion) at 1.5 MHz. R19 fine adjusts the gain of Q1 for best flatness (minimum incidental AM) at 1.5 MHz.

Figure 8F-8. Simplified Diagram of Phase Compensation Amplifier

### **IF Output Amplifier**

The third stage is a 13 dB amplifier which drives the AM Demodulator. Its gain is approximately one plus R29 divided by R27.

### **Troubleshooting**

#### General

Procedures for checking the Input Mixer and IF Amplifier Assemblies are given below. The circuits to check are marked on the schematic diagram by a hexagon with a check mark and a number inside, for example,  $\sqrt{3}$ . In addition, any points outside the labeled area that must be checked are also identified. Fixed signals are also shown on the schematic inside a hexagon, for example, (+1.9 TO + 2.1 VDC). Extend the board assemblies and their input and output cables where necessary to make measurements.

Tighten SMC connectors to 0.6  $N \cdot m$  (5 in lb). Hand tightening of connectors is insufficient. Hand-tightened connectors can work loose and cause reduced performance, malfunctions, or damage to the instrument.

### **Equipment**

| Oscilloscope      | HP 1740A      |

|-------------------|---------------|

| Signal Generator  | HP 8640B      |

| Spectrum Analyzer | HP 8559A/182T |

| Test Probe        |               |

| Voltmeter         | HP 3455A      |

### **LO Amplifier General Check**

#### NOTE

This test checks only the LO Amplifier at a low frequency but will easily localize a catastrophic failure.  $\langle \sqrt{2} \rangle$  LO Amplifier Check is more thorough and will detect more subtle failures; however, more time and equipment are required.

- 1. Key in 5 and press MHz to set the LO to 5.455 MHz.

- 2. Connect a high-impedance oscilloscope to the base of A17Q4. The waveform should be a square wave with a period of approximately 180 ns and an amplitude of 0.5 Vpp or greater excluding ringing.

- Hint: If the signal is faulty, check the output from the A19 LO Divider Assembly (see Service Sheet 17).

- 3. Connect the oscilloscope to the collector of A17Q4. The waveform should be a square wave of 1.2 Vpp or greater excluding ringing.

- 4. Connect the oscilloscope to the collector of A17Q6. The waveform should be a square wave of 1 Vpp or greater excluding ringing overshoot on the falling edge.

# **√2** LO Amplifier Check

#### NOTE

To check for a catastrophic failure of the LO Amplifier, use the (1) LO Amplifier General Check above.

- 1. Unplug A17U1 Mixer. Gently pry it from its socket with a screwdriver blade.

- 2. Set the spectrum analyzer to measure a +20 dBm, 0 to 1400 MHz signal. Connect its input to pins 8 and 9 of the Mixer socket using the test probe. The probe center goes on pin 9.

- 3. Key in 57.0 SPCL to cause the LO to sweep sequentially across bands DBLR through 3. The LO signal should sweep slowly from above 1300 MHz to below 40 MHz. The sweep will occur over five bands. As the low end of a band is reached, the sweep will stop, jump up slightly in frequency, then continue to sweep. Throughout the sweep, the fundamental of the LO should be between +7 and +15 dBm.

Hint: A faulty level may also be the result of a faulty output from the A19 LO Divider Assembly. Hint: The sweep can be halted by pressing the SPCL key. Use manual tune to manually set the LO frequency.

- 4. Set the spectrum analyzer to view a 0 to 40 MHz signal.

- 5. Key in 56.0 SPCL to cause the LO to sweep sequentially across bands 4 through 8. The LO should sweep slowly from above 50 to below 1.25 MHz in the manner described in step 3 above.