## HEWLETT-PACKARD JOURNAL

Technical Information from the Laboratories of Hewlett-Packard Company

## Contents:

### SEPTEMBER 1982 Volume 33 . Number 9

- Oscilloscope Measurement System Is Programmable and Autoranging, by William B. Risley More than an oscilloscope, this new instrument is computer-controllable and systems compatible.

- Designing the Oscilloscope Measurement System, by Russell J. Harding, Monte R. Campbell, William E. Watry, John R. Wilson, and Wilhelm Taylor The microprocessor brings the new dimension of programmability to the oscilloscope.

- Development of the 1980A/B Oscilloscope Measurement System, by Zvonko Fazarinc and William B. Risley From Hewlett-Packard Laboratories to HP's Colorado Springs Division, here are the people who developed the 1980A/B.

- Digital Waveform Storage for the Oscilloscope Measurement System, by Eddie A. Evel and Robert M. Landgraf With this option, the oscilloscope measurement system can digitize, store, and transmit waveform data and receive waveform data from a computer for display.

- Putting the Measurement System on the Bus, by Michael J. Karin The oscilloscope is a latecomer to the world of interface-bus-compatible instruments.

- Mechanical Design of the Oscilloscope Measurement System, by John W. Campbell Except for one printed circuit board, the same parts go into the two possible configurations.

- A High-Performance Bipolar Integrated Circuit Process, by Albert S. Wang and Irene V. Pecenco Transistor gain-bandwidth products can be as high as eight gigahertz.

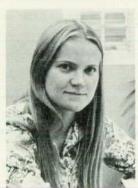

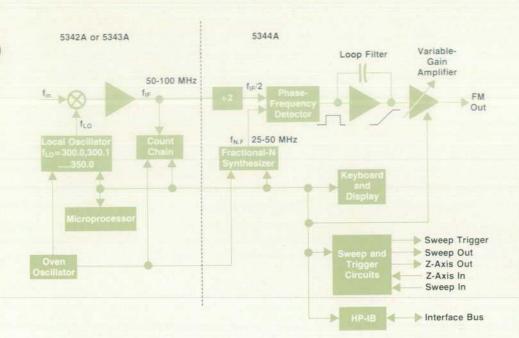

- Synthesizer Accuracy for Unsynthesized Microwave Sources, by V. Alan Barber Now signal generators and sweep oscillators can have the accuracy and stability of a synthesizer.

#### In this Issue:

Go into any circuit design lab and on just about every bench you'll find an oscilloscope, its glowing blue or green eye displaying one or a group of waveforms that the owner of the bench considers important. Designers spend hours staring at these fluorescent eyes, fine tuning their circuits until those waveforms look exactly the way they should. The oscilloscope's ability to display repetitive waveforms makes it a ubiquitous and essential instrument not only in the R&D lab, but also in the service engineer's tool kit and in production test areas, where it's been something of an anomaly. Often the oscilloscope is the only instrument in an automated production test system that has to be set up manually and can't talk to the computer.

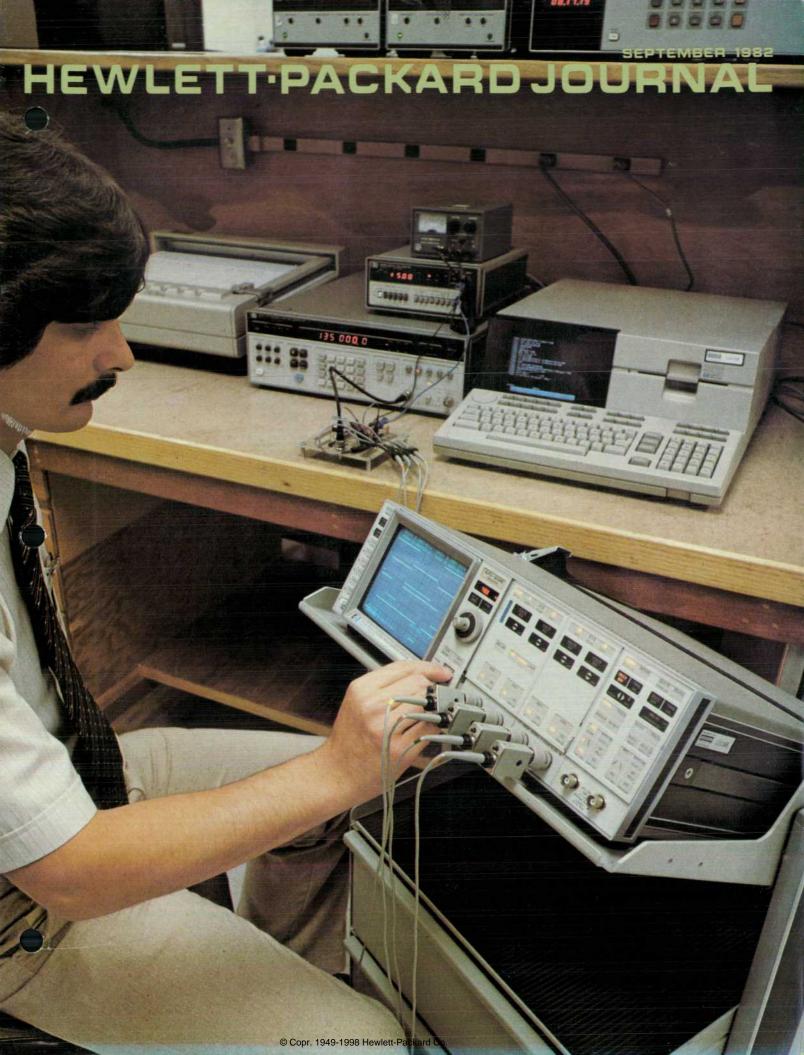

Now that can change. Our cover subject this month is an oscilloscope measurement system that can set itself up automatically or at the direction of a computer. The 1980A/B (it comes in a low, wide B model and a taller A model) can talk to the computer over the HP Interface Bus, HP's version of an industry standard communication method for programmable instruments. This programmable scope can capture and display a signal without any knob-twisting by the operator—that's called Autoscope. With its digital waveform storage option, it can take, store, and display samples of a waveform, transmit those samples to a computer, and get samples back for display along with messages for the operator. Another option, a plot/sequence memory, lets the operator initiate a predefined sequence of measurements by pushing a single button on a probe.

You'll find the story of the 1980A/B design on pages 3 to 26. Our cover photo shows a 1980B talking to an HP 9826A Computer in a lab bench test setup at Fairchild Camera and Instrument Corporation in Mountain View, California. Our thanks to Fairchild for their cooperation.

In the world of microwave frequency sources, the big three are signal generators, sweep oscillators, and synthesizers. Synthesizers offer the ultimate in frequency accuracy and stability and are generally more expensive than the others. The article on page 30 describes a new instrument, Model 5344S Source Synchronizer, that gives sweepers and signal generators the accuracy of a synthesizer, turns signal generators into sweepers, at least for narrowband sweeps, and greatly improves the accuracy of a sweep oscillator's wide sweeps by means of a procedure called "lock and roll." For much less than the cost of a synthesizer, the owner of a sweeper or signal generator can have synthesizer accuracy, some new capabilities, and a general-purpose microwave counter (part of the 5344S). It's like getting the best of two worlds for the cost of one and a half.

Many HP products contain proprietary HP integrated circuits as well as commercially available ICs. A variety of processes are used to produce these HP ICs. The article on page 27 describes one such process, a new high-performance bipolar process being developed by HP's Integrated Circuits Division in Santa Clara, California. Other processes will be described in upcoming issues.

-R. P. Dolan

Editor, Richard P. Dolan • Associate Editor, Kenneth A. Shaw • Art Director, Photographer, Arvid A. Danielson • Illustrator, Nancy S. Vanderbloom Administrative Services, Typography, Anne S. LoPresti, Susan E. Wright • European Production Supervisor, Henk Van Lammeren

# Oscilloscope Measurement System Is **Programmable and Autoranging**

This new concept in oscilloscopes is a significant aid to measurement productivity.

by William B. Risley

N THE DESIGN, manufacture, and service of electronic equipment no other instrument is so ubiquitous as the oscilloscope. Early in the technical curricula, students are introduced to the analysis of time-variant phenomena. The display of signal amplitude as a function of time provided by an oscilloscope has become firmly established in electrical engineering because of its ability to provide a faithful reproduction of the electrical activity at a given circuit node. So important is this method of analysis that oscilloscopes have come to accommodate a wide range of signal types. Signals may vary by five orders of magnitude in amplitude and by nine orders of magnitude in duration and still be meaningfully analyzed with a single instrument. Because of their range of application, oscilloscopes have become complex instruments, able to move facilely from one situation to another.

The thrust of today's measurement trends is towards higher levels of automation and the increased use of data bases. Most oscilloscopes, however, are not computercontrollable or systems compatible. Hewlett-Packard's response to this lack is a new breed of oscilloscope, Model 1980A/B Oscilloscope Measurement System, Fig. 1.

#### Computer Architecture

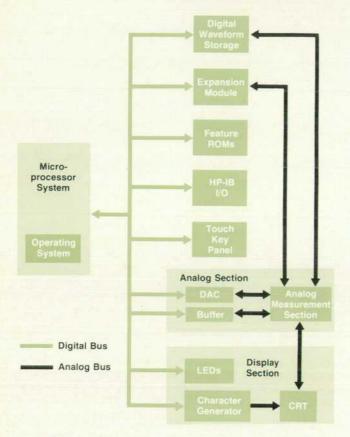

The 1980A/B Oscillosope Measurement System is an automated HP-IB\*-compatible instrument that makes significant contributions to the viewing, measuring, and processing of time-domain waveforms. With its microprocessor-based computer architecture, the 1980A/B is a multifunction, multifaceted instrument. Internally, it is divided into eight functional blocks that interface with each other by means of a bus structure (Fig. 2). This extensive digital control permits such features as an easy-to-use front panel, autoranging, complete programmability, digital waveform storage, and hardware and firmware expandability. Unlike other oscilloscopes, the 1980A/B's innovative front panel has a single rotary control. Color-coded touch keys arranged in a logical hierarchy are used for setting up

\*HP-IB is Hewlett-Packard's implementation of IEEE Standard 488 (1978).

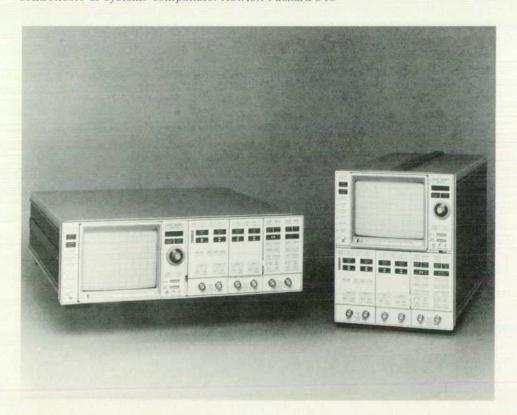

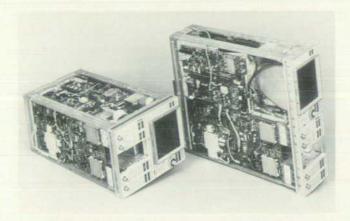

Fig. 1. Designed for use in automated systems, Model 1980A/B Oscilloscope Measurement System is compatible with the HP-IB (IEEE 488). Among its features are Autoscope, which gives the user a display rapidly and automatically. and front-panel calibration. Options include digital waveform storage and measurement sequence memory. (r) Model 1980A. (I) Model 1980B.

Fig. 2. Simplified 1980A/B architecture

the instrument, while the rotary control is used to adjust variable functions.

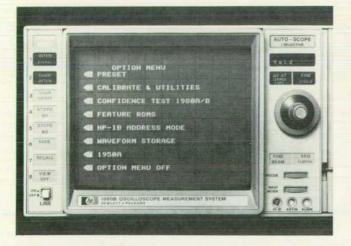

The display section permits the operator to interact with the instrument through the CRT, which displays both real-time and digitally stored waveforms, scale factors, and advisory messages. The display section includes an option menu, softkeys, eight nonvolatile save/recall registers, and intensity controls. Standard option menus include automatic instrument preset, front-panel calibration, automatic delay and input amplifier balancing, confidence tests to verify operation, and front-panel setting of the HP-IB address and operating modes. Menus are automatically updated as hardware and firmware are added.

When an invalid operation is attempted, advisory messages are momentarily displayed on the CRT. Invalid measurements are impossible using the 1980A/B, and the advisory messages help the operator use the instrument to its capacity. Error codes, displayed on light-emitting-diode (LED) lamps, provide information about internal malfunctions.

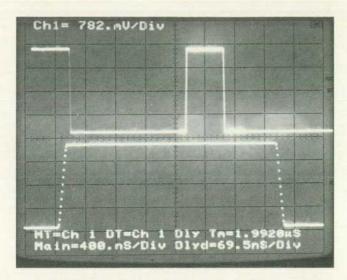

In its basic configuration, the 1980A/B offers two 100-MHz analog measurement channels with 2-mV/div deflection factors, two independent and direct 5-ns/div sweeps, main or delayed trigger view, delta-time and delta-voltage measurements, and a multitude of automated features including Autoscope, which allows the user to obtain a display rapidly without adjusting individual controls, and front-panel calibration, which lets the user calibrate the instrument in about 25 minutes by following instructions displayed on the CRT.<sup>1</sup>

Feature ROMs can be added to expand resident programmed firmware measurement capabilities. For example, an optional Plot/Sequence ROM, Model 19811A, lets the user program as many as 25 front-panel keystrokes for each front-panel input; each stored key sequence can later be activated using a probe pushbutton.

Remotely programmed operation is provided through a standard HP-IB port that interfaces with all functional blocks through the internal bus. All measurement parameters can be programmed, and touch key operation, CRT instruction display, and installed-enhancements addressing are also programmable. Touch key status, measurement results, and digitally stored waveforms may be sent to a computer/controller for processing.

With the HP-IB interface, the 1980A/B can be combined with other HP-IB-compatible instruments to form a completely automated test system. Because the 1980A/B is fully programmable, test routines can be established, stored, and used repeatedly.

With the addition of a 19860A Digital Waveform Storage Option (see article, page 15), the 1980A/B can be used as a complete test system for time-domain measurements. With the 19860A installed, repetitive events to 100 MHz or single-shot events to 5 kHz can be captured, displayed, and sent to a computer via the HP-IB for analysis. This results in complete answers without operator intervention. For example, a series of standard signals may be digitized and stored in a computer as a reference library for automatic testing. As tests are performed, signals may be automatically compared in software.

#### Summary

The 1980A/B is a timely response to today's economic, measurement, and technological trends. The concept of combining a broad range of oscilloscope capabilities, full programmability, and digital waveform storage into a highly flexible, interactive measurement system provides a new tool for computer-aided applications. This instrument is now at work in many systems in design, engineering, and production test.

#### Reference

P. Austgen, W. Watry, and M. Karin, "Software-based design automates scope operations," Electronics, March 10, 1981, pp. 181-188.

#### William B. Risley

Currently oscilloscope R&D manager of HP's Colorado Springs Division, Bill Risley was project and section manager for the 1980A/B. He joined HP's oscilloscope lab in 1972 as a design engineer on the 1722A Oscilloscope. He holds an MSEE degree from Colorado State University and a BA degree in physics from Princeton University. Away from HP, Bill keeps busy with his family—he has two sons—church activities, and gardening and foresting on his twenty acres in Black Forest, Colorado.

# Designing the Oscilloscope Measurement System

by Russell J. Harding, Monte R. Campbell, William E. Watry, John R. Wilson, and Wilhelm Taylor

N THE 1980A/B Oscilloscope Measurement System, the microprocessor brings the added dimension of programmability to the oscilloscope, making automatic waveform measurements possible. Rise time, voltage, width, and delay measurements and event detection can be attained through firmware and software.

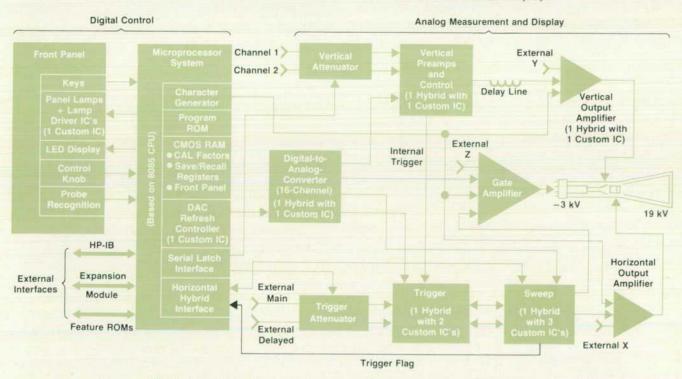

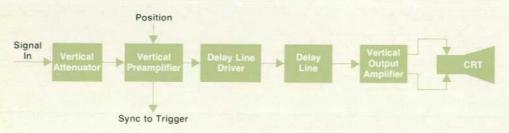

The architecture of the 1980A/B is shown in Fig. 1. The hardware consists of a digital control section, an analog measurement and display section, and the interfaces between these sections.

The digital control section is based on the 8085 microprocessor and associated chip set. The 8257 programmable DMA controller and the 8275 programmable CRT controller chips generate characters for the CRT readout. The 8355 I/O ROMs control switch functions such as range selections and channel on/off. The 8155 timer is used by various elements of the firmware, such as the control knob section, to time events. The HP-IB\* section uses the 8291 HP-IB talker/listener chip, which is tied to the 8085 bus. The expansion module is also tied to the 8085 bus.

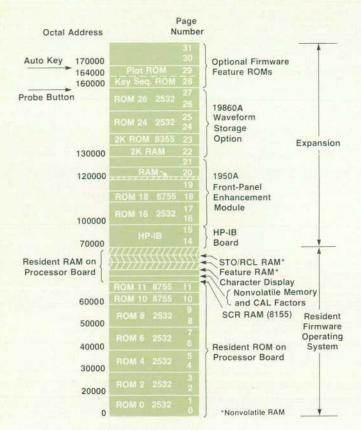

Fig. 2 shows the fixed allocation of the possible 64K bytes of addressable memory locations in the firmware operating system. The firmware that controls the basic 1980A/B sys-

\*HP-IB is Hewlett-Packard's implementation of IEEE standard 488 (1978).

tem is contained in the lower 32K of available address space, while the upper address space is dedicated to system expansion. All feature ROMs and options can call upon utilities and subroutines that reside in the main operating system.

All oscilloscopes contain vertical, horizontal, trigger, and display systems. In the 1980A/B, these are in the analog section. Because the 1980A/B is microprocessor-controlled, the horizontal, vertical, and trigger systems are programmable and are designed to make full use of the microprocessor. This requires that these systems be somewhat different from their conventional, nonprogrammable predecessors.

The 1980A/B's digital and analog sections are coupled through serial latch packs, a horizontal hybrid interface, a 16-channel custom DAC (digital-to-analog converter), and a custom DAC refresh controller. Hewlett-Packard designed the DAC refresh controller IC to provide the DAC with a continuous update of state information. DAC numbers between 0 and 2999 are sequentially fetched from 16 fixed locations in memory and serially transferred to the DAC by the DAC refresh controller independently of the 8085 processor. The DAC then translates the numbers to analog voltages, which control analog functions such as sensitivity, position, and trigger levels. The DAC hybrid also serves as the decoder for the LED displays.

Fig. 1. 1980A/B Oscilloscope Measurement System simplified block diagram.

Fig. 2. 1980A/B memory allocation.

#### Adapting the Analog Section

As the first step in making a programmable oscilloscope measurement system, the functions switched or controlled mechanically from the front panel of a conventional oscilloscope had to be electronically switched or controlled so that the microprocessor could control these functions. In the 1980A/B, the microprocessor has three ways of controlling the instrument: two are by switching and the other is analog. One of the switching sources originates in the microprocessor control system, and a 56-bit serial data bus distributes it throughout the instrument. The serial data bus is made up of latching shift and store registers that interface the bus to the various microprocessor-controlled circuits. The second switching control source originates in the horizontal section of the 1980A/B and controls functions that have to be switched in real time (e.g., channel selection for alternate or chop display modes). The third source, the microprocessor-controlled DAC, controls analog functions such as vertical position.

#### Horizontal System

An oscilloscope's horizontal system, which functions as a time scaler, generates main and delayed sweeps, delay time, and the associated control signals needed for viewing a range of time bases. In conventional oscilloscopes, these functions are restricted by the delay time generator, and delay time is achieved with an analog comparator. One input of this comparator is the main ramp voltage, and a variable resistor attached to the front-panel delay control knob controls the other input. As the main ramp voltage

changes, causing the CRT beam to move across the screen, the delayed sweep is enabled by the comparator. The delayed sweep begins immediately if the delayed sweep is in auto mode, or at the next delayed trigger if the delayed sweep is in the trigger mode. Delay times are varied by varying the comparator voltage. Since delayed sweeps are used to expand sections of the main sweep, they must sweep faster than the main sweep. Delayed sweeps are normally terminated at the end of the main sweep if not already completed.

The 1980A/B's horizontal system differs from those in conventional oscilloscopes in that its delay time generator is programmable and the main and delayed sweeps are independent. These two differences effectively eliminate the restrictions found in conventional horizontal systems, and they are possible because of the structure of the horizontal system and how it interacts with the microprocessor. Delay times from 0 to 9.999999999 seconds can be programmed via the HP-IB or from the front panel, and both main and delayed sweeps can be independently programmed from 5 ns/div to 1 s/div. With the 1980A/B, delay times are no longer dependent on the main sweep, and delayed sweep speeds are no longer restricted by main sweep speeds.

The advantages realized from this independent control become apparent while operating the 1980A/B manually. For example, it is possible to change the main sweep to achieve a more convenient display and not affect the delay time or delay sweep speed. This is particularly helpful when viewing both main and delayed sweeps in the dual mode.

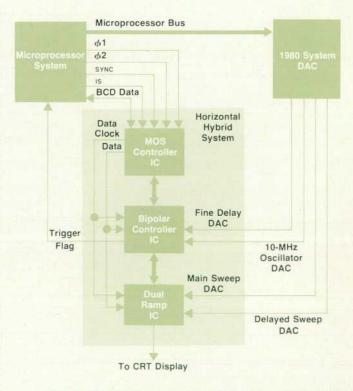

**Fig. 3.** The 1980A/B horizontal hybrid system. The system DAC has 16 channels. Four of these are used by the horizontal system.

The absence of interaction between display functions simplifies not only manual control but also HP-IB control. Measurements over the HP-IB can be made using a one-bit flag that looks for trigger events during programmed time windows. This is called the trigger flag. Time windows for the trigger flag are established by the delayed sweep gate, which is at a higher logic level while the delayed ramp is running. Therefore, the width of the time window is determined by the delayed sweep speed, and the start of the time window is set by the delay time. These are independent parameters.

The heart of the 1980A/B's horizontal system is the horizontal hybrid circuit. Three custom integrated circuits—the dual ramp IC, the bipolar controller IC, and the MOS controller IC—and an assortment of resistors and capacitors are all contained in this thick-film hybrid (Fig. 3). Each IC represents a major functional area.

Independent main and delayed sweeps are generated on the dual ramp IC. The ramp circuitry on this IC is identical for both main and delayed sweeps, and they share a common output buffer and beam blanking logic. Because the main and delayed time bases have the same circuitry and are programmed identically, they perform identically and are truly independent.

Sweep speeds in the 1980A/B are continuously variable, unlike the traditional 1, 2, 5 sequence of discrete settings (e.g., 1  $\mu$ s/div, 2  $\mu$ s/div, 5  $\mu$ s/div). Sweep ramp voltages are generated by charging a fixed capacitor with a constant-current source. In the 1980A/B, the size of this capacitor is digitally programmed while the current source is controlled by the 1980A/B's system DAC. Capacitor size establishes the exponent of the sweep speed and the system DAC determines the mantissa. For example, to set a sweep speed of 6.23  $\mu$ s/div, the capacitor size is programmed for the 1.0- $\mu$ s-to-9.99- $\mu$ s range. Then the DAC voltage, which controls the current sources, is programmed to establish the proper current. Using this method, sweep speeds are always calibrated, even at 6.23  $\mu$ s/div.

# Custom Microcircuits Make the 1980A/B Possible

The 1980A/B Oscilloscope Measurement System mainframe uses 17 custom monolithic ICs distributed among five custom hybrid circuits and six packaged parts. The technologies employed include a high-frequency process, a high-density bipolar LSI process, an N-channel MOS process, and both thin-film and thick-film hybrid processes.

The high-frequency process is a shallow planar process which produces transistors with typical cutoff frequencies ( $f_T$ ) of 2.2 GHz and subnanosecond switching speeds. Base insert and collector wall diffusions are included to reduce base and collector resistance to achieve the high performance. Tight alignment tolerances and 2.5- $\mu$ m minimum features provide small devices but comparatively limited complexities.

The LSI process is similar but has a higher level of complexity. This process has a thicker epitaxial layer and deeper base and emitter diffusions, but eliminates the base insert and collector wall diffusions, and so has fewer masking operations and relaxed design rules. Typical LSI transistor cutoff frequencies are about 1 GHz, resulting in switching speeds and propagation delays of about 1 ns.

Other custom microcircuit technologies used include a thin-film tantalum-nitride resistor network in the digital-to-analog converter (DAC) hybrid and several high-density N-channel MOS ICs used in both the DAC and horizontal hybrids to implement the control logic functions.

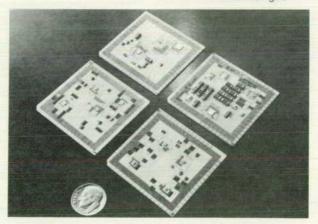

Thick-film hybrid technology is used to interface the various custom ICs with commercially available ICs and precision resistors and capacitors. The circuitry is partitioned into four major hybrids (see Fig. 1): the DAC, the vertical preamplifier, the trigger circuit, and the horizontal system. Using thick-film hybrids and custom ICs, the circuit density of the 1980A/B is at least an order of magnitude greater than an equivalent printed circuit board implementation. Also, a significant high-frequency performance advantage was realized thanks to the small conductor trace widths, the laser-trimmed 1% resistors, and the short trace lengths between adjacent components. Without the performance advantage of the high levels of integration and circuit density achieved, the 1980A/B would not have been a feasible project. Early in the development program it was clear that manufactur-

ing technologies would have to be improved to achieve costeffective production of these hybrids. Since each hybrid requires about 90 wire bonds, an automated wire bond process was developed. To achieve consistent, well controlled assembly of the add-on components, an automated hybrid assembly process was developed. A new hybrid test system was designed to facilitate rework. Because most electronic failures are recurrent and computers are extremely efficient at repetitive problems involving memory work, a computer was trained to troubleshoot hybrids by entering known solutions to specific failure modes. The computer compares symptoms of the hybrid under test with the history of all past failures. It then chooses the best cure for the particular failure mode. If no correlation is found, it will request aid from the technical staff. Since there is an on-going interface between the computer and the technical staff, the failure history file is continually updated and a complete record of past failures can be accessed.

> -William Duffy -John Meredith -Mike McTique

Fig. 1. The four major hybrids of the 1980A/B. From top, clockwise, the horizontal system, digital-to-analog converter (DAC), trigger circuit, and vertical preamplifier.

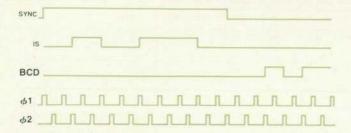

Fig. 4. The MOS controller IC controls the transfer of data from the microprocessor to the horizontal system. Data is transferred synchronously over three serial data lines—SYNC, IS, and the BCD line—using two external clocks, φ1 and φ2.

A startable 10-MHz oscillator, delay timer, and real-time control are on the bipolar controller IC. The startable oscillator generates an accurate 100-ns (10-MHz) delay clock which is synchronized to the main trigger. Establishing the timing of the delay clock and main trigger allows the delay time to be counted digitally, and this decouples the delay time from the main sweep. For delay times less than 100 ns, an independent fine delay ramp and comparator are used. Fine delays are controlled by varying the initial charge on a fixed capacitor. A constant-current source then discharges the capacitor, generating the fine delay times ranging from 0 to 99.9 ns.

Digitally counting delay times rather than using the analog comparator method of conventional oscilloscopes led to two special features of the 1980A/B: digital delay and automatic delay time calibration. The delay trigger clock replaces the 10-MHz startable oscillator when the 1980A/B is in the digital delay mode. The delay trigger clock goes high each time the delay trigger source satisfies the delay trigger conditions (level and slope). Therefore, the delay time is now a function of delay trigger events. This is particularly useful in finding the nth pulse in a data string that is jittering so badly that it cannot be seen.

During automatic delay time calibration, the 10-MHz startable oscillator frequency is matched to the crystal reference that generates the microprocessor clock. The delay counter is cleared and then allowed to count the 10-MHz startable oscillator clock for a given amount of time. The resulting count is transferred to the microprocessor for evaluation. If the count does not match the expected count, then the oscillator frequency is varied, and the entire process repeated. With completely automatic calibration, the 1980A/B can calibrate its delay time whenever requested. This means that the accuracy and stability of the crystal reference can be applied to every measurement.

The third custom IC in the horizontal hybrid is the MOS controller. All communication between the microprocessor

and the horizontal system is handled through three serial data lines connecting this IC to the horizontal interface circuitry in the microprocessor system. Scope mode, coarse delay time, and main and delayed sweep ranges are transmitted over these lines. Fine delay and continuous sweep speeds are controlled via the 1980A/B's DAC system. The MOS controller IC becomes involved in real-time control by counting the holdoff time between sweeps and the upper seven BCD digits of delay time or digital delay count.

#### Programming the Horizontal System

As stated above, one way that the microprocessor communicates with the horizontal system is through the DAC. Four DAC channels to the horizontal system are available. The main sweep rate, delayed sweep rate, 10-MHz oscillator, and fine delay time DAC channels are used to make fine adjustments in the horizontal system.

The basic digital information the microprocessor transfers to the horizontal system is grouped into three major areas: scope mode, sweep mode, and delay time. As stated above, the MOS controller IC controls the transfer of this data between the microprocessor and the horizontal system. Proper management of this data requires both interrupt and noninterrupt data transfers. Data transfers with interrupt reset the horizontal system, transfer data, and then restart the system using the new data. This type of data transfer is required when changing the scope mode or sweep ranges, and in some automatic measurement applications. Noninterrupt data transfers are used for changing delay times. The horizontal system does not recognize data transferred without an interrupt until the current sweep cycle is completed.

The MOS controller IC design takes advantage of the low power dissipation inherent in dynamic MOS circuit designs. The circuit uses two external clocks,  $\phi 1$  and  $\phi 2$ . Data is transferred synchronously with these clocks through three serial data lines: SYNC, IS (instruction), and the bidirectional BCD data line. The data transfer timing is illustrated in Fig. 4. During SYNC high, the instruction line data is shifted into an instruction decoder. If no valid instruction is recognized, the horizontal system continues unaffected. When a valid instruction appears, the MOS controller accepts information on the BCD data line. The first instruction sent to the horizontal system defines the type of data transfer that will follow. That is, it says whether the next data transfer will be with interrupt or without interrupt. After the type of data transfer has been established, all subsequent transfers are that type until another instruction to change the type is received.

A third type of data transfer is used when calibrating the delay time generator. The delay time generator is calibrated

Fig. 5. 1980A/B vertical system block diagram.

by zeroing the delay counter and then allowing it to run for a predetermined length of time. The upper seven BCD digits of the delay counter are then transferred to the microprocessor via the bidirectional BCD data line. This calibration transfer is the only transfer of data from the MOS controller IC to the microprocessor; all other data transfers go in the other direction. After the microprocessor has received the seven BCD digits, it compares what it received with what it knows should have been received. The difference is used to adjust the frequency of the 10-MHz oscillator. This is repeated until the received data agrees with the expected data. The oscillator's frequency is adjusted by the microprocessor via the 10-MHz oscillator DAC channel. The microprocessor controls the oscillator's frequency by controlling the output voltage, which controls a variable capacitor in the oscillator's LC circuit.

Real-time control of the horizontal system is a coordinated effort between the MOS controller IC and the bipolar controller IC. The bipolar IC receives scope mode data from the microprocessor via the MOS controller IC. Then on a sweep-by-sweep basis, the bipolar IC operates the horizontal system in the appropriate mode. The allowable modes are channel 1 versus channel 2, single sweep, auto or triggered main sweep, auto or triggered delayed sweep, and digital delay. During each sweep cycle the MOS controller IC counts the upper seven digits of the delay time. These digits represent either 1-µs counts or, in the digital delay mode, trigger event counts. Also, at the beginning of each sweep cycle the MOS controller IC counts a 1-MHz clock to establish an appropriate holdoff time as defined in Table I. Holdoff time is required so that the sweep capacitors can discharge completely before a new sweep is started.

The 100-ns digit of the delay time is counted on the control IC. Clocking for this counter is derived from the 10-MHz startable oscillator which is calibrated using the calibration data transfer mentioned earlier. As with the scope mode, the microprocessor sends the 100-ns digit via the MOS controller IC.

Delay time is counted from the most-significant digit to the least-significant digit. For example, delays greater than 1 µs are counted first on the MOS controller IC, which counts in 1-µs steps. After digits 1 µs and greater have been counted, the bipolar IC then counts the 100-ns digits. After all digits have been counted, there remain the delay times

Table I Holdoff Format Holdoff time (clock cycles) at 1 MHz

| Required Holdoff |                                            |  |  |

|------------------|--------------------------------------------|--|--|

| Counts           | Time                                       |  |  |

| 200,000          | 200 ms                                     |  |  |

| 200,000          | 200 ms                                     |  |  |

| 2,000            | 2 ms                                       |  |  |

| 2,000            | 2 ms                                       |  |  |

| 10               | 10 μs                                      |  |  |

| 10               | $10 \mu s$                                 |  |  |

| 0                | 0                                          |  |  |

| 0                | 0                                          |  |  |

| 0                | 0                                          |  |  |

|                  | Counts 200,000 200,000 2,000 2,000 10 10 0 |  |  |

# Allowing for System Expansion

Because of the way in which the microprocessor and oscilloscope are integrated within the 1980A/B Oscilloscope Measurement System, the instrument can handle two separate hardware options and seven firmware features. Hardware options-front-panel expansion modules and a waveform storage card—add only hardware capabilities, but the firmware features are ROMs that can use existing hardware to implement new features or measurement sets. Memory space is allocated for each of these expansion modes.

With firmware, designers can create new features tailored for the 1980A/B. The HP 19811A Plot/Sequence ROM, used with the 1980A/B's probe, is an example. It allows the user to program a sequence remotely, specifying up to 25 keystrokes for each front-panel input. The sequence specified for a particular input may then be executed by pressing a button on the probe attached to that input. Possible future ROMs include preprogrammed test sequences with step-by-step instructions to the operator via the CRT character generator and without an external controller. Resident firmware does not refer to an option by name or number. Instead, identification is contained in the option's ROM. When the option menu is pressed, the mainframe checks for the existence of each option by checking a known memory location. If the option exists, then the option menu is written according to the ASCII string that resides in the option ROM and is displayed on the CRT.

Feature ROMs are accessed through the softkey menus. During the main program, all options and features are allowed to respond to any rotary control motion or front-panel keystrokes. As controller library routines are developed, it will become possible to transfer popular utility or measurement programs to the 1980A/B's side of the bus to minimize bus traffic and enhance overall performance. Feature ROMs will also allow expansion of the HP-IB command set.

The possiblilities for future expansion are extensive because the system directly or indirectly polls all enhancements and the enhancements may be either ROM or expansion modules that contain ROM. In addition, design changes within the system itself, such as substituting another type of interface for the HP-IB, are possible because of the partitioned architecture.

-William Watry

ranging from 0 to 99.9 ns. The fine delay circuits on the bipolar IC handle these delays. Fine delay times are set by the DAC. A constant-current source discharges a capacitor to generate the fine delay. The initial voltage on the capacitor is set to the fine delay DAC voltage. Then, at the appropriate time, the capacitor is allowed to discharge to ground, generating an end-of-delay-time signal.

The microprocessor controls the fine delay by controlling the fine delay DAC output voltage. The fine delay DAC has a range of 0 to +4 volts, representing approximately -25 to +125 ns of delay. The overlap allows for system calibration.

The dual ramp IC also receives data from the microprocessor via the MOS controller IC. Four bits are required by both the main and delay time bases to define their respective sweep ranges completely. Decoding these bits determines the total capacitance and current switched into the ramp circuits. Table II shows the decoding of these bits.

Note that for each total capacitance value two current sources are used. ×1 and ×10. Both current sources are

| Т     | able II |      |

|-------|---------|------|

| Sweep | Range   | Data |

|   | Da | ou<br>ata |   | Sweep<br>Speed | Ramp Capacitor* |      |         |       | Current<br>Source |

|---|----|-----------|---|----------------|-----------------|------|---------|-------|-------------------|

| 0 | 1  | 2         | 3 | time/div       | 100 μF          | 1 μF | 0.01 μF | 50 pF |                   |

| 0 | 0  | 0         | 0 | 0.1-1 s        | IN              | IN   | IN      | IN    | ×1                |

| 0 | 0  | 0         | 1 | 0.01-0.1 s     | IN              | IN   | IN      | IN    | ×10               |

| 0 | 0  | 1         | 0 | 1-10 ms        | OUT             | IN   | IN      | IN    | ×1                |

| 0 | 0  | 1         | 1 | 0.1-1 ms       | OUT             | IN   | IN      | IN    | ×10               |

| 0 | 1  | 0         | 0 | 0.01-0.1 ms    | OUT             | OUT  | IN      | IN    | $\times 1$        |

| 0 | 1  | 0         | 1 | 1-10 μs        | OUT             | OUT  | IN      | IN    | ×10               |

| 0 | 1  | 1         | 0 | 0.1-1 μs       | OUT             | OUT  | OUT     | IN    | $\times 1$        |

| 0 | 1  | 1         | 1 | 0.01-0.1 μs    | OUT             | OUT  | OUT     | IN    | ×10               |

| 1 | 0  | 0         | 0 | 5-10 ns        | OUT             | OUT  | OUT     | OUT   | ×10               |

<sup>\*</sup>There is always a 50-pF capacitor in the circuit in addition to the ones switched in.

controlled by the microprocessor via the main sweep DAC channel and the delayed sweep DAC channel. These DAC voltages can be varied continuously from their minimum to their maximum values. Therefore, the current sources are continuously variable and the 1980A/B's sweep speeds are continuously calibrated.

#### Trigger Flag

To complete the control loop needed for automated measurements, the horizontal system must be able to talk back to the microprocessor. The horizontal hybrid interface provides a method of setting sweep ranges and delay time as well as a means of reading trigger conditions (trigger flag). Trigger flag is a feedback line from the sweep hybrid to the horizontal hybrid interface on the microprocessor board. This feedback line provides a flag from the trigger circuit to the microprocessor and allows the microprocessor to control the analog section interactively. This is the only time in normal operation (i.e., not during calibration) that data is transferred from the horizontal system to the microprocessor. Trigger flag is set if a trigger event occurs during the delayed sweep. The trigger source can be selected as either main trigger or delayed trigger. Using the programmable trigger source and time windows established by the delayed sweep gate, the trigger flag tells the microprocessor if a trigger event has occurred within the programmed time window.

It is the trigger flag that takes the 1980A/B out of the realm of a microprocessor-controlled oscilloscope and into the realm of a truly automated instrument that can detect signal conditions and self-adjust accordingly. The trigger flag is an integral part of the Autoscope routine, one of the 1980A/B's most significant features. The 8085 microprocessor firmware controls virtually all internal states of the 1980A/B. Using trigger flag, the settings of certain modes and values may be altered by means of an algorithm that includes the parameters of an external signal. In this way, the 1980A/B may be set up to display an input signal automatically. This is the function assigned to the AUTO-SCOPE key.

Pressing the **AUTOSCOPE** key causes the 1980A/B to examine an input waveform, adjust its settings, and present a signal approximately three divisions high and two cycles wide on the CRT. There is also a Selective Autoscope function, which is accessed through the blue prefix key, that retains previously selected setup functions such as  $50\Omega$  inputs and trigger conditioning.

#### Vertical System

The vertical system in a conventional oscilloscope functions as an amplitude conditioner. Because an oscilloscope must handle a large range of input signals, from millivolts to tens of volts, it is necessary to attenuate incoming signals to keep them within the dynamic range of the vertical amplifier. The vertical system must also delay the incoming signal so that the leading edge of a fast-rise pulse can be displayed on the CRT. It also provides a sync pickoff from the vertical signal which allows internal triggering, and it adds a position signal to allow convenient display of the signal.

Incorporating a microprocessor into an oscilloscope does not functionally change the vertical system block diagram. Fig. 5 shows the 1980A/B's vertical system. However, some different circuit and control implementations were incorporated to accommodate programmability. The basic building blocks of the vertical system of the 1980A/B are the attenuator, the preamplifier, the delay line driver, the delay line, and the output amplifier.

The major challenge of the vertical system was the design of the attenuator switches. They had to meet all of the electrical performance requirements of their mechanical predecessors, such as low contact resistance, low leakage currents, low input capacitance, low feedthrough capacitance, and high breakdown voltage, and they also had to be programmable. Programmability added a significant new constraint because of the electronic interface required and the increase in contact life demanded of an HP-IB-controlled instrument. The attenuator in a manual oscilloscope might see 50,000 cycles in a year of service while the attenuator in a programmable unit might see well over a million cycles within the same time period.

After a number of false starts using various types of offthe-shelf relays, and considering the natural extension of programming a cam-actuated mechanical attenuator via a step motor, a custom multiple-solenoid design seemed to be

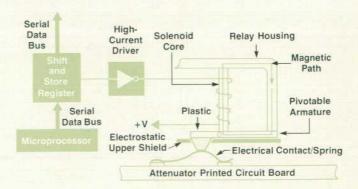

Fig. 6. Diagram of the attenuator switch, an important element of the 1980A/B's vertical system.

the right approach. Although this approach appeared simple, it did present a substantial set of problems.

Electrically, the attenuator has to provide a high-impedance (1 M $\Omega$ ) or 50 $\Omega$  termination, ac or dc coupling, ground reference, and attenuation of  $\times 1$ ,  $\times 10$ , and  $\times 100$ . This means that each attenuator needs eight contacts. Because of the space constraints of the mainframe, a dual attenuator package that includes both vertical input channels was chosen. The resulting design for a single contact is shown in Fig. 6.

The microprocessor controls the attenuator through the serial data bus. The outputs of the shift and store registers of the serial data bus interface to high-current drivers which control the individual solenoid coils. When a coil has been energized, it sets up a field in the magnetic circuit, which consists of the solenoid housing, the coil core, and the armature. The armature pivots in the electrostatic shield and forces the electrical contact/spring to make contact with the printed circuit board.

The electrical contact/spring, a critical component of this design, serves two functions. It is the signal path when activated, and the armature return spring when the coil is no longer energized. Springs on printed circuit boards are a common method of attenuator switching. However, the springs normally used are not designed for millions of cycles. Such a spring has to have extremely high tensile strength, good fatigue resistance, low tarnishing properties, high electrical conductivity, and reasonable manufacturability. To provide the amount of motion required of this

spring without too much stress, the spring material needs a low modulus of elasticity as well. At first glance, berillium-copper seemed the proper material. However, this material does not have the fatigue properties needed, and it also tarnishes. An alloy of palladium, platinum, gold, and silver met all the requirements. To maintain low stress, the spring is long and thin, and to provide adequate return force to the armature, it is wide.

As mentioned earlier, the magnetic path of the relay includes the housing, core, and armature. When the coil is energized, the armature pushes the spring down by pivoting around the core. The force must be quite high to overcome the force of the spring, and so a relay material with high permeability is used. When the coil is turned off, the current ceases to flow, and the return force of the electrical contact/spring overcomes the diminishing force of the armature and breaks electrical contact with the printed circuit board. The return force also overcomes a residual magnetic force that exists after the current is switched off. This force is minimized by putting a thick chrome plating on the armature. The plating acts as an air gap in the magnetic circuit and reduces the activation force at the end of the armature's travel. Reducing this force diminishes the unwanted high acceleration that wears out the armature and decreases contact/spring life.

The reliability of the contact system was recognized as critical. During the design cycle, the contact system was severely tested. The results of these tests were used to modify the design and production processes until the desired

Fig. 7. 10:1 vernier design eliminates the 1,2,5 intermediate switching found in most oscilloscopes and allows continuous calibration of the vertical system.

performance was achieved. The tests also showed that fewer than 0.6% of the contacts break in the first 1,000,000 cycles of operation. Useful life of the contacts is limited to around 1,500,000 cycles by the buildup of nonconducting organic polymers, which begins to increase contact resistance at this point.

In addition to fulfilling its function as an attenuator, the programmable attenuator designed for the 1980A/B also contributes in other areas. Primary among these is that it allows the microprocessor to scan through the vertical attenuation ranges automatically to perform automatic setup for bench applications. Second, it allows remote setup for bus-controlled applications. Third, the attenuator's input BNC connector has not only the usual signal and ground paths, but also a third path, which has two uses. One is to sense the value of a resistor in HP 10080-Series probes. If the resistor identifies the probe as a ÷10 probe, the microprocessor scales the volts/division readings on the CRT and LED displays so that the correct values are displayed. These probes also have a button that shorts the internal resistor to ground; this can be used to initiate a measurement sequence stored in the 19811A Plot/Sequence ROM (see box, page 9).

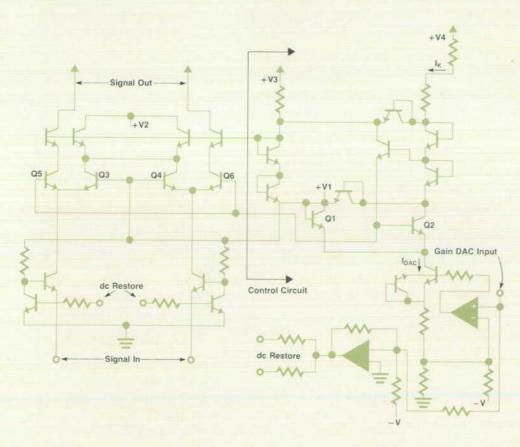

The circuit implementation of the remainder of the vertical system is identical to earlier designs except for the preamplifier and the interface level shifting necessary for electronic control. The design of the preamp is centered around a 10:1 vernier. This particular design eliminates the 1, 2, 5 intermediate range switching normally required for an oscilloscope and allows continuous calibration of the vertical system. No down-vernier, uncalibrated conditions exist for the 1980A/B.

Fig. 7 is the schematic design of the vernier circuit. Conceptually, the current  $\rm I_{\rm K}$  and the current  $\rm I_{\rm DAC}$ , which is generated from the gain DAC input, establish the emitter currents of devices Q1 and Q2 in the control circuit. Device Q1 in turn establishes a base voltage for devices Q3 and Q4 while device Q2 sets the base voltage for devices Q5 and Q6. By appropriately controlling the differential base-emitter voltage of these devices, the 10:1 vernier range can be achieved. The actual vernier range is approximately 12:1 to

allow for calibration range. The dc restore circuit keeps the dc bias level at the output of the vernier (collectors of Q5 and Q6) constant, independent of the vernier setting.

Continuous calibration lets the user set up a convenient display that is always calibrated. For example, the vertical sensitivity may be adjusted so that the peak-to-peak display of a signal of unknown amplitude covers ten divisions. The signal's peak-to-peak amplitude is then easily determined by multiplying the displayed vertical sensitivity by ten. If the vertical sensitivity display reads 38.9 nV/div, the signal's amplitude is 389 nV.

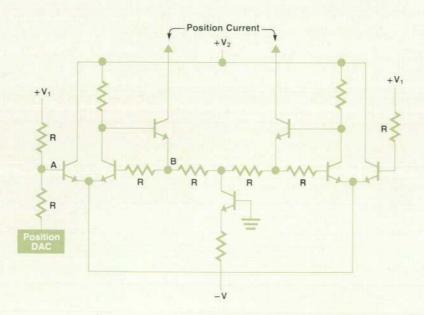

Vertical position is also controlled by one of the microprocessor-controlled DAC channels. This particular DAC output is a current and drives the circuit shown in Fig. 8. The voltage developed at point A is reflected to point B thus controlling the total position current available from the current source. The advantage of this circuit implementation is that it uses diffused monolithic resistors and does not have to rely on precision thick-film resistors for position accuracy. Like all analog functions on the 1980A/B, the vertical position is calibrated; calibration of the vertical position is the hardware basis for the front-panel  $\Delta V$  feature. When under bus control, the waveform can be positioned wherever desired, without an operator. Production test applications will find this useful.

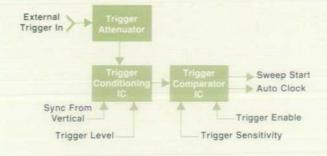

## Trigger System

An oscilloscope's trigger system selects the trigger source, internal or external, and conditions the selected signal by filtering. The trigger system provides ac or dc coupling and low-frequency or high-frequency rejection. Internal trigger source selection picks off a sync signal from one of the vertical input channels, while external source selection uses an external source input different from the vertical channels. Trigger view, which allows the user to view this conditioned trigger signal, aids in determining the trigger point. The output of the trigger system is a start-of-sweep signal for the horizontal system.

Adding programmability to an oscilloscope left the role of the trigger system unchanged. In fact, the only major

Fig. 8. Vertical position circuit uses diffused monolithic resistors. With this circuit, a displayed waveform can be placed wherever desired without the aid of an operator when the 1980A/B is under bus control.

Fig. 9. 1980A/B trigger system block diagram.

innovation in the 1980A/B's trigger system is in the interface implementation, which allows the trigger system to be controlled by the microprocessor system via the serial data bus. For external trigger inputs, the attenuator used is similar to the one used in the vertical system but with attenuation factors of  $\times 1$  and  $\times 10$  only.

The block diagram of the 1980A/B trigger system appears in Fig. 9. The three main functional blocks are the trigger attenuator for external inputs, the trigger conditioning IC for filtering the trigger signal, and the trigger comparator IC, which with the enable signal from the horizontal system generates the start-of-sweep signal.

Both the trigger conditioning IC and the trigger comparator IC are on a single thick-film hybrid circuit. Thick-film capacitors are used for implementing the filtering functions. Only the ac coupling mode requires circuitry outside the hybrid because of the size of the capacitor required.

Calibrated trigger level, one of the 1980A/B's special features, is provided by the trigger coupling IC. This feature lets the user preset the trigger level for bus-controlled applications. This is particularly valuable in production applications where the system under test has known characteristics and the trigger level can be preset without operator assistance.

The trigger comparator IC has two innovative features. The first of these is trigger sensitivity selection. Having two trigger sensitivities optimizes trigger performance as a function of vertical sensitivity. The lower trigger sensitivity corresponds to the high vertical sensitivity range (2 mV/div to 9.99 mV/div). This means that larger displayed signals are required to trigger the 1980A/B when it is on the 2.0 mV/div to 9.99 mV/div range than when it is on the 10.0 mV/div to 10.0V/div ranges. The ratio of trigger sensitivities

#### Wilhelm Taylor

After receiving his BSME degree from Colorado State University, Will Taylor joined HP's Colorado Springs Division in 1975. He has worked on the 1980A/B project and the 1950A expansion module for the 1980A/B. Will is currently with HP's Colorado Telecommunications Division and has an MBA from the University of Colorado in Colorado Springs. His hobbies include running, chess, and woodworking.

## John R. Wilson

A native of San Luis Obispo, California, John Wilson joined Hewlett-Packard in 1978 after receiving his BSEE degree from the University of California at Davis. He has worked on the 1980A/B is attenuator and contributed to the attenuator section of this article. His interests include kayaking, tennis, soccer, downhill and cross-country skiing, and photography.

#### William E. Watry

Bill Watry, software project leader in the oscilloscope R&D lab, has written a significant portion of the 1980A/B firmware including system expansion capabilities and the routines that interface the keyboard and rotary control. Bill recently assumed the management supervision of a laboratory group that is developing 1980A/B applications software. He has a BSEE degree, specializing in computer science, from the University of Colorado in Colorado Springs. Bill joined HP in 1966 and has worked on oscilloscopes for 16 years. He is married and has five children. He

coaches and plays soccer and enjoys motorcycling and skiing.

#### Russell J. Harding

Russ Harding joined HP in 1968 after receiving his BSEE and MSEE degrees from Purdue University. He has worked in the sampling oscilloscope group, the displays group, and the monolithic IC lab. After joining the 1980A/B project team, he was responsible for the design of the attenuators and trigger circuits. He then became project manager for the hardware design, and later transferred with the 1980A/B to production as production section manager. Russ is married and has a daughter and a son. In his spare time he hikes, crosscountry skis, collects beer advertising

memorabilia, and works on his son's model train.

#### Monte R. Campbell

Monte Campbell, presently project manager for the 1980 A/B's expansion modules, worked on the horizontal system integrated circuits in the 1980A/B. Monte, who joined HP in 1977, has a BSEE degree from Colorado State University and an MSEE degree from Stanford University. He is married, has a daughter, and lives in Woodland Park, Colorado. He has a private pilot's license and enjoys softball and skiing.

is 2 to 1. This difference helps reduce the possibility of triggering on noise when using the high-sensitivity vertical ranges.

The other feature of the trigger comparator IC is the auto clock output. This output is a shaped version of the input signal that is sent to the horizontal system. There it is combined with other signals to generate the trigger flag signal essential to the 1980A/B's Autoscope operation and other trigger flag measurements.

#### Reference

P. Austgen, W. Watry, and M. Karin, "Software-based design automates scope operations," Electronics, March 10, 1981, pp. 181-188.

## The Early History of the 1980A/B Oscilloscope Measurement System

#### by Zvonko Fazarinc

Hewlett-Packard Laboratories

The development of the 1980A/B Oscilloscope Measurement System began many years ago when John Young, then an HP vice president, approached Paul Stoft, director of the Electronic Research Laboratory, with a request for a concerted effort in the field of oscilloscopes. The explorations were to pursue the trends in time-domain measurements in view of the emerging digital electronics.

During the ensuing weeks a series of brainstorming sessions were conducted by Paul Stoft and attended by members of the technical staff. The Colorado Springs Division, which is responsible for oscilloscope development and manufacturing at Hewlett-Packard, sent representatives to Palo Alto, among them the present division manager, John Riggen.

The enthusiasm for what we called the "smart scope" grew quickly in the laboratory and exciting new ideas were generated at a high rate in a synergistic exchange between the traditional analog engineers and the digitally oriented team that had just completed the development of the first scientific pocket calculator, the HP-35. Eventually Paul Stoff felt that the time was ripe for organizing the project team and charged this author with the task.

First, the critical areas were staffed. Dan Hunsinger, presently the IC facility manager of HP's Santa Clara Division, was given responsibility for inventing and developing the voltage-controlled preamplifier. His effort resulted in proprietary designs that dealt successfully with noise and control linearity problems over two decades of gain. Dick Baumgartner, who had experience with oscilloscope design, was given the task of solving the voltage control problem for the sweep generator. Dick Crawford, the most experienced of all, who had been coordinating the whole effort within the laboratory and with the division up to that point, was charged with responsibility for deflection amplifiers, power supplies, and packaging. Because we wanted to keep the beam intensity under processor control, he was also faced with the problem of the DAC interface to the high-voltage supply. Dave Cochran, who had just developed and implemented the scientific library for the HP-35 Calculator, accepted responsibility for the control algorithms and for the display driver circuitry.

Wayne Grove joined the team as the liaison to divisions that would be involved in integrated circuits, hybrids, LED displays, and other components. Greg Justice was to develop a low-power vertical deflection amplifier and Jim Umphrey and Bill Mordan, whose talents were contributed by the Colorado Springs Division, were to develop the digital delay and the trigger circuit, respectively. Mark Morgenthaler joined the project to work on the attenuator but was soon charged with the development of a voltage-controlled delay generator and of a precise triggerable oscillator. Ken Peterson took on the responsibility for the delay counter. The number of controlled blocks grew quickly beyond the practicality of individual digital-to-analog converters, so Knud Knudsen was given the responsibility for a 16-channel single-chip DAC. Rich Wheeler's task was to adapt a magnetic card reader for storage of control settings. When Ralph Eschenbach

accepted the task of system partitioning into hybrids and the development of the required substrates, the project seemed to be well on its way with the exception of the digital controller. This problem was resolved when Francé Rodé, the developer of the HP-35 processor, responded to the challenge of making his processor do the controlling function and joined the team.

The tremendous strength and dedication of the project team resulted in fast progress in circuit development but also in an even faster proliferation of ideas that mercilessly ignored the traditions in oscilloscopy. Serious questions of market acceptance arose and we decided to subject the new concepts to the scrutiny of management, marketing, and representative users in the form of a computer simulation. Paul Hughet, coached by Jim Duley, produced a complete emulation of controls and responses on an HP computer. This was used successfully to test a number of competing ideas and provided a good preview of the proposed concepts for management. A project review by top corporate and divisional management, which included a functional mockup of the oscilloscope tied to the computer by an umbilical cord, brought full support for the project and a number of good suggestions, most of them from Barney Oliver, HP vice president for R&D, who was actively involved in the project throughout its life. A number of excellent suggestions came from division management, notably that for a single control knob with menu selection and character generation on screen as an alternative to individual pushbutton controls and LED displays.

Responsibility for the breadboard rested with Frank Lee, Rich Marconi, Lyman Miller and Gene Reynolds. They not only kept pace with numerous changes but continually upgraded the functional breadboard with custom integrated circuits as these were processed by the Santa Clara bipolar facility and by Loveland's MOS processing plant. During this period the industrial designers, Bill Wohltman and Dick Anderson, produced a line of attractive packages for the instrument, and George Drennan, Bob Hirsch, and Dan Paxton worried about the mechanical aspects of internal packaging in preparation for tooling design. Clarence Studley, the designer of the HP-35 keyboard, took another look at the same problem from the instrumentation viewpoint and generated a number of innovative ideas. The lion's share of the effort, though, was devoted to software. The newly acquired dimension of freedom unleashed the imagination of the project team and of oscilloscope users. Proposals for digital calibration, automatic balance adjustment and automatic setup of controls originated from Francé Rodé, Ralph Eschenbach, Pete Lindes, and Tom Hornak.

The need for closer coordination in view of the approaching transfer of the project induced the Colorado Springs Division to name Stan Lang as the responsible project manager. In the ensuing year the ties between the laboratory and the division strengthened through the goodwill of Stan and his team. After a visit by Bill Risley it became clear that the lab's role in the project was quickly nearing its end. A few months later the project was transferred.

# The Design and Development of the 1980A/B at Colorado Springs

#### by William B. Risley

Colorado Springs Division

After the 1980A/B Oscilloscope Measurement System was transferred to Colorado Springs, a substantial team was assembled to complete the design efforts. Walt Fischer, who is now marketing manager of HP's Colorado Telecommunications Division, was the R&D section manager with Tom Bohley, Stan Lang, and the author as project managers. Tom was responsible for the overall circuit design and packaging, and Stan handled the system design. My group was responsible for the processor system and firmware. The programmable attenuator was contributed by Russ Harding, Wilhelm Taylor, and John Wilson. Eidon Comish contributed the preamplifier and vertical output stage, and Marvin Estes helped support the vertical system design and developed probes. Roy Wheeler completed the digital to-analog converter circuits and hybrid and designed the gate and high-voltage power supply. Russ Harding, Jim Umphrey, Eldon Cornish, Monte Campbell, and Dennis Weller all contributed to the trigger and time base. Paul Austgen, Dick Tabbutt. Bob Landgraf, Bill Watry, Mike Karin, and Fred Rampey developed the processor system and firmware.

The package, front panels, and numerous parts were designed by John Campbell,

Carolyn Finch, Jim Carner, Ernie Hastings, and Wilhelm Taylor. Tom Bohley and Jim Felps developed the power supply, and Don Skarke and Joe Millard worked out the thermal management for the product. Near the end of the project, Ed Evel, Ken Rush, and Al Best helped resolve system problems resulting from putting a noisy processor into a highly sensitive instrument.

Ray Kushnir, Don Smith, Roy Wheeler, Tom Bohley, Ron Westlund, Chuck Small, and Larry Gammill all provided significant refinements and guidance in the transfer of the 1980A/B to production. Bill Ford, Johnnie Hancock, and Rod Schlater also contributed their skills to the transfer of the product to manufacturing. Jim Williams was the industrial designer and was assisted by Don Henry and Mike Easter.

There were many others without whom the project could not have been completed. Among these were the persistent engineers in the IC facilities at the Colorado Springs, Loveland, and Santa Clara Divisions, those in printed circuit design and fabrication in Colorado Springs and Loveland, and the process and production engineers who had to learn how to build the novel front panels and attenuators.

# Digital Waveform Storage for the Oscilloscope Measurement System

by Eddie A. Evel and Robert M. Landgraf

ITH THE ADDITION of digital waveform storage, the 1980A/B Oscilloscope Measurement System, which on its own is fully programmable, can be operated completely through a controller without human interaction. With the basic 1980A/B, data can be acquired using the continuously variable trigger level, trigger flag, and HP-IB controller software. However, this data cannot be displayed on the CRT screen. With the 19860A Digital Waveform Storage Option, digitized data can be displayed on the CRT and sent to a computer for analysis, and waveform data created by the computer can be displayed on the CRT. Although the 1980A/B's trigger flag used with external software can digitize waveforms, additional software is not needed with the 19860A.

The 19860A Digital Waveform Storage Option increases the overall usefulness of the 1980A/B by digitizing one or two displayed waveforms and storing them within the instrument for later display or for data output on the HP-IB. With this feature the 1980A/B can contribute to fully automatic applications. The HP-IB system controller can automatically analyze the digitized waveform data and perform go/no-go tests on complex signal waveforms, automatically adjust the device being tested, or instruct the operator. The 19860A lets the bench user store waveforms for future reference and obtain data output for bench applications. In addition to outputting data to a calculator or computer, the 19860A can output data directly to a plotter to obtain hard copy without the aid of a controller. Lowrepetition-rate data or in some cases single-shot data that normally cannot be observed on a conventional oscilloscope can be digitized and displayed.

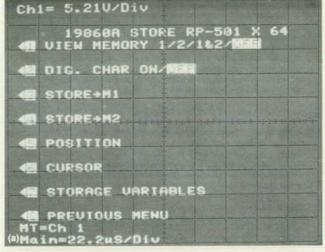

Fig. 1. 1980A/B option menu panel with 19860A Waveform Storage option installed.

#### 1980A/B-19860A Interaction

The 19860A hardware is designed to use and enhance the capabilities and features of the basic instrument. For example, since the 19860A digitizes waveforms on the 1980A/B's CRT screen, it uses all signal conditioning done by the 1980A/B, such as amplification, bandwidth limit, positioning, and channel switching. Also, the 19860A uses the delay sweep timing circuitry within the 1980A/B sweep circuitry as the time base for the digitizing operation. The 1980A/B's microprocessor controls the digitizing operation and does the data scaling and data input/output.

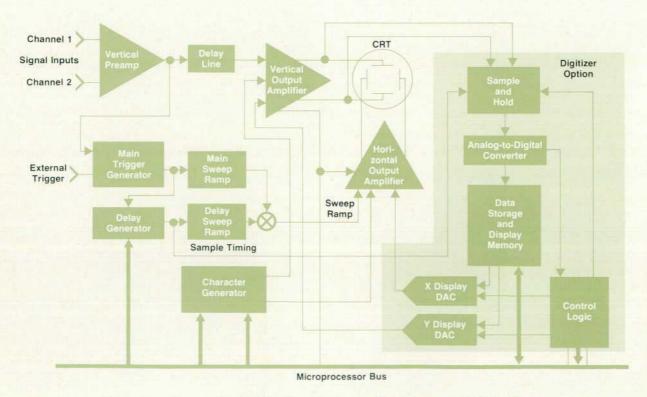

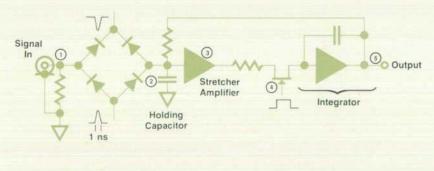

The digitizer option consists of a sample-and-hold cir-

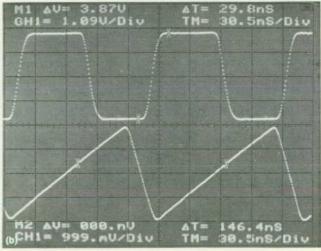

Fig. 2. (a) Waveform storage menu. (b) Cursors positioned on digitized waveforms with time and voltage differences displayed.

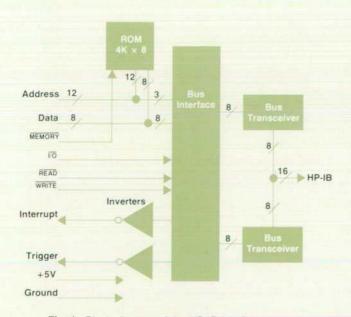

cuit, an analog-to-digital converter (ADC), data storage and display memory, two display digital-to-analog converters (DACs), and control logic. Fig. 3 illustrates how the 19860A digitizer is integrated into the 1980A/B system.

The 19860A expands the 1980A/B through two plug-in cards internal to the mainframe. One of the cards contains 2K of ROM and 1K×12 bits of data display RAM. An additional 8K of ROM uses two feature-ROM slots in the mainframe, and 384 more bytes of 1980A/B system RAM is available to the two occupied feature-ROM slots.

The 8085 system microprocessor executes restart commands that link the expansion blocks to the mainframe functions, which are shared. The restart command followed by a table number allows an effective subroutine jump to a specific, table-defined subroutine. The restart command links the mainframe to the expansion module, feature ROMs, and internal expansion cards and allows interlocking the rotary control. Cleanup routines resulting from key execution also connect with the expansion blocks. The information required to keep track of whether the signal source requires repetitive or real-time sampling is handled through the restart system as the instrument settings are changed. The expansion cards and expansion module each have different restart codes. Before the subroutine is read, an existence check is made to determine if the particular expansion block is contained in the instrument. If not, an immediate return is executed. (Also see page 21 for a discussion of mainframe/option interaction.)

As shown in Fig. 3, an incoming signal goes through the vertical preamplifier, the delay line, and the vertical output amplifier to the CRT. At the same time, the signal is sent to

the trigger circuit. A trigger is generated and used by the horizontal sweep circuit to initiate a sweep ramp. This goes through the horizontal output amplifier to sweep the beam across the CRT, thus generating the real-time trace.

As the first step in the digitizing operation, the instrument checks for a valid, digitizable signal and for a valid operating mode. Invalid modes include the dual horizontal mode, which displays both main and delayed sweeps, and the digital delay and trigger delay modes. Advisory messages indicating invalid modes are displayed, thus eliminating the need to refer to an operating manual for the meaning of error codes.

At the start of the digitizing routine, the microprocessor shuts down the interrupt system and terminates the character display so that only the signal source to be digitized is displayed during the storage operation.

During a digitize operation, the signal out of the vertical output amplifier is also fed to the sample-and-hold circuit. At the appropriate time, the sample timing signal is issued by the horizontal sweep circuit. This causes the sample-and-hold circuit to take a sample. Then an A-to-D conversion is done and the data is loaded into the data storage and display memory. Once the microprocessor senses that the data point has been loaded into memory, it programs the horizontal sweep for a new sample time. Then the sample-and-load-memory cycle is repeated until as many as 501 data points on the waveform are stored into memory. Later, the data may be displayed back on the CRT using the X and Y display DACs. The DAC outputs are multiplexed onto the CRT during the character generator display cycle.

Data is sampled at the output of the CRT driver to allow a

Fig. 3. Block diagram of the 19860A Waveform Storage Option for the 1980A/B Oscilloscope Measurement System. The option digitizes one or two displayed waveforms and stores the data for later display or output on the HP-IB (IEEE-488).

frequency response equivalent to the CRT display. Individually acquired digitized signals are stored in one of two local data memories. Each memory contains 501×12 bits, each 12-bit data word consisting of 10 bits of data, one bit for display blanking control, and one bit that is not used.

Status of the digital storage operation is reported over the HP-IB. The report includes completion of a digitizing operation, information equivalent to the CRT-displayed advisories, and information regarding the possible clipping of a signal positioned partially off screen. Thus, the information seen on the CRT is available to a computer for complete automation.

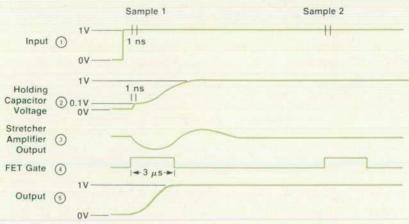

#### Repetitive and Single-Sweep Sampling

At the faster sweep speeds, the 19860A uses a repetitive sampling technique in which the signal to be digitized is sampled at different times during successive occurrences of the signal. Two sweeps per stored data point are used. The specific sampling times are determined by the sweep speed setting of the 1980A/B and the number of points selected to be digitized. The signal is sampled at each point by the narrow aperture of the sample-and-hold circuit, then an analog-to-digital conversion is made, and data is loaded into the memory. This method enables the 19860A to obtain ten-bit data on very fast signals (up to 100 MHz) while using a low-cost, low-power-consumption ADC. It also allows time resolution down to 100 ps between data points.

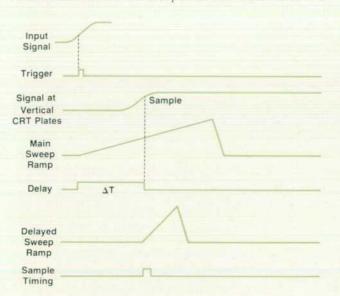

At sweep speeds slower than 1 ms/div, the minimum time between data points is greater than 20  $\mu$ s (determined by the maximum 501 points for ten divisions of horizontal display). This allows the 19860A to switch over automatically to a single-shot mode. In this mode, the 19860A starts sampling the signal when the 1980A/B is triggered, and up to 501 data points are taken on one occurrence of the signal. This mode operates like the repetitive mode, except that a programmable counter is started when the sample timing signal occurs (Fig. 4). The microprocessor programs the counter to count down starting from the value of the next time increment between data points. Each time the counter

Fig. 4. Timing for sampling a waveform to be digitized is generated using the 1980A/B's sweep delay.

reaches zero, a sample is taken. The result is that the timing signal takes the first sample and starts the counter, which takes all successive samples on one occurrence of the waveform.

Compared to a "flash" ADC, this method is much simpler, uses less power, and is a proven design. It requires less hardware and is cheaper to implement. For repetitive signals, it offers much higher bandwidth and much better timing resolution than a flash converter.

#### Sample Timing

The basis of the sample timing system is the microprocessor-controlled sweep timing circuit. The sample timing signal is generated through the oscilloscope's delayed sweep mode. An oscilloscope normally uses the delayed sweep mode to generate a sweep that begins some variable time after the main sweep is triggered and started. The user selects the delay time to observe part of a waveform on a faster delayed sweep speed. Fig. 4 shows the sequence of events.

First, the trigger circuit operates on the input signal to generate a trigger based on a transition of the input signal, such as a positive-going step. The trigger causes the main sweep ramp to start sweeping across the CRT to display the waveform. A delay is also initiated. At the end of the delay, the delayed sweep ramp is started. Either the main sweep ramp or the delayed sweep ramp is gated to the horizontal output amplifier to generate the horizontal sweep at the CRT. The delayed sweep causes the CRT beam to sweep across the CRT at a different rate from the main sweep, thus producing an expanded display of a portion of the input signal.

In addition to starting the delayed sweep at the end of the selected delay, the sample timing signal is generated. If the sampler is enabled, a sample is taken. To take samples at different points on the waveform, the microprocessor need only program different delay times. The microprocessor calculates the desired time between sample points and increments the delay generator time by that amount as each sample is taken on the waveform. When the desired samples have been taken and loaded into the memory, the microprocessor returns the delay setting to its original value.

The delay generator uses a combination of analog and digital circuits to obtain a very accurate delay time. For delay increments between 0 and 100 ns, an analog delay circuit is used. For delay increments greater than 100 ns, a counter and a crystal oscillator are used to achieve high accuracy. Using this system to generate the sample timing signal increases the timing accuracy of the digitized data over that of the real-time CRT display, which is generated by an analog sweep ramp circuit.

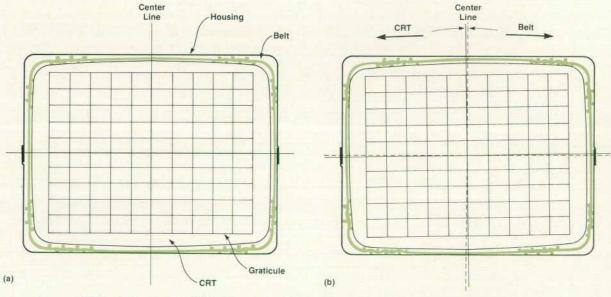

#### Defining the Digitized Window

In the vertical axis, any part of the trace that is within the CRT graticule will be digitized. In the horizontal axis, ten divisions are digitized except when the 1980A/B is in the intensified sweep mode. In this case, data is taken on the part of the waveform where the intensified marker appears, but the data taken is always redisplayed over ten horizontal divisions on the CRT.

Fig. 5. In intensified sweep mode, the digitizer samples the waveform during the intensified window, then displays this data over ten horizontal divisions.

The sweep mode that is in effect when the digitize command is given determines the time window to be digitized. There are three possible modes: main, delayed, and intensified. In main sweep mode, the microprocessor uses the main sweep time per division to calculate the time increment needed to obtain the desired number of points across ten divisions of main sweep. The delay is set to zero for the first point and then incremented for each successive point until all points are taken.

In the intensified sweep mode, the sweep is done by the main sweep ramp, but the delayed sweep ramp intensifies the trace. This defines the region that will be viewed when the oscilloscope is switched to delayed sweep. The intensified marker also defines the portion of the waveform to be digitized. The marker length is determined by the delayed sweep time per division and is used when calculating the digitizer time increment. After taking the desired number of points during the intensified window, the digitizer then displays this data over ten horizontal divisions as shown in Fig. 5. The first digitized point is taken at an initial delay determined by the oscilloscope settings, and then the delay is incremented for successive points. In delayed sweep mode, the real-time trace is expanded on the screen around the portion of the waveform defined in the intensified mode. The delayed digitizing operation is identical to the

intensified digitizing operation.

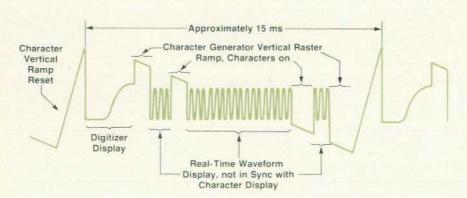

#### Display Cycle

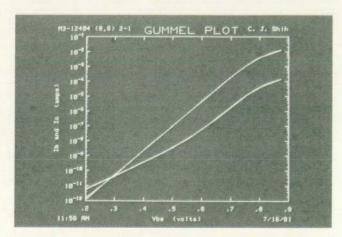

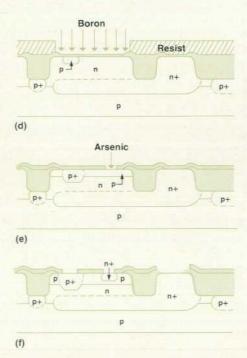

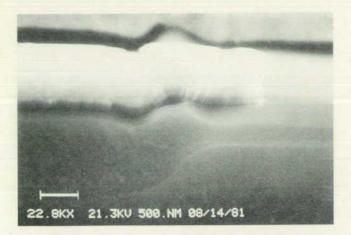

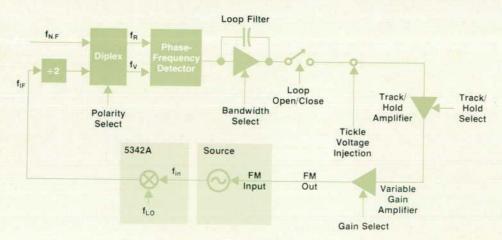

Once data from a waveform is stored in the memory, it may be displayed on the CRT with or without the real-time waveform display. To do this, the microprocessor initiates a digitizer display cycle each time the character display is refreshed, approximately every 15 ms. The digitized trace, the characters, and the real-time trace are all displayed by time-multiplexing the CRT beam. The characters are displayed by using a raster scan of the CRT and modulating the beam on and off. The digitized data is displayed during the vertical reset cycle of the raster scan. During the raster scan when characters are not displayed, the real-time trace is multiplexed onto the CRT and displayed (Fig. 6). Real-time trace timing normally is asynchronous with the character display cycle; therefore, the missing segments of the real-time trace usually are not noticeable.