# HEWLETT-PACKARDJOURNAL

### **HEWLETT PACKARD JOURNAL**

Technical Information from the Laboratories of Hewlett-Packard Company

### AUGUST 1983 Volume 34 • Number 8

#### **Contents:**

VLSI Technology Packs 32-Bit Computer System into a Small Package, by Joseph W. Beyers, Eugene R. Zeller, and S. Dana Seccombe Five very dense ICs are the key.

An 18-MHz, 32-Bit VLSI Microprocessor, by Kevin P. Burkhart, Mark A. Forsyth, Mark E. Hammer, and Darius F. Tanksalvala This NMOS IC contains over 450,000 transistors.

Instruction Set for a Single-Chip 32-Bit Processor, by James G. Fiasconaro A stackoriented design using segmentation forms this command set.

VLSI I/O Processor for a 32-Bit Computer System, by Fred J. Gross, William S. Jaffe, and Donald R. Weiss This IC uses the same basic circuits as the CPU chip.

High-Performance VLSI Memory System, by Clifford G. Lob, Mark J. Reed, Joseph P. Fucetola, and Mark A. Ludwig This system provides 256K bytes of memory per card and has a bandwidth of 36M bytes/s.

**18-MHz Clock Distribution System, by Clifford G. Lob and Alexander O. Elkins** A clock IC provides buffered two-phase, nonoverlapping clocks.

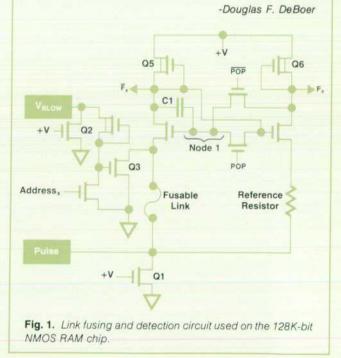

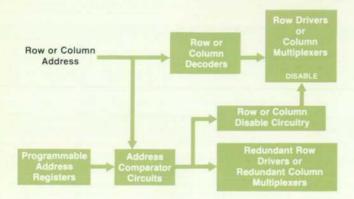

128K-Bit NMOS Dynamic RAM with Redundancy, by John K. Wheeler, John R. Spencer, Dale R. Beucler, and Charlie G. Kohlhardt Extra rows and columns improve chip yield.

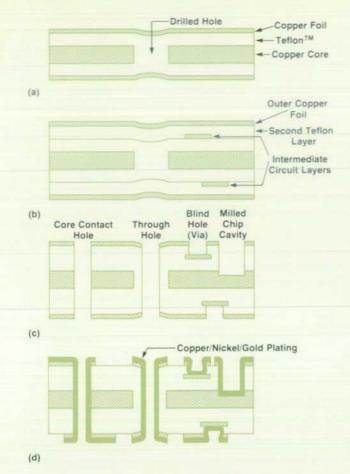

**Finstrate: A New Concept in VLSI Packaging,** by Arun K. Malhotra, Glen E. Leinbach, Jeffery J. Straw, and Guy R. Wagner This novel design integrates a heat sink with a printed circuit board.

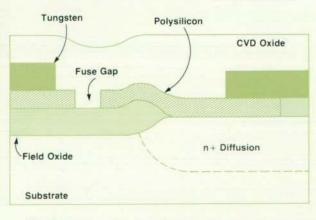

NMOS-III Process Technology, by James M. Mikkelson, Fung-Sun Fei, Arun K. Malhotra, and S. Dana Seccombe Refractory metallization, external contact structures, 1.5-μm-wide lines, and 1.0-μm spaces are used in this VLSI process.

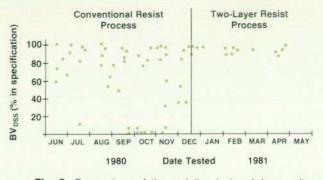

**Two-Layer Refractory Metal IC Process,** by James P. Roland, Norman E. Hendrickson, Daniel D. Kessler, Donald E. Novy, Jr., and David W. Quint Tungsten metallization reduces the risk of electromigration failure.

**NMOS-III Photolithography**, by Howard E. Abraham, Keith G. Bartlett, Gary L. Hillis, Mark Stolz, and Martin S. Wilson Step-and-repeat optical lithography, two-layer resist, and pellicles are salient features.

Authors

#### In this Issue:

Engineering productivity is under close scrutiny at many companies. Management wants more results for the money spent on R&D. Perhaps you remember, as I do, how the productivity of our engineers and scientists fairly spurted a few years ago when integrated circuit technology put scientific calculators in their pockets and powerful, interactive computers on their desktops. Can we do that again? The developments described in this issue are an attempt to do just that. A single integrated circuit chip packed with 450,000 transistors is the central processing unit (CPU) of a 32-bit computer system that fits in the category known as mainframes—the largest computers around. Four other equally dense chips

support the CPU. A brand-new method of mounting the chips is given a new name—finstrates (see cover). A new process, NMOS III, uses pure tungsten to connect elements on the chip, a major departure from current IC practice. Test systems are designed into some of the chips because it's impractical to test anything so complex from the outside. Several issues from now we'll carry the story of the new HP 9000 Computer, a mainframe on a desktop for individual engineers and scientists that may give major impetus to the use of computers for design, engineering, simulation, and complex mathematical problem-solving. In this issue, you'll read about the IC and packaging technologies that make the HP 9000 possible. It's a remarkable achievement and a remarkable story.

-R.P. Dolan

## VLSI Technology Packs 32-Bit Computer System into a Small Package

The new HP 9000 Computer is a compact, highly capable 32-bit computer system that incorporates five very dense integrated circuits made by a highly refined NMOS process.

#### by Joseph W. Beyers, Eugene R. Zeller, and S. Dana Seccombe

OW DOES ONE GO ABOUT PACKING the power of a large mainframe computer into a desktop computer? Answering this question was only one of the many problems facing the HP design team given the assignment of developing a personal engineering design station with enough computing power to allow the entire design process to take place on an engineer's bench. Their answer is a fully integrated 32-bit processing system based on five custom VLSI circuits. This required the development of three key technologies:

- A 32-bit system architecture realized by using advanced circuit design techniques

- A state-of-the-art NMOS VLSI\* process optimized for density and performance

- A new circuit board to dissipate the heat generated by the VLSI circuits and allow high-speed signal propagation.

#### System Overview

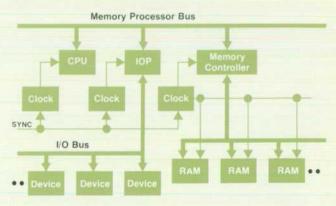

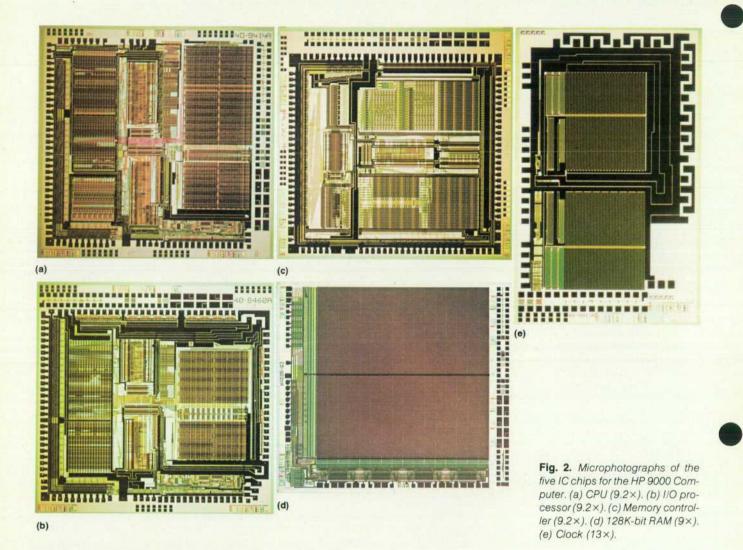

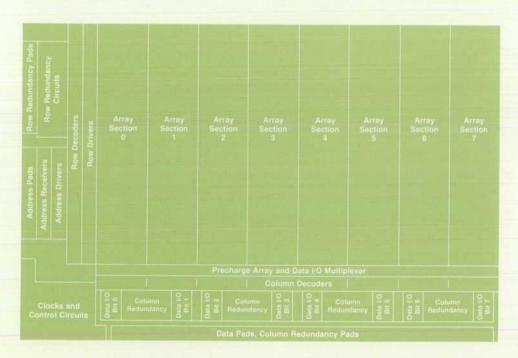

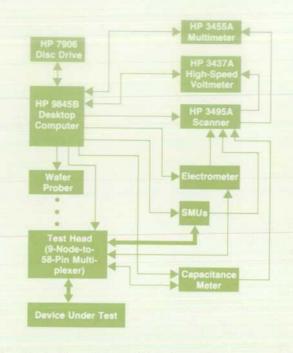

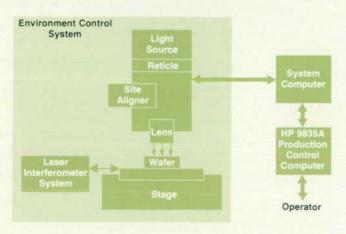

A block diagram of the 32-bit processing system is shown in Fig. 1. The system uses five different NMOS circuits operating at 18 MHz. These chips include a 32-bit CPU, an I/O processor, a memory controller, a 128K-bit RAM, and a clock driver (Fig. 2).

**CPU.** This single-chip 32-bit processor contains 450,000 transistors.<sup>1</sup> It is microprogrammed and has 9K 38-bit words of resident control store. It has twenty-eight 32-bit registers, a 32-bit ALU (arithmetic/logic unit) with multiply and divide logic, an N-bit shifter for bit extraction and alignment, and a seven-register port to the memory processor bus. The stack-oriented instruction set contains floating-point, string, and compiler optimization instructions. A 32-bit load instruction (including complete bounds checking) takes 550 ns and a 64-bit floating-point multiply takes 6  $\mu$ s. Microinstructions can execute in 55 ns.

**I/O Processor (IOP).** The IOP is also microprogrammed and contains 4.5K 38-bit words of control store. It handles eight DMA (direct memory access) channels with a data rate of up to 5M bytes/s. It has sixteen software-programmable interrupt levels and can independently execute command sequences from memory.

**Memory Controller.** The memory controller chip can control 256K bytes of RAM, perform byte, half-word, word, and semaphore\*\* operations, and do single-bit error correction and double-bit error detection of memory without any per-

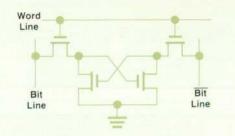

\*n-channel metal oxide semiconductor, very large scale integration. \*\*Used to control accesses in a multiple processor system. formance penalty. It can also heal up to 32 faulty locations and map logical to physical addresses in 16K-byte blocks. **RAM.** The 16K×8-bit RAM chip contains 128K bits of random access memory organized with redundant rows and columns. It is pipelined and has a 165-ns access time and a 110-ns cycle time.

**Clock.** The clock chip generates two nonoverlapping 18-MHz clock signals from a 36-MHz sine wave. It can drive a 1500-pF load with a 6-ns rise time.

#### Memory Processor Bus

The CPU, IOP, and memory controller communicate via the memory processor bus (MPB). The protocol of this 44line, 36M-byte/s bus can support up to seven CPUs or IOPs and fifteen memory controllers. This precharged dynamic bus is multiplexed between 29-bit addresses and 32-bit data words on alternating 55-ns clock cycles. The memory accesses are pipelined to allow sending up to two new addresses while the first data word is fetched from memory.

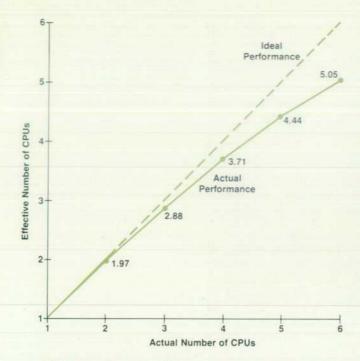

Because the 36M-byte/s data rate far exceeds the data requirements of one CPU, additional CPUs can be added and/or independent IOP operations can occur without a significant reduction in performance. Fig. 3 shows relative system performance as CPUs are added to the bus. Computation-intensive examples tend to approach the "ideal" line while heavy string operation performance tends to be lower than the average. The 32-bit CPUs are designed so that additional CPUs can be transparently added to the system. New tasks are usually assigned to

Fig. 1. Block diagram of 32-bit computer system based on five VLSI circuits: CPU, IOP, clock, memory controller, and RAM.

whichever CPU on the bus is free. However, a CPU can be dedicated to specific tasks. For example, the I/O processors can be programmed to send interrupt requests to either a specific CPU or all CPUs.

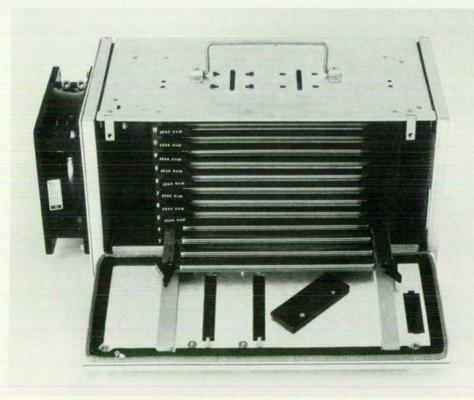

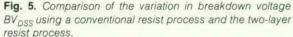

#### Packaging

Fig. 4 shows a picture of how the above system is packaged for the HP 9000 product line. The package, called the Memory/Processor Module, can hold up to twelve circuit boards. This allows a system configuration of up to 2.5 megabytes of memory with one CPU and one IOP. Up to three CPUs and three IOPs can be used for increased performance by sacrificing some of the memory. Power is supplied through two connectors on the bottom of the package. In the worst-case configuration, the system dissipates 185 watts. Forced air flow is used to cool the VLSI circuits to below a worst-case junction temperature of 90°C.

The standard I/O bus exits the package through a slot in the bottom and two optional I/O buses exit through connectors on the module's door.

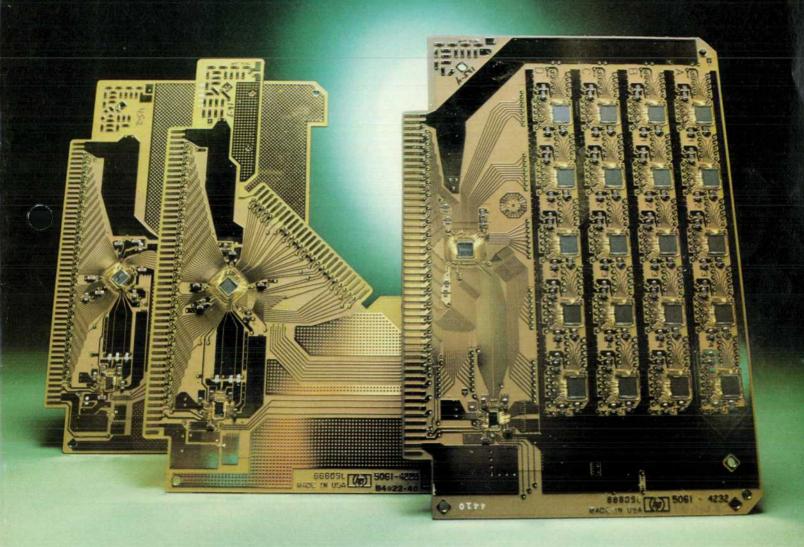

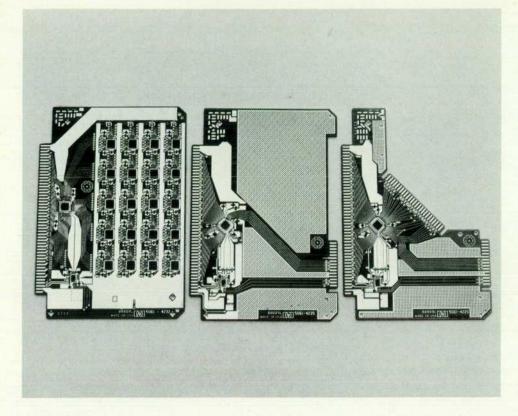

The VLSI chips are mounted on "finstrates." This name

was coined from this circuit board's dual role as a cooling fin and chip substrate. The Teflon<sup>TM</sup> dielectric covering provides for low-capacitance interconnections and the finstrate's copper core spreads the heat away from the chips. The three types of finstrates used in the module are shown in Fig. 5. In the center is the CPU board, which contains the CPU chip and a clock chip. On the right finstrate are an IOP chip and a clock chip. The inset on the upper right side of this IOP finstrate is where a small printed circuit board containing a set of TTL buffers for driving the I/O bus is attached. The memory finstrate on the left contains a memory controller, a clock, and twenty 128K-bit RAM chips to provide 256K bytes of single-biterror-correcting memory with a 36M-byte/s data rate.

The high-speed MPB exists only on the edges of the finstrates and the module's motherboard. The Memory/ Processor Module also contains a small printed circuit card that generates a 36-MHz master clock sine wave driven to each of the twelve finstrate slots.

The system is mechanically self-contained. Electromagnetic interference (EMI) is suppressed by using spe-

Fig. 3. Multiple 32-bit CPU performance for Whetstone B1D benchmark.

cial filters on the power supply connectors, honeycomb air filters at both ends, conductive door gaskets, and shielded I/O cables.

#### **VLSI NMOS Process**

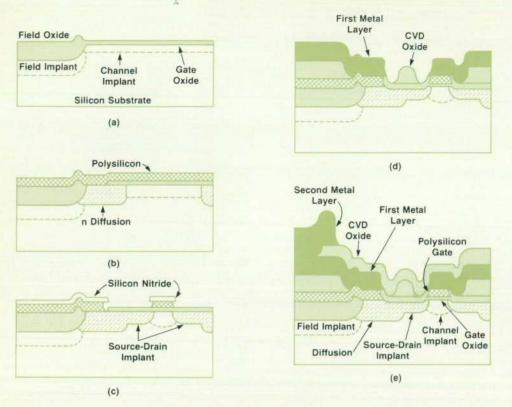

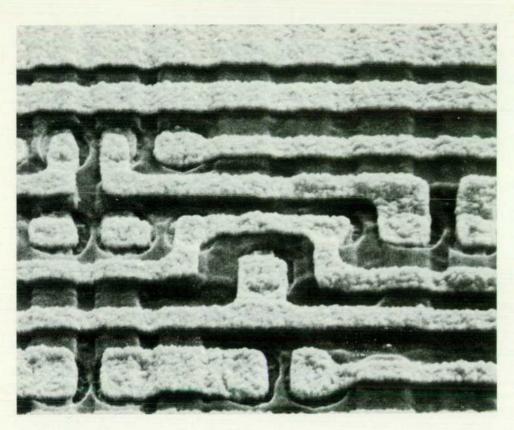

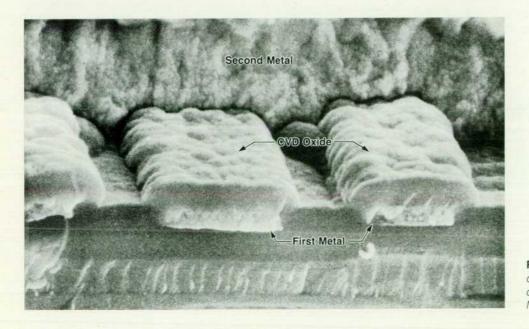

The major process design goal was to develop a high-

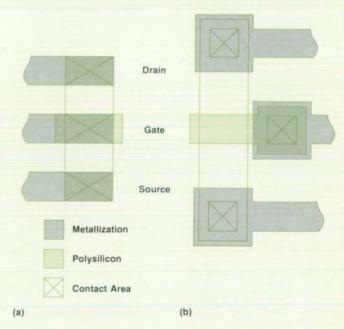

density, high-performance, highly reliable, productionvolume, VLSI process. These goals were realized by the use of a modified n-channel silicon-gate MOS process featuring 3½ levels of interconnect: diffusion, polysilicon with buried contacts, and two levels of refractory metal.<sup>2</sup>

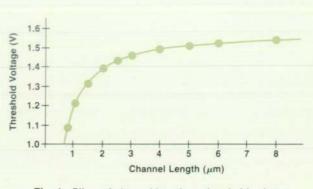

Integrated circuit densities are determined primarily by the minimum feature size. Lithographic considerations set this limit and resulted in layout rules and process capabilities that enable transistors to be fabricated with a minimum pitch of 2.5  $\mu$ m (1.5- $\mu$ m-wide lines spaced 1.0  $\mu$ m apart). The unconventional contact-over-gate device structure allowed even tighter layout rules.

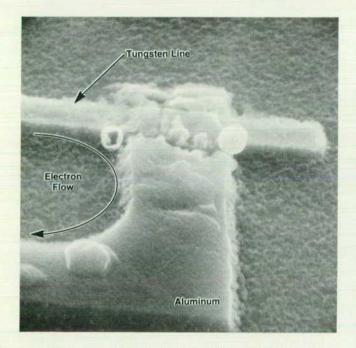

Another technique used to achieve the high circuit density is the use of two interconnect levels of refractory metal. Tungsten metallization was chosen because of its high conductivity and its resistance to electromigration.<sup>3</sup>

In addition to high density, transistor performance was emphasized. Special transistor characteristics (e.g., gateto-drain overlap capacitance and threshold voltage versus backgate voltage dependence) required the use of selfaligned gates, shallow source and drain regions, and transistor threshold voltage implants.

#### **Reliability and Self-Test**

Besides maximum performance, high reliability and easy serviceability were also key design goals. These goals were achieved through several approaches. First, the NMOS process was designed for high reliability—silicon gates, refractory metal (no metal migration problems), and conservative design specifications that protect against gate hot-electron injection. Second, except for the I/O drivers and clock circuit, the system is fully integrated—92 integrated circuit chips for a system with one megabyte of memory. Third,

Fig. 4. This package, called the Memory/Processor Module, can contain a complete 32-bit computer system with 2.5 megabytes of RAM. Performance can be enhanced by exchanging some of the memory boards for additional CPU and/or I/O processor boards.

**Fig. 5.** To dissipate the heat generated by the very dense VLSI chips, special boards, called finstrates, were developed. Shown from left to right are the 128K-byte RAM, CPU, and IOP finstrates.

special reliability features such as single-bit error correction and double-bit error detection were incorporated into the system's architecture. Up to 32 faulty locations per memory finstrate can be healed by redirecting their contents to registers on the memory controller chip, and memory size can be degraded in 16K-byte blocks (the address space can be assigned arbitrarily within or between memory cards in 16K-byte increments). Any card can be easily removed and the system will still operate, assuming, of course, that there are still at least one CPU, one I/O processor, and one memory card left in the system.

In addition, the thorough internal self-test can quickly identify any bad cards. At power-on, each card is tested without the need for external software and if a fault is detected, appropriate LEDs (light-emitting diodes) are lit to indicate which card is defective.

#### References

J. Beyers, et al, "A 32b VLSI Chip," Digest of Technical Papers, 1981 IEEE International Solid-State Circuits Conference, THAM 9.1.

2. J. Mikkelson, et al, "An NMOS VLSI Process for Fabrication of a 32b CPU Chip," Digest of Technical Papers, 1981 IEEE International Solid-State Circuits Conference, THAM 9.2.

3. P.P. Merchant, "Electromigration: An Overview," Hewlett-Packard Journal, Vol. 33, no. 8, August 1982.

### Acknowledgments

Bringing these complex technologies to production in late 1982 was the result of the determination and dedication of many people. Listed below are key contributors who transformed the initial design goals into a production reality.

The CPU chip design team included Joe Beyers. Kevin Burkhart, Dave Conner, Mark Forsyth, Mark Hammer, Tony Riccio, Harlan Talley, and Darius Tanksalvala. The CPU microcode was written by Jim Fiasconaro, Lee Gregory, Mike Kolesar, Bill Kwinn, Donovan Nickel, Rand Rentroe, and Larry Rupp. Fred Gross and Ed Weber wrote the IOP microcode and Mark Canepa, Ken Holloway, Bill Jaffe, Rich Köchis, Dave Maitland, Gary Taylor, and Don Weiss designed the IOP chip. The memory controller chip was developed by Joe Fucetola, Cliff Lob, Mark Ludwig, Bill Olson, Mark Reed, Tom Walley, and Jeff Yetter. Alexander Elkins designed the clock chip and Dale Beucler, Doug DeBoer, Lou Dohse, Charlie Konlhardt, John Spencer, Bill Terrell, and John Wheeler designed the 128K-bit RAM chip.

Hai Vo-Ba was responsible for the layout of the finstrates. The Memory/Processor Module's mechanical design and the internal boards were designed by Madi Bowen, Jerry Kaufman, John Moffatt, Severt Shands, Gary Taylor, and Guy Wagner. Craig Mortensen and Ed Weber developed chip design tools which were run by the computer operators—Bev Raines, Binh Rybacki, and Kathy Schraeder. Special test hardware and software were developed by Brady Barnes, Richard Butler, Doug Fogg, Bob Miller, and Walt Nester.

The NMOS process development team included Rod Alley, Jim Barnes, Jeff Brooks, Doug Crook, Fung-Sun Fei, Barry Fernelius, Dave Forgerson, Tony Gaddis, Larry Hall, Norm Hendrickson, Ulrich Hess, Gary Hong, Dan Kessler, Rajendra Kumar, Fred LaMaster, Zemen Lebne-Dengel, Rick Luebs, Bob Manley, Carol McConica, Jim Mikkelson, John Moffatt, Ken Monnig, Don Novy, David Quint, Jim Roland, Dana Seccombe, Jodi Riedinger Smith, Paul Uhm, and Gene Zeller.

The photolithographic technology was developed by Howard Abraham, Skip Augustine, Keith Bartlett, Gary Hillis, J. L. Marsh, Rob Slutz, Mark Stolz, Rick Tsai, and Marty Wilson. Dave Allen, Kevin Funk and Gien Leinbach were responsible for the chip assembly process and the finstrate process was developed by Rick Euker, Derl Pratt, and Jeff Straw. The reliability of the chips and the system was the responsibility of David Leary, Arun Malhotra, and Henry Schauer.

This HP Journal issue focuses on the R&D portion of the technology development. However, the successful fabrication of VLSI chips in volume is equally determined by the manufacturing organization that supports it. We would like to thank our manufacturing organization for their enthusiastic support, especially Ray Cozzens, Cliff Doyle, Jim Drehle, Gary Egan, Jerry Harmon, and John Mahomey.

Special recognition and thanks go to our secretaries Carol Miller and Lavonne Gardner.

HP's Cupertino Integrated Circuits Operation and Hewlett-Packard Laboratories helped us solve some of our process development problems. In addition, special recognition should go to the key managers who continually supported this development. They include Jack Anderson, Doug Chance, Christ Christopher, Don Schulz, and Fred Wenninger.

## An 18-MHz, 32-Bit VLSI Microprocessor

by Kevin P. Burkhart, Mark A. Forsyth, Mark E. Hammer, and Darius F. Tanksalvala

HE HEART OF HP's new 32-bit VLSI computer system is the Memory/Processor Module. The central processing unit in this module is an NMOS circuit containing 450,000 transistors on a single chip operating at a clock frequency of 18 MHz.<sup>1</sup> This compact CPU chip, which implements a 32-bit version of the HP 3000 Computer's stack-based architecture, is designed and microprogrammed to support multiple-CPU operations within a single Memory/Processor Module. Each CPU is capable of one-MIPS (million instructions per second) performance with very little performance degradation in multiple-CPU configurations.

#### Chip Organization

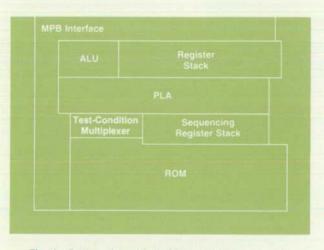

Fig. 1 shows the layout of the major functional components on the CPU chip. The data path area containing the ALU, register stack, and memory processor bus (MPB) interface is devoted to user- and system-level information processing. Two data buses within the data path link the ALU and the general-purpose register stack.

**Register Stack.** The register stack contains 31 registers used for machine instruction handling, general-purpose data storage, system addressing, and system status. Three registers are devoted to the machine instruction pipeline where special logic is included to predecode opcodes. Several registers in the stack hold the base and limit addresses for the data and program stacks in memory. Circuits are included to select the appropriate address base register automatically when address offsets are computed.

Four registers locally store the top values in the current data stack to allow fast access to often-used operands. Special-purpose hardware monitors one data bus for certain conditions such as zero, positive, and negative, and drives branch qualifier lines to the test-condition multiplexer. This data bus connects the register stack to the MPB interface.

Fig. 1. Outline of the 32-bit CPU chip indicating major sections of the chip's architecture. which handles all data transfers between the CPU and the memory and other processors.

Since the MPB interface has its own data registers and control logic, internal CPU processes can initiate transfers and continue operation while the interface handles the MPB's complex synchronous protocol. The interface has dual-channel capability so that two completely different bus transactions can be in progress simultaneously.

ALU. The arithmetic logic unit provides a wide range of single-state, 32-bit arithmetic, logic, and shift operations. Operands can be selected from the main data path or the ALU's internal buses, and one of the operands can be complemented. The shifter provides up to 31-bit right/left arithmetic or logical shifting during one clock cycle. The logic function unit performs the OR, AND, and XOR operations on the operands and the adder provides their sum with carry-out and overflow bits. Master/slave result latches store intermediate results and return data to the register stack buses.

Sequencing Register Stack. Control circuits dominate the center area of the CPU chip. This control area contains a programmable logic array (PLA) microinstruction decoder, a test-condition multiplexer, and a 14-bit sequencing register stack which generates the 14-bit microinstruction addresses going to the control store. Address capabilities of the sequencing stack include short and long jumps, subroutine jumps and returns, traps to subroutines, address incrementing, and skips.

A mapping ROM generates microcode start addresses for all machine instruction formats and opcodes. The CPU machine instruction mapper includes an opcode PLA that can be programmed to select opcodes from any combination of bits in a 16-bit opcode. By altering the opcode PLA programming, the CPU can be remicroprogrammed to execute other stack architecture instruction sets. The output of the opcode PLA is an address into one of the 256 14-bit locations in the mapping ROM.

**PLA.** The central PLA decodes microinstructions and sends control signals to the data registers, ALU, MPB interface, and sequencing register stack. Microinstructions are divided into fields, each field specifying control for a different section of the CPU.

**Test-Condition Multiplexer.** An integral part of the PLA is the test-condition multiplexer. This multiplexer uses one microinstruction field to select a control qualifier from the data path registers, ALU, or MPB interface. Conditional microinstruction branches are taken by using the qualifier to control the address issued by the sequencing stack.

**ROM.** CPU control store consists of a 9216-word ROM organized in 32-word pages. During each clock state, the micropage address selects one page. A word address is issued during the following clock state to select one of the words on this page. With this ROM design, branches such as skips and short jumps on the current page execute without interrupting the pipelined flow of microinstructions. Any jump off the current page results in one NOP clock state while the new page is selected. Microinstructions are transferred from this ROM to the central PLA by a 38-bit bus.

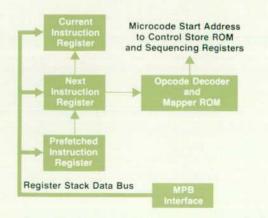

#### **Typical Operation**

The execution of a machine instruction begins when it is prefetched from memory and placed in the machine instruction pipeline registers (see Fig. 2). As the currently executing instruction completes, this prefetched instruction is moved up the pipeline into the next-instruction register and copied into the decoder-mapper in the microsequencing hardware. Meanwhile, execution of the immediately preceding instruction is initiated and another instruction is prefetched. Finally, this instruction is transferred to the current-instruction register and the appropriate starting microcode address is issued from the decoder-mapper. Instruction fetch, decode, and execution are performed in parallel except when a branch occurs.

Microcode from the control store ROM implements all machine instructions and performs the prefetch to keep the instruction pipeline full. The fields in each microinstruction are decoded by the central PLA, which sends control signals to the registers and ALU to move and process data. The MPB interface's dual-channel capability allows the currently executing instruction to fetch data on one channel while the instruction prefetch is in progress on the other channel.

Data fetched from memory is stored in general-purpose data registers in the CPU data path. Two parallel data buses within the data path simplify the transfer of operands to the ALU and the MPB interface. During each clock cycle, the ALU selects its operands and then performs an arithmetic operation and a logic or shift operation in parallel. Either or both results can be saved in the result registers, returned to the register stack, and/or used as operands during the next cycle. More complex operations such as multiplication or floating-point arithmetic are accomplished by sequences of microcode.

#### Features and Performance

The internal CPU data paths and registers, which carry and store user data and instructions, have full 32-bit widths. The CPU implements a stack-based architecture with a

Fig. 2. Block diagram showing arrangement of the machine instruction pipeline registers. machine instruction set consisting of 230 instructions in 16-bit and 32-bit formats. Two 32-bit buses link the 31 general-purpose registers with the ALU and the MPB interface. The ALU has two internal 32-bit registers and three internal buses. Typical IEEE-standard floating-point execution time is 5.94  $\mu$ s for a 64-bit addition and 10.34  $\mu$ s for a 64-bit multiplication.

The CPU sends and receives data on the MPB which links the CPU to the other CPUs, I/O processors, and main memory in the Memory/Processor Module. The basic data word is 32 bits, but byte, half-word, and double-word load and store instructions are supported within a direct 500megabyte address range.

The microinstruction bus linking the control store ROM and the PLA decoder transfers one 38-bit microinstruction every 55 ns. The control store ROM on the CPU chip contains 350K bits divided into 288 pages. Each page contains 32 words, each 38 bits wide. This ROM has a 70-ns access time, which includes a 20-ns final word select time.

Special microinstruction sequencing hardware provides addresses to the control store every 55 ns and minimizes the use of microcode fields for address control. Conditional jumps and subroutine calls in microcode are handled by the sequencing hardware to off-load these tasks from the ALU's main data path. The sequencing stack contains six registers, three incrementers, a comparator, a 10-by-14-bit trap ROM, a 256-by-14-bit mapping ROM, and an opcode PLA with 16 inputs, 120 product terms, and 8 outputs. The sequencing stack is interconnected by two 14-bit buses and one 5-bit true-complement word-select bus.

The pipelined microinstructions are divided into seven fields of five or six bits. Different microinstruction formats multiplex the different fields and constants into a single 38-bit word to enhance the efficiency of microcoded routines. These formats are decoded in the PLA based on the opcode in the 'special' field. The PLA microinstruction decoder, which consists of 55 inputs, 508 product terms, and 326 outputs, performs two-level decode logic in 55 ns.

#### **Design for Testability**

The complexity of the chip presented some very difficult testing challenges—fault coverage of a 450,000-transistor circuit with nearly 300,000 nodes, characterization at clock rates up to 24 MHz, verification of 350K bits of on-chip firmware, and providing process feedback from the first design in a new IC technology. Relying on commercially available LSI testers to solve these problems was not feasible because of their high cost, limited interactive diagnostic capabilities, and performance limitations. To provide a fast screen and detailed diagnostics under realistic operating conditions at low cost, it was necessary to incorporate most of the needed test capability into the chip's design.

Several key concepts are involved in the built-in testability of the CPU chip. A structured design methodology and a bus-oriented architecture allow substantial partitioning. Since all of the inputs and outputs of the individual circuits are connected to at least one of the major internal buses, every circuit can be individually controlled and observed by communicating with only a small number of data and control buses. A structured design separates circuits into distinct functional blocks, and a building-block approach

### Instruction Set for a Single-Chip 32-Bit Processor

#### by James G. Fiasconaro

Fitting the entire CPU for a powerful 32-bit computer on a single manufacturable IC was a formidable task by any standard. This task was accomplished, in part, by encouraging the engineers who were designing and implementing the hardware and the instruction set to make the necessary tradeoffs between the two, but always with a thought towards the performance of the resulting chip. The present design is the result of many optimizing iterations. The hardware contains thirty-nine 32-bit registers, a 32-bit shifter, a 32-bit ALU, and 9K 38-bit words of microcode control store. It executes microcode at an 18-MHz rate.

The instruction set is stack-oriented. Each program has its own execution stack for allocating local variables, passing parameters to other procedures, saving the machine state on procedure calls, and evaluating expressions. There are instructions for pushing data onto the stack from memory, and for popping data from the stack and storing it in memory. Arithmetic instructions operate on the uppermost data words in the stack and leave their results on the stack. Instructions that operate from a set of parameters get these parameters from the top of the stack.

Segmentation is used to support virtual memory in the CPU instruction set. Every program can use up to 4096 code segments and 4096 data segments, and must use at least three segments-a code segment, a stack segment, and a global data segment (Fig. 1). Three pairs of 32-bit registers on the CPU point to the start and end of each of these three segments. These are the base and limit registers shown in Fig. 1. Another register, the program counter, points to the current instruction in the code segment, and two other registers point into the stack segment. The Q register points to the most recently pushed stack marker and the S register points to the uppermost 32-bit word in the stack. Four other registers on the CPU are used as a cache memory for the top four words in the stack, greatly reducing the number of reads and writes necessary to maintain the stack in memory. The information required to manage the segments used by each program is maintained in memory-resident tables. Each program has its own code and data segment tables and one common set of system code and data segment tables is shared by all programs.

Each code segment table entry contains the location and length of the segment, an absence bit, a privileged mode bit, a reference bit, and a use count. The use count indicates how many CPUs in the system are using the code segment at each point in time. Two primary instructions using the code segment tables are PCL (procedure call) and EXIT. PCL pushes a four-word stack marker, which contains the index register, the status register, the offset to the preceding stack marker, and the return address, onto the stack and transfers control to the new procedure. EXIT does the reverse and returns to the calling procedure. Both instructions also do a considerable amount of error checking.

Each data segment table entry contains the location and length of the segment, an absence bit, a privileged mode bit, a reference bit, a dirty bit, a write enable bit, a paged bit, a page-size field, link information, and a use count. Unlike code segments, data segments can be paged (with the exception of a program's stack and global data segments). Each program can access up to 4096 data segments through an external data segment pointer. If the segment is not paged, this pointer is interpreted as a 12-bit segment number and a 19-bit offset within the segment. (Segment length can be up to 2<sup>29</sup> bytes.) If the segment is paged, this pointer is interpreted as a 31-bit virtual address with a 12-bit segment number, a page number, and an offset within the page. The page size can be chosen by the operating system in powers of two up to 2<sup>15</sup> bytes. For paged segments, the data segment table entry points to a page table that contains a two-word entry containing location and status information for each page. Unpaged segments can be linked together and treated as a single logical entity, either by allocating the individual segments in consecutive data segment table entries, or by letting each data segment table entry point to the next entry in the chain.

Because the instruction set is stack-oriented, many instructions (e.g., ADD, SUB, AND, and OR) operate on the uppermost words in the stack and do not require any source or destination specification. Instructions that push information onto the stack and pop information from the stack use direct, direct indexed, indirect, or indirect indexed addressing. Direct addressing uses a base register and an offset specified in the instruction. Direct indexed addressing is similar except that the index register (a 32-bit two's-complement byte offset) is also added. Indirect addressing starts with the direct addressing calculation and fetches the indicated word from memory. This word is interpreted as a stack segment pointer, a global data segment pointer, or an external data segment pointer. Stack and global data segment pointers are simply offsets from the stack base and data base registers. External data segment pointers are evaluated through the data segment tables as described earlier. Indirect indexed addressing is like indirect addressing except that the index register is added after the indirect pointer is evaluated.

The instruction set provides a full repertoire of load and store instructions for bit, byte, half-word, word (four bytes) and double-word quantities using the addressing modes just described. All memory accesses using these instructions are bounds checked against program base and program limit, stack

•

base and S register, data base and data limit, or the location and length information in a table as appropriate. A bounds violation causes a trap to the operating system. Stores into code segments are not allowed. In unprivileged mode, a user can access only the user's own code, stack, global data and external data segments. The instruction set also provides a set of privileged load and store instructions which use absolute addresses instead of segment base and offset information to access memory.

The primary data types supported by the instruction set are integers, floating-point numbers, and byte strings. Integers can be either 16-bit or 32-bit two's-complement numbers, 32-bit unsigned integers, or eight-digit unsigned decimal integers. The basic operations for add, subtract, multiply, divide, negate, compare, shift, and rotate are provided along with provisions to facilitate multiprecision (i.e., greater than 32-bit) integer arithmetic. Instructions that use one integer from the stack and an 8-bit immediate operand in the instruction are also provided.

Two types of floating-point numbers are supported. The first type includes 32-bit and 64-bit IEEE-standard binary floating-point numbers. The standard is met by supporting performancecritical operations directly in microcode and all other operations either directly by the operating system or by traps from microcode to the operating system. The second type is a 17-digit decimal format; only conversions between this format and the 64-bit IEEE-standard format are supported.

Both structured and unstructured byte string operations are supported. Unstructured strings are simply byte arrays. A set of move, scan, and translate instructions is provided to support this data type. Structured byte strings correspond to the string data types found in most high-level programming languages. These strings are accessed through a four-word string descriptor containing a pointer to the string, its maximum length, an index to the first byte of interest, and the number of bytes of interest. The current length of the string is stored in the first four bytes of the byte array containing the string. Instructions to load, concatenate, validate, and assign structured byte strings are supported.

The instruction set interacts with the operating system in two primary ways. The first way is through traps to code supplied by the operating system. When the microcode encounters a situation that it cannot handle, it traps to a prearranged entry point in a prearranged code segment. There are two broad categories of traps. The first category consists of error conditions. Examples include segment bounds or table length violations, privileged mode violations (attempts by unprivileged programs to execute privileged instructions or access privileged information), integer divide by zero, and system errors. The second category consists of situations that require operating system intervention. Examples

limits the number of different blocks.

To use these architectural features for testing purposes, a small amount of diagnostic support circuitry was added to the chip. The microinstruction register, one data register connected to an internal data bus, and an internal opcode bus were modified to allow loading or dumping serially through a single bus line. These registers can directly or indirectly control all of the internal data, address and control signals on the chip. Modifications to the microsequencing state machine provide the ability to halt or single-step microcode execution in a manner transparent to the microprogram being executed. This is done by using latches on all test qualifiers and recirculating data on internal buses.

A diagnostic interface port was added to facilitate control of the internal test features. This port consists of seven of the include absent segments, pages, and page tables, stack overflow, floating-point mathematics traps, attempts to execute unimplemented instructions, and traps to support a set of high-level language debugging aids.

The second way the microcode interacts with the operating system is through a set of instructions. These instructions are primarily involved with task dispatching and I/O. This approach supports getting to and from the dispatcher and I/O driver code, assists some of the low-power operations which the dispatcher and I/O drivers must perform, and provides a special stack for the dispatcher and I/O drivers. The details of the algorithms used in the dispatcher and I/O drivers were left for the operating system to implement in machine code. This approach provides a good tradeoff between speed and flexibility.

The I/O interrupt handler provides sixteen I/O interrupt levels. At each level, I/O interrupts are handled on a first-come-first-serve basis. This is accomplished in cooperation with the I/O processor (IOP) chip by maintaining a linked list of all of the devices waiting for service at each priority level. The IOP logs devices at the end of each list and the CPU removes devices from the head of each list. Finally, provisions are made so that any CPU in a multiple-CPU system can handle any I/O interrupt.

Table I lists typical instruction times for a few CPU instructions. However, these times do not tell the whole story because up to three CPUs can be included in each Memory/Processor Module. Support for multiple-CPU systems was built into the instruction set from the very beginning. This support occurs primarily in the areas of dedicated memory locations, interrupt handling and manipulation of the code and data segment tables in memory. This support guarantees exclusive access to system information when necessary and facilitates implementation of efficient memory management in the operating system.

#### Table I Typical Instruction Times

| Instruction                           | Time (µs) |

|---------------------------------------|-----------|

| Direct Load                           | 0.56      |

| Integer Add                           | 0.28      |

| Integer Multiply                      | 2.9       |

| Integer Divide                        | 9.4       |

| 64-Bit Floating-Point Add             | 6.0       |

| 64-Bit Floating-Point Multiply        | 10.4      |

| 64-Bit Floating-Point Divide          | 16.0      |

| Procedure Call (to same segment)      | 3.3       |

| Procedure Call (to different segment) | 7.8       |

|                                       |           |

CPU chip's wire-bond pads: four opcode-bit pads, a serial I/O pad, an output pad, and a synchronizer input pad. The four opcode bits are connected to PLA inputs and used to control the serial shift registers and alter normal microinstruction sequencing. Data is loaded into and dumped from the internal registers via the serial I/O pad. The output of the test multiplexer can be observed via the output pad. The synchronizer input pad allows asynchronous communication between the diagnostic port and an external tester. The opcode bits are only executed once each time the synchronizer input is pulsed, which enables a relatively slow computer to communicate with and control a CPU running at a much higher clock frequency.

These features form an extremely powerful set of diagnostic tools. Operations that can be controlled through the

diagnostic port include setting microcode breakpoints, single-stepping microcode, loading and examining internal registers, and executing externally supplied microcode. The chip partitioning allows testing and characterization of a single circuit regardless of whether other circuits on the chip are functional. This capability proved to be essential in verifying a design of this complexity.

Testing chips in a production environment requires a high-speed pass/fail screen. To do this, a 100K-bit self-test microprogram was encoded into the CPU's ROM. This microprogram executes in twenty million clock cycles and outputs a series of pulses through the diagnostic port to indicate functionality of each major section of the chip. In addition to the standard instruction set, the self-test uses a set of microinstructions designed specifically for testing. Greater than 95% coverage of 'stuck-at....' faults is achieved, and a variety of other potential defects such as storage node leakage, pattern sensitivities, and timing problems are covered as well. The self-test microprogram is executed whenever the chip is powered up, so it can be used for system verification and field tests besides wafer tests.

A feature of the architecture allows the CPU to communicate with itself via independent pad drivers and receivers connected to each of the MPB interface pads. Functional pad testing can thus be accomplished without the need for external, expensive, high-speed test electronics. However, if required, various loads can be connected to the circuit's pads during testing to simulate a system environment.

System-level hardware and software verification are also addressed by the built-in test features. A flip-flop controlled through the diagnostic port can put the CPU in a mode where it enters a transparent idle state at the completion of each machine instruction. This allows instructions to be single-stepped. Special microcode routines to provide breakpoint, variable tracing, and other software verification features are programmed into the CPU's ROM. Low-level system debugging can be done by executing microinstructions supplied through the diagnostic port to drive and monitor the system bus.

#### Acknowledgments

The CPU development effort was carried out at Hewlett-Packard's Systems Technology Operation in conjunction with the Engineering Systems Division. The initial phase of development was carried out under the guidance of Chris Christopher and Joe Beyers, and later development efforts were managed by Craig Mortensen and Lou Dohse.

#### Reference

1. J. Beyers, et al, "A 32b VLSI Chip," Digest of Technical Papers, 1981 IEEE International Solid-State Circuits Conference, THAM 9.1.

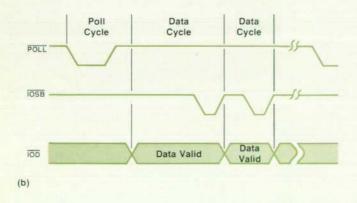

## VLSI I/O Processor for a 32-Bit Computer System

by Fred J. Gross, William S. Jaffe, and Donald R. Weiss

P'S 32-BIT VLSI computer system requires a highperformance input/output data path. The design objectives for the I/O path were to provide high data rates to peripheral devices to match the high performance of the CPU and to minimize the design effort. An I/O processor (IOP) able to control most I/O transactions without interfering with the CPU was chosen because it met the performance objective, and by using the same circuits and basic structure as the CPU chip, also met the second objective. As a side benefit, the first production runs of each chip served to test the other chip's design and establish a common reliability record for the shared circuits.

The I/O processor has an I/O bus bandwidth of 5.1M bytes/s when transferring at maximum rate. The IOP is capable of addressing eight device adapters, also known as I/O cards. Each device adapter has its own DMA (direct memory access) resource. There are sixteen levels of interrupt assignable to device adapters. The IOP is also capable of independently executing simple channel programs.

A microcode-controlled state machine gives the I/O processor enough power to perform all of its I/O tasks. A 38-bit microcode word with eight subfields allows simultaneous control of the I/O processor's internal registers and external control lines.

#### Operation

Operation of the I/O processor is directed by the CPUs in the computer system. The IOP alternately checks for a command from any CPU in the system or for a valid service request from any enabled device adapter. A CPU communicates with an IOP by sending it a command word and a data word. Embedded in the command word is the requesting CPU's return address. This allows all CPUs in a system to use any IOP. Commands sent from a CPU can set up DMAs, read registers on the IOP, or do direct I/O with a device adapter. Complex tasks that an IOP cannot handle independently result in CPU interrupts.

The IOP is connected to other processors and memory via

the memory processor bus (MPB). The MPB interface is a 32-bit pipelined interface with a synchronous protocol that allows overlapped memory fetches. It has its own registers and control logic, which hide its complex protocol from the IOP's register stack and control logic. This improves performance by allowing internal operation in parallel with memory operations. The MPB interface on the IOP chip is identical to the one on the CPU chip.

The IOP's I/O bus connects it to the device adapters. The new I/O bus protocol for the IOP is called HP-CIO for Hewlett-Packard Channel Input Output. The protocol was defined during the development of the IOP to provide a processor-independent, message-oriented bus.

During an IOP poll cycle, a device adapter enabled for service requests asserts a data line corresponding to its assigned address. The IOP latches the I/O bus responses, masks out any disabled devices, priority encodes the results, and then services the highest numerical address.

Service consists of transferring bytes or half-words (two bytes) which can be either data or commands. During the transfer, the address lines select one device adapter and the data direction line indicates who will be the data sender. The end of a transfer is signaled by the trailing edge of the I/O strobe IOSB, which the device adapter uses as a clock when receiving data or as a signal to assert the next data when sending data.

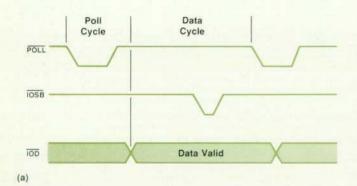

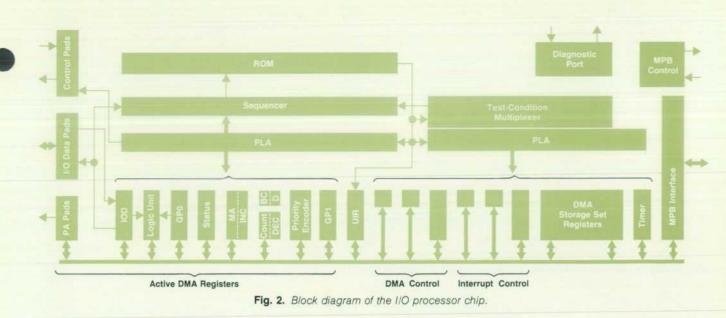

A poll cycle on which a single data transfer occurs is called a multiplex cycle and a cycle on which multiple data transfers occur is called a burst cycle (Fig. 1). A burst cycle increases I/O bus bandwidth because more bytes are trans-

Fig. 1. Timing diagram for (a) multiplex and (b) burst I/O cycles in the I/O processor.

ferred per poll cycle. The bandwidth reaches a maximum of 5.1M bytes/s in burst mode and 973K bytes/s in multiplex mode. When a poll is won by a device adapter for DMA, it has the option of asserting burst request BR. A device adapter in burst mode can take any number of transfers between two and thirty-two by asserting and then unasserting BR at the appropriate times. To reduce the lock-out time to an acceptable level, the IOP limits the number of transfers per poll cycle to no more than thirty-two.

The width of the data word (byte or half-word) on the I/O bus is determined by the data sender. If the IOP is transferring in byte mode, channel byte CB is asserted to indicate to the device adapter that only the least-significant eight bits of the data bus are valid. If the device adapter is transferring in byte mode, device byte DB is asserted.

CPU interrupts are usually the result of either a DMA termination or a device adapter service request that cannot be handled by the IOP. When an interrupt occurs, the IOP records a device adapter interrupt request at the end of a linked list in memory for the interrupt level it is on. (This level is assigned by the CPU and stored in the status register for a particular device.) A message is then sent to the CPU to indicate that an interrupt was recorded for that particular interrupt level. When the CPU completes its current instruction, it services the highest-level list, starting at the list's beginning.

The CPU can configure itself to accept all interrupts, all interrupts above a certain level, or no interrupts. Each IOP has a register for enabling interrupts for any or all device adapters. A register on the IOP determines whether a particular CPU gets the interrupt request, or if all CPUs in the system get the interrupt request. In the latter case, the first eligible CPU available services the interrupt.

CPU commands not requiring a response can be placed in a list in memory for the IOP to execute. These lists are called channel programs. Each entry consists of a command word and a data word. The fourth word of the device reference table contains a pointer to the next executable command in the channel program. Each device adapter for every IOP has its own unique table in memory. When a status bit is enabled for a particular device adapter, the IOP executes one command per poll cycle when there are no CPU commands or service requests. A typical channel program allows multiple data transfers from different memory addresses to take place without interrupting the CPU. The logical completion of a channel program usually results in an interrupt.

#### I/O Processor Design

The IOP consists of a microcoded control section implemented with an internal ROM, an address sequencer, and a PLA decoder, a register stack of 44 registers connected by a common bus, the MPB interface, and an I/O interface. A block diagram of these sections on the IOP chip is shown in Fig. 2.

The control store is a 4608-by-38-bit, series-FET ROM with two-state pipeline access. In the first state of the pipeline, a page address is issued to select one 32-word page of the 144 possible pages. In the second state, the word address selects one of the 32 words on the selected page to be transferred to the PLA via a 38-bit bus. Branches within the current page do not interrupt the pipeline timing be-

cause the new word address is selected in the first state. Only jumps off the current page cause the pipeline to be restarted. The IOP only needs a ROM one-half the size of the CPU ROM. Structuring the CPU ROM into two equal arrays simplified the conversion to the IOP design.

The ROM address sequencer computes the 13-bit address of the next location to be fetched from ROM. In normal sequential access the previous address is incremented, but nonsequential addresses can be selected from either the previous instruction's branch target, the top of a subroutine stack, or a trap ROM. The address sequencer circuits are the same as those used for the CPU, but to conserve space, the opcode mapper circuit is deleted.

The PLA decodes the microcode words from the control store ROM and generates over 230 signals to control the IOP. The PLA is implemented with dynamic NOR-NOR logic for high performance, high density, and low power consumption. The IOP PLA is specially programmed for the IOP architecture, but the low-level building-block circuits for its design are identical to those used in the CPU's PLA.

The test-condition multiplexer controls conditional branching in the ROM address sequencer. It consists of static latches to sample and hold status information or external qualifiers, and a series-FET multiplexer to select the proper qualifier for the conditional branch.

The eight subfields in the 38-bit microcode word are classified as test, special, bus drive, bus receive, and four I/O controls. This word structure allows handling the unusual task of simultaneously directing data flow internal to the IOP while providing the appropriate I/O timing signals. In many cases I/O timing is adjusted by merely adding or deleting NOP (no operation) words to the microcode.

The register stack is made up of registers from 4 to 32 bits in length and a logic unit. The registers are divided into an active set that contains information about the DMA currently in progress, and a storage set that holds DMA information for all eight device adapters when DMA is not active. The active DMA registers consist of a memory address register with an incrementer, a count register with a decrementer, a burst count register with a decreregister with bits testable by the test-condition multiplexer, and an I/O data transfer register. When a DMA becomes active, the memory address, count, and status register values are transferred from the storage set to the active set. Each device adapter has a data register on the IOP chip to eliminate the need for a memory access before a data transfer. Response time to a DMA request is greatly improved since all information is contained on the IOP. When the transfer or transfers are completed, the new register values are stored in the storage set and the data buffer is filled or emptied.

The logic unit on the IOP replaces the powerful ALU found on the CPU. The bit-set/clear function performs a logical AND, OR, or exclusive-NOR between the IOD and GPO registers and places the results on the common bus. The constant function can set any of the sixteen leastsignificant bits on the common bus. The compare function compares 32, 16, or 8 bits of the IOD and GPO registers and sends the results to the test-condition multiplexer.

The I/O bus hardware consists of data drivers and receivers, address register and drivers, control drivers, and input qualifiers. The data drivers buffer the IOD register contents for output and are in a high-impedance third state during input operation while data is latched in the IOD register. The pad driver has a push-pull output stage designed to drive a load of 15 to 20 pF. The lines are buffered by external high-speed bipolar devices. This design has the advantages of being able to drive a large bus capacitance quickly without requiring a large IC chip area and of isolating the MOS lines from damage caused by static discharge. Input receivers consist of a protection device and a regenerative latch. The latch ensures proper system operation by resolving the input level before the internal test-condition multiplexer tests it.

The diagnostic port is a seven-line serial interface used for testing and diagnostics. It is identical to the one used on the CPU and allows the CPU and IOP to be tested on the same custom tester.

#### Self-Test

When power is applied, the IOP turns on its self-test

indicator and performs a self-test of its hardware using microcode routines programmed in its ROM. The routines are classified as internal test, I/O interface test, channel-tochannel test, and memory test. The internal test functionally tests all registers, operations, and sequencing. The I/O interface test sequentially sets and clears all output control lines and tests their level by a separate input. All inputs are driven high and low by special outputs and tested to ensure that they are functional. The channel-to-channel test causes the IOP to send data to itself via the MPB. Finally, if the CPU sends a message to the IOP indicating that there is working memory in the system, the IOP tests its ability to write to and read from memory. After the successful completion of all tests, the IOP turns its self-test indicator off.

## **High-Performance VLSI Memory System**

by Clifford G. Lob, Mark J. Reed, Joseph P. Fucetola, and Mark A. Ludwig

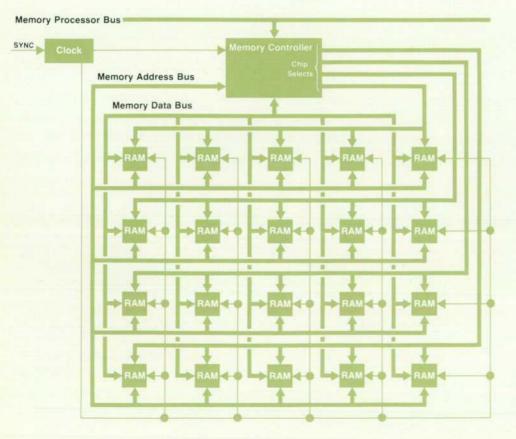

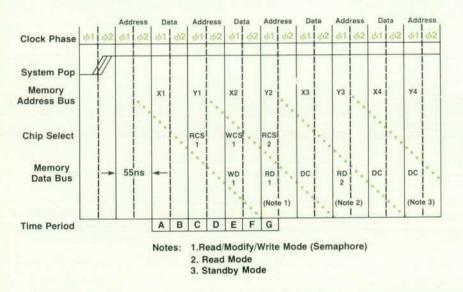

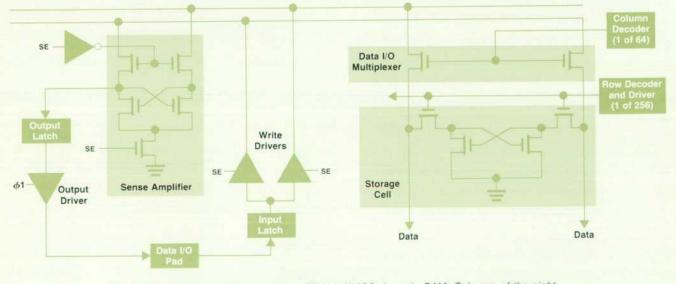

MPLEMENTING A HIGH-PERFORMANCE memory for HP's new 32-bit VLSI computer system requires the achievement of several important design goals to realize the full potential of this VLSI architecture. A dense resident memory and a large virtual address capability is desirable. A large memory bandwidth is needed to support multiple CPUs and I/O processors (IOPs) without creating bottlenecks. Also needed is the ability to do flexible memory operations such as byte, half-word, word, semaphore transfer, and refresh functions that are transparent to the CPU, IOP, and operating systems. Fig. 1 shows a block diagram of a memory card for the 32-bit VLSI computer system. The key elements are the memory processor bus (MPB), MPB interface, memory controller chip, 128K-bit dynamic RAM chips, and clock chip.

Each memory card has twenty RAM chips organized in four rows of five chips each. Each RAM chip supplies 128K bits of memory storage and the memory card provides 256K bytes of total storage. Thus, a Memory/Processor Module can contain up to 2.5 megabytes of memory if it uses only one CPU and one IOP, and memory cards are inserted in all of the module's ten remaining empty slots.

Fig. 1. Block diagram of highperformance VLSI memory system.

To achieve a large virtual address space, the 32-bit address has three bits of format control, allowing the remaining 29 bits to be used for addressing up to 2<sup>29</sup> bytes. In addition, virtual memory support is provided by the CPU's microcode and instruction set.

The memory controller chip and the RAMs communicate via an 8-bit memory address bus, the 39-bit memory data bus, and a chip select (CS) line. Each row of five RAM chips has its own CS line, and the memory controller chip is connected to each row. Except when doing a refresh, the chip asserts only one CS line at a time. The memory address bus (MAB) and CS lines are driven only by the memory controller chip. The memory data bus (MDB) is bidirectional; write data is driven by the memory controller chip and read data is driven by the RAMs.

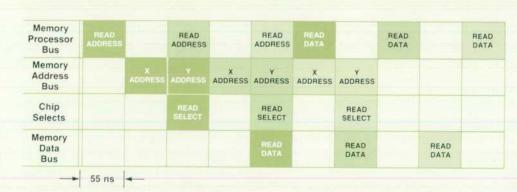

A large memory bandwidth is achieved through the MPB interface protocol, the pipelined nature of the RAM chip, and 18-MHz operation. Fig. 2 shows the timing for three read cycles. The internal pipeline design of the RAM allows it to accept a second address before handling data for the first address, and to issue read data nine million times per second. This allows the processors to issue three nonsequential data address requests without waiting for the first data word. Multiple processors, through a priority polling scheme, can interleave data.

After the polling sequence is completed, a memory address is sent on the bus and a read operation is indicated. The memory controller issues an 8-bit X address and a 6-bit Y address in succession on the memory address bus and generates the appropriate chip select CS. The RAM then decodes the address and outputs data onto the memory data bus. The memory controller corrects and aligns the 39-bit data word from the RAM row and outputs a 32-bit data word to the memory processor bus.

A single CPU can use no more than 65% of the bandwidth of the memory system. During normal operation, a CPU uses 30% of the bandwidth. In a system with multiple CPUs or CPUs with IOPs, the full bandwidth of 36M bytes/s can be completely used.

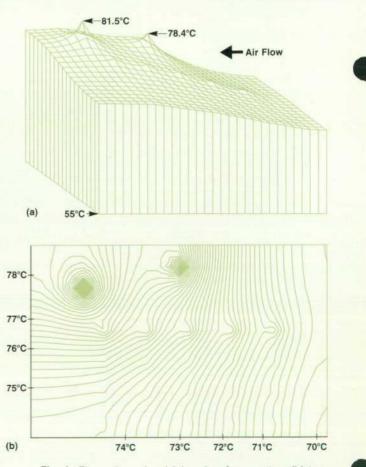

Important to packaging of the memory system is the finstrate board onto which the memory controller, RAM, and clock chips are mounted. Using forced-air cooling, the junction temperatures of the RAMs on an active memory card will not exceed 90°C, even under the following worst case conditions: 55°C ambient, 15,000 ft altitude, low fan voltage, and a fully loaded Memory/Processor Module. These low junction temperatures contribute to the excellent reliability of this memory system. Flexible memory operations and high reliability and availability are implemented in the memory controller chip. This chip is controlled by a PLA (programmable logic array) for speed. It contains three separate synchronous state machines that control self-test, 'healing,' and normal memory controller operations. The chip dissipates up to five watts and has a total of 119 wire-bond pads.

In addition to refreshing the RAM chips, the memory controller performs the following functions:

- Aligning (reading and writing) of bytes and half-words

- Implementing semaphores by using the RAM capability of reading and writing in the same cycle

- Mapping logical addresses to physical memory

- Correcting single-bit errors and detecting double-bit errors on the fly

- Healing bad memory locations by replacing them with other on-chip memory locations

- Testing itself and the RAM chips.

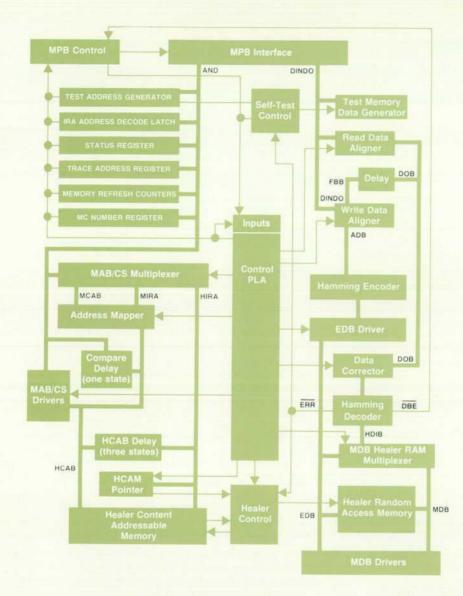

#### Memory Controller Chip

Fig. 3 shows a detailed block diagram of the memory controller chip. The MPB interface handles the MPB protocol and routes addresses and data into and out of the chip. The mapper contains 32 CAMs (content addressable memories) and issues chip selects and part of the Y address. The MAB/CS drivers and multiplexer handle time multiplexing of X (row) and Y (column) addresses and read and write chip select signals. The MDB drivers and multiplexer handle time multiplexing of read data from, and write data to the RAMs.

The healer block also contains 32 CAMs. When an error is detected in memory, the healer places the physical address of that location in one of its CAMs so that substitution will be made for all subsequent accesses to that address.

The data manipulation section contains a Hamming encoder which attaches seven check bits to the 32-bit write data, a Hamming decoder which detects the position of a single-bit error and the existence of a double-bit error, a data corrector which corrects the single-bit error, and byte aligners which extract bytes and half-words from memory in nonword read operations and place bytes and half-words into memory for nonword write operations.

The MPB protocol is based upon polling for address/data bus cycles, and a master-slave synchronous handshake. During power-on, each CPU and IOP is assigned a nonzero channel number based on its physical position in the Memory/Processor Module. This channel assignment can be altered by the operating system to give highest priority to

Fig. 2. Memory system timing. The different shades indicate three separate, but interleaved read cycle operations.

the processors requiring the most bandwidth for their tasks. The protocol allows for eight priority-assigned channels with 0 the highest priority and 7 the lowest priority.

Each memory controller is hardwired to channel 0, and is given a unique number (MC#) by the power-on procedure.

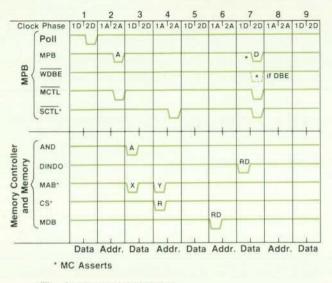

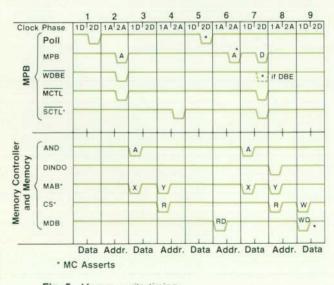

Figures 4 and 5 show protocol timing for read and write operations. The highest-priority channel responding to a poll wins the bus cycle, asserts the address on the next state,\* asserts MCTL (master control) indicating a valid address, and, if this is a write operation, asserts WDBE (write/ double-bit error). Two states later, the addressed slave asserts SCTL (slave control) to signify that it recognizes the address and currently is not busy. Three states after that, the data is asserted on the bus—by the slave if the transaction is a read, and by the master if it is a write. The slave asserts SCTL to signify that it can complete the transaction and the master asserts MCTL to signify that it can complete the transaction.

As a processor on the MPB, the memory controller chip has many characteristics very different from the CPU and IOP chips. Its master functions are simply to broadcast a "In this article, one bus cycle is equal to two states. message to the system, and to grab bus cycles for refreshing memory and for write operations. These chips are resident on channel 0 to guarantee that they win the bus poll cycle for these operations. In designing the chip, it was considered important that any master or slave processor functions interleave cleanly with pipelined memory accesses.

Each row of RAM chips on a memory finstrate provides 16K words of 39 bits each. Each word consists of 32 data bits and seven check bits which make up a modified Hamming code to allow single-bit and double-bit error detection and single-bit error correction. The 40th bit is not used.

A read address asserted on the MPB causes data to be returned five states later (Fig. 2). This includes time needed by the chip to perform its mapping functions, error detection, and data alignment. RAM access time is three states. However, a new access can be initiated every two states to give a 110-ns cycle time. The RAM is pipelined so that a second access can be started while another is still in progress.

#### **Read Memory Operation**

Fig. 4 shows timing for memory read operations. When

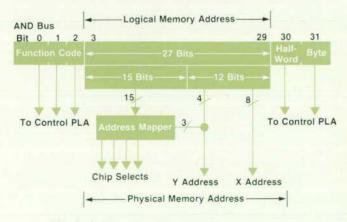

an address is placed on the MPB, it is automatically placed on the AND (address, data) bus during P1D ( $\phi$ 1 data). Parts of the address on the AND bus are processed simultaneously by many parts of the memory controller chip. An internal register access decode section checks to see if the channel field (bits 3 to 5) equals 0. It also captures address bits 6 to 10 and 23 to 29, which are pertinent to determining which memory controller chip register is accessed. The CAMs in the mapper compare bits 3 to 17 to their contents. Meanwhile, bits 18 to 29 go to the MAB/CS section and the healer, and bits 0, 1, 2, 30, and 31 go to the control PLA. In the MAB/CS section, bits 22 to 29 go out immediately to the

### **18-MHz Clock Distribution System**

#### by Clifford G. Lob and Alexander O. Elkins

Designing the high-frequency distribution system to allow HP's new 32-bit VLSI processor to operate at 18 MHz proved to be a significant design challenge. The chips required 6V, two-phase, nonoverlapping clocks with rise times less than 6 ns and overshoot/undershoot less than 1V. It was decided early in the project that, because of area constraints, the processor chips would not buffer their clocks. However the RAM chips do provide some buffering. Hence the capacitive loading components vary from approximately 300 pF per phase for a CPU chip to approximately 30 pF per phase for a CPU chip to approximately 30 pF per phase for a CPU chip to approximately 30 pF per phase for a RAM chip. In addition, the capacitive loading presented is highly variable because of the dynamic circuits used and depends on which circuits are active. Worst-case tolerances produce capacitive specifications that can vary  $\pm 30\%$  and cause unbalanced loads on each phase.

The first step in the design of the clock distribution system was the clock buffer chip. The clock buffer chip divides a 36-MHz signal and produces the two-phase, nonoverlapping clocks  $\phi 1$ and  $\phi 2$ . Large capacitive drive is required since the RAM finstrate can load the clocks with 1500 pF per phase. In addition, the clocks are required to use a system sync signal to ensure that  $\phi 1$ occurs on all finstrates simultaneously.

The chip size is 5.84 by 3.65 mm. Each large output transistor on the chip has a channel approximately 55,000  $\mu$ m wide by 2.1  $\mu$ m long and an output impedance of 0.5 ohm.

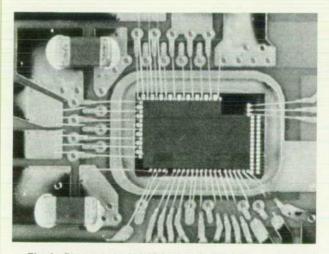

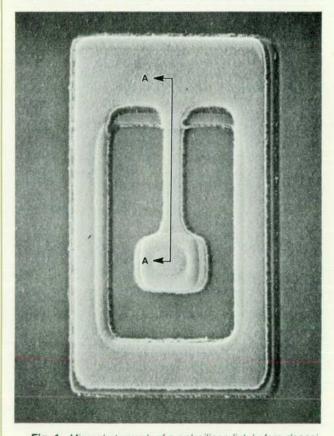

Fig. 1 shows a clock chip bonded to a finstrate and surrounded by chip capacitors used to reduce inductance and to bypass the supplies and ground. Peak currents of 2 to 3A occur when the clock switches. Multiple bonds interleaved with power supply and ground signals and multilayer chip metallization are used to reduce inductive and resistive effects.

Strip-line and microstrip techniques are used to distribute the clocks to the other chips on the finstrate. Careful attention was

Fig. 1. Photograph of 18-MHz clock buffer chip mounted in its cavity on a finstrate.

given to minimizing inductance because to achieve the clock specifications under worst-case variations, there must be less than 12 nH in series from the buffer to any chip. For comparison, a single wire bond contributes about 4 nH, and a 2-inch loop of wire is about 160 nH. Another inductance-reducing technique is the use of multiple taps per clock phase on the processor chip.

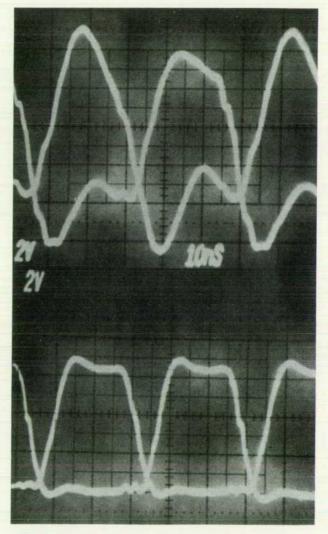

Fig. 2 shows actual clock waveforms as distributed with an earlier straightforward wiring approach, and as achieved with the tuned high-frequency design currently in use.

Fig. 2. Clock waveforms using (a) an earlier straightforward wiring approach and using (b) the present tuned high-frequency design.

Fig. 4. Memory read timing.

RAMs as the X address (see Fig. 6).

The mapper's CAM outputs drive the mapper ROM, which generates chip selects and three bits of Y address during P1A ( $\phi$ 1 address). The operating system must ensure that logical-to-physical mapping assignments are unique because these outputs are wired-OR lines. Simultaneous matches in more than one mapper CAM can cause false physical addresses. An output by any mapper CAM causes a MY (my memory) condition to be sent to the control PLA and the MPB interface. An SCTL will be given on P2A ( $\phi$ 2 address) if this MY condition occurs and the control PLA determines that this is a memory operation.

The chip select and mapped Y address go to the healer and the MAB/CS section where they go immediately to the RAM as the read CS and as the Y address on MAB 1 to 3 (MAB 0 is not used in the Y address). Bits 18 to 21 from the original address were delayed and are now issued on MAB 4 to 7 to complete the Y address.

Available on the next P1A (state six), 39 bits of data from memory go to the seven decoding trees in the Hamming

Fig. 5. Memory write timing.

decoder. The decoder delays 32 of the bits for one clock phase while it generates seven syndrome bits. The syndrome bits are true during P2A when they are presented to the data corrector along with the 32 delayed bits of read data. If the syndrome bits are zero, the data corrector puts the delayed read data, unchanged, on the data output bus (DOB) during P1D.

If the syndrome bits are not zero, six of them provide a binary pointer for the data corrector to use to invert one of the read data bits. In the case of a single-bit error, the seventh syndrome bit (parity check of all 39 data bits) is a one and the bad bit is corrected. Should the parity check be a zero while the others indicate there is an error, a double-bit error has occurred. The bit inverted by the data corrector is neither of the error bits, so a signal (DBE) about this is sent to the chip's MPB interface. Error detection and correction are accomplished in 40 ns.

Data on the data output bus goes to the read data aligner, and is also delayed one state to the fast-byte bus (FBB). In the read data aligner, signals from the control PLA select and right-justify bytes or half-words for nonword operations, or pass through the whole word for word operations. The read data aligner output goes to the data-in/data-out (DINDO) bus, which is connected to the MPB interface. The MPB interface now places the data, the second SCTL, and the DBE signal (if present) on the MPB.

#### Write Memory Operations

Fig. 5 shows some timing for memory write operations. If the memory operation is a write, the control PLA directs its MPB interface to poll for a bus cycle during state five. This obtains the bus cycle needed to put the write data into memory. In state six, it repeats on the MPB the original address, which was in a delay pipeline in the interface. Most of the read memory cycle is then repeated to accomplish the second half (completion) of the write.

Of course, several things are different from read operations. First of all, in state seven, the read data is not placed on the MPB, but rather the write data from the master processor is latched by the interface. On P1A during state eight, that data goes via the DINDO bus to the write data aligner. For nonword operations, the write data aligner merges the rightmost byte or half-word with the read data on the fast-byte bus by substituting it as specified by the address. In word operations, the read data is ignored and

the write data is passed through.

The output of the write data aligner goes to the Hamming encoder. The Hamming encoder delays the data by one-half state while it generates seven check bits from it. The check bits are appended to the 32 data bits. Its P2A output is sent to the encoded data bus. This bus goes to the memory data bus section, which presents the 39 bits to the RAM as write data during P1D in state nine. Also during P1D in state nine, the PLA has the MAB/CS section repeat the chip selects to the RAMs (write CS).

#### Semaphore Operation

A semaphore operation reads data from a memory location and sends it to the master processor while a minus one is written to that location. The master processor uses this to obtain control of a process. The semaphore operation follows the read operation with a few differences. First, the output of the Hamming encoder is turned off, so the encoded data bus and thus the write data on the memory data bus is left precharged (all ones, which is minus one in the signed integer format). Then during state five, the control PLA has the MAB/CS section repeat the chip selects as write CS. This makes the RAMs accept the minus one from the memory data bus as write data for that location.

#### **Healer Operation**

In the healer, bits 18 to 29 of the address on the AND bus are delayed one state, concatenated with the output of the mapper ROM, and presented through the healer cam address bus (HCAB) to the healer's CAMs (HCAMs) and to a pipeline that delays the bits for three states. The output of the HCAMs goes to the healer control PLA. A match by an HCAM causes a substitute memory location (an HRAM) to dump its contents to the HRAM output bus while the input to the Hamming decoder is switched from the memory data bus to the HRAM output bus.

The healer has a significant effect on system reliability and availability. Up to 32 words per memory finstrate can have hard errors without either shutting down the system because of known memory problems (uncorrectable hard errors) or potential memory problems (hard single-bit errors increasing the likelihood of uncorrectable errors).

#### Healing on the Fly

Healing on the fly is transparent to system performance. It improves system integrity by healing known memory errors as they are detected, without affecting the current transaction or bus bandwidth as a correction and write-back scheme would. It also provides a log of the error addresses, which is useful in the repair or replacement of a card.

A nonzero set of syndrome bits sends a signal ERR to the healer. ERR causes the HCAM pointer to increment during the next state. As ERR comes true, the address in the HCAB delay pipeline is dumped on the healer's internal register access (HIRA) bus while the HCAM indicated by the HCAM pointer is set from the HIRA bus. When the HCAM pointer is incremented, the next address goes to the next HCAM, leaving the error address in the previous HCAM—thus the error is healed.

the HCAM indicated by the pointer. When the HCAM pointer is incremented, the read data is similarly captured in the HRAM, allowing the healer to have the same data in its substitute memory as was in the bad memory location. When the healer pointer count goes from 31 to 32, the healer is filled, a status bit is set, and a message is sent to the system.

#### Internal Register Access

To manage the healer and mapper, the system must be able to access their CAMs. It must also access the MC# (memory controller chip number) and status registers to turn on the system and the trace register for the system's debug aid. This is done with a channel access to channel 0. As previously mentioned, the address on the AND bus goes to an internal register access (IRA) decode section. This section checks the MC# field of the address (bits 6 to 9) against the memory controller chip's MC# and signals the control PLA if it matches. Memory controller chip IRA operations are handled with data going directly between the register and MPB interface. The main pathway is the data time (P1A) of the AND bus. The AND bus is connected via a multiplexer to the HIRA and mapper IRA (MIRA) buses in the healer and mapper.

#### Refresh

Since the NMOS RAM is dynamic, it must be refreshed. This is accomplished by having synchronized refresh counters on each memory controller chip. A refresh occurs every 16 bus cycles (32 states). The X address is changed for each refresh, but the CS signal is given each time to all RAMs. The MPB address time for the refresh cycle is normally wasted, so it is used as the time when a memory controller chip sends its messages to the CPU.

#### **Memory Management**

Also important to the system is being able to map and unmap memory blocks or to heal and unheal HCAMs. Thus each mapper CAM has a MAPOUT bit which disables that CAM no matter what the other contents of the CAM are. Each healer CAM has a HEALED bit, which when not set, disables that healer CAM.

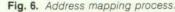

#### Self-Test

The self-test section of the memory controller chip is almost as complex as microprocessors of six years ago. Occupying 5% of the chip's die area and containing about 7000 transistors, it does a 99% confidence test on the internal circuitry and the chip's MPB interface. Self-test on a good chip completes in less than 1.5 ms.

Self-test simulates the memory controller chip's MPB interface receiving addresses, data, and control signals from another processor. It does this by placing signals on the buses and control lines from the MPB interface to the internal registers, control PLA, and data manipulation section. Thus, the circuitry of the chip is tested as a functional unit rather than testing sections of circuitry separately.

Any failure halts the self-test. If no failure occurs, a column-march test is done on the RAM addresses controlled by each CAM in the mapper. Should Hamming decoding detect any error or the data be incorrect (as in the case of

Fig. 7. Block diagram of self-test system incorporated onto the memory controller chip.

an addressing failure), the mapper CAM is loaded with a MAPOUT condition as a message to the operating system that the memory is not 100% good. The memory test takes less than 500 ms to complete.