# HEWLETT-PACKARD

**FEBRUARY 1988**

## HEWLETT-PACKARD

#### Articles

- 6 Precision Digital Oscilloscopes and Waveform Recorders, by James L. Sorden

- 12 Waveform Recorder Software Design

- Signal Conditioning and Analog-to-Digital Conversion for a 4-MHz, 12-Bit Waveform Recorder, by Albert Gee and Ronald W. Young

- 23 Adaptive Sample Rate: A First-Generation Automatic Time Base, by Richard W. Page and Nancy W. Nelson

- 26 Waveform Reconstruction Techniques for Precision Digitizing Oscilloscopes, by Richard W. Page and Allen S. Foster

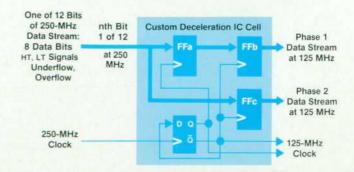

- 32 Digital Design of a High-Speed Waveform Recorder, by Rayman W. Pon, Steven C. Bird, and Patrick D. Deane

- 35 Printed Circuit Board Transmission Lines

- 39 Waveform Recorder Design for Dynamic Performance, by Brian J. Frohring, Bruce E. Peetz, Mark A. Unkrich, and Steven C. Bird

- 48 Fixed-Frequency Sine Wave Curve Fit

- 49 Packaging a High-Performance 250-Megasample-per-Second Analog-to-Digital Converter, by Patrick D. Deane, Simcoe Walmsley, Jr., and Farid Dibachi

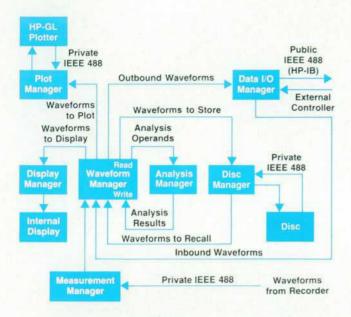

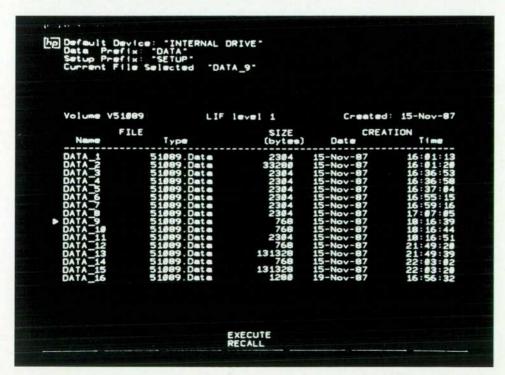

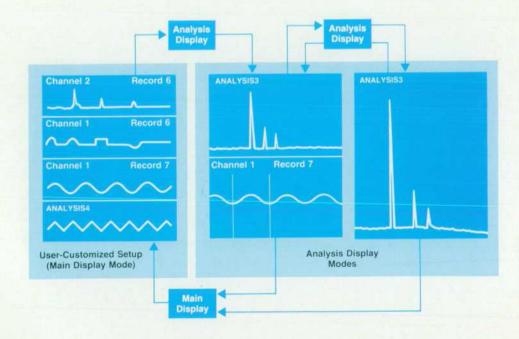

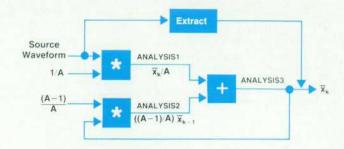

- 53 Precision Digitizing Oscilloscope Waveform Analysis, Display, and Input/Output, by Douglas C. Nichols

- 63 Handling of Significant Digits

- C Developing a Printed Circuit Board Design System, by Elaine C. Regelson

| 6 | Q | Automating | the | Printed | Circuit | Board | Design | Process, | by | Gary | Jackowa | y |

|---|---|------------|-----|---------|---------|-------|--------|----------|----|------|---------|---|

| U | U |            |     |         |         |       |        |          |    |      |         |   |

70 Finding Paths in a Gridded Data Structure

71 Managing HP PCDS with the Design System Manager, by Paul S. Reese and Mark E. Mayotte

- 73 Use of Filesets in HP PCDS

- 75 Version Strings

#### 77 A Multidevice Spooler for Technical Applications, by Deborah A. Lienhart

Integrating Applications in a Design Management System, by Mark E. Mayotte

82 HP PCDS Library Module

84 Software Quality Assurance on the HP Printed Circuit Design System Project, by David E. Martin

#### Research Report

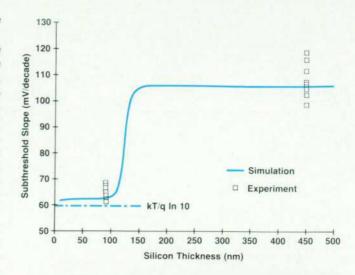

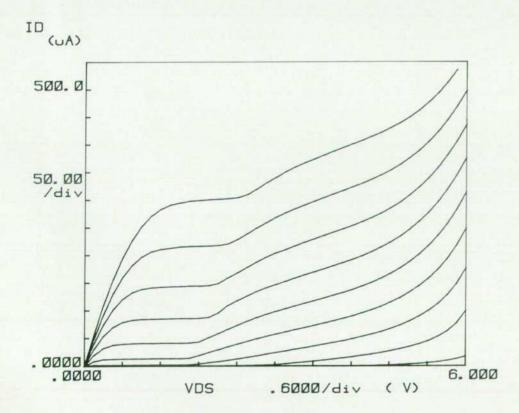

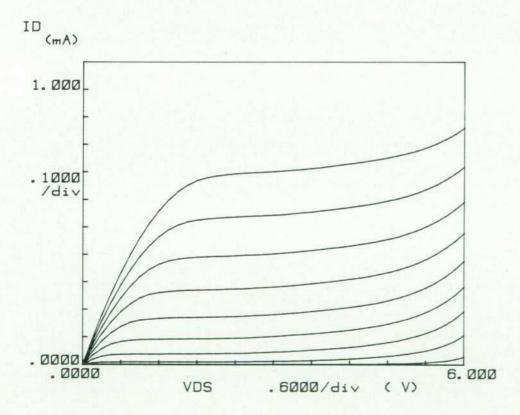

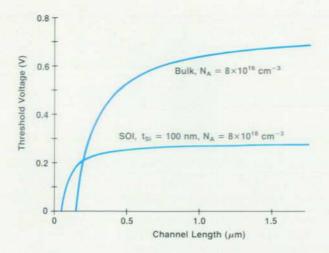

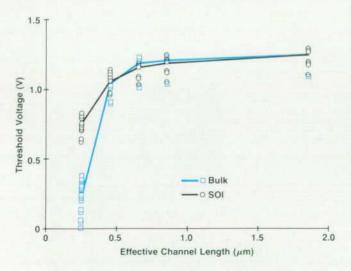

87 Silicon-on-Insulator MOS Devices for Integrated Circuit Applications, by Jean-Pierre Colinge

#### **Departments**

- 4 In this Issue

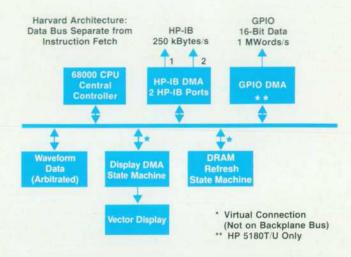

- 5 What's Ahead

- 94 Authors

#### In this Issue

That most basic of electronic instruments, the oscilloscope, has gone digital in a big way. The 1988 Hewlett-Packard Test and Measurement Catalog doesn't list a single traditional analog oscilloscope, but there are ten different kinds of digitizing oscilloscopes. In a digitizing scope, input signals are sampled, the samples are measured by an analog-to-digital converter (ADC), and the resulting numbers are stored in a waveform memory. This stored data can be used to create a display of the input signal that looks like a traditional oscilloscope display, or it can be manipulated digitally for various purposes. There are different digitizing scopes because there

are design trade-offs. In general, if you sample faster you get more bandwidth but you can't measure as precisely. You get the most bandwidth if you deal only with repetitive input signals. Some digitizing scopes are designed for maximum bandwidth for repetitive inputs, some for maximum digitizing speed, and some for maximum fidelity and dynamic range.

In this last category are the HP 5180T/U, HP 5183T/U, and HP 5185T Precision Digitizing Oscilloscopes, described on pages 4 to 64. These scopes are waveform recorders paired with an analysis and display module. They rate the adjective "precision" because high-fidelity, fully specified dynamic performance is a distinguishing characteristic of the waveform recorders they're based on. Critical to that performance is the ADC, and two ADC designs are presented in this issue. One has a 250-megasample-per-second digitizing rate and 8-bit precision (page 39), and the other is a 4-megasample-per-second, 12-bit unit (page 15). Other waveform recorder design details can be found in the articles on pages 4, 32, and 49, and the article on page 53 explains the functions of the analysis and display module. Two unusual capabilities of these scopes are adaptive sample rate (page 23) and waveform reconstruction (page 26). The former saves waveform memory by automatically reducing the digitizing rate if the frequency content of the input signal is below a certain threshold. The latter applies sophisticated interpolation techniques when creating a display from the stored waveform data. While most digitizing scopes need ten samples to make a cycle of sine wave look right, these can do it with only two and a half samples.

What gets mounted on a printed circuit board and how it's put there has changed a lot over the years. Complexity and density have increased greatly. Manufacturing and testing are fully or partially automated. A board designer in this environment is seriously handicapped without an effective computer-aided design (CAD) system. Hewlett-Packard's offering in this area consists of two software applications for HP 9000 engineering workstations. The HP Engineering Design System (HP EDS) captures the designer's schematic diagram and simulates the operation of the logic to verify the design functionally. The HP Printed Circuit Design System (HP PCDS) provides tools for board layout and generates instructions for automatic manufacturing and testing equipment. The two applications can exchange data in either direction and they share the same library of standard components.

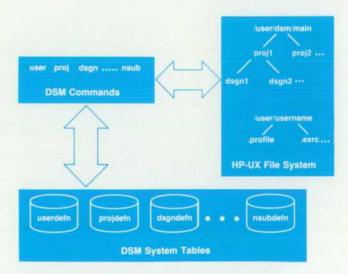

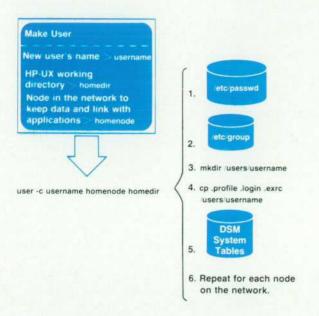

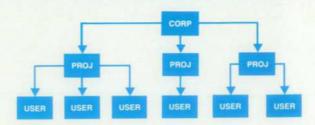

The story of HP PCDS is told by its designers on pages 65 to 86, beginning with an overview of the product and a description of the Design Module, which interacts with the board designer to define the board, place components on it, and generate manufacturing outputs. Algorithms for autoplacement of components and autorouting of the traces between components are discussed in the paper on page 68. Autorouting, considered the most critical element in a printed circuit board CAD system, is done by the HP PCDS Autorouter Module. The third of HP PCDS' three modules, the 8500-component, user-modifiable Library Module, is described on page 82. Quality assurance issues faced by the design team are covered in the article on page 84. Two special needs of HP PCDS and similar CAD systems were addressed by developing related software. First, because the productivity gains that a CAD system delivers can be greatly diminished by the extra management effort required to keep track of data and coordinate large project teams,

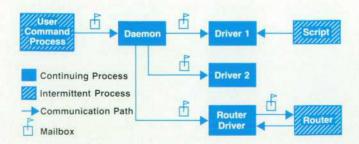

the Design System Manager was developed (see page 71). HP PCDS runs in the Design System Manager environment along with similar CAD applications. The Design System Manager provides application integration (page 80), network support, file security, and control of multiple versions of files. Second, because a CAD system has to send output to a wider-than-usual variety of devices, a special spooler was developed. The spooler is the subject of the paper on page 77.

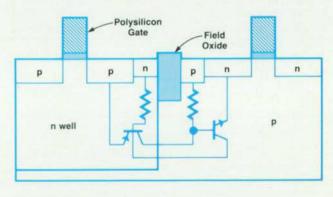

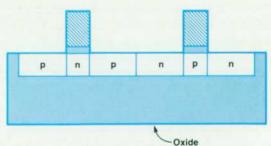

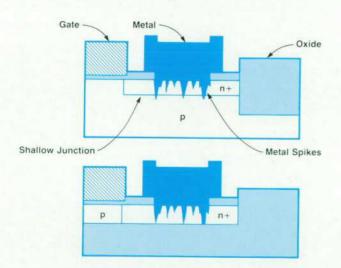

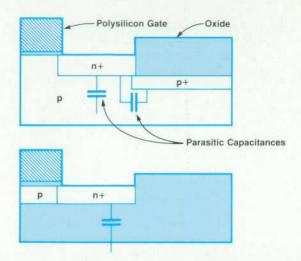

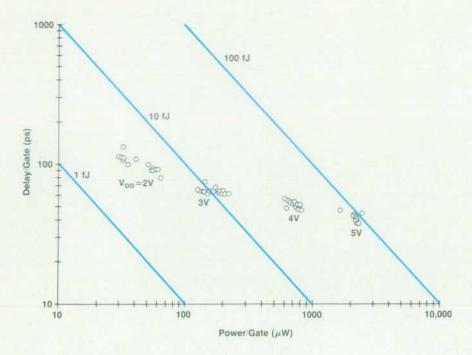

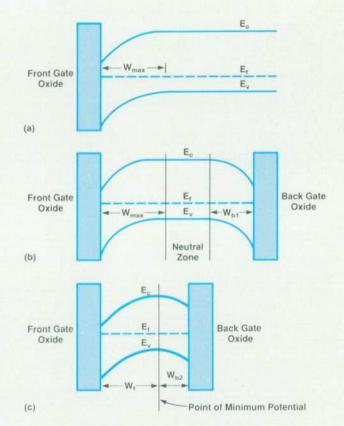

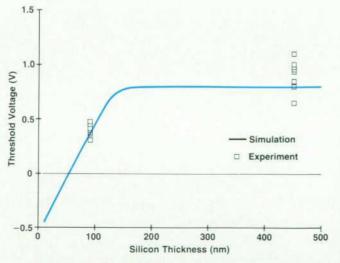

Eleven years ago, HP produced its first silicon-on-sapphire (SOS) integrated circuit, a 16-bit microprocessor chip. SOS offered a combination of low power consumption, high speed, high circuit density, and static operation that was unmatched by any other IC technology. The hope was that the system-level advantages of SOS would offset its relatively high cost. Today, SOS is considered too costly for most commercial uses, although it is still used in some applications; for example, it's used in satellites because of its radiation hardness. On the other hand, the basic idea of building silicon integrated circuits on insulating substrates is alive and well. New silicon-on-insulator (SOI) technologies are being developed using calcium fluoride or silicon dioxide instead of sapphire (which is a form of aluminum oxide). Silicon dioxide is especially attractive because it's a common integrated circuit element and doesn't require special processing equipment. In the paper on page 87 we get an introduction to SOI technology and its advantages and learn about the SOI research being done at HP Laboratories.

-R. P. Dolan

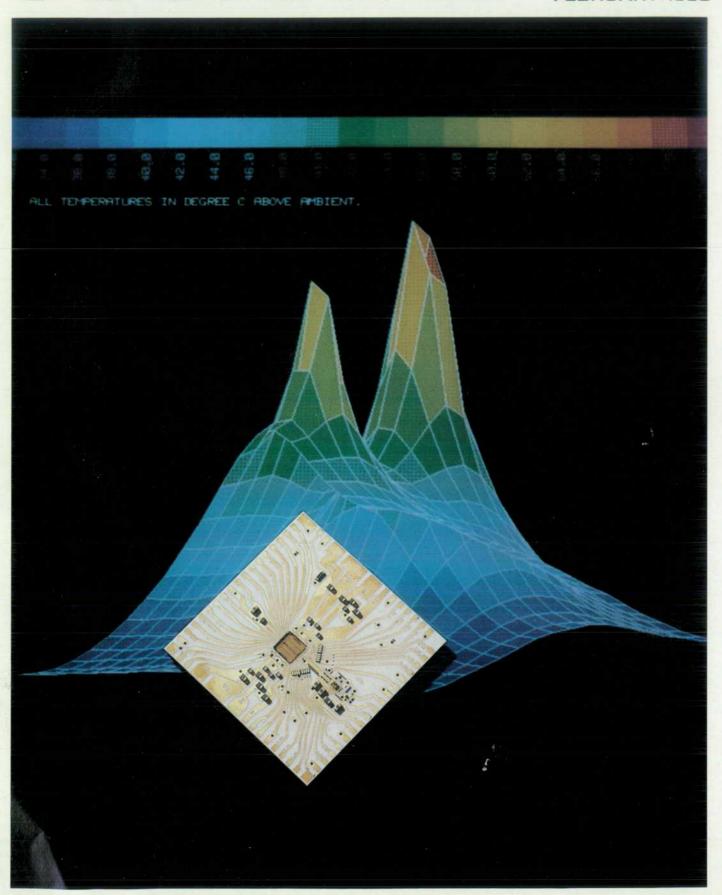

#### Cover

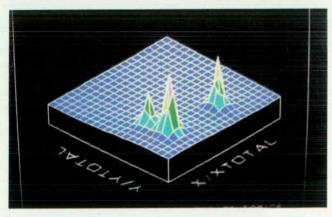

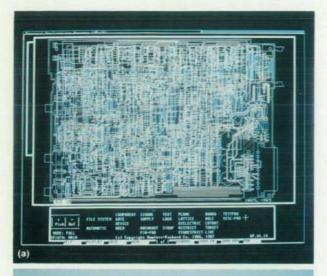

The ADC hybrid microcircuit of the HP 5185A Waveform Recorder is pictured in front of a display from a thermal modeling program that was used to predict the heat transfer characteristics of the ADC hybrid and other microcircuits.

#### What's Ahead

Scheduled for the April issue are design papers on millimeter-wave components and the HP 8770A Arbitrary Waveform Synthesizer. There will also be three papers from the 1987 HP Software Engineering Productivity Conference describing a virtual user software testing tool, a system for controlling and measuring the load on the kernel of the HP-UX operating system, and process measures to improve R&D scheduling accuracy. Another paper discusses how to adapt the various logon mechanisms of AT&T's UNIX® operating system to the manufacturing environment.

## Precision Digital Oscilloscopes and Waveform Recorders

This precision instrument family consists of five digitizing oscilloscopes based on three waveform recorders and an analysis, display, and I/O section.

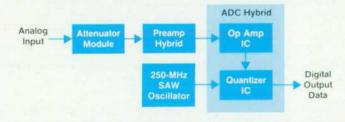

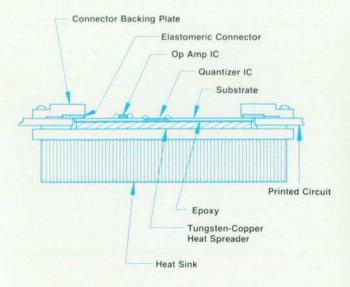

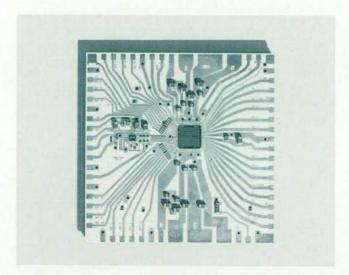

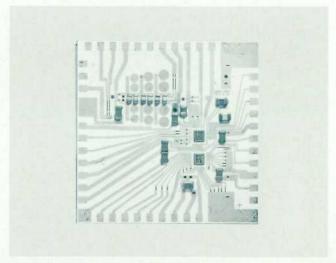

by James L. Sorden

OR MANY APPLICATIONS, the functions of an oscilloscope, voltmeter, counter, power meter, and spectrum analyzer can be provided by a single measurement instrument: the precision digitizing oscilloscope. In addition to measurements on repetitive signals (the generally assumed condition with conventional measurement instrumentation), the precision digitizing oscilloscope can make measurements on transient or single-shot signals, signals often impractical to analyze with conventional measurement tools.

To be able to function as all of the instruments mentioned, the precision digitizing oscilloscope must meet two conditions. First, the fundamental measurement device (transducer or analog-to-digital converter) must have a high degree of accuracy, fidelity, and dynamic range. Second, the analysis and input/output functions must be quick, comprehensive, and correct.

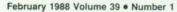

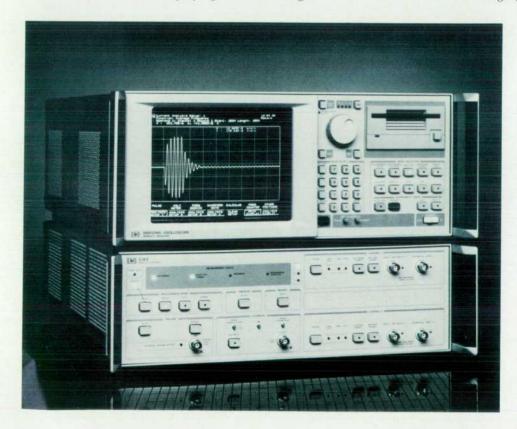

The HP 5180T/U, HP5183T/U and HP 5185T Precision

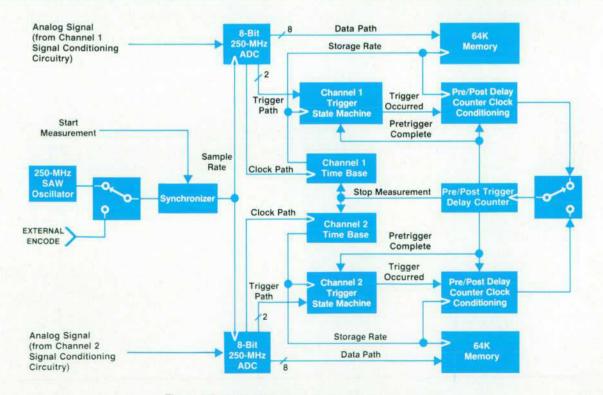

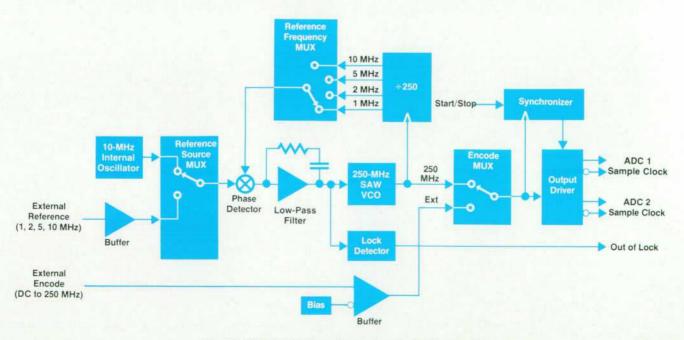

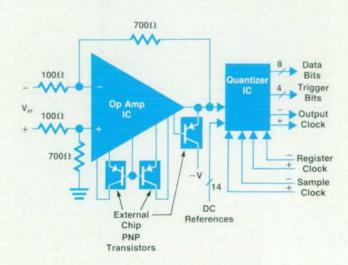

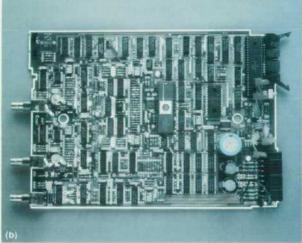

Digitizing Oscilloscopes combine analysis functions with excellent measurement fidelity to characterize single-shot or repetitive signals, either simple waveshapes or complex modulated analog signals. These instruments have two major subsections: (a) the waveform recorder with either two or four channels of data acquisition, and (b) the analysis, display, and I/O section. The HP 5180T/U (Fig. 1) uses the 20-MHz HP 5180A Waveform Recorder, which has a 10-bit ADC (analog-to-digital converter) and a 16Kword memory. The HP 5183T/U (Fig. 2) uses the HP 5183A Waveform Recorder, which has dual independent 4-MHz, 12-bit ADCs and 64K words of memory (256K optional). The T versions are two-channel instruments and the U versions are four-channel instruments that use two of the two-channel waveform recorders. The HP 5185T (Fig. 3) uses the HP 5185A Waveform Recorder, which has dual independent 250-MHz, 8-bit ADCs.

The measurement strengths of these instruments,

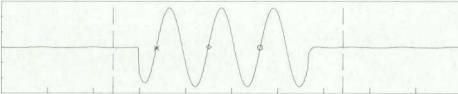

Fig. 1. The HP 5180T Precision Digitizing Oscilloscope consists of an HP 5180A Waveform Recorder and an analysis, display, and I/O section. The HP 5180A provides 20-MHz, 10-bit analog-to-digital conversion.

coupled with their built-in processing and analysis capabilities, make them well-suited for measurement systems in ATE, production, and R&D environments. In the laboratory, the digitizing oscillocope is a stand-alone, interactive instrument. For many ATE and production systems, on the other hand, the waveform recorder can be used without an analysis, display, and I/O section to minimize rack space and eliminate front-panel clutter and confusion.

This article gives an overview of the design of the HP 5183A Waveform Recorder. The analysis, display, and I/O section that transforms the waveform recorder into digitizing oscilloscopes is described in the article on page 53. The waveform reconstruction techniques that maximize the effective bandwidths of the HP oscilloscopes are discussed in the paper on page 26. The design of the HP 5185A Waveform Recorder is the subject of the papers on pages 32, 39, and 49.

#### HP 5183A Waveform Recorder

The HP 5183A is a lower-cost waveform recorder. Its data acquisition, analog-to-digital conversion, and analysis techniques make many contributions to the state of the art, including adaptive sample rate, dropout trigger, and other concepts. These are detailed in the box on page 12 and the papers on pages 15 and 23.

The block diagram of the HP 5183A Waveform Recorder is typical for waveform recorders. Elements common to most recorders are:

- Input signal conditioning, including multiple sensitivity ranges and high impedance

- High-speed transducer (analog-to-digital converter)

- High-speed memory system capable of following the ADC output and later replaying data into a digital I/O

- system

- Internal and external triggering to define measurement time endpoints

- Time base and oscillator system to control the ADC

- Digital system controller

- Digital HP-IB.

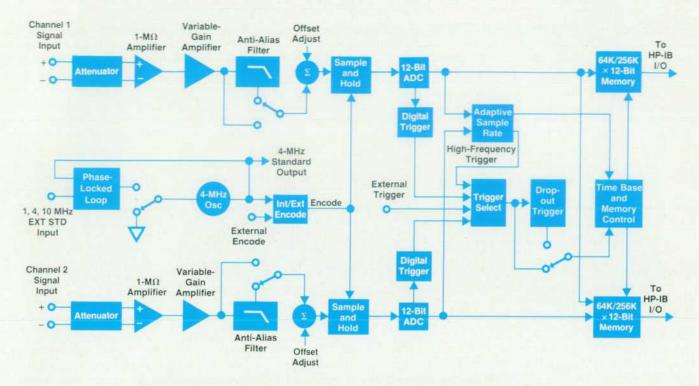

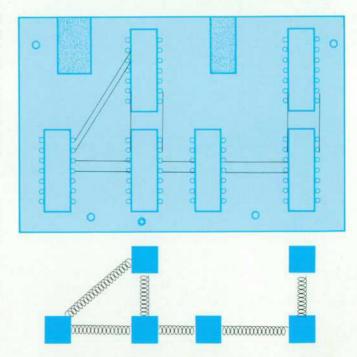

Shown in Fig. 4 is the signal flow functional block diagram for the HP 5183A recorder.

Input Amplifier System. The input amplifiers consist of a pair of 1-M $\Omega$  fully conditioned and programmable differential input amplifiers with switchable anti-aliasing filters. This high-impedance signal buffering makes it possible to monitor the user's system without disturbing its normal operation. Since this signal buffering system is built into the instrument, it is fully specified (this is not the case if external buffering is required). The switchable low-pass anti-aliasing filters prevent undesired aliasing of high-frequency signals and noise into the bandwidth of the recorded signal.

Analog-to-Digital Converter System. Each of the HP 5183A's two channels has its own independent 12-bit ADC with dc-to-4-MHz sample-and-hold signal conditioning. The maximum sample rate is 4 MHz. The two-pass converter uses an 8-bit flash ADC with a resultant 4-bit overlap (see article, page 15). From a system designer's point of view, a digitizer is most useful if it can be clocked at arbitrary rates and/or with nonuniform encode sequences. The HP 5183A ADC can be clocked at any rate from less than 1 Hz to 4 MHz.

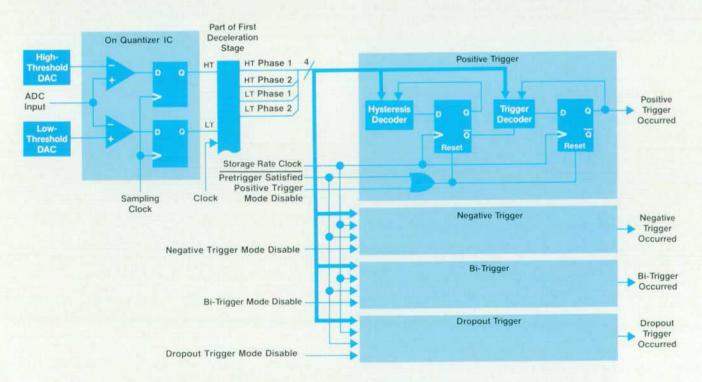

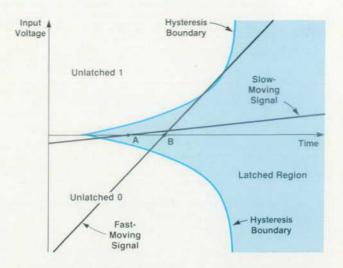

#### **Precision Digital Trigger**

The second most difficult technical challenge in any waveform recorder design (after providing a high-fidelity

Fig. 2. The HP 5183T Precision Digitizing Oscilloscope consists of an HP 5183A Waveform Recorder and an analysis, display, and I/O section. The HP 5183A is a low-cost recorder that provides 4-MHz, 12-bit analog-to-digital conversion.

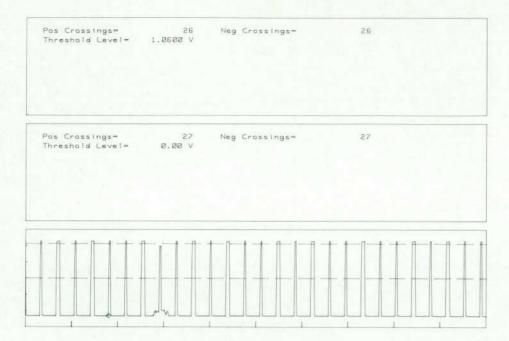

ADC) is to provide an accurate and reliable trigger system. All of the products in this family use digital triggering. Since the ADC is fully specified and tested, so is the trigger circuitry. The exact signal digitized by the ADC is seen by the precision digital trigger. There can be no drift or other inaccuracies relative to the digitized data. The trigger level control and the trigger hysteresis control are fully adjustable. This ensures optimum triggering for each application.

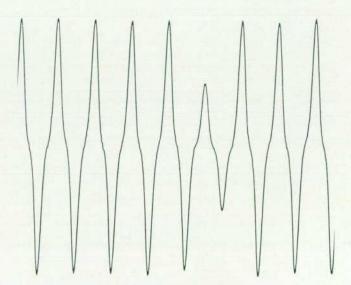

Dropout Trigger. A triggering technique that allows triggering in the absence of a signal has been implemented in the HP 5183 and HP 5185 systems. This feature allows triggering on and recording signal sag or total signal loss on signals that have a normally constant peak amplitude (Fig. 5). When the preset trigger amplitude conditions are not met for an interval set by the dropout delay timer, the trigger command occurs. The dropout trigger circuit consists of conventional trigger detection circuitry plus a special timer. The timer is reset with the trigger detection circuitry. If the timer circuit does not reset in the time specified by the user, then the trigger has not occurred during that time, and a dropout trigger signal is sent to the memory, activating the normal memory stop circuitry. Some examples of dropout trigger applications include:

- Ignition systems. Determine the cause of cylinder misfirings and record the time and waveshape of the signal pattern around the misfire.

- Communication systems. Determine the cause and characteristics of carrier loss or distortion.

- Power distribution system monitoring. Two classic anomalies on a power distribution system are brownouts or line sag, an application for dropout trigger (Fig. 5), and high-voltage spikes, an application for bi-trigger mode (Fig. 6).

- Oscillators. When an oscillator squegs, a measurement can be made to determine the time and shape of the anomaly.

- Magnetic media testing. Digital tape or flexible disc systems can be precisely analyzed to see the exact magnetic position of data lost.

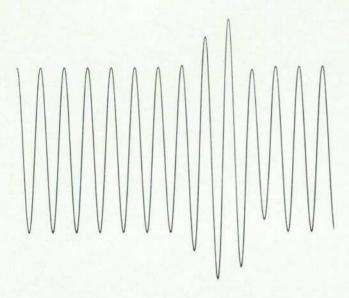

High-Frequency Trigger. A class of transients that conventional trigger circuits do not handle well is high-frequency noise transients that do not exceed the nominal peak-to-peak voltage level of the signal. An example of this class of noise transients is high-frequency transients on a power line system, often generated by switching spikes from inductive loads. With the adaptive sample rate system, HP 5183 Option 301, the included high-frequency digital filter can be used to detect these transients. Relatively low-energy, high-frequency transients can be detected in the presence of a much larger low-frequency signal. The detected signal is used to fire the trigger system and initiate recording of the transient (Fig. 7).

#### Time Base System

The time base system has the primary function of providing flexibility in the ADC sampling rate, permitting longer time records at slower sampling rates (assuming one operates within the Nyquist sampling criterion). The HP 5183 system can switch between its main rate and a second, or delayed, rate. This feature is most often used to conserve memory or increase measurement time when the operator has prior knowledge of the signal bandwidth. Either time base can set to any period from 250 ns to 4 seconds in 250-ns increments. In addition, two new functions, burst time base and adaptive sample rate, are available in the time base.

Fig. 3. The HP 5185T Precision Digitizing Oscilloscope consists of an HP 5185A Waveform Recorder and an analysis, display, and I/O section. The HP 5185A provides 250-MHz, 8-bit analog-to-digital conversion.

Fig. 4. HP 5183A Waveform Recorder simplified signal flow block diagram.

Burst Time Base. The burst time base mode allows the operator to record a selectable number of data samples automatically after a trigger event. The number of samples can be any integer from one to the total memory length. After a rearm delay of two sample points, the HP 5183A is ready to record the next burst immediately. This is an extremely efficient technique for recording hundreds or thousands of data bursts in a single record. No data is recorded between bursts (Fig. 8).

The circuit consists of a counter in the time base system. It is set for a specified number of sample points, then is rearmed and waits for the trigger event. A typical application is to analyze peak pulse amplitudes of a series of waveforms. Examples include radar return pulse analysis, Otto cycle engine instantaneous power peak analysis, and digital magnetic media error testing.

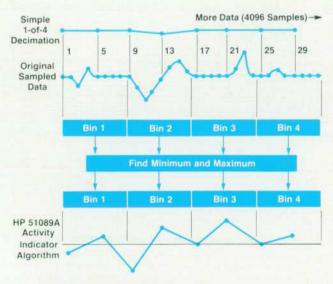

Adaptive Sample Rate. Adaptive sample rate (Option 301) automatically slows down the time base when higher sampling rates are not required, preserving all timing information and signal shape. Details of the signal processing are covered in the article on page 23. Adaptive sample rate effectively increases memory up to 60 times or up to 30 million samples.

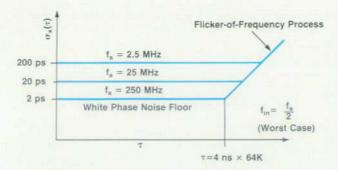

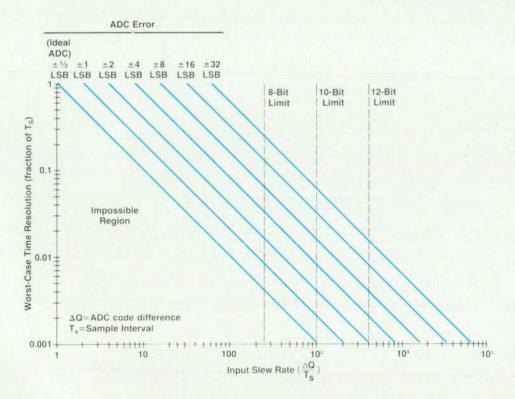

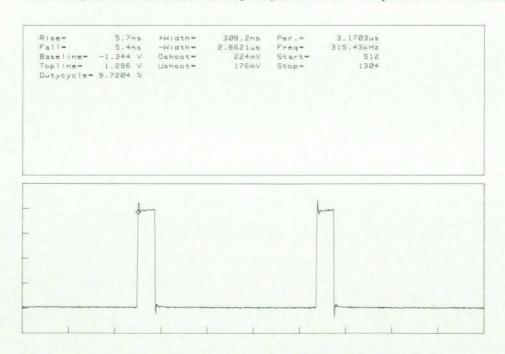

Reference Oscillator. The 4-MHz crystal oscillator is an extremely critical time base subsystem. It must always maintain sufficient purity to ensure the fidelity of the ADC. For example, with a 1-MHz input signal and 12 bits of ADC resolution, ½ bit of noise distortion will be induced by 39 picoseconds of jitter (Fig. 9). For this reason, the oscillator consists of an extremely quiet voltage-controlled oscillator in a sophisticated phase-locked loop with a 4-MHz crystal reference. The VCO can be locked to a 1-MHz, 4-MHz, or 10-MHz external high-stability oscillator or to the Option

010 internal oven oscillator to provide the stability needed for mathematically comparing waveform data taken at significantly different times or different temperatures.<sup>2</sup>

#### **Memory System**

The typical waveform recorder memory system consists of static read/write memory (SRAM) IC chips controlled by a counter and an address register. Although this is a satisfactory scheme, SRAM is more expensive, takes more power, and is less dense (fewer bits per IC) than dynamic read/write memory (DRAM). In a computer architecture,

Fig. 5. Dropout trigger is a new feature that can capture brownouts or unexpected load increases.

Fig. 6. Bi-trigger can be used to capture an unexpected load decrease or high-voltage spikes.

where the necessary cycle stealing control circuits for memory refresh (mandatory for preserving memory) are relatively straightforward, DRAM is much less expensive.

In waveform recorders, access to the memory must be assured whenever a sample point is taken. The HP 5183A data rate can vary from nanoseconds to seconds per sample point. The memory must start and stop as demanded by the user (a function of memory size and trigger time). In addition, the adaptive sample rate system may ask the memory system to decimate 63 out of every 64 sample points taken. Although a complex digital control problem, we chose a DRAM system for its advantage of greater memory size at far lower cost.

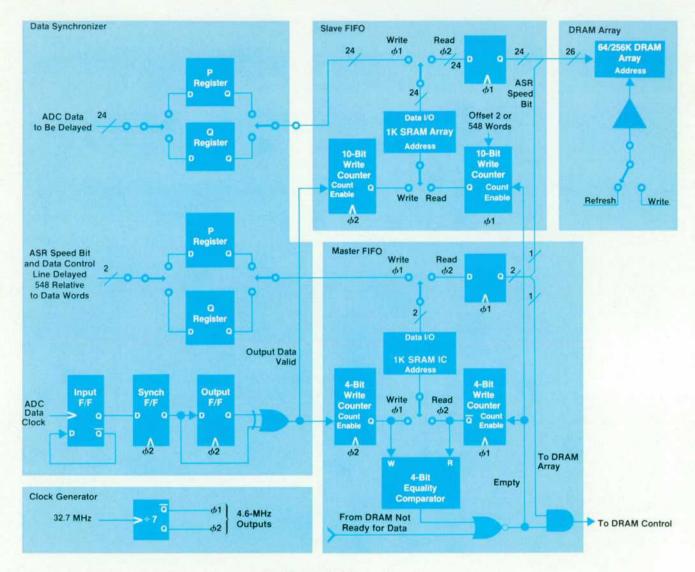

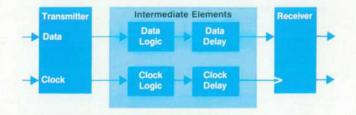

The HP 5183A memory system provides input synchronization, first in, first out (FIFO) buffering, shift register buffering (for delay of ADC data), and output synchronization with a minimum amount of hardware (Fig. 10, page 14). Among the design contributions in the memory system is a unified hardware implementation for a combination FIFO buffer and a programmable shift register having synchronous input and output capabilities. The design is not subject to errors caused by metastable states of the input and output flip-flops.

Clock Generator. The memory generates an internal clock of approximately 4.6 MHz. This frequency is used so that the instantaneous data rate of the memory is slightly higher than the 4-MHz maximum sample rate. This 0.6-MHz margin allows for refresh overhead (cycle stealing). The front end of the memory runs on the phase 2 clock and the rest runs on phase 1.

Data Synchronizer. Data from the ADCs (two 12-bit ADC data channels) is clocked alternately into 24-bit registers. The data is clocked in by the data clock coming from the ADC, and clocked out by the phase 2 clock. When a word is being read into one register, the previous word is being clocked out of the other register. This guarantees that the data will not be changing as it is read out, regardless of the relative timing of the data clock and the incoherent

phase 2 clock. An input flip-flop controls which of the registers accepts ADC input data and an output flip-flop controls which register outputs the data. The two flip-flops are connected through a synchronizing flip-flop which provides the transition between the two different clocks in the system. An exclusive-OR gate generates the output signal to indicate whether data is available from the data synchronizer during the current 4.6-MHz clock period. The adaptive sample rate speed and data valid signals are processed through similar synchronizers.

Master FIFO. The master FIFO stores the adaptive sample rate speed bit and control data while the DRAM memory is refreshing and then releases it as the DRAM is able to accept it. The buffer consists of static RAM. It is written to on the phase 2 clock and read out on the phase 1 clock. Four address bits are required. Multiplexers switch the data and address between read and write. The addresses are generated by two four-bit counters. The write counter increments whenever new data comes in and the read counter increments whenever data is read out by the DRAM. Hence, the read counter is constantly chasing the write counter. During refresh periods, the write counter continues to advance and store, while the read counter is held. When no new data is coming in, the write counter stands still while the read counter catches up. A comparator looks at the two addresses and generates an empty signal if they are equal. This instructs the DRAM not to try to take any more data. The FIFO has a capacity of 15 words. A maximum of 9 words are used during DRAM refresh delay.

The data control signal coming out of the FIFO is routed to a qualifier to determine whether the ADC data should be stored. This allows the adaptive sample rate system to discard redundant data. This happens downstream from the FIFO so as not to upset the counters. Hence, data will be written to the DRAMs unless the adaptive sample rate system says no, the FIFO is empty, or the DRAMs are in a refresh cycle. The adaptive sample rate speed bit is sent

Fig. 7. High-frequency trigger can capture high-frequency transients that do not exceed the nominal peak-to-peak voltage of the signal.

Fig. 8. Burst time base mode is used to record a selectable number of samples after a trigger and then stop, rearm, and begin recording again after another trigger. Memory is conserved because no samples are recorded during uninteresting periods between bursts. Recorded signal (top) for input signal (bottom).

directly to the DRAM array as a data bit.

ADC data passes through the slave FIFO. This FIFO is similar to the master except that it has ten-bit address counters and a 24×1024-bit static RAM array. It is identified as a slave circuit because the count enable signals from the master control its address counters. The read counter is preset to either 2 or 548 before making a measurement. This offset is maintained indefinitely, resulting in a 2-word or 548-word delay pipeline in the data path. This circuit can be thought of as a programmable shift register of length 2 or 548. The delay of 2 compensates for trigger system detection delays. The 548-word delay is invoked during adaptive sample rate operation to compensate for the delaying effects of the adaptive sample rate low-pass and smoothing filters.

DRAM Array. After the incoming data is synchronized, buffered, and pipelined, it is routed to the memory, which consists of 64K or 256K 25-bit words of DRAM. The 25 bits are needed for the two 12-bit ADC data channels plus the adaptive sample rate speed bit. Memory refresh is done on one row every 10 microseconds.

DRAM Address Circuitry. The addresses for the DRAMs are generated by an 18-bit data address counter and an 8-bit refresh counter. A multiplexer selects between the refresh address and the data address. In a repeating cycle, the refresh address is strobed in. The row address is then latched and a series of column addresses is sent. This is the page mode of DRAM operation.

**Read Registers.** The data played back from the DRAMs is read out one byte at a time to the data bus. The DRAM control circuit generates a sequencing signal to clock new data from the DRAM into the read registers after the previous byte has been accepted.

DRAM Control Circuit. The DRAM control circuit is a 48-state repeating sequence circuit driven by the 4.6-MHz clock. Two periods are devoted to refresh, and two periods are devoted to latching the row address. The other 44 periods are available for writing or reading data. An eightbit counter is hardwired to divide by 48. A decoder circuit

switches the address multiplexer at the appropriate time and enables the DRAM RAS and CAS appropriately.

#### Other Design Features

The HP-IB system is a conventional state machine design. The high-current ±5V power supplies are secondary switching regulator designs.

The mechanical package design contains a conventional card cage but the cage is constructed as a monocoque welded aluminum frame. This design yields extremely stiff and strong but lightweight packaging. The thermal and acoustic management considerations dictated the use of three low-noise cooling fans for maximum reliability and low noise. Front-panel keys and annunciators are slaved to the display, I/O, and analysis module in the HP 5183T/U or to a remote computer when the HP 5183A recorder is used.

#### Acknowledgments

Many, many people have contributed to success of the HP 5180T/U and HP 5183T/U. I would especially like to thank Mark Allen, Phil Deaver, Mike Detro, John Fenwick, Jack Folchi, Rick Karlquist, Nancy Nelson, Doug Nichols, and Celia Vigil, who all served as R&D project managers. Jim Ammon, Jason Cotton, Bill Daley, Patty Damron, Nina Delu, Al Gee, Andy Gong, Ron Felsenstein, Al Foster, Dick

(continued on page 14)

Fig. 9. With a 1-MHz input signal and 12-bit resolution, ½ bit of noise distortion will be induced by 39 ps of jitter.

#### Waveform Recorder Software Design

The HP 5183A Waveform Recorder is tailored to the measurement requirements of a computer-controlled general-purpose waveform recorder and integrated with measurement application specific software. The HP 5183A consists of the precision waveform recorder hardware described in the accompanying article and measurement control software optimized for high measurement throughput.

While the HP 5183A Waveform Recorder and the HP 5183T Precision Digitizing Oscilloscope (an HP 5183A with a display module) are directed toward different applications, migration paths from one application to the other do exist. An example of moving from an HP 5183T to an HP 5183A is the development of a measurement procedure by a design engineer through interactive use and testing on the lab bench. When the procedure is implemented on an automated production line, the final algorithm can be implemented with a recorder. The HP 5183A offers faster performance and lower cost than the HP 5183T in the dedicated test system. Alternatively, measurements taken on remote recorders can be sent to a central HP 5183T to be processed using its powerful analysis capabilities. The HP 5183A would function as a lower-cost precision transducer, and the HP 5183T would be the central data reduction processor.

#### Software Architecture

The HP 5183A Waveform Recorder software is a library of procedures that allow the user to program the setup of the waveform recorder and control measurement cycles in the recorder. This software is typically used as procedures loaded with the user's software. Users can develop their own custom measurement systems and use the services provided by the HP 5183A software. Additional demonstration procedures allow the HP 5183A and its computer to function as a digitizing oscilloscope.

The primary contribution of the software is to provide an interface between easy-to-program high-level software and the difficult-to-program control register set that makes up the hardware. The software hides all the detailed information required to program the instruments; the user is presented with a standard procedure-oriented interface. This procedure library is provided in the BASIC language for HP 9000 Series 200/300 Technical Computers.

Architecture. The HP 5183A software is implemented as a set

of standard procedures that are directly executed when called. Support of interrupts and multiprocess concurrency on the host computer are independent of the use of these libraries. These features can be implemented by the user in custom software.

Interfaces. Parameters passed to library procedures describe the operations to be performed by the library. The parameters are numeric or ordinal types that correspond to the physical parameters of the system where possible. More complex record type data structures supported in some languages are not used as parameter types. Advantages of this interface are that the same design can be ported to other languages or systems with minimum revision. It also allows users to program the instrument with the same numeric parameters they use to analyze data, rather than the ASCII string command embedding required by

To maximize usability, the interfaces are designed to be similar to other HP instrument controller software systems. In particular, the interfaces are similar to those used in the earlier-generation

HP 51800 Waveform Recorder Software and will be compatible with future waveform recorders and products. Since the software insulates the user from any machine specific interactions with the recorder, it will be source code compatible with other waveform recorder products.

**Feature Set Extension.** The software supports all hardware capabilities of the HP 5183A. Analysis or enhanced display capabilities can be added easily using third-party software.

**Software Data Structures.** The HP 5183A software can be modeled as two fundamental data structures. One data structure contains the current recorder state in the form of control codes written to the recorder when it is programmed. This low-level or bit-level description of the instrument setup is a software image of the recorder control registers. This type of data structure contributes to the high measurement throughput.

The second fundamental data structure prevents complex interactions between parameters from introducing any calling order dependence on the subprograms. This structure remembers the parameters that are interactive, so the final instrument state can be made independent of the library subprogram calling order.

Recorder State. The recorder state completely describes the state of the waveform recorder. It contains additional information required by the software, including instrument number, HP-IB select code, and bus address for multiple-instrument systems. This data structure is treated as a read-write variable. It is copied or rewritten if recorder setup information is internally saved or recalled to a file or to disc.

A library procedure is provided so the user can easily determine the current state of any HP 5183A in a system. This procedure formats the state information and displays it on the controller display.

For each recorder in a multiple-recorder system, the software instantiates a copy of the two data structures. All references to the particular instrument being programmed for setup or measurement are made by setup number. In this way, the number of recorders in the system is dynamic, and each recorder is separately controllable.

#### Software Operations

In controlling the waveform recorder, the software performs certain operations on its data structures. These operations include: setup, translate, measurement, initialize, calibrate, and verify.

Setup Input Parameters. These operations take user-entered values for recorder setup, enter them into the appropriate data structures, and update the hardware to reflect the new setup state. These operations are implemented as procedures called by the user software; value parameters describe the new setup state. This layer of software can be modeled as a shell that hides the complex hardware register programming task from the user.

The setup layer is implemented as BASIC subprograms; parameters to the subprograms define the hardware capabilities controlled by the software. Some checking of the input parameters is performed. Invalid parameters are logged as errors by the called subprogram. Error conditions cause the subprogram to exit without modifying the setup state. Consistency checks, which generate warnings when a parameter is limited or adjusted to the nearest allowed hardware value, are deferred to a separate subprogram. This approach, as opposed to having each subprogram issue warnings, avoids having the same warning issued

most programmable instruments.

more than once and avoids issuing a warning that is not warranted by the final instrument state. Once the user has made all the changes to a setup, subprogram B83check\_setup can be called to do a consistency check.

An example of a setup procedure implemented in BASIC is:

SUB B83set\_input (INTEGER Setup, Channel, REAL Range, Offset, OPTIONAL INTEGER Coupling, Config. Filter)

| Setup    | 1 to 32    | index to data tables for this instrument |

|----------|------------|------------------------------------------|

| Channel  | 1 to 2     |                                          |

| Range    | 0.1 to 50  | volts select in 1-2-5 sequence           |

| Offset   | ±2 × range | entered in volts                         |

| Coupling | 0,1        | dc-coupled/ac-coupled                    |

| Config   | 1,2,3      | single-ended/differential/disconnected   |

| Filter   | 0,1        | filter out/in                            |

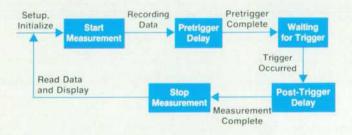

Measurement. These procedures initiate and control a measurement cycle in the waveform recorder, using the instrument setup previously entered. At the completion of these procedures, the sample data from the waveform recorder has been read into the computer memory and is ready for processing by the user software. An example of a measurement cycle using the BASIC software is as follows:

SUB B83start\_meas (Setup)

REPEAT

Temp = B83meas\_done (Setup)

UNTIL Temp

B83transfer\_rec (Setup, Channel, Buffer, Header(\*))

Setup

index to instrument being controlled

Channel

channel to be transferred

Buffer Header(\*)

I/O path name to predefined data buffers pointer to an array to hold the waveform header

information required to scale the data

Software is supplied in source code format for BASIC. The BASIC system consists of about 3000 noncommented source statements.

#### Performance Results

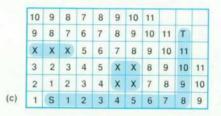

In many applications the ability to acquire many waveforms rapidly translates directly into reduced production test overhead. The measurement throughput numbers shown in the following table are typical characteristics and can vary depending on parameters such as sample rate, time spent waiting for a trigger, etc.

| Measuremen | ts per | Second |

|------------|--------|--------|

|------------|--------|--------|

|                                                                    | HP      |               | HP9          | 000          |              |              |  |

|--------------------------------------------------------------------|---------|---------------|--------------|--------------|--------------|--------------|--|

| Controller:                                                        | Vectra* | Model<br>236U | Model<br>310 | Model<br>320 | Model<br>330 | Model<br>350 |  |

| 1024-Point Blocks<br>with Data Trans-<br>fer to Controller         | 8       | 16            | 13           | 20           | 22           | 27           |  |

| Auto Advance:<br>1024-Point Blocks<br>Stored in Internal<br>Memory | 29      | 40            | 31           | 55           | 60           | 70           |  |

<sup>\*</sup>Requires the HP 82300A BASIC Language Processor Card.

#### Other Systems

A goal of the HP 5183A project was to provide a path for porting the software into other systems. The use of a structured

software design and the implementation in a high-level language were key strategies in this process. Also, the use of HP language extensions to BASIC was minimized.

MS-DOS Systems. Many instrument control and automated test systems are being developed in the MS™-DOS operating system for use on personal computers, such as the HP Vectra PC or the IBM PC. Using the HP 82300A HP BASIC coprocessor card, HP BASIC 5.0 runs directly in the PC. The HP 5183A software can then be run under BASIC 5.0. All the functionality of the HP 5183A software can be exercised. This includes instrument addressing and control over the HP-IB, waveform display to the CRT, and the creation of waveform data files on disc. Users can combine the waveform recorder control software and the superior HP-IB I/O processing and fast development time of HP BASIC with the industry standard MS-DOS data processing and spreadsheet packages to develop their own optimum measurement systems and to leverage existing investments in HP-IB and MS-DOS sys-

HP-UX/UNIX Systems. HP BASIC 5.0 allows direct file transfers from BASIC to HP-UX or UNIX® operating system environments. Using these systems, data files from the waveform recorder taken with the HP 5183A software library can be passed directly into HP-UX. The full range of UNIX data manipulation and communications capabilities can then be used to process the data. For example, under the BASIC operating system, data from the waveform recorder can be saved in a disc file. From the HP-UX operating system, the file can then be processed by any of the standard UNIX utilities, such as sort, awk, or grep.

MS-DOS is a trademark of Microsoft Corp. UNIX is a registered trademark of AT&T in the U.S.A. and other countries.

> John Ketchum Project Leader Santa Clara Division

Fig. 10. HP 5183A memory system.

(continued from page 11)

Fowles, Ron Keeley, Alice Kwei, Rich Page, Don Schremp, Phil Scott, Ralph Smith, Dana Stoffers, Chris Szeto, Phil Vitale, Steve Will, Ron Young, and Russ Zandbergen are other dedicated R&D engineers who labored long and productively on these projects. Many others contributed years of work in the QA, production, and marketing departments. Special thanks to Al Scalise, key production engineer, who sorted out so many of the early production problems, and to Dan Hunsinger, Santa Clara Division R&D manager, for his continued support.

#### References

- 1. J.L. Sorden and M.S. Allen, "Waveform Recording with a High-Dynamic-Performance Instrument," *Hewlett-Packard Journal*, Vol. 33, no. 11, November 1982, pp. 3-9.

- S.C. Bird and J. A. Folchi, "Time Base Requirements for a Waveform Recorder," ibid, pp. 29-34.

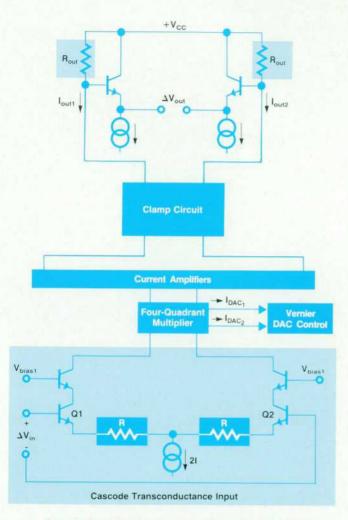

# Signal Conditioning and Analog-to-Digital Conversion for a 4-MHz, 12-Bit Waveform Recorder

by Albert Gee and Ronald W. Young

HE ANALOG-TO-DIGITAL converter (ADC) in the HP 5183A Waveform Recorder samples at a rate of four million samples per second and provides 12 bits of amplitude resolution. The 4-MHz sample rate exceeds the minimum 2-MHz rate (Nyquist rate) needed for adequate characterization of input signals with 1-MHz bandwidth. With 12 bits of amplitude data, the ideal signal-to-quantization-noise ratio is 74 dB and the resolution is ±0.05% for full-scale input signals.

Key features of the analog circuitry include the design of a modern discrete operational amplifier, a discrete sample-and-hold circuit, series-parallel ADC topology with pipelined ADC timing, a low-noise oscillator, and pseudorandom noise to improve the ADC's linearity. The performance of the input amplifier and ADC systems has been thoroughly evaluated and characterized with both static and dynamic input signals. The static characterization involves measuring the transfer function (with a tracking loop measurement) to determine the linearity. The dynamic performance is analyzed using the DFT (discrete Fourier transform), curve fit, and histogram tests. <sup>1</sup>

Digital signal processing techniques can be used on the raw digital data to increase the signal-to-noise performance;

these techniques include averaging multiple measurements and oversampling (with respect to input signal bandwidth) followed by digital filtering. These issues are discussed in detail later in this paper.

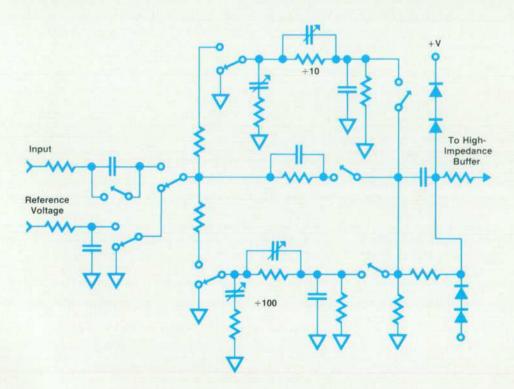

#### Input Amplifier

Two identical attenuators, one for each input, handle the input configuration and coarse ranging while presenting 1-M $\Omega$  input impedance to the signal sources (see Fig. 1). In each channel, input clamp circuitry is followed by two high-impedance buffers that convert the differential signal to a low-impedance system. This signal is then converted to a single-ended signal. Two switchable gain stages in cascade implement the 1-2-5 variable-gain sequence, producing a  $\pm 1$ V-full-scale signal which goes to a switchable 1-MHz anti-aliasing filter and then to the output buffer, which incorporates a  $\pm 200\%$  offset control. The control interface circuitry allows input configuration and offset calibration from the HP-IB through the internal register bus.

The input configuration has four possible states: accoupled, dc-coupled, ground, and reference. In the ground and reference states, the input BNC is decoupled from the attenuator and left floating. The ground state connects the

Fig. 1. HP 5183A Waveform Recorder input attenuator.

local ground to the input of the attenuator. The reference state connects a precision reference voltage to the input of the attenuator. The voltage reference is selectable from  $\pm 100$  mV to  $\pm 10$ V in a 1-2-5 sequence, plus 0V.

The attenuator provides coarse ranging as a selection of one of three decade attenuators:  $\div 1$ ,  $\div 10$ , and  $\div 100$ . The selected range is terminated with a 1-M $\Omega$  resistor. The  $\div 10$  and  $\div 100$  attenuators have pole-zero compensation for parasitic capacitance. They also have an adjustment to match the input capacitance with the  $\div 1$  attenuator. The nominal input impedance is 45 pF in parallel with 1 M $\Omega$ .

The clamp circuitry protects the FET in the high-impedance buffer from overvoltage. A large series resistor in front of the clamps limits the current in the clamp diodes for low-frequency overvoltages. For high-frequency overvoltages the resistor is bypassed with a capacitor to speed up the response of the clamp diodes. Two pairs of series diodes form the positive and negative clamps. The series diodes maintain the low-leakage characteristic of the circuit after repeated high-frequency clamping. The clamps limit the FET gate voltage to approximately  $\pm 6.5 \text{V}$ .

The high-impedance buffer is a discrete FET-input op amp in unity-gain configuration. The discrete op amp is used throughout the input amplifier design. A detailed description is given later.

Up to this point in the system, there are two identical sets of circuitry, one for each differential input. The two signal paths are matched and have identical circuit layouts. Another discrete op amp, with similar topology, performs the differential-to-single-ended conversion. An active current source is used to bias the gain stage instead of a resistor. This increases the common mode rejection of the amplifier.

Each switchable gain stage is a discrete op amp in noninverting gain configuration. The first stage switches between  $\times 5$  and  $\times 1$ . The second stage switches between  $\times 2$  and  $\times 1$ . This allows the implementation of a 1-2-5-10 gain sequence. The partitioning of the gain is optimized for overall noise performance.

The anti-aliasing filter is a 1-MHz low-pass filter designed for overall frequency response of  $-3~\mathrm{dB}$  at 1 MHz and below  $-60~\mathrm{dB}$  at 3 MHz. It is a 10-pole matched-impedance elliptical filter, Gaussian to  $-6~\mathrm{dB}$ . The filter can be bypassed by selecting the alternative signal path, which matches the insertion loss of the filter.

The output stage is another discrete op amp nominally in a noninverting gain-of-two configuration. The gain and offset adjustments occur at this stage. The offset control voltage is introduced at the summing node. The nominal output is  $\pm 1V$  with  $\pm 2V$  offset.

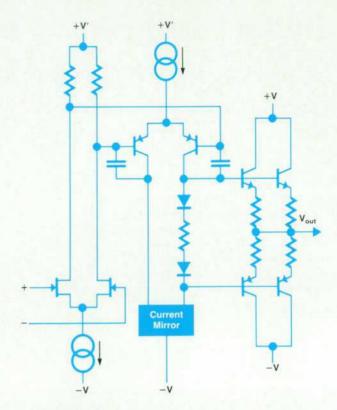

#### **Discrete Operational Amplifier**

Much of the performance of the input amplifier is dependent upon the performance of the discrete FET-input op amp (Fig. 2). The discrete op amp is designed to rely more on circuit linearity than feedback to achieve its distortion performance and bandwidth. The open-loop gain is approximately 50 dB, compared to over 100 dB for a typical commercial op amp. The FET input stage provides for low input bias current and the output stage can drive  $50\Omega$  to 2V peak-to-peak at 1 MHz with low distortion.

The frequency compensation is symmetric, with one

Fig. 2. Discrete FET-input operational amplifier used in the input amplifier.

capacitor from the base to the collector of each pnp transistor in the emitter-coupled pair in the gain stage. The capacitor connected to the low-impedance side of the active load introduces a nearly coincident pole-zero pair at low frequencies. The capacitor connected to the high-impedance side of the active load introduces the dominant pole for the open-loop frequency response.

The discrete op amps are optimized for 1-MHz distortion performance. The input bias current, which is determined by the FET, is less than 100 pA at 25°C. The input offset voltage is typically less than 10 mV and has a temperature coefficient of 50  $\mu\text{V/°C}$ . In a unity-gain configuration, the bandwidth is 40 MHz. The corresponding harmonic distortion is less than -75 dBc for a 10-dBm sinusoid input at 0.95 MHz. The slew rate is  $400\text{V/}\mu\text{s}$ . The output noise in unity-gain configuration is 8 nV/  $\sqrt{\text{Hz}}$  at 500 kHz. The op amp dissipates 800 mW in its quiescent state with no load.

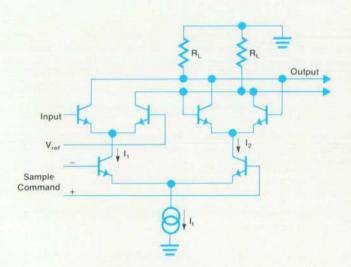

#### Analog-to-Digital Converter

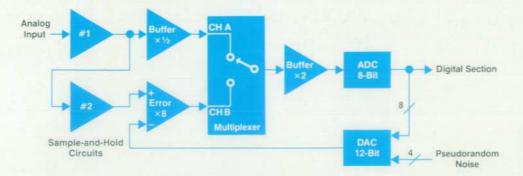

Fig. 3 shows the simplified block diagram of the seriesparallel ADC. The components of this subranging ADC include two sample-and-hold circuits, an analog multiplexer, an 8-bit A-to-D converter, a 12-bit D-to-A converter, and an error amplifier. The intermediate results of two 8-bit A-to-D conversions are combined to form the final high-resolution 12-bit result.

Sample-and-hold circuit #1 acquires and holds a sample of the input signal. This sample is routed via path A to the A-to-D converter, where a first-pass conversion produces a digital approximation to the analog signal. The precision D-to-A converter converts the digital approximation to an

Fig. 3. Block diagram of the 4-MHz, 12-bit analog-to-digital converter in the HP 5183A.

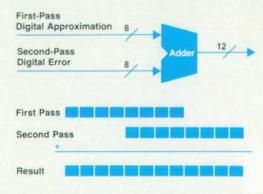

analog signal, which is subtracted from the sample-andhold output signal. This analog error signal is amplified and routed via path B to the A-to-D converter, where a second-pass conversion produces the digital error. The second-pass digital error is scaled to compensate for the error amplifier gain and is added to the first-pass approximation to generate the high-resolution, 12-bit representation of the analog input signal (Fig. 4).

An error analysis of this system shows that only the D-to-A converter and the sample-and-hold circuit need to have 12-bit accuracy. The rest of the system components need only have an accuracy consistent with the 8-bit A-to-D converter. A benefit of this converter, unlike successive approximation ADCs, is that errors in one pass can be corrected by subsequent passes if there are overlapping bits between the passes. This ADC has a speed advantage because the D-to-A converter needs to settle only once versus twelve times for a successive approximation ADC.

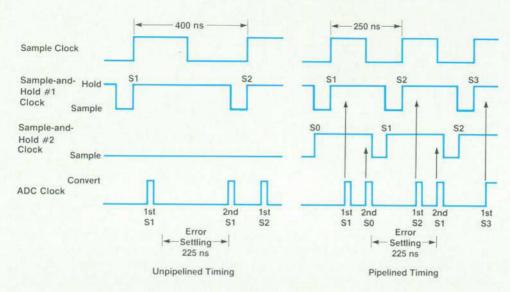

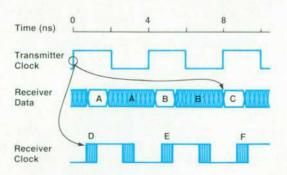

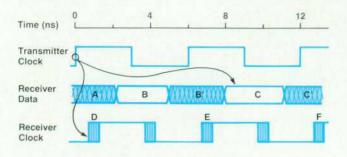

Pipelined Architecture. Even with its speed advantage, the series-parallel topology is not sufficient to achieve the desired 4-MHz sampling rate with the chosen components. The most time-consuming portion of the conversion cycle is waiting for the D-to-A converter and error signal to settle. The 4-MHz sampling rate is attained by pipelining the system. The main idea of pipelining is that a repetitive sequential process can be converted to a higher-frequency process by inserting an appropriate delay element so that operations can be performed concurrently. In this case, pipelining is implemented by using a second sample-and-hold circuit as the delay element, as shown in Fig. 3. The second sample-and-hold circuit makes both the current analog sample and the next analog sample available concurrently. While the error signal for the current sample is settling, a first-pass conversion of the next sample is done.

Fig. 5 gives a detailed example of unpipelined versus pipelined timing of the ADC. In the unpipelined case, the sequence of events is: acquire the signal, perform the first-pass conversion, wait for the error to settle, and then perform the second-pass conversion. In the pipelined case, there are two parallel paths. For the first path, the sequence of events is: acquire the current signal and then perform the first-pass conversion of the current sample. For the second path, the sequence is: acquire the previous signal and then perform the second-pass conversion of the previous sample. For the example given, the sampling rate increases from 2.5 MHz for the unpipelined case to 4 MHz for the pipelined case.

An additional benefit of pipelining is that the stepwise outputs of the second sample-and-hold circuit and the D-to-

A converter can be timed to change simultaneously. Thus the error amplifier is not overdriven and exhibits only a very short switching transient.

Pseudorandom Noise. Since the D-to-A converter determines the overall system accuracy, a 12-bit converter is used. The eight most-significant bits are used for the first-pass digital approximation. The four least-significant bits are used to add pseudorandom noise to dither the analog error signal as shown in Fig. 3.

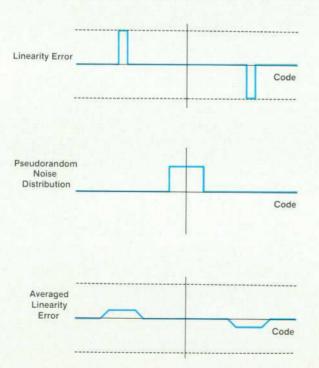

The purpose of pseudorandom noise is to randomize the quantization error associated with each ADC code. For instance, referring to Fig. 6, assume that the error function of the ADC transfer function is represented by the first graph and that the pseudorandom noise probability density is represented by the second graph. If the pseudorandom noise is independent of the input signal, then the resulting averaged error function is given by the convolution of the two graphs. The net effect, as shown in the third graph, is to improve the average linearity of the ADC. Since the digitally added noise is known exactly, the same noise can be subtracted out of the digital result. Therefore, pseudorandom noise has all the benefits of analog dither plus the important advantage of not contributing any noise power to the digitized signal. Thus large amounts of pseudorandom noise can be used, and in this case, up to 16 LSBs (= 4 quantizer bits) of noise are used. Note that with the gain ratio (ratio of first-pass gain to second-pass gain) mismatched, an attenuated component of the pseudorandom noise is present at the digital output. Thus the pseudorandom noise can also be used to calibrate the gain ratio by grounding the analog input signal and nulling the second-pass output for minimum noise power.

Pseudorandom noise is especially useful for repetitive

Fig. 4. The second-pass digital error is scaled and added to the first-pass approximation to form the 12-bit result.

Fig. 5. Pipelining is used to achieve the 4-MHz sampling rate in the 12-bit ADC. The arrows show which sample-and-hold circuit is involved in each conversion in the pipelined case.

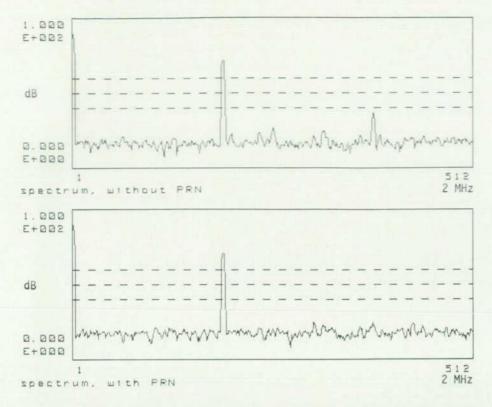

signals that can be averaged, signals that are phase coherent with the sample clock, or low-level signals where the quantization noise is less likely to be uniformly distributed. An example of the last case is shown in Fig. 7, which compares the spectrum of a digitized low-level sine wave with and without pseudorandom noise. The randomizing effect of the digital dither can be seen by the absence of the aliased harmonics in the pseudorandom noise case.

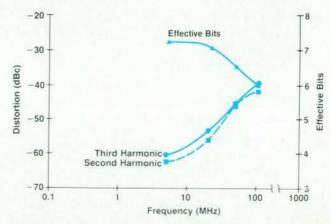

#### **ADC Performance**

In the curve fit test, a sine wave is digitized by the ADC, and from the resulting digital data, the best-fit sine wave that minimizes the mean squared error is calculated. Normally, the frequency used is one that will ensure testing a

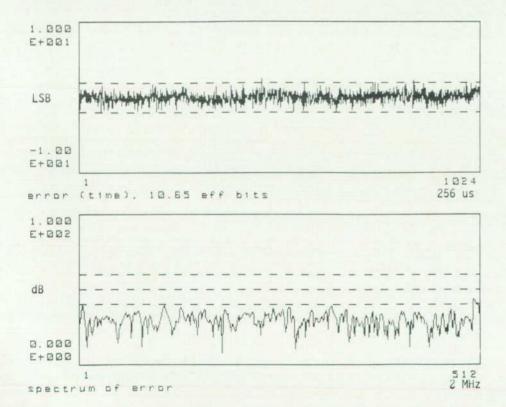

Fig. 6. Pseudorandom noise is used to dither the analog error signal and improve the average linearity of the ADC.

majority of the ADC codes and is similar to the intended application bandwidth. In the dynamic testing of this particular ADC, full-scale sine waves with a nominal frequency of 1 MHz were used. Fig. 8 shows the resulting error in both the time and frequency domains of a curve fit test using a test frequency of 0.985 MHz; the number of effective bits is 10.65. The apparent performance of a high-resolution ADC can easily be limited by the noise of the input signal source. An HP 8662A low-noise synthesizer (with the output low-pass filtered) was needed to measure the number of effective bits accurately.

The DFT test is effective in separating the noise power into distortion (harmonics), environmental sensitivities (discrete lines), and white noise (flat noise floor) components. Analyzing the data in the frequency domain is particularly useful since nonlinearities present in the ADC produce harmonics of the input frequency that are readily detected. The harmonics are not restricted to multiples of the input frequency, since aliasing folds the higher-order harmonics ( $\rm f_x > f_{\rm s}/2$ ) back down to between 0 and  $\rm f_{\rm s}/2$  as given by the following equation:

$$f_{alias} = |f_x - f_s \times round(f_x/f_s)|$$

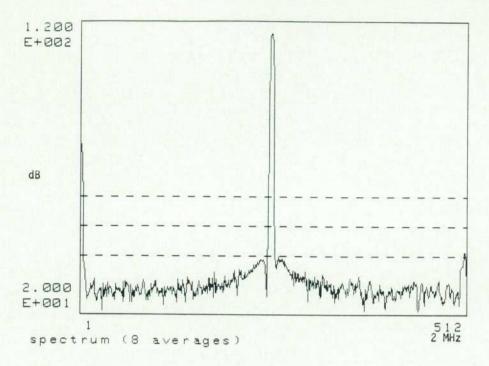

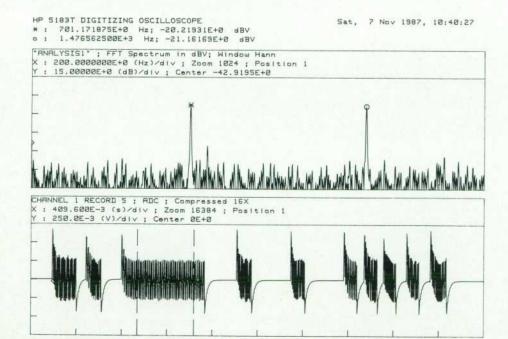

In Fig. 9 the spectrum of a digitized 0.985-MHz sine wave is computed. The highest spurious signal, second-harmonic distortion, is below  $-70~\mathrm{dBc}$ .

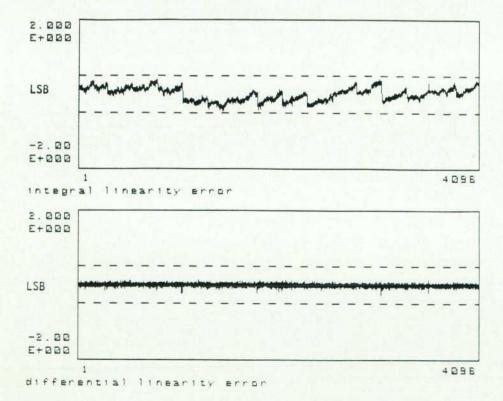

Integral linearity measures the deviation of the transfer function data from the best fit (minimum mean squared error) line through the data. Integral nonlinearity highlights global nonlinearities, which can produce high distortion. Static differential nonlinearities greater than  $\pm 1$  LSB indicate potentially missing codes and nonmonotonicity. Fig. 10 shows both the integral and static differential nonlinearity of the ADC to be within  $\pm \frac{1}{2}$  LSB.

For dynamic signals, differential nonlinearity and missing codes can be best measured by using the histogram test with a sine wave input. The input test frequency should be chosen to ensure that all the ADC code levels are tested. The ADC raw histogram and linearized histogram results in Fig. 11 show the ac differential nonlinearity to be well within  $\pm 1$  LSB.

Fig. 7. Spectra of a digitized lowlevel sine wave with and without pseudorandom noise.

In an aperture jitter test, the input signal is phase-locked to the ADC sample clock, and the ADC is set to sample only on the zero crossings (regions of highest slew rate) of a high-frequency, high-amplitude sine wave. Experimental results for this converter indicate an rms aperture jitter of 28 ps or a degradation of 0.3 effective bit for a 1-MHz test input.

#### **Maximizing Performance**

In many instances, the signal-to-noise ratio performance of the HP 5183A can be improved by postprocessing the raw digital data with averaging and filtering algorithms. These signal processing techniques depend on random noise that is uncorrelated with the input signal. With the injection of pseudorandom noise into the ADC, as men-

Fig. 8. (Top) Error in curve fit test for a test sine wave at 0.985 MHz. (Bottom) Frequency spectrum of the error.

**Fig. 9.** Spectrum of a digitized 0.985-MHz sine wave.

tioned earlier, the quantization noise is randomized with respect to the input signal so that the noise can be considered white.

Averaging. If the input signal is repetitive and if the measurements can be phase-coherently triggered with the input signal, then averaging multiple measurements will decrease the noise power of a single measurement by a factor equal to the number of measurements averaged (n). Thus the signal-to-noise ratio of n averaged waveforms is:

$SNR(n) = 10 \log(signal power/(noise power/n))$ = 10 log(n) + SNR(1).

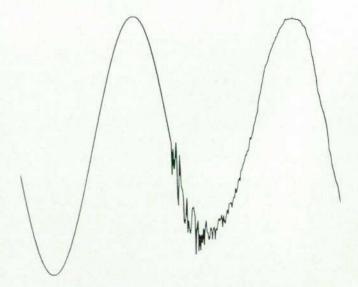

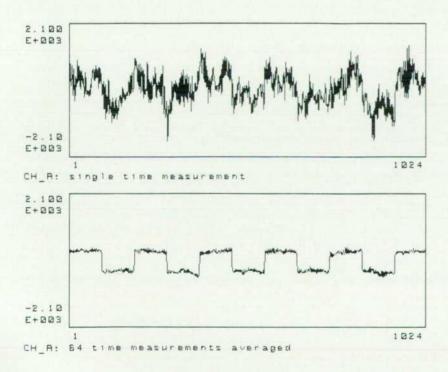

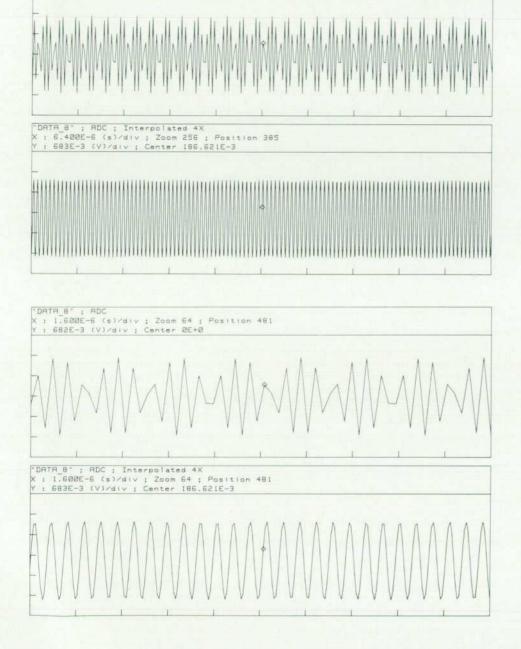

For example, with sixteen averages, the SNR can be expected to increase by about 12 dB over the SNR of a single measurement. With averaging, the noise that is reduced can be the noise in the input signal and/or the noise generated internally in the digitization process. An example of the benefits of averaging is shown in Fig. 12. The upper

Fig. 10. Integral and static differential nonlinearity of the HP 5183A ADC.

Fig. 11. Raw and linearized histograms show the ac differential nonlinearity of the ADC to be within ±1 LSB.

plot shows the sum of the input signal and noise based on one measurement (no averaging). The lower plot shows the result of averaging 64 measurements. The original input signal characteristic is now easily discerned. It is important to note that averaging techniques to enhance SNR are ultimately limited by the linearity of the digitizer.

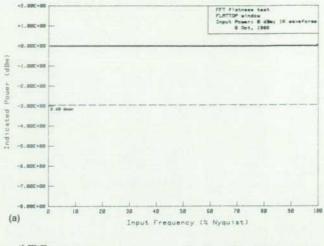

Oversampling and Postprocessing. The dynamic perfor-

mance of the HP 5183A is specified as 10 effective bits at 1 MHz. This specification is limited by the analog harmonic distortion performance at high frequencies. For lower input frequencies, the performance increases as the harmonic distortion decreases. Performance at lower frequencies is limited primarily by quantization noise. Thus, if the input frequency is lower than 1 MHz, the number of effective

Fig. 12. An example of the benefits of averaging.

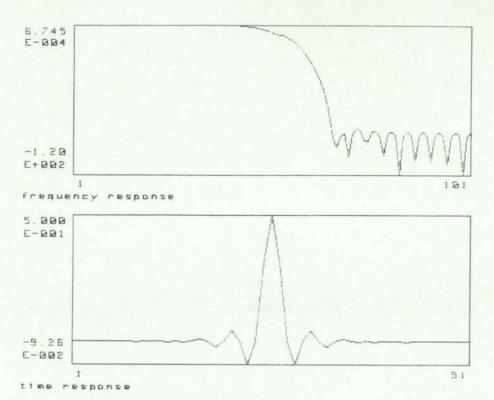

Fig. 13. Response of the digital filter used to increase effective bits for low-frequency signals by removing high-frequency quantization noise.

bits will be greater than 10 and lower harmonic distortion will be realized. However, an even better signal-to-noise ratio can be achieved by removing the high-frequency quantization noise as well. This can be accomplished by oversampling the signal and externally postprocessing the quantized data with a digital low-pass filter to reduce the noise bandwidth. If the input signal is oversampled ( $f_{\rm s}>nf_{\rm in},\ n>2$ ) and if the quantization noise is white, then the noise power in the frequency range  $f_{\rm s}/2>f>f_{\rm in}$  can be digitally removed. The noise power left is  $f_{\rm in}/(f_{\rm s}/2)$  of the original noise power, which corresponds to an increase in the number of effective bits as follows:

Original noise power

$$N_o = \frac{q^2}{12} = \frac{A^2}{12(2^{2b_o})}$$

where q is the quantizer resolution and A is the full-scale amplitude. Rearranging terms,

$$b_o = original effective bits = \frac{1}{2} log_2 \frac{A^2}{12N_o}$$

The filtered noise power is

$$N_f = N_o \left( \frac{BW_f}{BW_o} \right)$$

,

where  $BW_o$  and  $BW_f$  are the original and filtered bandwidths. Therefore, the number of effective bits after filtering is

$$b_f = \ \frac{1}{2} \ log_2 \ \frac{A^2}{12 N_f} = b_o + \frac{1}{2} \ log_2 \frac{BW_o}{BW_f}$$

For every factor-of-two reduction in bandwidth (oversampling by a factor of 2) the number of effective bits can increase by  $\frac{1}{2}$  bit (if quantization noise is the limitation and not ADC distortion). For example, with an input signal of 125 kHz maximum and a 12-bit ADC sampling at a rate of 4 MHz (BW $_{\rm o}=2$  MHz), this signal processing technique increases the ideal 12-bit ADC to a theoretical performance of 14 effective bits. Note that the noise floor in the frequency domain does not decrease, but rather the bandwidth is reduced. The costs of this technique are a reduction in maximum record length and input bandwidth, and additional computation time.

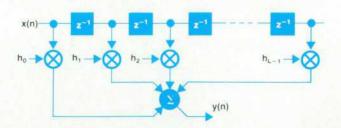

The signal is oversampled by setting the sample rate to  $nf_{in}$  and setting the record length to n times the desired length. The digital filtering can be done in either the time domain or the frequency domain. We chose a linear-phase FIR (finite impulse response) filter with 50 coefficients (Fig. 13). The filter is designed to divide the input bandwidth by half the sample rate. To select bandwidths other than  $\frac{1}{2}$ , the filter is used iteratively in conjunction with data decimation (by a factor of two) to reduce the sample rate. Since the data is filtered before each decimation, there is negligible aliasing. With a 100-kHz signal (using a low-pass-filtered HP 8662A), the number of effective bits increases to 12.7; this compares with 11.0 effective bits without any digital filtering.

#### Reference

Dynamic Performance Testing of A-to-D Converters, Hewlett-Packard Product Note 5180A-2. 1982.

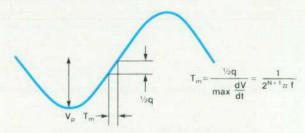

### Adaptive Sample Rate: A First-Generation Automatic Time Base

by Richard W. Page and Nancy W. Nelson

HEN CAPTURING TRANSIENT signals, it is desirable to use a high sample rate to preserve input signal details. This limits the maximum recording time of the measurement. In the HP 5183A Waveform Recorder with Option 301 Adaptive Sample Rate (ASR), the input signal is sampled at the selected fast rate only when there is significant detail present, and at a much slower rate when there is no significant detail. Thus ASR maximizes the recording time without compromising signal integrity. ASR continuously estimates the input signal's bandwidth and switches to a lower sample rate whenever possible.

The ASR circuit computes the ratio of the input signal's instantaneous spectral energy below the set threshold frequency to the total input signal energy. If this ratio is unity, all signal energy lies below the threshold frequency and the input signal can be down-sampled without any loss of information. The ASR circuit fixes the threshold frequency to be one hundredth of the Nyquist frequency and allows down-sampling by sixty-four.

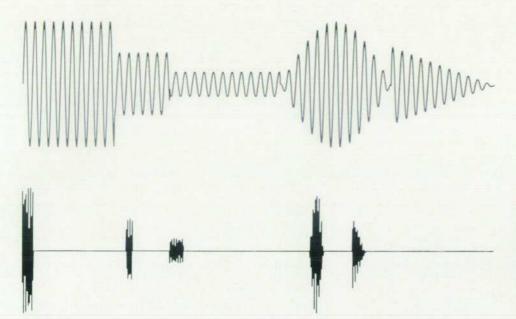

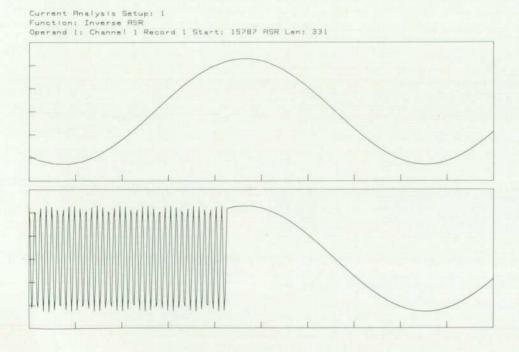

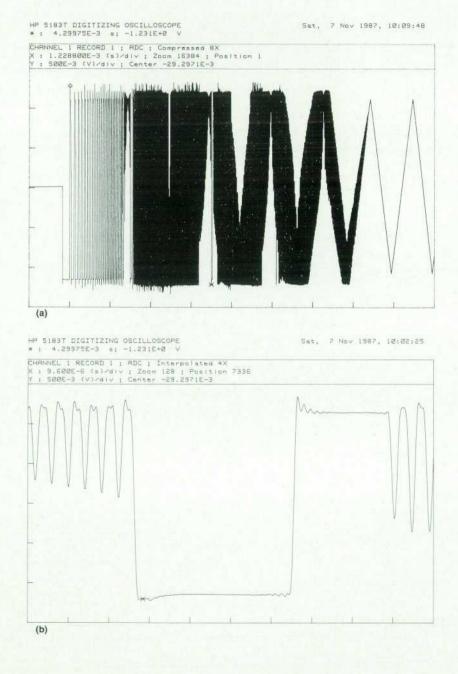

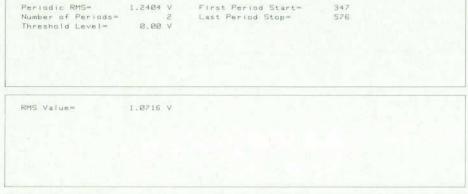

Fig. 1 shows a typical ASR output and the input signal reconstructed from it, demonstrating that the ASR algorithm preserves the input signal.

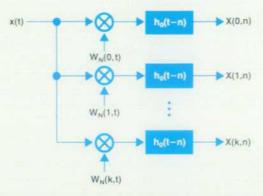

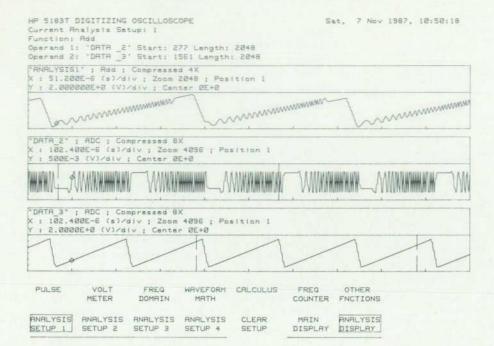

#### **ASR** Implementation

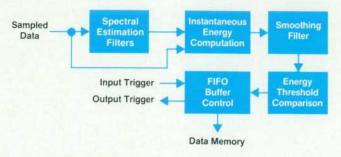

Fig. 2 illustrates the data flow and computations within one channel of the ASR circuit. Two channels of ADC data are input at the user-selected time base rate. This data is filtered by the spectral estimation filters which eliminate energy above the threshold frequency. Output from the estimation filters is used along with the input signal to compute instantaneous energy ratio. This ratio is computed by subtracting logarithms of the two signals. The resulting difference in logarithms is smoothed and compared to a set energy threshold. If the resulting smoothed ratio estimate is below the threshold limit, a slow sample rate is indicated for the current sample. Buffer control circuitry accumulates sample rate decisions over groups of 64 input samples and generates the composite fast/slow sample rate signal. This signal is used to control the signal that tells the waveform recorder's data memory whether to store data or discard data. It is also stored with the data waveform memory. Because this fast/slow signal is stored, it is possible, for a sufficiently low threshold limit, to reconstruct the input signal completely, including all timing informa-

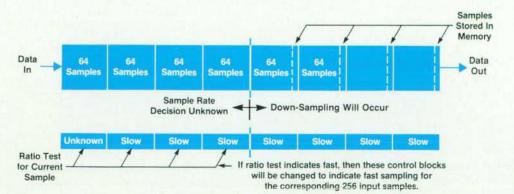

Although the ASR circuit independently examines and computes the required sample rate for each channel, both channels are stored at the same rate. Selecting the appropriate trigger source (either channel 1, channel 2, or composite trigger) causes the sample rate decision to be derived respectively from channel 1, channel 2, or the inclusive-OR of the decisions from channel 1 and channel 2. The ASR circuit always monitors the input signal and computes a sample rate decision. For down-sampling to begin, at least 256 consecutive ratio tests must indicate that down-sam-

Fig. 1. HP 5183T display of the output of the adaptive sample rate circuit (bottom) and the reconstructed input waveform (top). The bottom waveform shows the actual memory contents. Before the trigger point, the input waveform is down-sampled; only one out of every 64 possible sample values is stored, making the display appear compressed. The top waveform shows that the original signal can be reconstructed from the stored data.

Fig. 2. Adaptive sample rate system single-channel data flow.

pling is possible. In addition, the ASR FIFO buffer must contain four consecutive blocks of 64 data samples that can be down-sampled. This guarantees that at least four samples will be stored in memory at the slow rate once down-sampling has been initiated. Down-sampling will continue as long as each consecutive block of 64 samples indicates that down-sampling is possible (Fig. 3). The ASR FIFO buffer delays the input signal to allow the ASR circuitry to change the sampling decision from slow to fast for the preceding 256 input samples. This ensures that data preceding the slow-to-fast sample rate decision is output at the fast sample rate, providing maximum detail around the sample rate transition.

The instrument trigger signal is sent to the ASR circuitry and used to ensure fast sampling around the trigger sample. This guarantees that the trigger sample will be stored in memory. The trigger signal is inclusive-ORed with the instantaneous sample rate decision derived from the energy ratio comparison. The ASR FIFO buffer responds to a trigger by forcing a slow-to-fast sample rate decision.

When ASR is disabled, the buffer control circuitry is held reset and the sample rate decision is still output to the trigger circuit. Setting the trigger condition to high-frequency trigger allows the trigger circuit to be activated by transitions on the sample rate decision line. This feature allows the instrument to trigger on transitions from slow to fast sample rate as computed by the ASR. This is useful because wideband noise is present in many transient capture applications before and after the occurrence of the transient event.

The user-selectable noise threshold prevents the ASR circuit from computing a fast sample rate decision for insignificant noise by forcing all signals below the noise

threshold to be ignored. The control is user-adjustable over 25% of the input signal range. Thus, the noise threshold control affects signals that are small and near zero volts, measured at the ADC. Clearly, if the input signal has a large dc bias, the noise threshold control will not be effective. A dc component can be eliminated by using ac input coupling feature or offset control. A large dc bias will also adversely affect the ASR circuit's ability to make the correct sample rate decision because this decision is based on an energy ratio.

The ASR circuitry computes partial short-time Fourier transforms using a custom CMOS circuit. This circuit is a 3- $\mu$ m-process, 2000-gate gate array with 98% of the gates used. The gate array's pipelined arithmetic circuits are clocked at a 16-MHz rate. Four additions and two multiplications are computed in 250 ns. One custom CMOS circuit is used per input channel. The output of the custom CMOS circuit is a measure of the input signal energy below the threshold frequency. It is used to compute the energy ratio.

Instantaneous energy comparison results are computed by subtracting the logarithms of the squared magnitude of the input signal and the squared magnitude of the CMOS gate array output (short-time Fourier transform). These instantaneous results are statistically noisy. To remove the variance from the energy comparison, the instantaneous energy comparison results are passed through a time division multiplexed digital smoothing filter. This digital filter is a single-pole low-pass filter.

#### Signal Processing Theory

The ASR circuit computes spectral energy estimates by means of a partial calculation of the short-time Fourier transform (STFT), which is defined as:

$$X(k,n) = \sum_{t=-\infty}^{\infty} w(t-n)x(t)W_N(k,t)$$

(1)

where w(t) is the N-sample window beginning at time n, x(t) is the input sequence, and

$$W_N(k,t) = \exp(-j2\pi kt/N)$$

Here the sampling frequency is normalized to 1 Hz and  $\Delta t = 1/f_s = 1$ .

The STFT estimates spectral components by computing

**Fig. 3.** Adaptive sample rate FIFO buffer operation.

Fig. 4. Time function, sliding window, and windowed time function for short-term Fourier transform computations.

the discrete Fourier transform of the input signal multiplied by a sliding window (Fig. 4). The window w(t) determines a filter shape that indicates how the spectral estimates are smeared by the finite observation time and how much spectral leakage will occur as a result of the window shape.

The STFT for bin k can be viewed as the output of a linear system whose input is the frequency-shifted (modulated) signal  $x(t)W_N(k,t)$ . The response is determined entirely by the window function. The STFT is equivalent to a bank of identical low-pass filters operating on the N sequences  $x(t)W_N(k,t)$ , k=0,1,...,N-1 (see Fig. 5). The output power from each low-pass filter is equal to the input power contained in the band centered about  $\omega=2\pi k/N$  as viewed through the spectral weighting function induced by the sliding window.

The filter bank analogy provides a convenient framework for examining spectral estimators. The analysis filter's main lobe width determines the ability to resolve components. Sidelobe behavior determines leakage (scalloping loss or picket fence effect). The ability to track variations in the input spectrum depends on the estimation window and the filter bank output sample rate. Longer time windows result in improved spectral resolution but reduced ability to track nonstationary behavior.

The total signal energy for the ratio test beginning at time n is given by Parseval's relation:

$$E(n) = \sum_{k=0}^{N-1} |X(k,n)|^2 = \sum_{t=-\infty}^{\infty} |x(t)w(t-n)|^2$$

(2)

The energy threshold T<sub>L</sub> is:

$$T_{L} = \frac{1}{E(n)} \sum_{k=0}^{f_{L}(n)} |X(k,n)|^{2}$$

(3)

Fig. 5. The short-term Fourier transform is equivalent to a bank of identical low-pass filters operating on N weighted input sequences.

The threshold frequency  $f_L(n)$  can be computed from equation 3 by solving for  $f_L(n)$  with  $T_L$  fixed. Alternatively,  $T_L$  can be computed for a fixed value of  $f_L(n)$ . Fixing  $f_L(n)$  and computing  $T_L$  requires less hardware. The current adaptive sample rate implementation assumes a fixed value of  $f_L(n)$  and computes  $T_L$ . A comparison is made between the computed value of  $T_L$  and a fixed value. If  $T_L$  is greater than or equal to this fixed value, the sample rate is reduced. The fixed value is chosen such that 90% of the input energy will be included in the band from dc to  $f_L(n)$ .

#### Acknowledgments

The custom short-time Fourier transform CMOS circuit was designed by Patty Damron. Jim Sorden provided the initial concept of an automatic time base and supplied the resources and management support for this development.

#### Bibliography

- 1. M.R. Portnoff, "Time-Frequency Representation of Digital Signals and Systems Based on Short-Time Fourier Analysis," *IEEE Transactions on Acoustics, Speech, and Signal Processing*, Vol. ASSP-28, February 1980, pp. 55-68.

- J.B. Allen and L.R. Rabiner, "A Unified Approach to Short-Time Fourier Analysis and Synthesis," Proceedings of the IEEE, Vol. 65, no. 11, November 1977, pp. 1558-1564.

- 3. R.W. Shafer and L.R. Rabiner, "Design and Simulation of a Speech Analysis-Synthesis System Based on Short-Time Fourier Analysis," *IEEE Transactions on Audio and Electroacoustics*, Vol. AU-21, June 1973, pp. 165-173.

- 4. A. Paupolis, Signal Analysis, McGraw-Hill, 1977.

- 5. A.N. Kolmogorov and S.V. Fomin, Introductory Real Analysis, Dover Publications, 1970.

- B. Widrow, EE373 Adaptive System Course Notes, Stanford University, 1977.

- 7. J.B. Allen, "Short-Term Spectral Analysis, Synthesis, and Modification by Discrete Fourier Transform," *IEEE Transactions on Acoustics, Speech, and Signal Processing*, Vol. ASSP-25, June 1977, pp. 235-238.

- 8. J.O. Smith and J.B. Allen, "Variable Bandwidth Adaptive Delta Modulation," *Bell System Technical Journal*, Vol. 60, no. 3, May-June 1981, pp. 719-738.

- 9. J.S. Lim, et al, "Signal Reconstruction from Short-Time Fourier Magnitude," IEEE Transactions on Acoustics, Speech, and Signal Processing, Vol. ASSP-31, August 1983, pp. 986-998.

## Waveform Reconstruction Techniques for Precision Digitizing Oscilloscopes

by Richard W. Page and Allen S. Foster

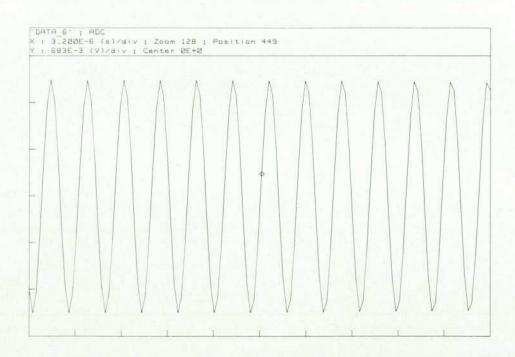

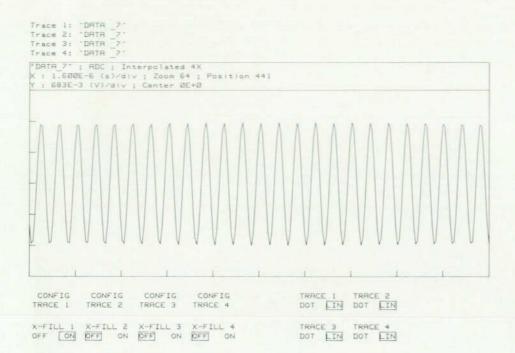

AVEFORM RECONSTRUCTION algorithms allow digitizing oscilloscopes to produce unambiguous displays, even when sampling near the Nyquist limit. In theory, a signal can be reconstructed from its samples if the sampling rate is greater than twice the highest frequency present in the signal. In other words, slightly more than two samples per cycle are theoretically enough to reconstruct a sine wave. In practice, one usually needs to sample at two or more times this Nyquist rate to get a reasonably faithful reproduction of a waveform from its samples. That is, the signal bandwidth usually cannot exceed about 50% of the digitizer bandwidth.

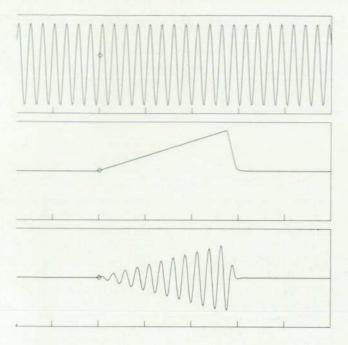

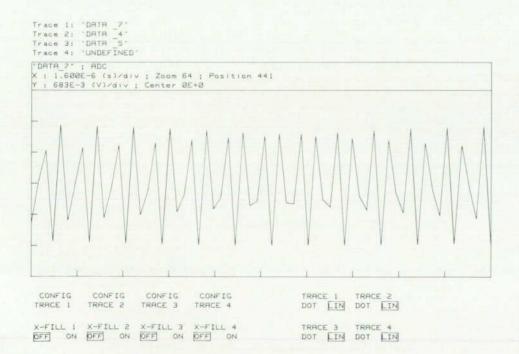

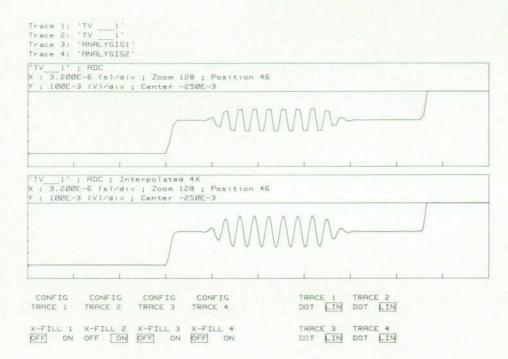

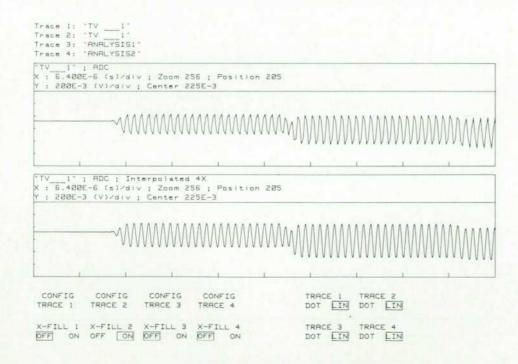

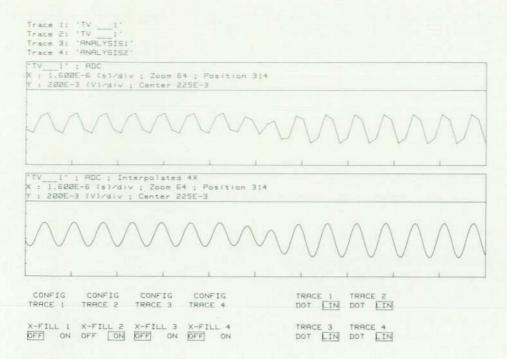

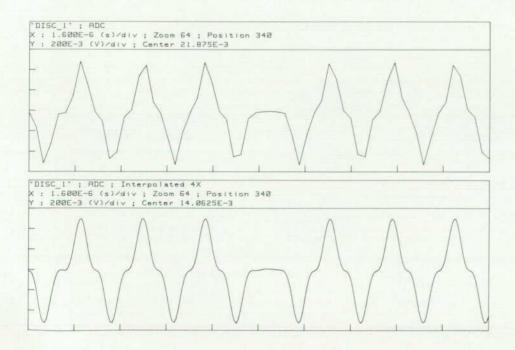

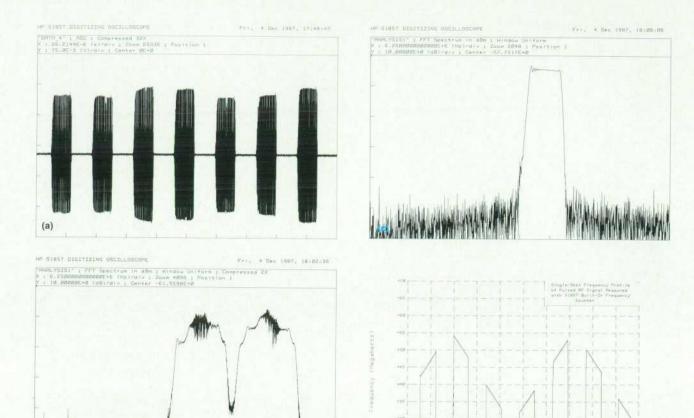

With special waveform reconstruction techniques, however, over 80% of the digitizer bandwidth can be viewed. The result is a lower-cost digitizing circuit and better use of high-speed acquisition memory. Fig. 1 shows an HP 5180T display of a sinusoid captured using 10 points per cycle without reconstruction. Fig. 2 shows a sinusoid captured using 2.5 points per cycle with reconstruction. The display of the higher-frequency sinusoid (2.5 points per cycle) is equal in fidelity to Fig. 1. In this case, waveform reconstruction increases the usable bandwidth by a factor of 4.

Comparing the reconstructed waveform to the raw data shown in Fig. 3, it is apparent that waveform reconstruction enhances postcapture processing. In particular, reconstruction allows examination of the fine structure in the data. Display measurement accuracy is increased for zero crossing, peak value, and time interval determination measurements. Waveform reconstruction provides optimum viewable bandwidth for a given digitizing rate.

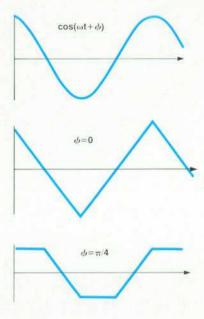

Without reconstruction, the display is typically an envelope of the minimum and maximum sample values. Fig. 4 illustrates what can happen. The signal is sampled at four points per cycle. When it changes phase, its amplitude appears to drop by 3 dB. This phenomenon arises because linear interpolation (connect the points) has been used to reconstruct the signal from its sample values. As the signal is oversampled by a larger margin, linear interpolation reconstruction becomes increasingly more reasonable and accurate. At five times the Nyquist rate, 10 points per cycle for sinusoids, linear interpolation is accurate within 5%. At this level of accuracy, reconstruction errors are acceptable. This has led to the "minimum ten sample points per cycle" rule in digitizing oscilloscopes for reasonable displays. However, the sampling theorem tells us that all of the signal information is preserved when we sample at slightly more than two points per cycle.

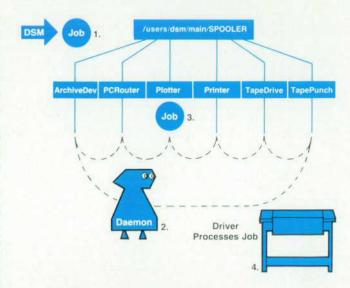

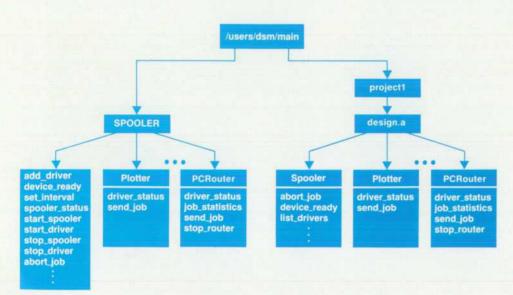

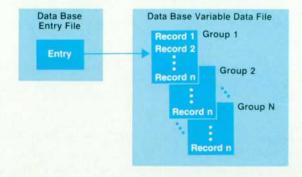

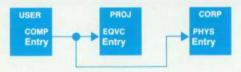

#### Representation of Signals