# HEWLETT-PACKARD JOURNAL October 1991

© Copr. 1949-1998 Hewlett-Packard Co.

# JOURNAL

# Articles

| 6  | Introduction to the HP Component Monitoring System, by Christoph Westerteicher                                         |

|----|------------------------------------------------------------------------------------------------------------------------|

| 9  | Medical Expectations of Today's Patient Monitors                                                                       |

| 10 | <b>Component Monitoring System Hardware Architecture</b> , by Christoph Westerteicher and Werner E. Heim               |

| 13 | Component Monitoring System Software Architecture, by Martin Reiche                                                    |

| 4  | Component Monitoring System Software                                                                                   |

| 5  | Component Monitoring System Software Development Environment                                                           |

| 9  | Component Monitoring System Parameter Module Interface, by Winfried Kaiser                                             |

| 21 | Measuring the ECG Signal with a Mixed Analog-Digital Application-Specific IC, by Wolfgang<br>Grossbach                 |

| 5  | A Very Small Noninvasive Blood Pressure Measurement Device, by Rainer Rometsch                                         |

| 6  | A Patient Monitor Two-Channel Stripchart Recorder, by Leslie Bank                                                      |

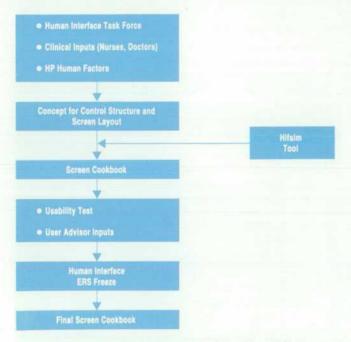

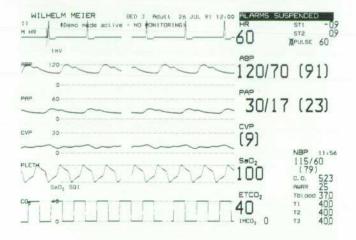

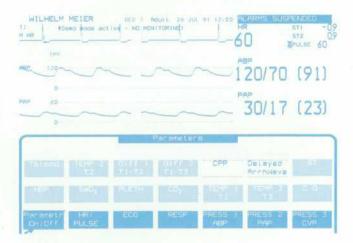

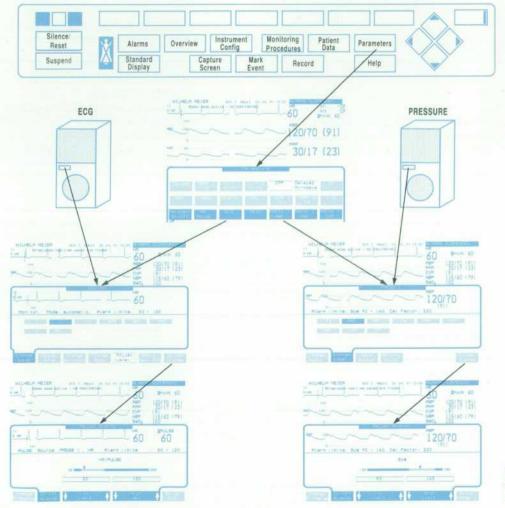

| 9  | Patient Monitor Human Interface Design, by Gerhard Tivig and Wilhelm Meier                                             |

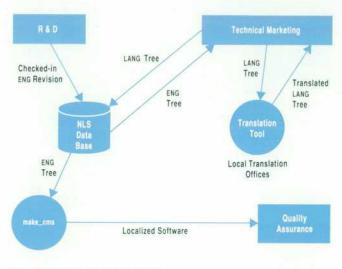

| 7  | Globalization Tools and Processes in the HP Component Monitoring System, by Gerhard Tivig                              |

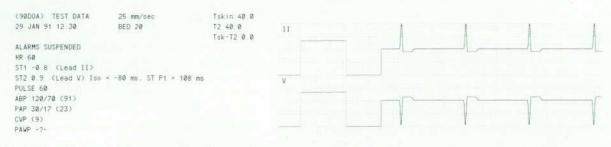

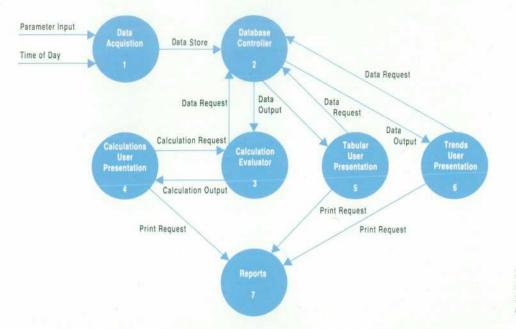

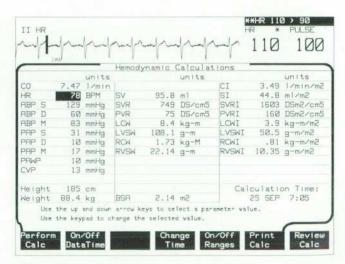

| 0  | The Physiological Calculation Application in the HP Component Monitoring System, by Steven J. Weisner and Paul Johnson |

| Λ  | Mechanical Implementation of the HP Component Monitoring System, by Karl Daumüller and                                 |

Erwin Flachsländer

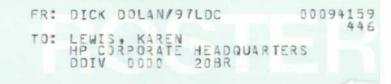

Editor, Richard P. Dolan • Associate Editor, Charles L. Leath • Contributing Editor, Gene M. Sadoff • Art Director/Photographer, Arvid A. Danielson Production Supervisor, Susan E. Wright • Administrative Services, Diane W. Woodworth • Illustration, Richard M. Dominguez • Typography/Layout, Rita C. Smith @Hewlett-Packard Company 1991 Printed in U.S.A.

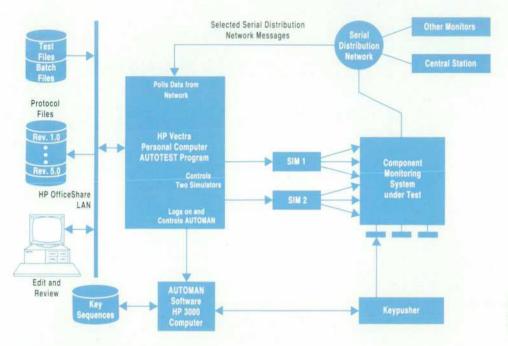

| 49 | An Automated Test Environment for a Medical Patient Monitoring System, by Dieter Göring                                                         |  |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 52 | Production and Final Test of the HP Component Monitoring System, by Otto Schuster and Joachim Weller                                            |  |

| 55 | Calculating the Real Cost of Software Defects, by William T. Ward                                                                               |  |

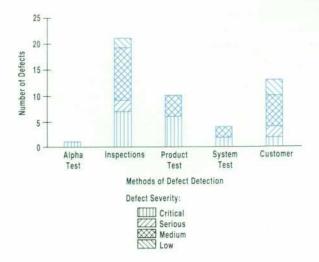

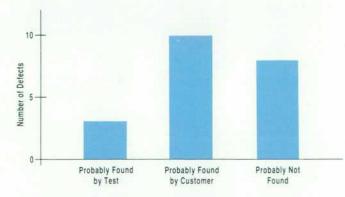

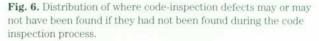

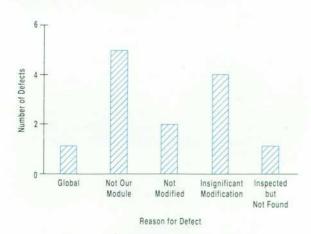

| 58 | A Case Study of Code Inspections, by Frank W. Blakely and Mark E. Boles                                                                         |  |

| 69 | The HP Vectra Personal Computer, by Larry Shintaku                                                                                              |  |

| 70 | The HP Vectra 486 EISA SCSI Subsystem                                                                                                           |  |

| 72 | The HP Vectra 486/33T                                                                                                                           |  |

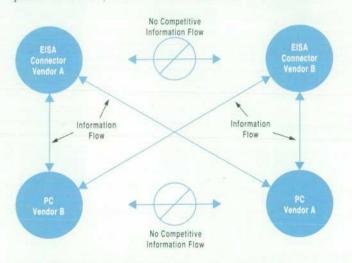

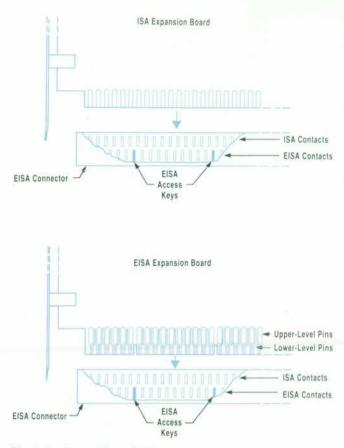

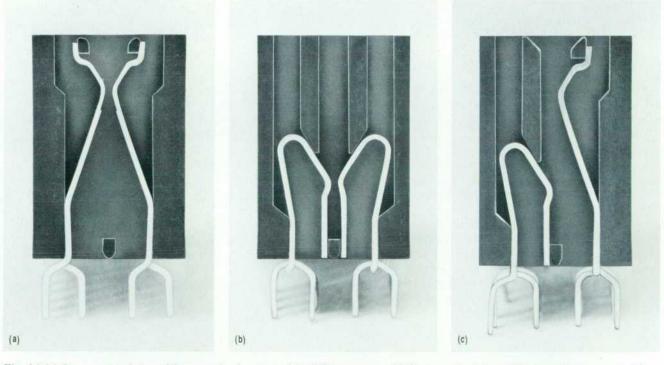

| 73 | The EISA Connector, by Michael B. Raynham and Douglas M. Thom                                                                                   |  |

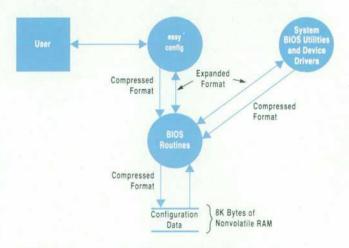

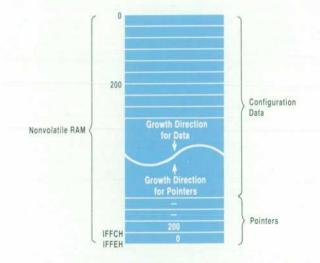

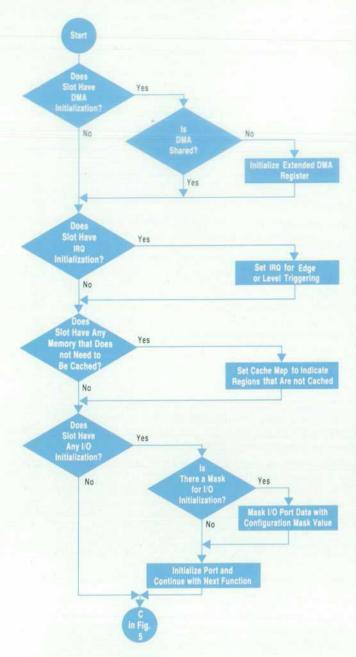

| 75 | EISA Configuration Software                                                                                                                     |  |

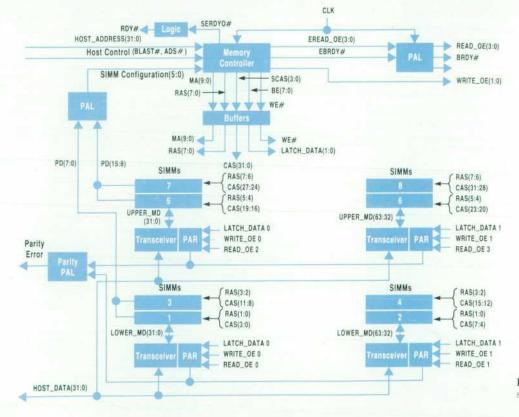

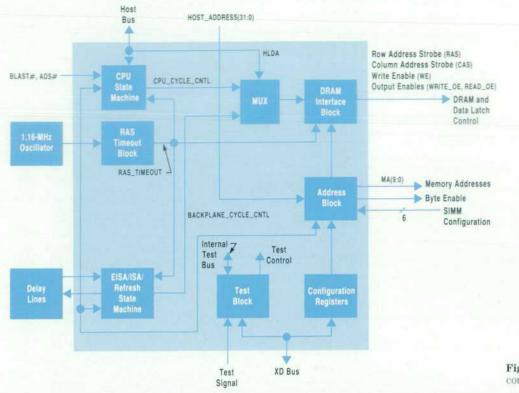

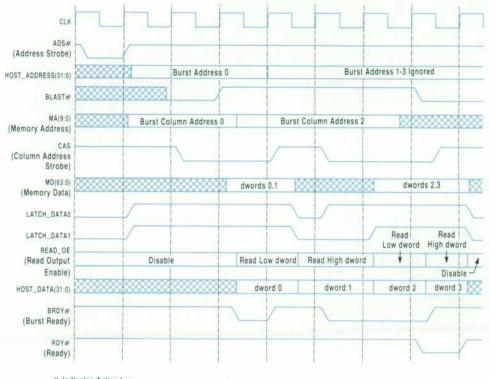

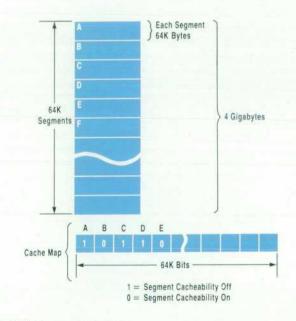

| 78 | The HP Vectra 486 Memory Controller, by Marilyn J. Lang and Gary W. Lum                                                                         |  |

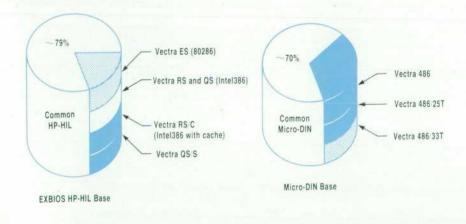

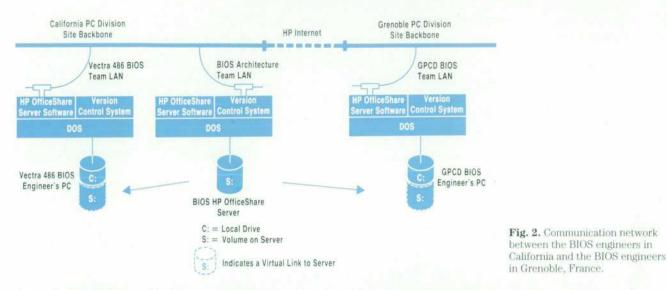

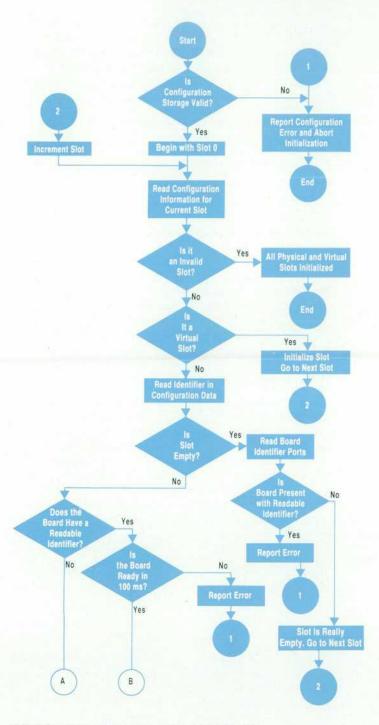

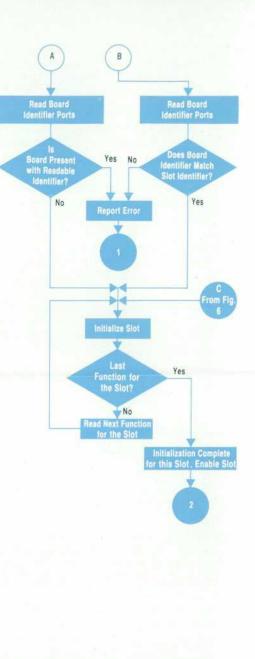

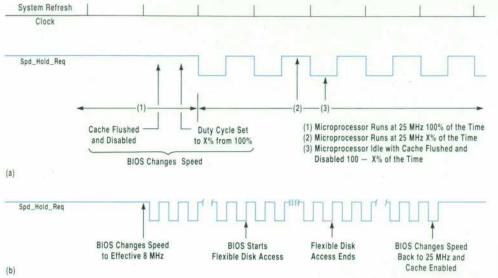

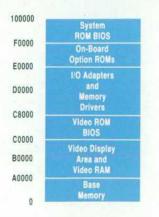

| 83 | <b>The HP Vectra 486 Basic I/O System</b> , by Viswanathan S. Narayanan, Thomas Tom, Irvin R. Jones Jr., Philip Garcia, and Christophe Grosthor |  |

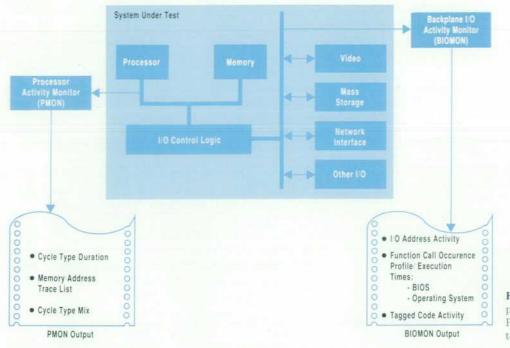

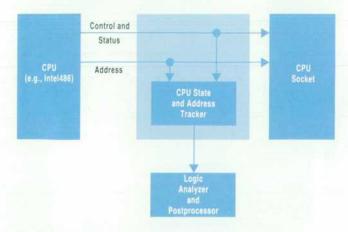

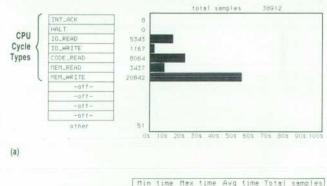

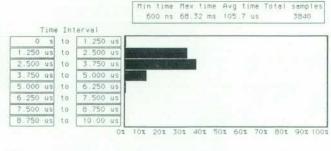

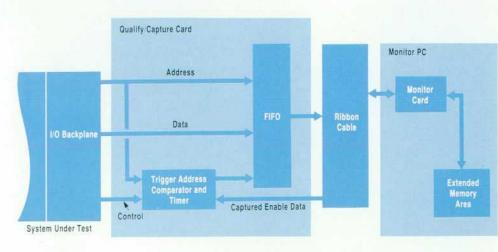

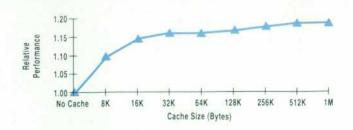

| 92 | Performance Analysis of Personal Computer Workstations, by David W. Blevins, Christopher A. Bartholomew, and John D. Graf                       |  |

# Departments

- 4 In this Issue5 What's Ahead64 Authors

# In this Issue

While cost containment is certainly the most publicly visible concern in medical care today, hospitals are under just as much pressure to improve the quality of patient care. Since they can invest in new equipment only every seven to fifteen years, hospitals want that equipment to be easy to upgrade and adapt to new technologies. In designing HP's fourth-generation patient monitoring system, the engineers at HP's Medical Products Group had to deal with these and other issues influencing their hospital customers' investment decisions. The design of the new system, which they call the Component Monitoring System, emphasizes modularity, flexibility, and ease of use while addressing the increasing need to measure new patient parameters and to process this

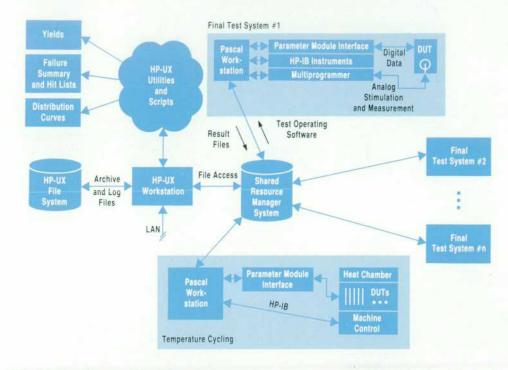

information using powerful algorithms and data management tools. The article on page 6 introduces the system and its overall architecture, while details of the hardware and software architectures can be found in the articles on pages 10, 13, and 19. The necessary functions of data acquisition, parameter signal processing, display, and system connections are implemented as hardware and software building blocks. Application software modules, such as the blood pressure measurement software, can be arbitrarily assigned to any CPU in a loosely coupled multiprocessor system. The applications think that they are running on a nonexistent virtual processor. The architecture makes it easy to configure the system for both current and future needs in the operating room, intensive and cardiac care units, and other hospital areas, and contributes to a greatly simplified, low-cost production and test process. Patient parameters such as blood pressure, the electrocardiogram (ECG), blood gases, temperature, and others are measured by state-of-the-art modules that can be located close to the patient while the signal processor and displays can be in another room, if necessary. The ECG, blood pressure, and recorder modules are described in the articles on pages 21, 25, and 26. The system not only provides the clinician with the raw data measured by these modules, but also processes it, as explained in the article on page 40, to obtain many meaningful indicators of physiological functions, such as ventricular ejection and systemic vascular resistance. Ease of use is delivered by a thoroughly tested user interface design (see page 29), which can be localized easily for most languages (page 37). Mechanical design, software testing, and production and final test of the Component Monitoring System are the subjects of the articles on pages 44, 49, and 52.

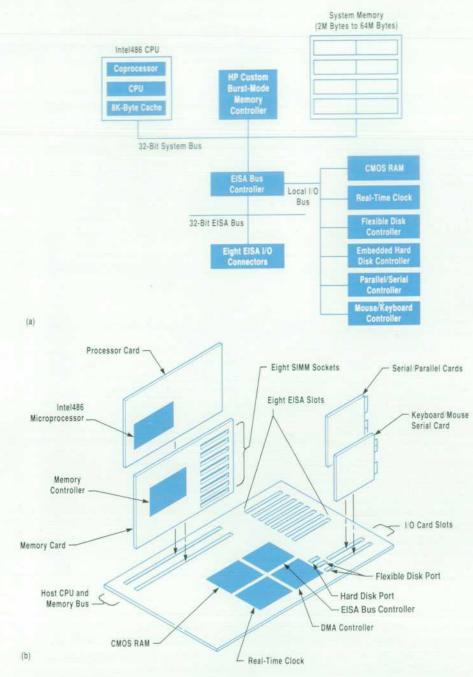

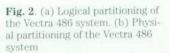

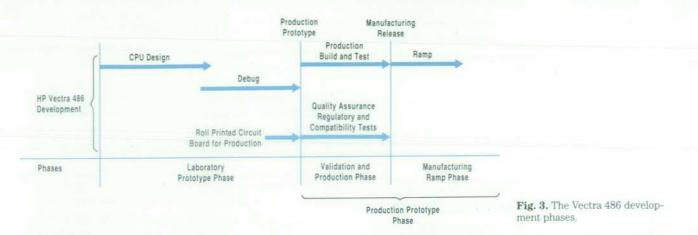

The personal computer, or just PC, based on the Industry Standard Architecture (ISA) pioneered by the IBM PC, has gained steadily in processing power as each new generation of Intel microprocessors was introduced. The HP Vectra 486 PC uses not only the latest-generation microprocessor, the Intel486, but also the new Extended Industry Standard Architecture (EISA). The Intel486 integrates the CPU, a cache memory, and a math coprocessor onto one chip running at 25 or 33 megahertz. The EISA takes the 16-bit ISA bus to 32 bits while maintaining compatibility with all ISA I/O cards. The design of the HP Vectra 486 shows that designers can still contribute creatively within the constraints of industry standards. Among the design contributions are an architecture that incorporates all of the new technical features of the EISA and adapts easily to faster versions of the Intel486, a bus connector that accommodates both EISA and ISA cards, a burst-mode memory controller, a high-performance hard disk subsystem, and enhancements to the Vectra's basic I/O system (BIOS) to take advantage of all of the new features. An overview of the Vectra 486 design appears on page 69, and the articles on pages 73, 78, and 83 discuss the connector, memory controller, and BIOS designs. Performance analysis of many of the design concepts was done using a specialized hardware and software toolset, allowing the designers to make critical design trade-offs before committing to hardware (see page 92).

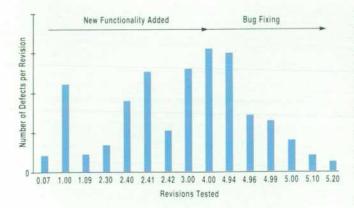

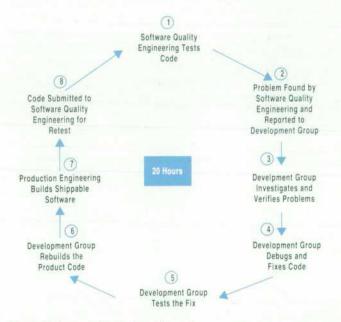

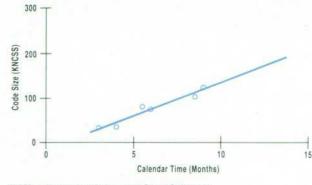

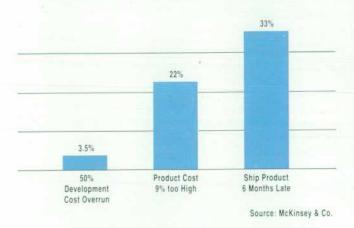

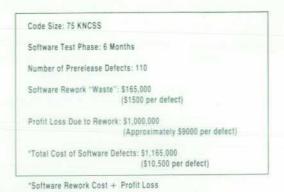

How much does a software defect cost in terms of unnecessary expense and lost profit? Why is it important to know? As Jack Ward of HP's Waltham Division explains in the article on page 55, if you're trying to justify the cost of a new software development tool, it helps to know what the tool will save by reducing software defects. He proposes an algorithm for computing the cost of software defects, applies it to a five-year database of software product releases, and shows that defect prevention and early removal can save a lot of money.

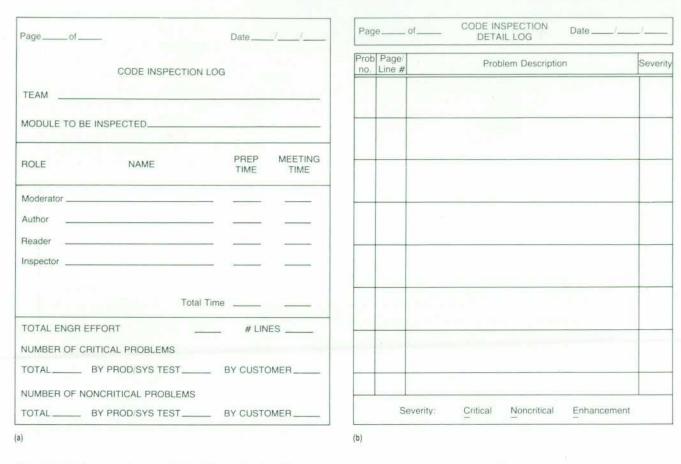

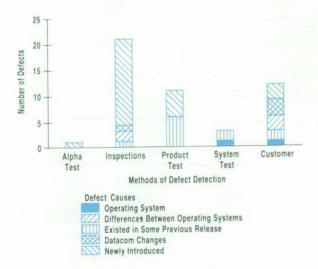

Code inspections are now standard procedure in many software development organizations. Are they effective? The article on page 58 describes the results of one HP division's effort to collect data to find out. There are both positive and negative findings, but the conclusion is that formal inspections are beneficial, while the value of informal inspections is still open to question.

R.P. Dolan Editor

# What's Ahead

The December issue will feature HP Sockets, a software tool for integrating applications in a network environment. An article from HP Laboratories in Bristol, England will introduce HP's formal specification language, HP-SL, and four articles will present examples of the use of HP-SL in software development. Another article will describe the HP Network Monitoring System for telecommunications networks using the 2-Mbit/s primary rate interface and the CCITT R2 or #7 signaling system. The 1991 index will also be included.

The Hewlett-Packard Journal is published bimonthly by the Hewlett-Packard Company to recognize technical contributions made by Hewlett-Packard (HP) personnel. While the information found in this publication is believed to be accurate, the Hewlett-Packard Company disclaims all warranties of merchantability and fitness for a particular purpose and all obligations and liabilities for damages, including but not limited to indirect, special, or consequential damages, attorney's and expert's fees, and court costs, arising out of or in connection with this publication.

Subscriptions: The Hewlett-Packard Journal is distributed free of charge to HP research, design and manufacturing engineering personnel, as well as to gualified non-HP individuals, libraries, and educational institutions. Please address subscription or change of address requests on printed letterhead (or include a business card) to the HP address on the back cover that is closest to you. When submitting a change of address, please include your zip or postal code and a copy of your old label.

Submissions: Although articles in the Hewlett-Packard Journal are primarily authored by HP employees, articles from non-HP authors dealing with HP-related research or solutions to technical problems made possible by using HP equipment are also considered for publication. Please contact the Editor before submitting such articles. Also, the Hewlett-Packard Journal encourages technical discussions of the topics presented in recent articles and may publish letters expected to be of interest to readers. Letters should be brief, and are subject to editing by HP.

Copyright © 1991 Hewlett-Packard Company. All rights reserved. Permission to copy without fee all or part of this publication is hereby granted provided that 1) the copies are not made, used, displayed, or distributed for commercial advantage; 2) the Hewlett-Packard Company copyright notice and the title of the publication and date appear on the copies, and 3) a notice stating that the copying is by permission of the Hewlett-Packard Company.

Please address inquiries, submissions, and requests to: Editor, Hewlett-Packard Journal, 3200 Hillview Avenue, Palo Alto, CA 94304 U.S.A.

# Introduction to the HP Component Monitoring System

This fourth-generation patient monitoring system offers a set of hardware and software building blocks from which functional modules are assembled to tailor the system to the application and the patient.

# by Christoph Westerteicher

Over the past twenty years HP has been a supplier of patient monitoring equipment to the healthcare industry. Patient monitors are observational and diagnostic tools that monitor physiological parameters of critically ill patients. Typical parameters include the electrocardiogram (ECG), blood pressure measured both invasively and noninvasively, pulse oximeter (SaO<sub>2</sub>), and respiratory gases, among others. The catalog of parameters is still growing based on the need for better patient care and the technical feasibility of new measurement techniques.

Patient monitors are used in a variety of departments within hospitals. These include operating rooms, intensive care units, cardiac care units, in-hospital and out-of-hospital transportation, and special function areas such as lithotripsy and x-ray. A patient monitoring system must be versatile and applicable to most of these areas. This means that it must support a wide range of configurations and allow quick adaptation to the patient-specific level of care. For a normal appendectomy, monitoring the ECG, noninvasive blood pressure, SaO<sub>2</sub>, and one temperature will suffice. At the other extreme, during a cardiovascular operation as many as eight different physiological parameters will be measured.

The HP Component Monitoring System is designed to meet these requirements. This article outlines the high-level project goals and the approaches taken to meet them. It also describes the overall hardware and software architecture of the HP Component Monitoring System. Subsequent articles in this issue highlight the technical contributions of the Component Monitoring System project in more detail.

# **Design Goals**

The HP Component Monitoring System is the fourth generation of patient monitors to be designed and built by the HP Medical Products Group. Based on our experience, current customer needs, and expected future trends in the medical field, two objectives were viewed as areas in which HP could make a major contribution. One is the area of modularity and flexibility and the other is ease of use.

**Modularity and Flexibility**. The monitor is composed of the following functional modules:

- Data acquisition

- Parameter signal processing

- Monitor control and data input

- Display

- System connects.

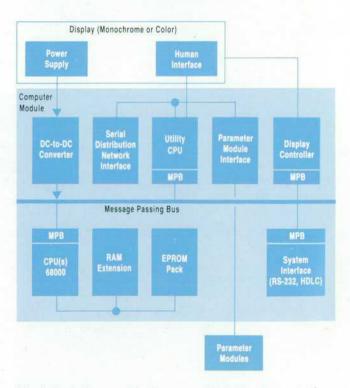

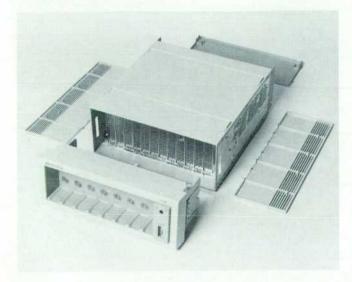

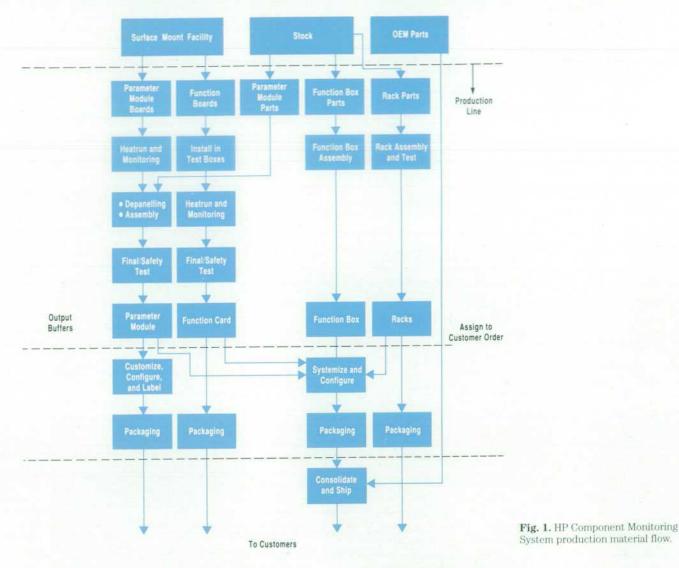

Each of these functional modules is implemented in a set of hardware and software building blocks, which as a whole form the Component Monitoring System depicted in Fig. 1. Separating the monitor into its generic elements provides many advantages. First, the monitor can easily be configured to best meet the application needs of the individual customer. Parameters can quickly be combined according to the required level of care and changed when necessary. Second, adding functionality to a monitor is as simple as inserting the appropriate hardware into an existing unit and updating the software if necessary.

A third advantage is that the Component Monitoring System can be kept abreast of new technological trends by

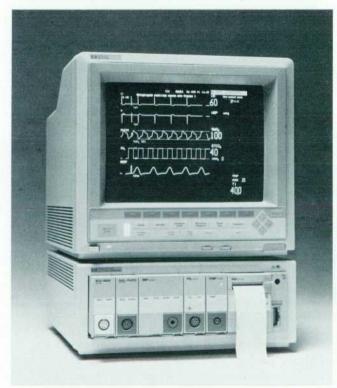

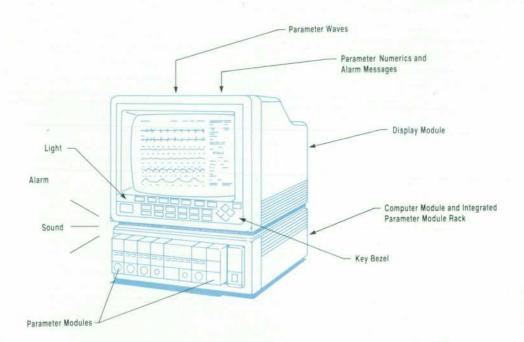

Fig. 1. In the HP Component Monitoring System, a fourth-generation patient monitor, each functional module is implemented in a set of hardware and software building blocks.

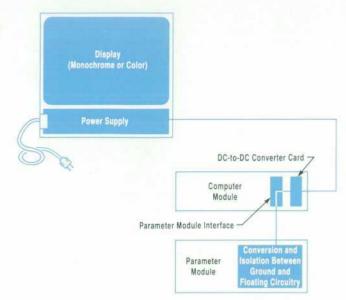

Fig. 2. The Component Monitoring System architecture has three segments: the module rack and parameter modules, the computer module, and the displays. The module rack can be either an integral part of the computer module or totally detached. A remote keypad is optional.

enhancing or redesigning the appropriate functional element. Implementation will only affect one building block, and will be fully backward compatible with existing systems.

Finally, production has been dramatically simplified. Customization of each monitor is the last integration step in production. Thus, all components can be assembled and tested without knowing the specific configuration in which they will be used.

Flexibility is enhanced by designing the monitor components so that their physical location can be optimized to address ergonomic considerations and by allowing the user to program the monitor's default settings and standard configuration. This means that the monitor can be adapted to a wide range of current and future clinical applications.

**Ease of Use.** Ease of use is of particular importance for patient monitors in operating rooms and critical care units, where clinicians use patient monitors to make informed decisions about potentially life-threatening situations. In the past, clinicians have had to strike a compromise between the desired functionality of a patient monitor and its ease of use. Our goal was to make this very sophisticated piece of equipment truly intuitive for doctors and nurses to use. Other areas that we focused on, and that played an important role during the development phase were:

- Implementation of methods to meet HP quality goals.

- Minimization of production costs and support for a linear cost profile. This means that functionality can be segmented down to its generic building blocks. Should a particular feature be needed, the customer pays for it and nothing more.

- Standardization, ranging from uniform design tools and software development environments all the way to minimizing the number of different electrical components used in the Component Monitoring System as well as the number of mechanical parts needed to assemble the unit.

# System Architecture

From an architectural standpoint the Component Monitoring System can be divided into three segments (see Fig. 2):

- Module rack with parameter modules

- Computer module

- Displays.

The module rack and parameter modules represent the interface to the patient. Each parameter module is dedicated to the measurement of one or more physiological signals, and is housed in a separate enclosure. Within the parameter modules, the transducer signals are electrically isolated from ground potential, amplified, sampled, and converted from an analog to a digital format. The digital parameter values together with the status of each module are polled at fixed intervals and sent to the computer module for further interpretation.

Up to eight single-width modules fit into one module rack. The module rack can be either an integral part of the computer module or totally detached, in which case it would be called a satellite module rack. The satellite module rack is connected to the computer module by an umbilical-cord-like cable, which carries both the digital signals and a 60V dc power line for the parameter modules. One computer module can support as many as four satellite module racks. This concept allows the user to position the parameter modules as close as possible to the patient, where the signal is measured. The transducer cables can thus be kept short, minimizing the amount of wiring as well as the tendency for it to become tangled or draped over the patient.

### **Computer Module**

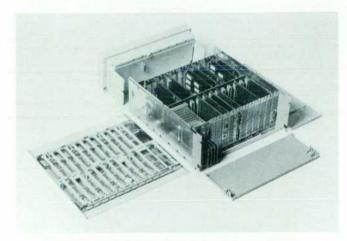

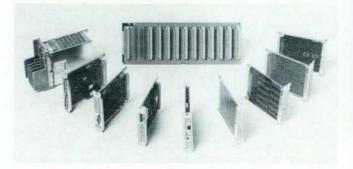

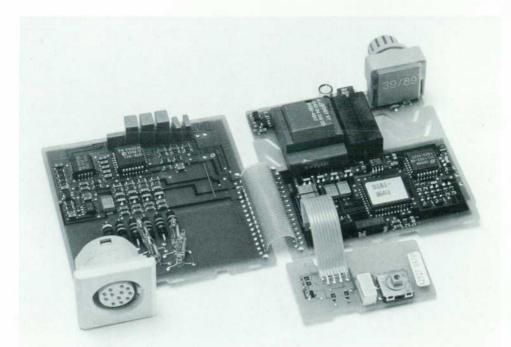

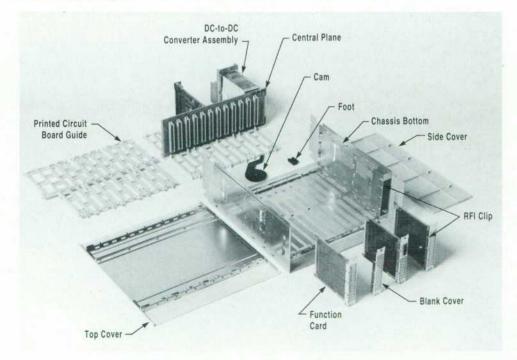

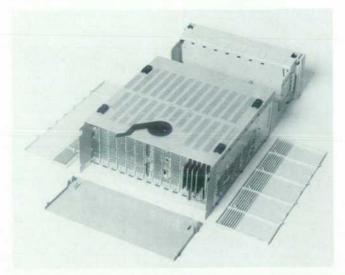

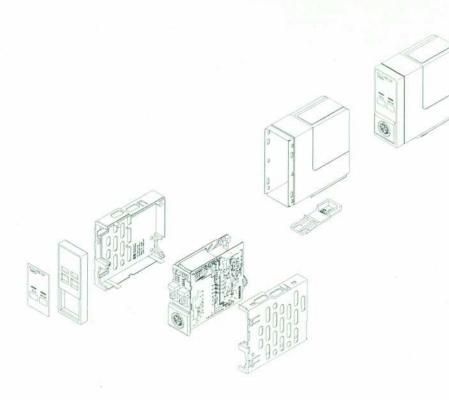

The computer module is the main processing unit. It consists of a cardcage that can house up to 23 function cards and one dc-to-dc converter (Fig. 3). Function cards currently available include CPUs, memory cards, interface cards, display controllers, and a utility card. For the first release, a total of 11 function cards were designed. The interconnection within the cardcage takes place via the central plane, a motherboard located in the middle of the chassis with press-fit connectors mounted on both sides

Fig. 3. The computer module houses up to 23 function cards.

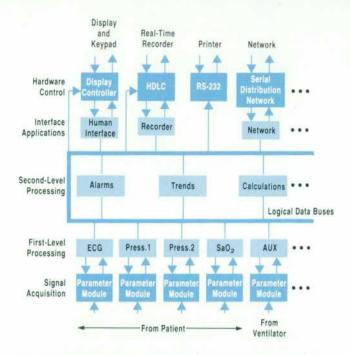

Fig. 4. Functional block diagram of a Component Monitoring System patient monitor. The shaded boxes are software functions on the CPU card processors. The solid boxes are specific hardware and firmware functions.

of a printed circuit board. Data exchange between the function cards takes place on the message passing bus. This bus is routed to all 23 slots on the central plane, allowing a high degree of freedom as to where a function card can be inserted. The message passing bus is the backbone of the Component Monitoring System. Many of the goals listed above only became possible with the help of this communication concept.

The basic function of the message passing bus is that of a broadcast system. Each message sent on the bus consists of a header, which describes the content, and the actual data. A source (e.g., a CPU card) will obtain control of the message passing bus and transmit its information. The data is not transmitted in a point-to-point fashion from one source to one receiver. Instead, message passing bus data is transmitted without any specific destination, and it is up to the function cards to watch for the information needed by their applications. As soon as a card detects a match between a header it is looking for and the header of the message on the bus, it automatically pulls this data into an internal stack.

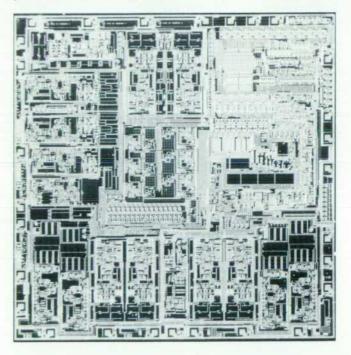

The activities of bus arbitration, transmission, header matching, and data reception are controlled by the message passing bus chip. One of these interface chips is located on each function card that actively takes part in the communication process. The chip was designed specifically for the Component Monitoring System. It also was the first HP production ASIC (application-specific IC) to be designed using a silicon compiler tool.

A more detailed description of the message passing bus concept and the design of the interface chip can be found in the article on page 10, which covers the Component Monitoring System hardware architecture.

### Displays

The customer can choose either a monochrome or color high-resolution display. Multiple independent displays can be used to present different sets of information to specific user groups. For example, the surgeon needs a different presentation of patient information than the anesthesiologist during surgery.

Physically separating the display from the computer module gives the user a choice of screen sizes and the possibility of mounting the computer module at a remote location when space next to the patient is at a premium.

The user interacts with the monitor through a combination of hardkeys and softkeys on the display keypad or through a remote keypad which functionally duplicates the keys on the display bezel.

# Software Modularity

The concept of a modular system also applies to the software architecture (see Fig. 4). Application-specific modules represent the basic building blocks out of which the total solution can be assembled. The ECG application, for example, including the signal interpretation, alarm handling, and control interaction, is all encapsulated in one module. To the surrounding environment these application software modules are totally self-contained packages, and only exchange information with one another via the message passing bus. By virtue of this concept, it is possible to link each module as an independent entity with any of the other modules and assign it to one of the Component Monitoring System CPU cards.

A more detailed description of the software architecture can be found in the article on page 13.

All of the Component Monitoring System software is stored on EPROM function cards. These cards are physically located next to a CPU, and the applications running on that CPU execute directly from the adjacent memory card. All other CPU cards in the monitor get their application software downloaded into the on-board RAM during boot time. The advantage of this solution is that installing software is as easy as inserting one EPROM card.

# Summary

The Component Monitoring System has proved that the concept of component modularity can be extended far beyond the mere ability to mix and match parameter modules. Modularity in this system means that the customer can tailor the patient monitor to best fit the application all the way from the parameters that need to be registered to the displays and interfaces the system should incorporate. The Component Monitoring System can also grow with the user's needs over time, and thus secure the hospital's assets for many years.

The success of the modularity concept is reflected in the fact that some of the hardware and software elements have found their way into other medical devices manufactured by HP. Overall, the Component Monitoring System architecture has proven it can function as a monitoring platform for years to come.

(continued on page 10)

# Medical Expectations of Today's Patient Monitors

HP has been a supplier of patient monitors since the mid-1960s. The HP 7830, HP 782xx, HP 7835x, and HP 7853x monitors have measured vital signs like ECG, blood pressure, body temperature, carbon dioxide, inspired oxygen, and others.

Over the years, customer demands and measurement technology have both developed. Simple ECG monitors have gradually become complex monitoring solutions, acquiring, processing, displaying, and storing many parameters. These modern monitors need to communicate over dedicated LANs, both with one another and with central stations. For this purpose, several years ago, HP introduced a serial distribution network (SDN), which makes it possible to transmit a multitude of parameters, high-resolution waveforms, and other information to as many as 32 participants in a synchronous way. These features are not easily achievable with modern asynchronous LANs.

#### **Medical Expectations**

Most of today's patient monitors do not satisfactorily fulfill many of the current and future expectations for these systems. The increasing need to measure new parameters and to postprocess this information using powerful signal processing algorithms and data management tools require a different approach. At the same time, our customers are under tremendous cost containment pressure, allowing them to invest in new equipment only in cycles of seven to fifteen years. Having these and other customer needs in mind, we launched a development program for a new patient monitoring system. The goals of our project were to:

- Develop a solution that can be easily adapted to our worldwide customers' medical as well as financial needs.

- Develop a user interface that allows the user to control the system easily through different means including softkeys, touch, and remote keyboards (see article, page 29).

- Develop a solution for all major languages, including Asian languages.

- Develop a solution that is backwards compatible with the existing LAN (SDN) and future LAN implementations.

- Develop a solution corresponding to our customers' space restrictions. This often means acquiring measurement data close to the patient to avoid the so-called "spaghetti syndrome"—too many cables around the patient—and processing and displaying the measurement data farther away from the patient.

Develop a solution that allows additional CPUs to be added to the system according to the signal processing needs, and that provides independent displays that can be addressed directly.

#### Conclusion

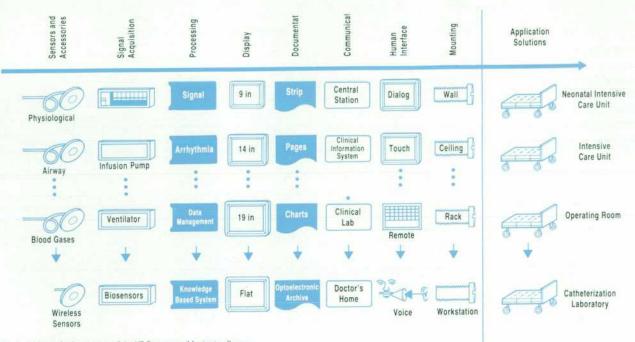

The HP Component Monitoring System is our solution to these needs. Fig. 1 shows the bedside monitoring concept of this system. Expansion is possible both horizontally and vertically in this matrix. The horizontal axis shows the various functional needs, while the vertical axis shows various ways in which these needs are met in specific applications. The last row of the matrix shows examples of possible future capabilities that can be added easily to the Component Monitoring System if and when they become available.

The HP Component Monitoring System is an ultraflexible patient monitoring system that can be adapted to almost all monitoring needs that arise in hospitals worldwide. Its built-in modularity and an HP proprietary message passing bus make it independent of technology changes in microprocessors, LANs, or displays. This is expected to result in a very long product lifetime, thereby protecting our customers' investments. By offering different configurations of the Component Monitoring System, we provide a wide price/performance range, and through a flexible upgrade strategy, we ensure high adaptability to our customers' future needs.

The Component Monitoring System is a truly international development that involved engineers in the U.S.A. and in Europe. Today, it is being manufactured at two HP sites, one in Europe and one in the U.S.A.

Such a significant technology step can never be taken without encountering challenges. Thanks to the engagement and dedication of all of the team members, these challenges were met successfully.

> Frank Rochlitzer General Manager Surgical and Neonatal Care Business Unit

Fig. 1. The bedside monitoring concept of the HP Component Monitoring System.

# Acknowledgments

The design of the Component Monitoring System has been a team effort involving at times up to 50 engineers located at the Waltham and Böblingen Medical Divisions. All of these individuals and many others deserve recognition for their hard work to make this product a success. I would also like to thank all who contributed to this series of articles on the Component Monitoring System. Besides the authors of each chapter, and the numerous unnamed supporters, one person deserves particular recognition: Heike Schreiber. Her continued enthusiasm and devotion helped to make this issue of the HP Journal possible.

# **Component Monitoring System Hardware Architecture**

Up to 23 function cards residing in a computer module communicate over a message passing bus. The computer module, the display, and the parameter modules that measure vital signs can be in separate locations as needed by the application.

# by Christoph Westerteicher and Werner E. Heim

The prime objective in the development of the HP Component Monitoring System was to build a patient monitor that would adapt optimally to the majority of clinical applications, now and in the foreseeable future. To the R&D team, this meant modularity, but not just in the sense of being able to mix and match parameters. The goal of this project was to carry the idea of configurability a quantum leap into the future.

# **Major Parts**

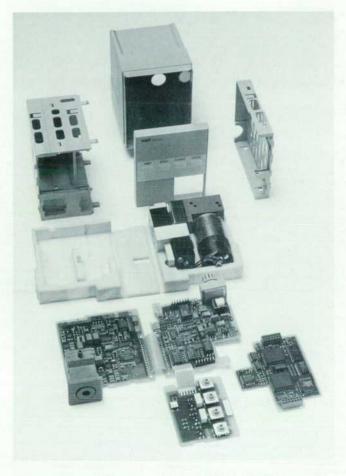

The Component Monitoring System can be segmented into three parts (Fig. 1):

- The rack and parameter modules

- The computer module

- The display.

This segmentation is not just a theoretical way of looking at the Component Monitoring System. The system can actually be separated into these components. It is therefore possible to place the parameter modules close to the patient and position the display within sight of the anesthesiologist, while the computer module can be totally removed from the vicinity of the patient.

# **Computer Module**

The computer module incorporates all the processing power, the interfaces to other devices and networks, the display controllers, and drivers for human interface equipment.

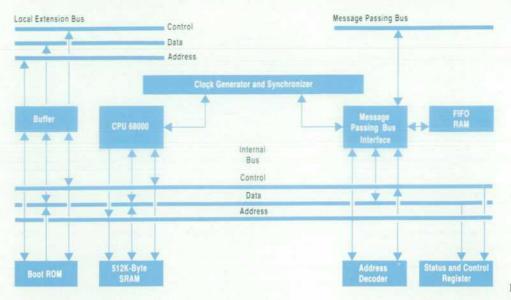

These functional elements have been broken into their generic components, and then designed and implemented as individual function cards. The processing power, for example, is provided by an application dependent number of CPU cards, working together as a loosely coupled multiprocessor system. Based upon a 16/32-bit microprocessor, each CPU card is an independent subsystem, includ-

Fig. 1. Block diagram of the Component Monitoring System hardware architecture.

Fig. 2. CPU card block diagram.

ing a large amount of static memory, boot EPROM, and an interface chip for the computer module's internal bus, the message passing bus (Fig. 2). The ability to work as a self-contained, independent entity was the smallest common denominator we wanted to apply to our computer module building blocks. Because of this concept, processing power, interface cards, or display controllers can be added depending upon the customer's application. New function cards can be added by plugging them into the computer module without interfering with the existing configuration.

Local resources of a function card, like static memory or EPROM, can be extended by adding a battery-buffered static RAM card and an EPROM card. They connect to a local extension bus, which is routed on the same connector as the message passing bus, thus allowing an identical design for all slots on the backplane.

At first release of the Component Monitoring System, there are 11 function cards. The spectrum includes the above-mentioned processor and memory cards, interface cards to RS-232 devices and HP's medical signal distribution network (SDN), high-resolution monochrome and color display controllers, and other cards.

Each function had to fit onto the standard function card. To make this possible, several application-specific integrated circuits (ASICs) provide high performance in a minimum of card space. Surface mount technology allows components in very small packages to be mounted close together directly on the surface of a function card. The benefits of these new technologies are highly automated production processes, reduced part count, and increased reliability.

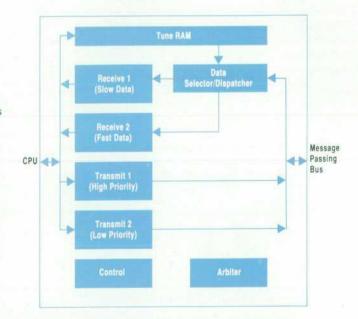

# Message Passing Bus

The message passing bus represents the backbone of the Component Monitoring System. It is by virtue of this solution that it was feasible to implement modularity in such an extensive fashion.

The message passing bus is based on a message broadcasting system, in which one bus participant transmits information without having to specify the address of the receiving device. Instead, every message is classified by a header, indicating the content of the message. A bus participant interested in a specific class of messages writes the header of the information and a priority into the signature RAM of its message passing bus interface. When the header of the message on the bus and the header in the signature RAM match, the receiving card's message passing bus interface automatically loads that message into its FIFO buffer. Depending on the priority assigned, the incoming information is pushed into either the high-priority or the low-priority FIFO, thereby preprocessing data for the CPU. Comparing headers and moving information into and out of the FIFOs is controlled by the message passing bus interface chip with no interaction from the data processing device. Fig. 3 is a block diagram of this chip.

The major advantages of this concept are threefold. First, messages only need to be sent once, regardless of the number of bus participants interested in the information. This guarantees that bus bandwidth is not used merely to

Fig. 3. Message passing bus interface chip block diagram.

duplicate messages going to multiple receivers. Second, the absolute bus bandwidth is defined by the speed of the message passing bus interface chip. The chip controls the transmit and receive FIFOs and compares headers without support from the data processing device. In essence, the message passing bus chip is a buffer between a high-speed bus and data processing logic working at varying speeds, which should not be interrupted by every bus activity if it is to function effectively.

The third major advantage of the message passing concept is that new system cards can be added to a monitor, and as long as they know the algorithm for allocating headers, they can actively participate on the message passing bus. The bus has a decentralized arbitration algorithm, which determines how each participant accesses the bus. Each interface chip incorporates arbitration circuitry based on a round-robin-like system, assigning the bus on a rotating priority basis. If the current bus master is level n, priority n-1 will be given to the next interface requesting the bus, and so on sequentially. This guarantees that the bus is shared equally among all of the function cards and is dynamically distributed every time a message is sent.

The message passing bus chip was designed as an ASIC, using a silicon compiler tool to develop and simulate the circuit's functionality.

# **Central Plane and Power Concept**

In the center of the computer module chassis is a 23-connector motherboard with press-fit sockets mounted on both the front and the rear. The message passing bus is routed to all 23 slots on this central plane (Fig. 4).

Since all of the function cards are mechanically identical in size, any card can be inserted into any slot of the central plane, thus making possible a wide range of configurations. The only exemption is the dc-to-dc converter, which always is located in the same slot. This one card provides the power for the computer module, and is sourced with 60V directly from the Component Monitoring System display (Fig. 5).

This somewhat uncommon power architecture was necessary to comply with the stringent leakage current limits imposed on medical equipment. If the Component Monitoring System were to incorporate separate power supplies in the display and the computer module, the leakage currents of both to ground would be added together, making it very difficult to reduce this value to below 100  $\mu$ A.

Fig. 4. Computer module central plane and function cards.

Fig. 5. Power concept. The single power supply is housed in the display.

The second reason for taking the power supply out of the computer module was the need to reduce the amount of heat dissipated in this small box to a minimum, so as not to jeopardize reliability. We therefore decided to have only one power supply for the entire Component Monitoring System, and to house this in the display.

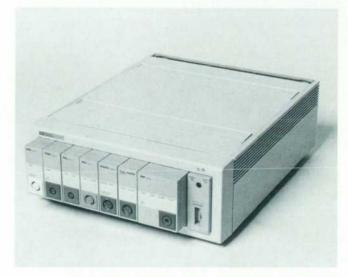

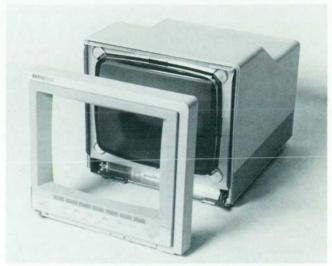

# The Display

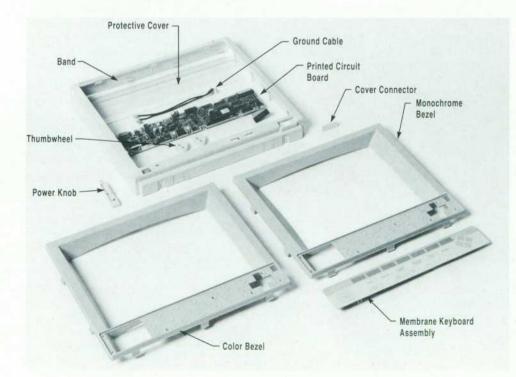

Customers can choose either a monochrome or color 14-inch display (Fig. 6). These are high-resolution, noninterlacing, high-contrast displays designed and built specifically for medical applications.

To provide outstanding waveform quality, the displays and the display controllers have a very high horizontal resolution of 2048 pixels. At this pixel spacing the human eye can no longer resolve the individual dots, so the curves appear very smooth.

The displays also incorporate the Component Monitoring System control panel, located beneath the screen. This control panel is the main means of interacting with the monitor. It consists of a membrane keyboard, LED indica-

Fig. 6. The display also incorporates the control panel.

tors, and the human interface board, which is an HP-HIL device looped through to the computer module.

#### Summary

The hardware architecture has proven to be one of the steps on the ladder to success of the Component Monitoring System. With the advent of this new monitor, production has been automated and streamlined to an extent unheard of for such a complex device as a patient monitor. The parts standardization effort has resulted in a mere 300 different items for the entire system. Our customers can now have a state-of-the-art monitoring system that they can configure to their specific needs, and at the same time be assured that their system has been designed to stay abreast with technological or application changes for many years to come.

# Acknowledgments

For their outstanding results, for their endurance, and for being a most enjoyable team to work with, our thanks go to all members of the Component Monitoring System hardware group.

# **Component Monitoring System Software Architecture**

A modular design leads to a complex but easily manageable system that ensures economical resource utilization.

# by Martin Reiche

HP Component Monitoring System patient modules can be mixed and matched to suit the application. A module is added simply by plugging it into any free slot in the module rack. Wouldn't it be convenient to handle all functions implemented as software the same way? Just find a free resource on any CPU card and assign the required set of software building blocks to it. Use only as many CPUs as necessary. This article will show that this approach is not only viable, but also appropriate in terms of both development economics and resource utilization.

The basic idea of having building blocks with standardized interfaces that can be arbitrarily combined has proven its power in many projects. The Component Monitoring System patient signal acquisition system, computer module, and message passing bus concept reflect this idea well.

This approach should also be promising for software. However, a problem with software is its complexity, both internally and in terms of interaction with external entities. Component Monitoring System software modules show significantly different profiles in resource requirements, must share a multiprocessor real-time system in varying configurations without conflicts, have to act and communicate in a meaningful way with regard to the current configuration, and are implemented by different people in different places at different times. This makes standardization difficult. We will show how these problems were overcome, both from an architectural point of view and from a development environment perspective. As we proceed, we will encounter a continuously recurring question in different contexts: How can we provide the needed creative freedom for each individual, and at the same time manage their cooperation and integration into a coherent total solution?

## Layered Software

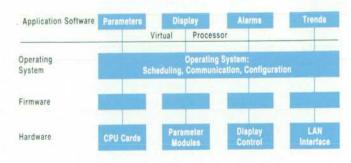

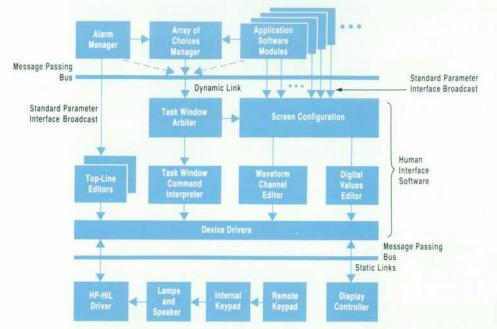

As can be seen in Fig. 1, the Component Monitoring System's functionality can be represented in a layered scheme. Similar to existing computer systems, the hierarchy has four levels:

Fig. 1. The basic task allocation scheme of the Component Monitoring System uses a layered software structure. The lower-layer activities are transparent to the application software modules, which are designed to run on a virtual processor.

# Component Monitoring System Software

| Total amount of source code:                                               | 315 KNCSS   |

|----------------------------------------------------------------------------|-------------|

| Number of software modules developed                                       | 30          |

| Number of module instances in an instrument                                | 43          |

| Number of message passing bus headers allocated<br>by the operating system | 380         |

| Average data flow on the message passing bus                               | 50 kbytes/s |

- The CPU cards represent the basis for all data processing. They communicate over the message passing bus. All interfaces to external devices are found here.

- Firmware located on these cards provides services to the higher layers of the model. The firmware implements complex application independent functions by converting commands and protocols into hardware related signals. Patient parameter modules play a special role: controlled by firmware, their analog and digital hardware converts the incoming patient signals into digital information accepted by the computer module.

- The operating system establishes the data paths between the application software modules on the one hand and the firmware on the other. It controls the execution of the application programs, moves messages back and forth, and continuously supervises the correct execution of all functions.

- It is up to the applications to provide the signal interpretation, computation, alarm generation, and similar functions and to support user interaction by drawing windows and menus on the screen. How functions are implemented in the lower layers is hidden from the application software modules.

### Modules and Messages

All function cards are designed so that they can be arbitrarily combined over the central plane. They can transmit and receive messages and perform their functions regardless of the slots in which they reside.

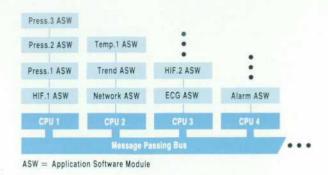

In a straightforward extension of this principle, the Component Monitoring System software architecture allows for arbitrary distribution of software to the various processor cards (see Fig. 2). These self-contained application software modules are the building blocks of the modular system. Each module represents a large functional area for example, the signal processing for the blood pressure measurement with its affiliated aspects of alarming, control interaction, transducer calibration, and so on.

To achieve this modularity, the current configuration is made transparent to the modules. They will execute on any CPU card, and their sharing of a CPU card with other modules will not interfere with their operation. The only way they can communicate is to transmit and receive messages. As with the message passing bus, the

Fig. 2. Application software modules can be assigned arbitrarily to the available CPU cards to achieve the most economical resource utilization.

origins and destinations of these messages are hidden from the application.

This principle guarantees maximum flexibility in reaching the required functionality with a given hardware set. It also reduces development risks, since at the beginning of a complex project, neither the sizes of the modules nor the resulting processing requirements can be accurately estimated.

# **Inside a Module**

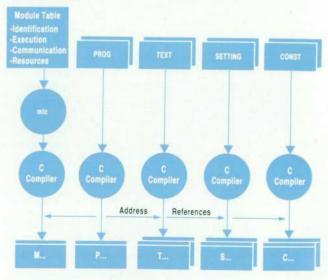

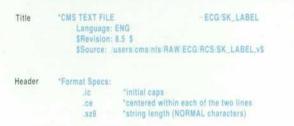

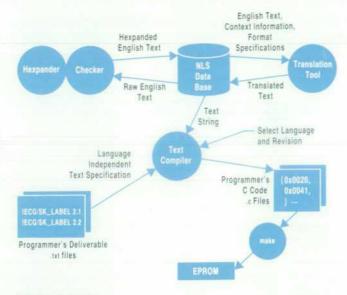

From a programmer's point of view, a module is composed of a number of related C-language source files (see Fig. 3). There are different types of files. For example, PROG files contain executable code and variable definitions, and TEXT files consist only of character codes.

Following a tailored syntax, an ASCII file called a module table provides comprehensive information about that module. Identification, communication behavior, execution, and resource requirements are specified in this table. This file is converted to C source code by means of an HP-developed compiler called mtc. In this way, a generic module

Fig. 3. An application software module consists of a module table and a set of C source files. A proprietary compiler, mtc, converts the module table to C source code. structure is defined, along with a formal description of interfaces among the modules and the rest of the system. These standardization rules are followed by every software designer, specify the guidelines for all interaction, and lay the foundation for a fully automated code generation process. Thus, machine-processed specification *enforces* standardization.

All C code is then compiled and linked, yielding a number of object files, which are loaded unchanged into an EPROM card to be plugged into the computer module.

### Virtual Processor

The main characteristic of this software concept is that the current configuration is invisible to all of the applications. They do not know which modules are assigned to which processor, how many processors are available, which interface cards are present, or where messages come from and where they go. Therefore, software developers must not make any assumptions as to where their applications will be executed. The only way modules are allowed to communicate with each other is by exchanging messages.

These are prerequisites for a truly modular system in which applications can be mixed and matched according to a predefined functionality. With this in mind, it is appropriate to define an abstract programming model that we call a *virtual processor* (see Fig. 1). This is a collection of artificial resources such as application priorities or data links. The virtual processor supplies the application programmer with all of the construction elements necessary to implement functions effectively and straightforwardly. The programmer can write functions that process

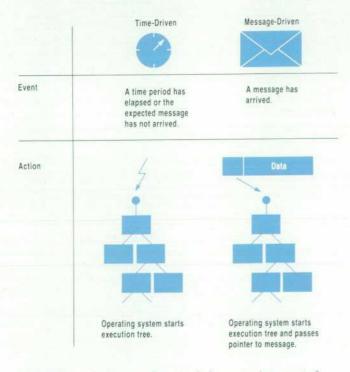

Fig. 4. Execution trees can be started after a certain amount of time has elapsed or when a certain event occurs.

# Component Monitoring System Software Development Environment

All development was performed on HP 9000 workstations running under the HP-UX operating system and connected by a local area network. This includes the operating system, the development tools, and all applications and documentation. Each workstation had mass storage and emulation facilities (HP 64000) and could be tailored to specific needs.

Starting out with only a few developers on a single HP 9000 Series 500, we ended up with about ten HP 9000 Series 300 systems being used by 20 software engineers toward the end of the project.

Thanks to the power and flexibility of these HP-UX systems, the continuous evolution of the development environment proceeded very smoothly with respect to both its extent and its comprehensiveness. For example, all generic data (e.g., symbol tables for message specification or tools for process automation) was automatically updated on all machines. As a consequence, at any point in time, identical processes were used project-wide—a prerequisite for smooth integration of the components.

Since all application modules have the same form, it was possible to implement the standard generation processes only once. Besides the definition and evaluation of the module table, a uniform process supports the implementation of any application. This turned out to be very helpful, for despite the different functions of the modules and the various inclinations of the development engineers, one always finds recurring features in any implementation. This makes software maintenance easier for engineers other than the original programmer. For example, different language options of a module can be generated without touching any code.

In our environment, a single engineer had complete responsibility for specifying, designing, and implementing each software module. The activities of all of the developers had to be decoupled as much as possible. Since enforced synchronization would have been intolerable, a major requirement for the development environment was to support easy generation of running versions at all involved work-stations. Here the Component Monitoring System's self-configuration, implemented as the boot process, proved valuable. All software modules are self-contained and independent. During the boot process the modules are initiated within the current run-time environment. This environment can always be tailored to meet the needs of the module under construction.

The integration process is always executed the same way. The current versions of the operating system and other modules are collected from the workstations on the LAN and are loaded into the current work environment. A configuration table then assigns the modules to CPUs in such a way that each module under construction runs on an emulated CPU. Symbol tables can then be corrected beforehand to allow for symbolic access to all variables and functions.

In summary, the extensive effort invested in the development environment and boot process has been very beneficial to the entire development and maintenance process, as well as to the product's quality. Other projects leveraging from the Component Monitoring System platform have profited and will continue to profit from this comprehensive and comfortable development environment.

messages without having to pay attention to how the information is distributed. Concepts such as interrupts, task control blocks, and the message passing bus chip can be ignored by the programmer, who is free to concentrate on the medical application. Thus, the application programmer's task is to convert the specific functions into programs that can run on the virtual processor, and the operating system's task is to support this program module by means of the current hardware configuration and ensure that any two applications on a single CPU do not interfere with each other. The features of the virtual processor are defined very formally, and the application programmer can only build on them. The interface specification of a module with respect to the virtual processor is found in the module table and is expressed in terms of the virtual processor.

This abstract model and its formal presentation have proven to be extremely useful, both for separating tasks within the development process, and for automating the integration process.

# **Execution Model**

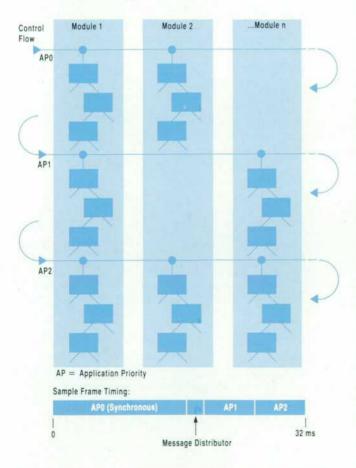

Every module's program code can be considered a set of routines forming separate execution trees. The entry routines, that is, the roots of the trees, can be executed after the completion of a certain time period or upon reception of a message (Fig. 4). Since functional areas within a module may have different precedence requirements, execution trees can be assigned to one of several application priorities (see Fig. 5). For example, continuous waveform processing has the highest priority assignable, because it must process a batch of samples every 32 ms, and thus may delay the execution of all other functions if given a lower priority.

The total computing capacity of a certain CPU may be distributed among several execution trees within several modules with several priorities. The overhead generated for context switching is minimal.

Fig. 5. Application module software can be thought of as a set of execution trees. These are assigned to application priorities, which are virtual processor resources.

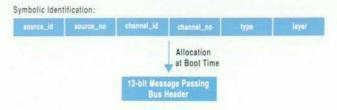

Fig. 6. Every message has a composite symbolic identification, which is evaluated at boot time, when message headers are allocated.

The application programmer specifies the priority of each execution tree. At run time, the execution time is partitioned externally to the module, without effecting its functionality. The programmer also specifies the amount of execution time required. The operating system guarantees every application the timely execution of each tree and checks this in a continuous fashion. This is essential to the safety of patient monitoring.

### **Communication Model**

As already mentioned, communication among software modules and interface cards is implemented as an exchange of messages. Message routing functions reference a 12-bit header, allowing for a maximum of 4096 different data streams. It would have been possible to assign all headers project-wide in advance, but the Component Monitoring System employs a more elaborate process for establishing data paths. Every message has a composite (six-field) symbolic identification assigned. This is evaluated at boot time when headers are allocated (see Fig. 6). Modules transmitting or receiving messages specify this symbolic identification within their module tables. This method allows the implementation of some important concepts. If modules are installed more than once, say for multiple pressure lines, multiple similar data paths have to be established appropriately. This can be done externally to the modules at boot time simply by counting the source numbers shown in Fig. 6. Also, related messages can be collected into message classes by assigning identical keys, for example to the type field. Each message of a specific class then shares a predefined structure.

Programming with message classes represents a powerful method for dealing with configuration dependencies. The operating system supports broadcast messaging in a very convenient way. For example, all alarm messages generated by various sources are transmitted in messages of type ALARM. The central alarm management facility—an application software module—can specify that it wants to receive all alarm messages and then process them in the order that they appear. Using wild-card specifiers for the unknown fields in the symbolic identification keeps the module code receiving broadcast messages regardless of the current configuration. Blocks of memory for class members can be requested with a simple entry in the module table. The configuration dependencies are then resolved at boot time.

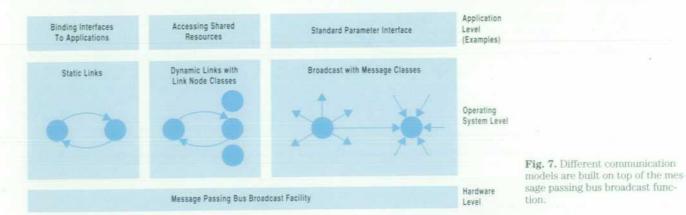

Besides broadcasting, the Component Monitoring System operating system uses two other important types of communication: static point-to-point and dynamic point-to-

point. Static links are private communication links between two entities, most notably application software modules and interface cards. Dynamic links are valuable when one resource is used by different application software modules at different times. A temporary write to a screen area or the reading of softkeys are examples of this concept. Classes of dynamic link nodes can be defined using the mechanism described above (link nodes are entry points into an application software module whose affiliated message is of some type specified in the receiver's module table). Fig. 7 summarizes how these communication types are built on the message passing bus broadcast facility to serve the upper application level.

The standard parameter interface represents the backbone of patient data communication within the Component Monitoring System. It is a set of class definitions that forms a kind of logical data bus on which all patient data processing modules can broadcast their data. Any receiver can then operate on waveform, numeric, alarm, or other messages in a completely decoupled fashion.

### **Automated Configuration**

Modules contribute to the system's flexibility only if their handling is simple, comparable to the ease of handling patient parameter modules. To achieve this, the Component Monitoring System development environment makes heavy use of automated processes, acting on formal interface descriptions. The module table, for example, is composed of the formal specifications relating to the specific module. When specifying communication behavior and execution requirements, the programmer can reference items of interest by means of symbolic names—the same names that can be found in the program source code.

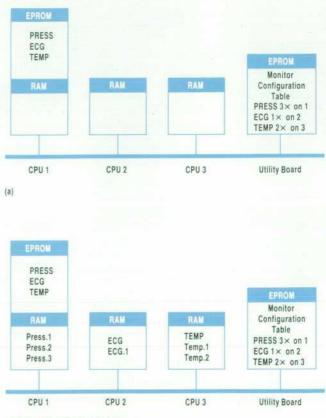

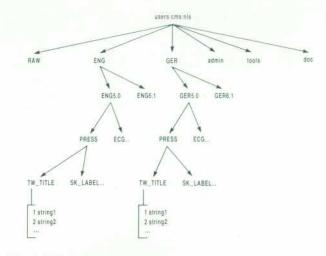

As long as the system is not powered, all hardware and software components appear unrelated. The computer module cards are all connected electrically, but no logical data path is apparent. The CPUs are "empty" (Fig. 8a). At boot, a monitor configuration table located on the central EEPROM tells the boot process how to arrange software modules on the CPU cards (Fig. 8b). Using the module tables in the individual modules, the boot process binds the modules into the run-time system. After the program code has been transferred to the CPU cards and all configuration dependent data structures have been initialized, all modules will operate as expected. More than 40 application software module instances are installed in the Component Monitoring System. In this process, the module tables supply all information necessary to install the data paths. In the first step, reservations for message passing bus headers are accepted. All references to communication concepts such as message classes can then be resolved. The process is analogous to the link process for computer object code. More than 800 message passing bus headers are allocated by the boot process; this gives an idea of the amount of communication that is required to operate the system.

Delaying the linking of software modules until the boot process has, among others, one important advantage: it

PRESS, ECG, TEMP: Module Code

Press.x, ECG.x, Temp.x: Module Instance Data

(b)

Fig. 8. A monitor configuration table tells the boot process how to arrange the application software modules on the CPUs.

allows configuration independent implementation and an ease of software maintenance that is normally true only of hardware elements.

# Conclusion

Both the software design and the Component Monitoring System software development environment (see page 15) placed great emphasis on decentralization and decoupling and on the standardization and formalization of interfaces. The latter provides the opportunity for comprehensive automation, which in turn shows significant advantages:

- Automation of all external activities supports a smooth integration of each module into the total solution. It eliminates communication problems within the development team by separating responsibilities and establishing noncorruptible entities.

- Automated processes are reliable and efficient. They only have to be implemented once, and future users do not need an in-depth understanding to be able to use them.

- Automated processes enforce consistency. Deviations from a standard are prevented by the tools. Specification

flaws quickly become apparent. The overall system remains consistent. This is an important contribution to software quality.

Automated processes maintain flexibility. The evolution of processes can be coordinated centrally, with only a few engineers involved. Users are affected to a much lesser degree.

A project of the magnitude of the Component Monitoring System software development cannot be managed in a reasonable way without a very high degree of automation.

# Acknowledgments

The author would like to thank the engineers from the operating system group, namely Martin Bufe, Kai Hassing, Holger Kaun, Paul Kussmaul, and Wolfgang Schneider, for their ingenious work on the operating system and the development environment, as well as their professional support for all application programmers.

# **Component Monitoring System Parameter Module Interface**

This interface is the link between the component Monitoring System computer module and the patient parameter modules. It provides fast response, optimum use of the available bandwidth, configuration detection, and parameter module synchronization.

# by Winfried Kaiser

The parameter module interface of the HP Component Monitoring System is the interconnection between the computer module and the module rack. The module rack can house a wide range and a varying number of parameter modules. By means of transducers attached to the patient, the parameter modules measure the patient's vital signs. These devices include the ECG, temperature, and recorder modules, and many others.

The major challenges associated with the design of the parameter module interface can be summarized as follows:

• The system must be able to support communication between the rack interface card in the computer module and a variety of parameter modules that may differ in such characteristics as the sampling rate of the analog signal, the number of signal input or output channels, the kind and amount of data that a parameter module receives from the computer module (control data) or sends to the computer module (status data), and mechanical size (1, 2, or 3 slots wide).

- It is a requirement of some clinical applications that certain waveform samples be measured and made available at an analog output with an absolute delay of less than 20 milliseconds.

- It must be possible to plug any parameter module into any slot in the module rack. The system must identify the parameter module and its position within the rack (configuration detection).

- The communication link of a system under power must not be influenced by plugging in or unplugging parameter modules or even entire racks.

- The parameter modules must be synchronized with each other.

- The link must support the detection of defective devices.

# Link Design

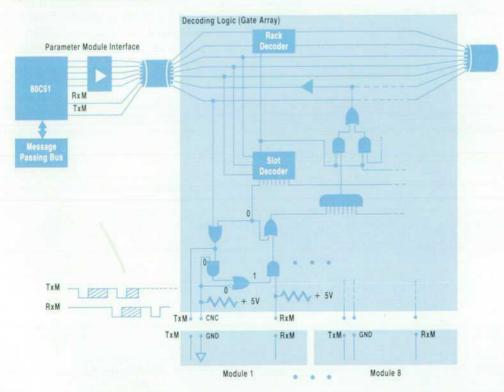

The rack interface card in the computer module has one connector to interface to as many as four module racks. A module rack houses a maximum of eight single-width

Fig. 1. Up to 32 parameter modules are addressed using five address lines. Decoding logic connects the addressed module to the receive and transmit lines of the rack interface in the computer module. modules. This means that up to 32 parameter modules can be attached to one rack interface card.

Connections are established to each of the 32 slots by means of five address lines (see Fig. 1). Using these address lines, the decoding logic in the addressed module rack connects one of that rack's slots to the receive and transmit lines of the rack interface in the computer module.

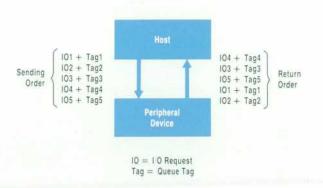

The serial interface of the 80C51 microcomputer (internal UART, full duplex, 500-kbaud) is used for communication between the rack interface card and the addressed parameter module. Because of the fast response time requirement, it was decided that the parameter modules should transmit their information one sample at a time. The rack interface gathers all parameter samples over a period of 32 ms and forms them into the corresponding message passing bus data.

# **Communication Protocol**

The rack interface controller starts the communication with the parameter modules with a special identification cycle. All possible rack slots are addressed, and a special control byte requests identification. A connected module responds by sending its device identification, hardware and firmware revision, and other parameter-specific data.

Using this identification and an internal reference table, the rack interface compiles all necessary data about the connected device types. This includes each device's sampling rate and its number and kind of transmit and receive bytes. After scanning all of the slots, the system knows which parameter modules are available.

Special digital logic together with a simple connected/ not-connected connector pin inside each parameter module enables the rack interface to recognize whether or not a module is plugged into any slot, or whether a module is defective. If a parameter module is connected, it responds when it receives the control byte from the rack interface. If a module is not connected, the incoming byte is sent back to the rack interface card without any delay. If there is no response at all a defective module is recognized.

# Scan Table

After the system determines which parameter modules are present, a scan table is generated in the rack inter-

| face to describe and control all subsequent communica-     |

|------------------------------------------------------------|

| tion. The scan table consists of 16 2-ms time slices. The  |

| table entry for each time slice specifies which parameters |

| are polled during that time slice (see Fig. 2).            |

The arrangement of the scan table depends on the speed classes of the parameter modules connected. There are five speed classes based on the sampling rate of the parameter modules: 2-ms, 4-ms, 8-ms, 16-ms, and 32-ms. The 2-ms parameters are entered in each column of the scan table, the 4-ms parameters in every other column, and so on. A special algorithm guarantees that the entries are made so that each device is addressed at fixed intervals.

The free part of the scan table is used to address slots that have no modules inserted. When a parameter module is plugged into the rack it is immediately recognized and activated in the scan table, which contains the superset of all parameter modules that are allowed. A module that is removed from the rack is deactivated. Thus it is possible to connect and disconnect any parameter module during normal monitoring.

Analog output devices that need a fast response time are entered at the end of each time slice and receive the data from the selected parameter module within the same time slice. The total delay from input to output is less than 2 ms (see Fig. 2).

# **Parameter Module Interaction**

When a parameter module is addressed by sending it a message (receive interrupt), it responds immediately by transmitting a predefined internal data block, typically consisting of waveform and status data. After the transmission, the parameter module starts an analog-to-digital conversion cycle of the patient signal or performs other tasks depending on the control information in the received message. The result of the analog-to-digital conversion and status information are stored into a module's internal data block. This data is transmitted the next time the parameter module is addressed. Since communication with a particular device always takes place after a fixed interval, the module can synchronize itself with this polling sequence.

At the 500-kbaud data rate of the parameter module interface, a typical communication cycle with a parameter module with one waveform takes about 120 microsec-

Time (ms)

|    | 0   | 1    | 2   | 3   | 4   | 5    | 6   | 7   | 8   | 9    | 10  | 11  | 12  | 13   | 14  | 15  |

|----|-----|------|-----|-----|-----|------|-----|-----|-----|------|-----|-----|-----|------|-----|-----|

|    | ECG | ECG  | ECG | ECG |

|    | P1  | Sa02 | P2  | NBP | P1  | SaO2 | P2  | NBP | P1  | Sa0, | P2  | NBP | P1  | Sa0, | P2  | NBP |

|    | P3  | 5402 | T.3 | T4  | P3  | 5402 |     |     | P3  | 0002 |     |     | P3  | 5402 |     |     |

| 15 | co  | T2   |     |     | T5  |      |     |     |     |      |     |     | -   |      |     |     |

| 5  | T1  |      |     |     |     |      |     |     |     |      |     |     |     |      |     |     |

|    |     |      |     |     |     |      |     |     |     |      |     |     |     |      |     |     |

|    |     |      |     |     |     |      |     |     |     |      |     |     |     |      |     |     |

Fig. 2. The scan table entries specify which parameter modules are addressed in each of sixteen 2-ms time slices. Analog output devices that need data immediately receive it within the same time slice. onds. When communication with one module has been completed, the next device in the scan table is addressed.

This procedure ensures both optimum use of the available bandwidth and synchronization of the parameter module and the rack interface card.

# Summary

The parameter module interface represents a very flexible solution for connecting a wide variety of modules to the Component Monitoring System computer module. Although the requirements addressed by the interface are complex, the final implementation is both versatile and rugged, and was kept relatively simple by integrating some of the decoding logic.

# Acknowledgments

I would like to thank Dieter Woehrle and Norbert Wunderle for their excellent contributions in developing and implementing the parameter module interface and the firmware for the parameter modules.

# Measuring the ECG Signal with a Mixed Analog-Digital Application-Specific IC

Putting the ECG data acquisition subsystem into a Component Monitoring System parameter module mandates high-density packaging and low power consumption, and was only possible by implementing major elements of the circuit in a large mixed analog-digital ASIC.

# by Wolfgang Grossbach

Nearly everyone is familiar with one of the most important medical parameters—the electrocardiogram, or ECG. The electrical voltages created by the heart have been well-known to the medical community for nearly a century. In the beginning the ECG was measured by sensitive galvanometers with the patient's hands and feet placed in vessels filled with saline solution. Improvements in the assessment of diagnostic ECG signals have been closely related to the evolution of electronics, great strides being made when amplifying devices such as vacuum tubes and later transistors became available. Today, low-noise operational amplifier circuits are state-of-the-art for ECG signal processing.

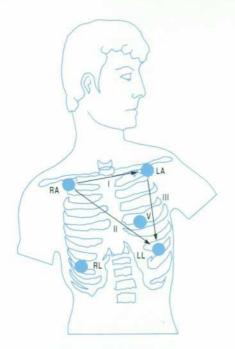

Physiologically, the polarization and depolarization of the heart's muscle mass creates a three-dimensional electrical field that changes with time. As a result, voltages can be measured on the surface of the body that represent the pumping cycle of the myocardium. A strong effort has been made to standardize the points at which the voltages should be measured. The most widely used are three differential voltages: From right arm (RA) to left arm (LA), from LA to left leg (LL), and from LL to RA. These voltages are known as ECG leads I, II, and III. The right leg electrode (RL) acts as the neutral pole in this system. This configuration is known as the Eindhoven triangle (see Fig. 1).

### **ECG Signal Characteristics**

The amplitude of the ECG signal as measured on the skin ranges from 0.1 mV to 5 mV. The frequency extends from 0.05 Hz to 130 Hz. Physiological signals like the ECG differ from artificial signals in that they are not reproducible from one time segment to another. They are more statistical in nature and have larger variations in signal characteristics than, say, a signal generator output. This places additional requirements on the measurement system, especially the analog input stages. Although the average amplitude is only around 1 mV, there are large dc offset voltages because of electrochemical processes between the electrode attached to the patient and the patient's skin. These can be as high as ±500 mV. Also, the contact resistance between an electrode and the body surface can vary widely and reach values around 1 M $\Omega$ . In addition, the system must be capable of detecting that an electrode has fallen off the patient. Perhaps the largest constraint is the presence of 60-Hz or 50-Hz power line noise. The human body acts like the midpoint of a capacitive divider between one or more power lines and ground. Thus, common-mode voltages as high as 20V p-p can be superimposed on the body. Eliminating this source of noise is one of the major tasks of an ECG amplifier. Fortunately, the ECG signals are differential signals while the power line

Fig. 1. Placement of ECG electrodes. The colors of the cabling system are standardized. The right leg (RL) connection acts as the neutral pole. (In monitoring applications the RL and LL connections are often as shown here and not on the legs.)

voltages are common-mode, so the noise can be reduced with differential amplifiers.

Another requirement results from artificial pace pulses used to stimulate the heartbeat of some patients. Pacemaker devices are implanted into the chest, generating small pulses up to 1V p-p at frequencies in the kilohertz range. Pace pulses are superimposed on the ECG signal and have to be detected to differentiate them from the peak value of the ECG signal, called the QRS complex. This is important because the heartrate measurement is based on this QRS signal, and an incorrect interpretation would result in an incorrect value.

In emergencies when the heart stops beating (ventricular fibrillation), a commonly used procedure is to apply a voltage pulse of about 5 kV p-p with a 5-ms duration to synchronize the neural stimulus of the heart's muscle mass and bring it back to normal operating conditions. Because of the high voltages needed to defibrillate a patient, the inputs of the ECG circuit must be protected. Other sources of noise are electrosurgery devices, which are used in operating rooms as electronic scalpels. These devices contain high-frequency currents in the megahertz range. The high current density at the tip of the electrode coagulates the protein, thereby stopping bleeding. The ECG module must provide additional filtering against this high-frequency noise.

# **Integrated Solution**

The design goals for the Component Monitoring System ECG module included reduced cost, reduced size, minimum power consumption, and increased reliability and functionality compared to the current patient monitor generation.

The target size was a single-width parameter module. This module measures only 99.6 mm by 36 mm by 97.5 mm

(3.9 in by 1.4 in by 3.8 in). It was therefore obvious that we would have to use surface mount technology to meet the size objective. In addition, it soon became apparent that a large percentage of the electronic circuit would have to be integrated in silicon if the entire device was to fit into a single-width module. This and the need for cost reduction on such a high-volume parameter module as the ECG module clearly indicated that an application-specific integrated circuit (ASIC) would be the appropriate solution.

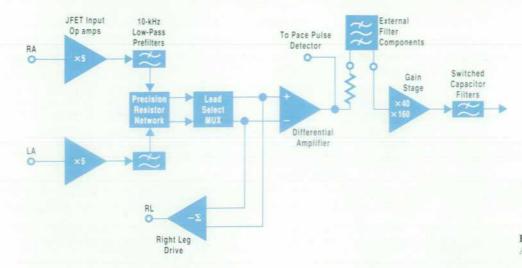

The investigation revealed that the chip size we had in mind and the mixed analog-digital design were real challenges for a fully custom ASIC. Our plan was to integrate the following function blocks into a single chip:

- Full three-channel ECG amplifier with various filter stages of both analog and switched capacitor type

- Precision resistor network for the weighting function

- Three-channel lead select multiplexer

- Precision differential amplifiers with high common-mode rejection ratio

- Eight-channel multiplexer for sequential scanning of all analog signals

- Bandgap voltage reference

- 10-bit analog-to-digital converter (ADC)

- Digital control logic for switching filter corner frequencies, multiplexers, and other circuits

- Serial interface to connect the chip with the surrounding circuits.

To be able to integrate all this, a 3-µm CMOS process was chosen. It is a p-well LOCOS process with polysilicon gates and ion implantation. NMOS and PMOS field-effect transistors are combined. Also available are n-channel JFETs and pnp bipolar transistors. The thin-film resistors are laser trimmable to within 0.1% matching. Available cells include JFET operational amplifiers, bipolar opamps, switched capacitor filters, 8-bit to 14-bit analog-to-digital and digital-to-analog converters, and sample-and-hold amplifiers.

# The Electrocardiograph ASIC

The basic functions of the ECG circuit can be seen in Fig. 2, which shows one of the three independent channels. The inputs are switched to the RA and LA electrodes as active inputs. The RA and LA inputs of the chip are connected to the patient. Protection circuits against ESD and defibrillator pulses and current-limiting resistors are provided outside the chip on the printed circuit board. JFET input opamps amplify the signal five times and act as high-impedance input buffers. A precision resistor network (Wilson network) sums the various electrode voltages to achieve the standard voltages for the different ECG selections. The multiplexer selects the appropriate lead voltages from the resistor network. The 10-kHz low-pass filters act as prefilters for anti-aliasing purposes to reduce the high-frequency components in case an electrosurgery unit or other high-frequency noise source is coupling into the module. These are analog filters. They protect the switched capacitor filters with their time-discrete sampling system against unwanted aliasing disturbances resulting from high-frequency noise.

Fig. 2. Basic structure of the ECG ASIC (one of three channels).